深入浅出IIC协议 - 从总线原理到FPGA实战开发 -- 第一篇:I2C总线协议深度解剖

第一篇:I2C总线协议深度解剖

副标题 : 两根线如何征服千亿设备?详解硬件工程师必须掌握的通信奥义

1. 为什么I2C仍是嵌入式经典?

1.1 总线拓扑的哲学

拓扑对比图

SPI需4线+N片选 vs I2C仅2线级联

UART点对点 vs I2C多主从架构

成本控制实例 :某智能手表传感器模组布线成本节省37%

1.2 技术演进时间线

- 1982~2023关键节点 :

| 年份 | 事件 | 速率提升 |

|---|---|---|

| 1982 | Philips发布初版标准 | 100kHz |

| 1998 | 专利开放引发生态爆发 | 400kHz |

| 2007 | 加入高速模式(HS-mode) | 3.4MHz |

| 2014 | 最新版UM10204规范 | 5MHz |

1.3 当代应用场景

- 工业领域 :PLC模块中的板载温度传感器链

- 消费电子 :手机摄像头模组的控制总线

2. 物理层核心机制

2.1 电气特性深度解析

-

开漏输出原理 :

电路中仅使用一个N沟道晶体管。晶体管的漏极直接输出,没有连接到电源电压。工作原理:当晶体管导通(开启)时,输出端接近地线;当晶体管关闭时,输出端是悬空的,需要外部上拉电阻连接到高电平,以确保输出端能够达到高电平状态。

优点:简化了驱动电路,方便与不同电压的电路接口,常用于I2C等总线通信协议中。

缺点:输出高电平时依赖外部上拉电阻,对电路的设计提出了额外要求;输出电流能力较弱。 -

为何需要上拉电阻?避免总线"锁死"的数学证明

-

上拉电阻计算黄金公式 :

Rp(min) = (VDD - VOL(max)) / IOL Rp(max) = tr / (0.8473 × Cb) 其中: tr = 上升时间(规范要求<1μs@100kHz) Cb = 总线总电容(包括线路+器件引脚)

- 实例计算:当VDD=3.3V, Cb=200pF时,Rp取值区间

2.2 地址扩展的演进

- 7位 vs 10位寻址对比表 :

| 特性 | 7位地址 | 10位地址 |

|---|---|---|

| 设备数量 | 112个 | 1008个 |

| 首字节格式 | 0bAAA AAAA R/W | 0b1111 0AX R/W |

| 典型应用 | 传感器 | 大型存储阵列 |

3. 协议层关键时序

3.1 起止信号的时间密码

- 时序参数规范表 :

| 参数 | 标准模式 | 快速模式 | 单位 |

|---|---|---|---|

| tSU:STA | 4.7 | 0.6 | μs |

| tHD:STA | 4.0 | 0.6 | μs |

| tSU:STO | 4.0 | 0.6 | μs |

- 常见设计错误 :

案例1:FPGA主频过高导致tSU:STA不满足

案例2:未考虑线延迟引发的建立时间违例

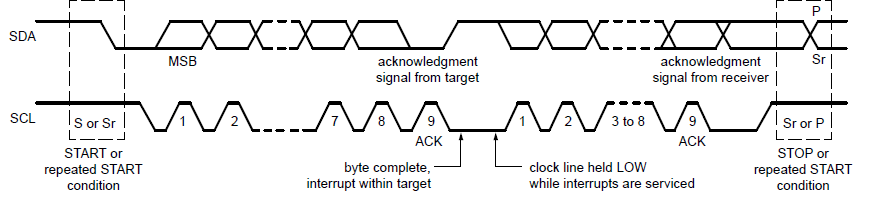

3.2 ACK/NACK应答机制

- 从机响应流程图 :

Master发送字节 → 释放SDA → 从机在第9时钟拉低SDA → Master检测ACK

- NACK的三种含义 :

- 从机地址不匹配

- 写入时从机寄存器不可写

- 读取时主机应终止传输

3.3 时钟拉伸(Clock Stretching)

- 典型应用场景 :

低速从机(如EEPROM)的数据准备期

安全芯片的加密计算耗时阶段 - Verilog处理代码片段 :

always @(posedge scl) begin if (slave_busy) scl_out <= 1'bz; // 释放SCL线 else scl_out <= scl_gen; end

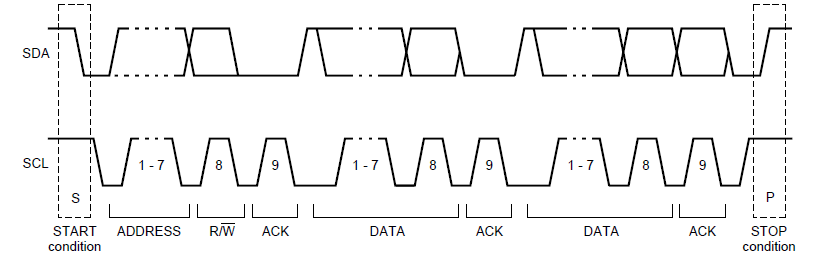

4. I2C 协议时序要求

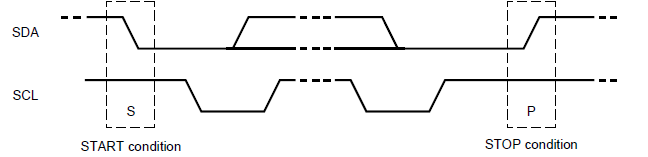

4.1 I2C传输开始结束时序

SCL: 高电平

SDA: 高电平 -> 低电平 传输开始

低电平 -> 高电平 传输结束

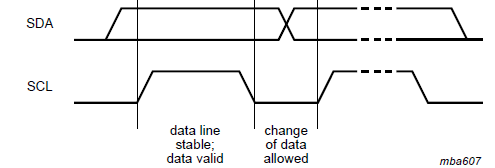

4.2 I2C有效数据时序

SCL:高电平时,SDA保持不练

SDA: SCL低电平时,SDA允许变化

4.3 I2C数据传输时序

Byte format: MSB first

配套资源

- I2C协议检查表 (PDF下载):包含22个关键参数速查表

- I2C 协议 2021版本 :62页完整I2C协议