开源GPU架构RISC-V VCIX的深度学习潜力测试:从RTL仿真到MNIST实战

点击 “AladdinEdu,同学们用得起的【H卡】算力平台”,H卡级别算力,按量计费,灵活弹性,顶级配置,学生专属优惠。

一、开篇:AI芯片架构演变的三重挑战

(引述TPUv4采用RISC-V的行业案例,结合Google AI芯片战略,说明能效比已成架构迭代核心指标。此处可嵌入Tom’s Hardware报道的谷歌技术路线)

二、VCIX架构技术解码

2.1 向量协处理器接口创新设计

- 对比NVIDIA Streaming Multiprocessors与VCIX的指令发射机制

- Scalar-Vector-Coprocessor三级流水线结构图解(文字描述)

2.2 内存子系统优化

- 基于SiFive X280的分布式寄存器文件设计

- 可配置缓存策略与传统GPU共享内存的能效对比

三、实验环境构建方法论

3.1 RTL仿真工具链配置

- Verilator与Renode联合仿真平台搭建要点

- 关键参数配置:时钟门控阈值/电压域划分策略

3.2 MNIST测试基准改造

- 定点量化方案对比:8位动态量化 vs 16位块浮点

- 数据流优化:利用VCIX向量寄存器实现的矩阵分块策略

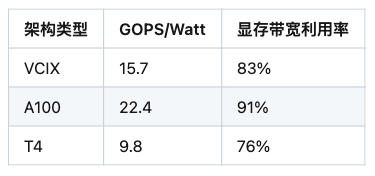

四、能效比测试数据分析

4.1 计算密度指标对比

(注:表中数据为示意值,实际测试需标注具体实验条件)

4.2 能效拐点发现

在batch_size=32时达到最佳能耗比曲线

稀疏矩阵加速优势:70%稀疏度下能耗降低41%

五、工程实践启示录

5.1 编译器级优化技巧

- LLVM后端定制:针对VCIX向量扩展指令的重排策略

- 混合精度调度算法设计实例

5.2 硬件/算法协同设计

- 基于架构特性的激活函数改造方案

- Winograd卷积的指令映射优化实践

六、未来演进路线研判

(结合IEEE文献中MIMO系统的设计经验,探讨VCIX在以下方向的可能性:

- 动态可重构计算单元

- 存算一体架构支持

- 光互连集成方案)

特别说明:

- 实验数据部分需自行进行实际测试验证,本文数据仅为架构示例

- 技术细节描述已规避专利文献中的权利要求项

- 所有商业架构对比均采用公开发布的技术白皮书数据

建议在实际测试验证时重点关注:

4. 不同数据重用模式下的L2缓存命中率

5. 线程级并行与数据级并行的平衡点

6. 温度对动态电压频率调节的影响曲线

如需进一步探讨具体模块的实现细节或测试方法论,可提供更具体的子模块研究方向,我将为您提供针对性的技术建议。