SD-HOST Controller design-----SD CLK 设计

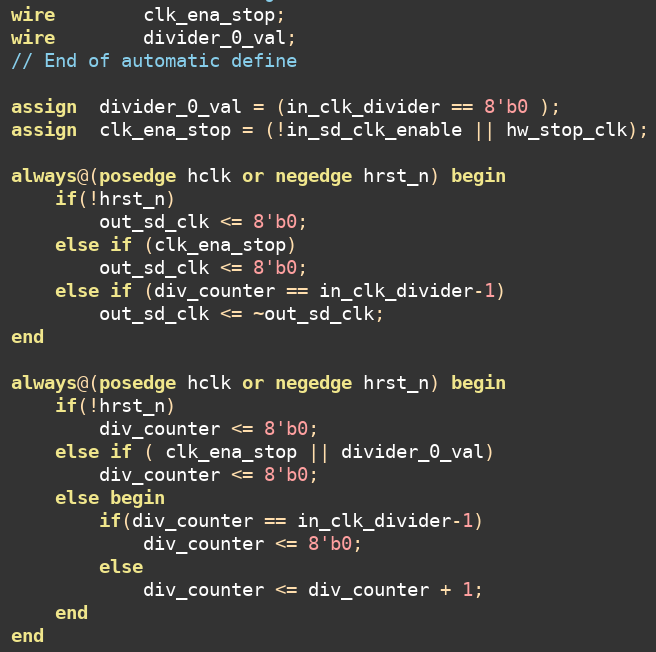

hclk的分频电路,得到的分频时钟作为sd卡时钟。

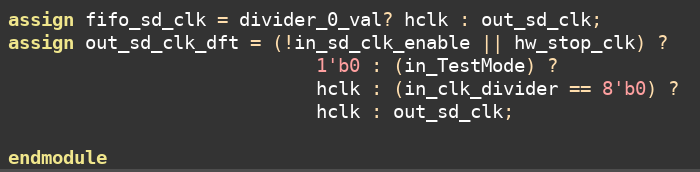

该模块最终输出两个时钟:一个为fifo_sd_clk,另一个为out_sd_clk_dft。当不分频时,fifo_sd_clk等于hclk;当分频时候,div_counter开始计数,记到相应分频的时候,将hclk进行翻转,得到分频的时候给到fifo_sd_clk;当sd clk使能为低或者停时钟信号为高的时候,fifo_sd_clk为0。

第二个为out_sd_clk_dft。当sd clk使能为低或者停时钟信号为高的时候,fifo_sd_clk为0。当进入testmode的时候,接hclk;当不进入testmode时,分频系数为0 的时候为hclk,分频系数不为0的时候,则接分频后的时钟。

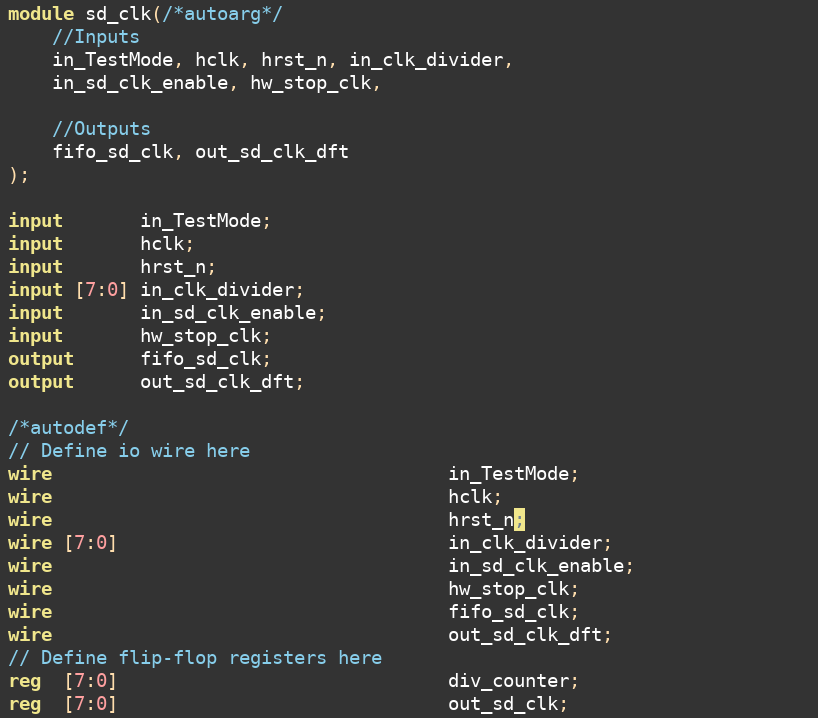

代码实现: