cache state

常用的cache一致性协议有:AXI、ACE和CHI。在ACE和CHI中分别定义了cache的state,而cache state是进行一致性维护的基础。ACE定义了MESI和MOESI这两种状态,接下来先说一下CHI的cache state。

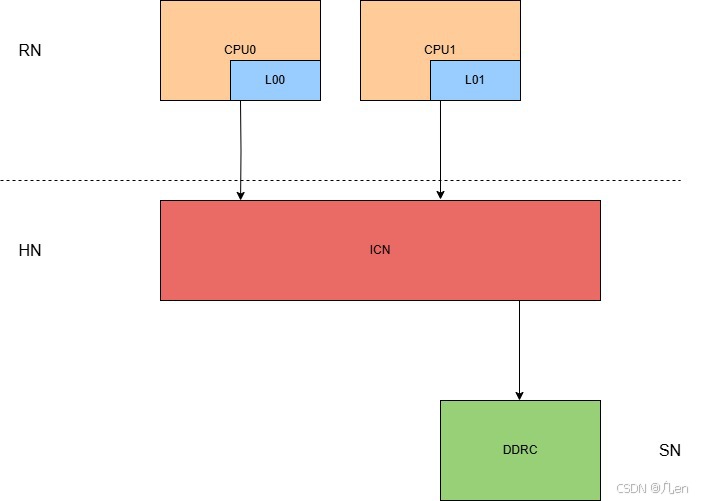

假设现在所有的cache都没有数据。

CPU0从DDRC读了一个数据到L00,这个数据地址是0x0010,数据是0x1111。那么L00有这个数据了!

先定义一下cache state model,在一个cache,有一个数据,这个数据给定义了这几种属性:

1)valid跟invalid:这个好理解呀,你读回来一个数据,你这个cache这个数据就是valid的,如果这个数据在其他cache修改了,你这就是个旧数据,那就是invalid。

比如说cpu1也读到这个数据了,也就是L01也有这个数据。然后cpu0改写了这个地址的数据,那你L01里面的就是旧数据,就是invalid的了。

2)Unique跟Shared:Unique的意思是这个地址的数据,只在我这个cache里面有,其他的cache都没有这个数据。Shared的意思,请注意!!!,Shared表示可能有其他cache里面有这个数据,仅仅是可能而已!

比如说cpu0读到的这个数据,L01里面必须没有这个地址的数据,就Unique。如果cpu0读到的这个数据状态是Shared,那L01里面可能有这个地址的数据,也可能没有。

3)clean跟Dirty:这个有一点点复杂,简单说来,根据有没有责任更新主存来。Dirty呢,表示我有责任要更新主存。Clean呢,表示我没有责任更新主存。为啥要更新主存呢,就是因为cache里面的数据跟主存里面的数据不一样,有新数据了。那是不是一个cache有新数据了,就有责任更新主存了?诶不一定哟!

比如说:cpu0读到的这个数据,然后改写了,原来数据地址是0x0010,数据是0x1111,现在跟主存里面的数据是一样的,所以没有责任更新主存,是clean的。

现在把数据改成0x2222了,诶!你就成了Dirty的了,你有责任要更新主存了。

但是现在cpu1从L00读到这个地址(可以不从主存里面读的)到L01,那么L01里面的数据也是0x2222了。那么!!两个cache的状态是什么呢!

答案是一个是Dirty,一个是Clean。哪个是Dirty,哪个是Clean呢!!??都!可!以!看怎么实现,反正现在两个cache数据都跟主存的不一样。至少而已只需要一个有责任去更新主存就好了,另一个clean。

4)Full、Partial和Empty:一般来说,我们从主存里面不会只读一个地址8bit的数据,我们会读一个cacheline,一个cacheline可能是512bit,可能更大也可能更小。假设我们是512bit也就是64Byte,CPU0读到的这个64Byte的数据,然后CPU0改了其中1Byte,那你就叫做Partial Dirty了。64Byte全改了就叫Full Dirty。那么Empty是个啥呢?就是你cache里面有一个地址,但是没有数据。为啥要这么玩?看下面cacheline的state吧哈

cache state model这东西说来也是纯软的,跟Protocol属于同一种东西,但定义了这些东西是要为硬件服务的,怎么服务呢?看cacheline state。