器件(八)—芯片封装中的开尔文源极

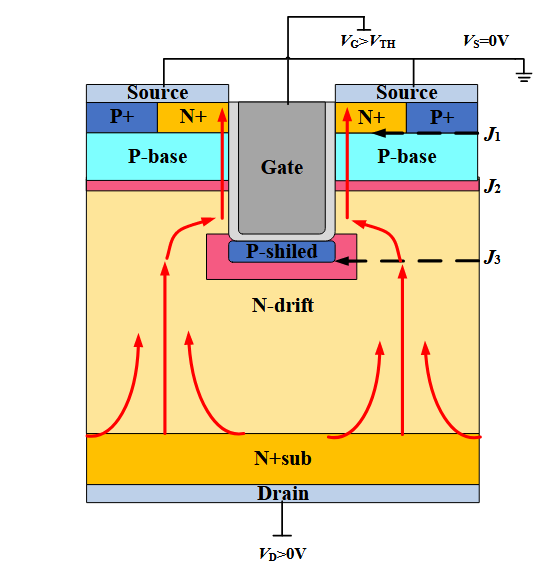

首先再次回顾一下MOS到底怎么导通的

在如上的结构中,栅极加压,让N+和P-base间形成导电沟道,Vds间加正电压,流到N+里的电子依靠这个电压一路飘洋过海,通过Gate给它开辟的沟道,从N+到P-base,再从P-base到N-drift(如果Gate不给开辟,这条道它是走不通的,会因为P-base和N-drift间形成的电场在P-base就被卡住)最后一路流到了N+sub,被漏极收集,从漏极跑到电路里,形成电流,这是漏源回路;而栅极和源极之间也会通过N+形成一个回路,就是栅源回路

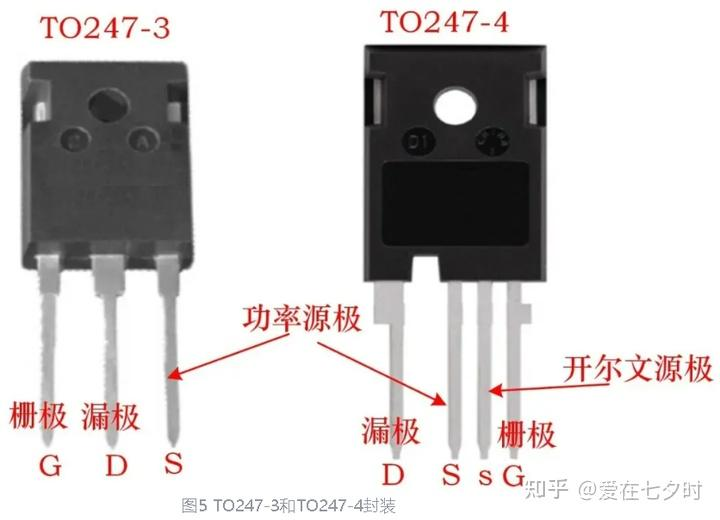

而以TO-247-4为代表的开尔文源极,本质上是在金属化时通过单独分隔出一部分源极(也就是开尔文源极),再单独打键合线,引脚引出,从而将栅源回路和漏源回路的引出部分分隔开,使漏源回路上寄生电感在开启时因为快速流过大电流而产生的几伏的反向电压影响不到栅源回路。差别看下图

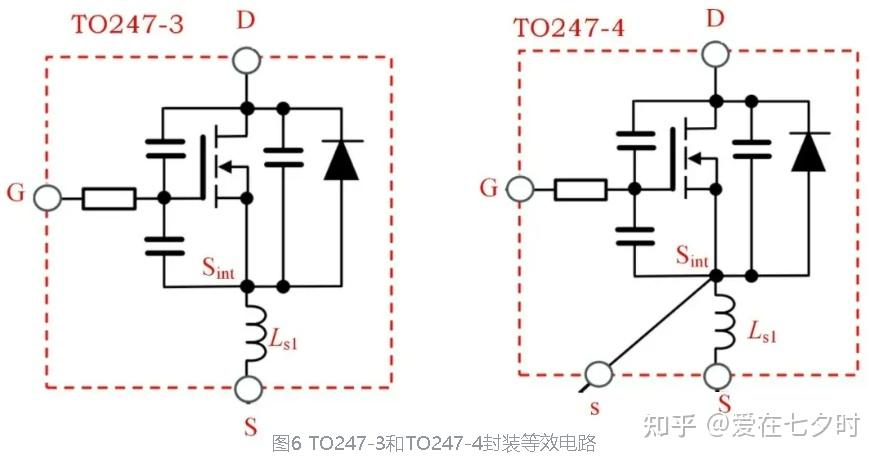

那么这里就存在了一个问题:这两个回路内部是否重合呢?

答案是,重合,区别只在于Ls1是否被两回路共用。

这里需要提到一个概念,就是芯片看上去厚,实际上是很薄一片,只有大概1mm厚,所以它的寄生电感主要来自于封装时的打线和外接端子。

而由于SiC MOSFET上流过的电流在达到极限值之前,都是外接回路给多少它流多少,所以单独接一个开尔文源极,就类似于在管道中把本来一个的出水口分成一大一小,管道内部腔体依旧相连,总出水量不变,栅源回路连接小出水口,漏源回路连接大出水口,而大小出水口并不连在一起(大源极连接在主功率回路里,开尔文源极连接在驱动功率回路中,两回路在电路板上被分隔成两个区域)所以大出水口上的动静不会影响小出水口,这时哪怕Ls1上电压已经窜到负几伏,也不影响栅极上的电压,因为这俩就不在一个回路里