ARM GIC(七)亲和路由:GICD_IROUTER寄存器具体如何与MPIDR配合使用?

ARM GIC(一) GIC V3架构基础学习笔记

完善亲和路由章节。

一、MPIDR

MPIDR(Multiprocessor Affinity Register)寄存器在ARM架构中用于标识处理器的亲和性信息,这对于中断处理非常重要,特别是在多处理器系统中。MPIDR寄存器包含多个字段,其中最重要的是Affinity Level字段,它用于定义处理器的亲和性级别。以下是MPIDR寄存器如何影响中断处理的详细说明:

-

定义处理器亲和性

MPIDR寄存器中的Affinity Level字段通常包含四个8位的子字段(a, b, c, d),这些字段定义了处理器的亲和性级别。这些亲和性级别用于标识处理器在多级处理器拓扑结构中的位置,例如在一个包含多个集群和核心的SoC中。 -

亲和性路由

在GICv3中,亲和性路由允许中断被路由到具有特定亲和性的处理器。这意味着中断控制器可以根据中断的亲和性要求将中断发送到最合适的处理器。这是通过配置GICD_IROUTER寄存器来实现的,该寄存器中的Affinity字段与MPIDR中的Affinity字段相匹配。 -

中断目标选择

当一个中断发生时,GIC会检查中断的亲和性要求,并将其与所有处理器的MPIDR寄存器中的亲和性进行比较。GIC会选择亲和性与中断要求最匹配的处理器来处理该中断。这种方式可以确保中断被高效地路由到最合适的处理器,从而提高系统的整体性能。 -

负载均衡

通过合理配置MPIDR寄存器和GIC的亲和性路由,可以实现更有效的负载均衡。例如,可以将高优先级的中断路由到当前负载较低的处理器,或者将特定类型的中断路由到专门处理这些中断的处理器。 -

实现特定的中断处理策略

在某些应用场景中,可能需要特定的中断处理策略,例如将某些中断仅路由到特定的处理器。通过配置MPIDR寄存器和GIC的亲和性路由,可以实现这些特定的中断处理策略。

示例

假设一个SoC包含两个集群,每个集群有四个核心。MPIDR寄存器可以配置为:集群0,核心0-3:Affinity Level为0.0.0.0到0.0.0.3

集群1,核心0-3:Affinity Level为0.0.1.0到0.0.1.3

如果一个中断的亲和性要求为0.0.0.x,则GIC会将该中断路由到集群0的某个核心。

MPIDR寄存器通过定义处理器的亲和性级别,对中断处理产生重要影响。它使得中断控制器能够根据中断的亲和性要求将中断路由到最合适的处理器,从而提高系统的效率和性能。

二、GICD_IROUTER

GICD_IROUTER寄存器与MPIDR(Multiprocessor Affinity Register)寄存器配合使用,以实现对中断的亲和性路由。在GICv3中断控制器中,每个SPI中断都有一个对应的GICD_IROUTER寄存器,用于配置该中断的目标处理单元(PE)。具体来说,GICD_IROUTER寄存器中的位用于指定中断的路由模式,其中bit 31用于设置中断路由模式,其取值如下:

0:该中断被路由到aff0 – aff3指定的PE上。

1:该中断可被路由到partition node上的任意PE上。

在AArch64状态下,一个PE的亲和性值定义在MPIDR_EL1寄存器中,由4个8位字段(a.b.c.d)组成的32位值。这些字段被标准化为下面的形式:Aff3.Aff2.Aff1.Aff0,其中Affx代表亲和性级别x。当启用亲和性路由时,若处理physical interrupts,那么System register access也必须启用。

GICD_IROUTER寄存器的配置允许将中断绑定到特定的CPU核心,这是通过将CPU的MPIDR_EL1寄存器写入该寄存器中实现的。例如,可以使用GICD_IROUTER寄存器来指定SPI中断的目标PE,其中n是中断号。每个core的affinity值可以通过MPDIR_EL1寄存器获取,每个affinity占用8bit。配置对应core的MPIDR值,可以将中断路由到该core上。

此外,设计必须确保MPIDR_EL1所指示的亲和值与连接到PE的Redistributor的GICR_TYPER所指示的亲和值相同。

通过ARE bit来启用Distributor安全状态下的Affinity routing,Affinity routing启用的条件:对于Secure中断,GICD_CTLR.ARE_S bit is set to 1;对于Non-secure中断,GICD_CTLR.ARE_NS bit is set to 1。

三、四层亲和路由

在ARM架构中,4层亲和性(Affinity)用于描述一个处理器核心在系统中的拓扑位置。这种4层亲和性表示法为每个处理器核心提供了一个唯一的标识符,用于中断路由和负载均衡。这四层亲和性通常表示为 Aff3.Aff2.Aff1.Aff0,每一层都可以有不同的位宽,但通常每层为8位。以下是这四层亲和性的具体含义:

Aff3(最高层):这一层通常用于表示最大的亲和性域,如在多插槽(multi-socket)系统中的不同插槽(socket)或不同的物理处理器包(package)。在单插槽系统中,这一层通常固定为0。

Aff2:这一层用于表示插槽或包内的集群(cluster)。在多核心设计中,这一层可以帮助区分不同的核心集群。

Aff1:这一层用于表示集群内的核心组(core group)。在一些设计中,这一层可以用来区分集群内的不同核心组,以实现更细粒度的亲和性控制。

Aff0(最低层):这一层用于表示核心组内的具体核心(core)。这一层通常用于直接指定中断应该被路由到的具体核心。

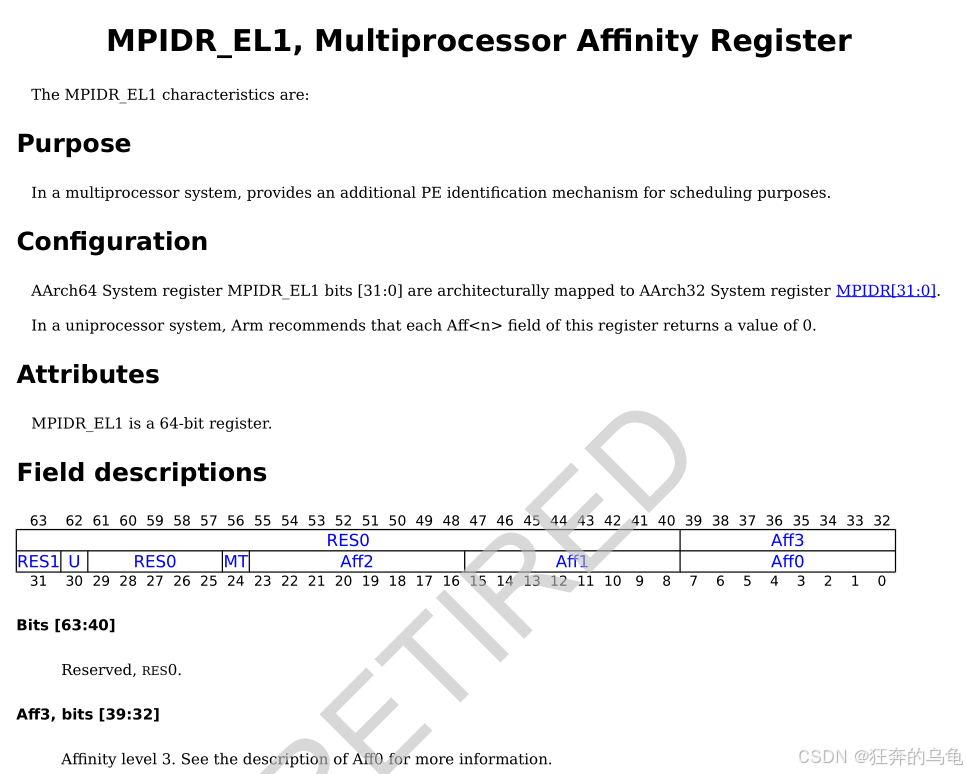

Field descriptions

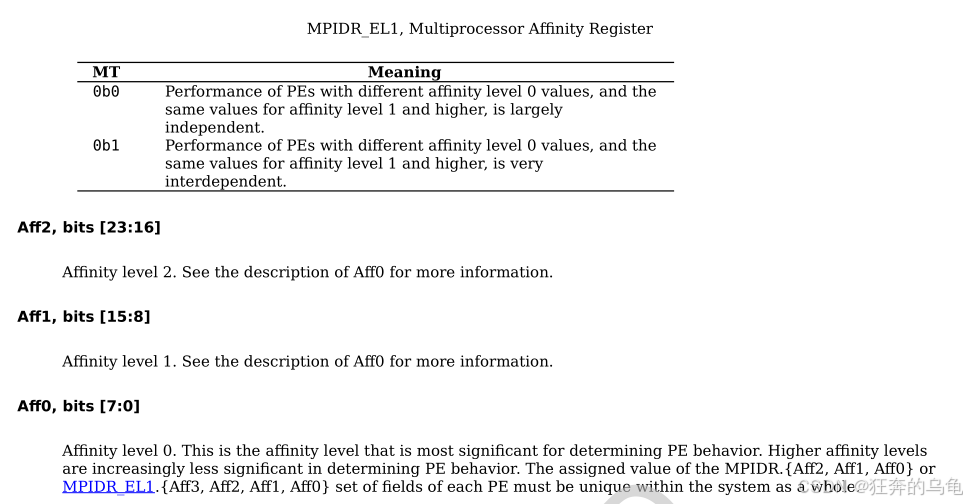

寄存器的位被分为多个字段,每个字段代表不同的亲和性级别(Affinity Level)。RES1[63:40]:保留位,读为0。RES0[39:32]:保留位,读为0。Aff3[31:24]:亲和性级别3,用于标识处理器在系统中的更大规模结构,如插槽或物理处理器包。MT[23:24]:多线程位,指示处理器是否支持多线程。Aff2[22:16]:亲和性级别2,用于标识集群内的核心组。Aff1[15:8]:亲和性级别1,用于标识集群内的核心组或子簇。Aff0[7:0]:亲和性级别0,用于标识核心组内的具体核心。

这种4层亲和性表示法允许系统设计者根据处理器的物理和逻辑结构来配置中断路由,从而实现更高效的中断处理和负载均衡。例如,在一个大的多插槽系统中,可以使用Aff3来区分不同的插槽,使用Aff2来区分插槽内的集群,使用Aff1来区分集群内的核心组,最后使用Aff0来指定具体的处理核心。

在实际应用中,这四层亲和性的位宽和具体含义可能会根据具体的系统设计和处理器架构有所不同。然而,这种分层的亲和性表示法提供了一种灵活的方式来描述处理器核心的拓扑结构,从而支持复杂的中断路由和负载均衡策略。