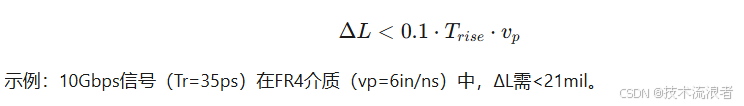

PCB设计实践(十三)PCB设计中差分线间距与线宽设置的深度解析

一、差分信号的基本原理与物理背景

差分信号技术通过两条等幅反相的传输线实现信号传输,其核心优势体现在电磁场耦合的对称性上。根据麦克斯韦方程组的对称解原理,两条线产生的电磁场在远场区域相互抵消,形成以下特性:

1. 共模噪声抑制机制

- 原理:外部干扰在两条线上产生的感应电动势近似相等,接收端通过差分减法器消除共模分量。在1GHz频段下,差分对的共模抑制比(CMRR)比单端信号提升40-60dB。

- 实例:USB 3.2接口中,差分对的共模噪声容限可达80dB,确保高速数据传输的稳定性。

2. 电磁兼容性优化

- 法拉第电磁感应定律应用:反向电流产生的磁场在远场抵消,实测显示差分线对的辐射功率密度比单端线路降低30dBμV/m。

- EMI抑制案例:在5G基站射频电路中,采用差分线设计可将高频段辐射干扰降低至FCC Class B标准以下。

3. 信号完整性保障

- 阻抗稳定性:线间耦合电容(Cm)与互感(M)的平衡关系维持奇模阻抗恒定。例如,FR4板材下6mil线宽、8mil线距的差分阻抗可控制在100Ω±5%。

- 相位同步性:差分对的对称结构减少了信号传播时延差异,适用于PCIe 4.0等要求时延偏差<1ps/inch的场景。

二、典型应用场景与技术参数规范

1. 高速数字接口

(1) USB 3.2 Gen2

- 阻抗要求:90Ω差分阻抗

- 设计参数:

- 外层:5mil线宽/5mil线距

- 内层:4mil线宽/6mil线距

- 长度匹配:偏差控制在±5mil以内,过孔数量限制为每英寸≤2个

(2) DDR4/5内存接口

- 阻抗范围:80-100Ω

- 布线规范:

- 线宽4mil,线距6mil

- 长度匹配精度±2mil,蛇形绕线间距≥3倍线宽

2. 射频与微波电路

(1) 5G毫米波频段(28GHz)

- 结构设计:共面波导结构

- 参数设置:

- 线宽12μm,线距8μm

- 铜箔粗糙度<0.1μm,表面处理采用化学沉银

(2) 微波滤波器

- 渐变线宽设计:从10mil到6mil的梯形结构

- 性能指标:带外抑制>40dB,插入损耗<0.5dB@6GHz

3. 高功率电源传输

- 服务器背板供电案例:

- 48V/10A场景下采用2oz铜厚、80mil线宽

- 线距扩展至20mil防止电弧放电,过孔载流能力按IPC-2152标准提升20%

三、线宽与线距设置的核心依据

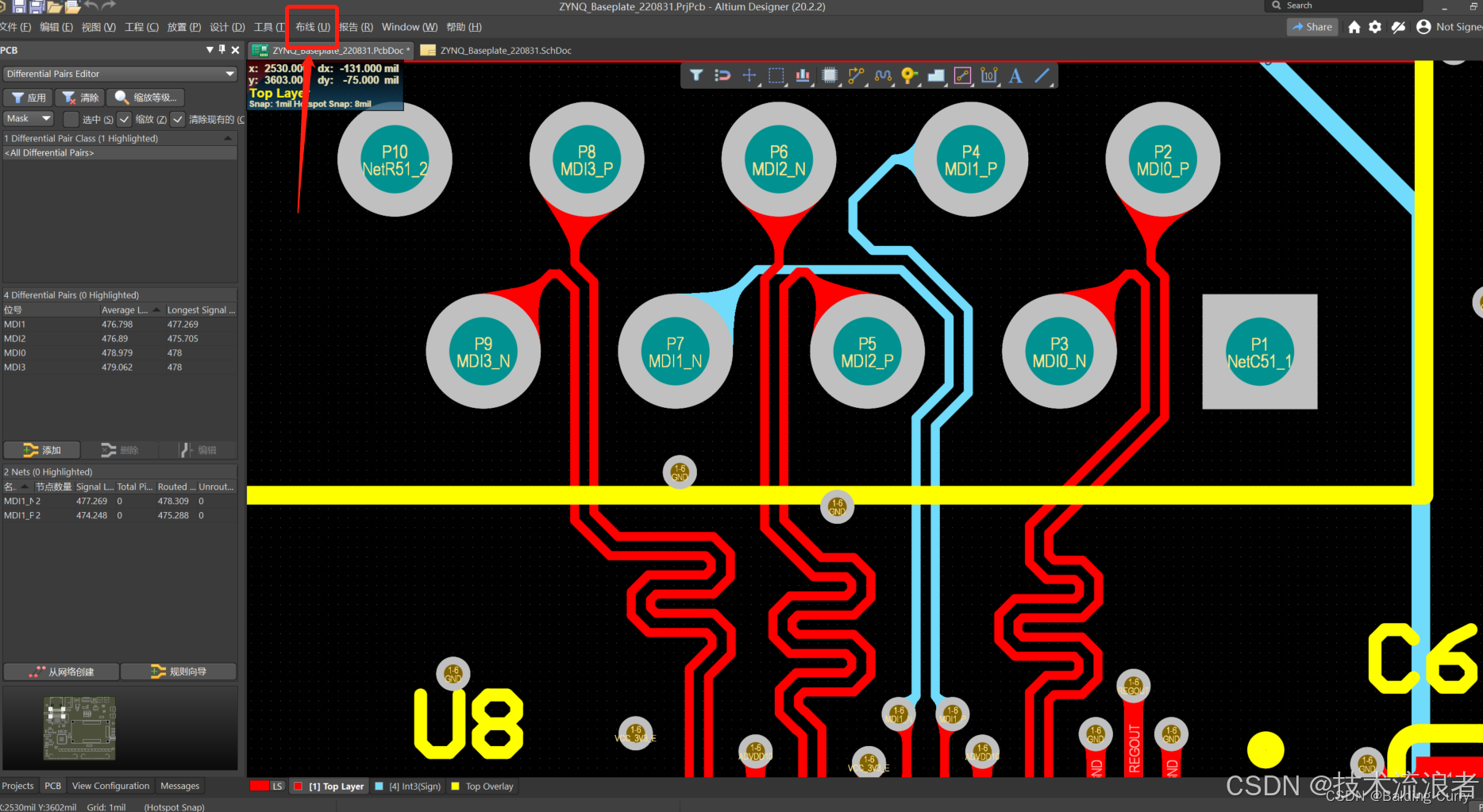

1. 阻抗控制模型

(1) 计算公式

(2) 工艺修正因子

- 介质损耗角正切(tanδ)>0.02:线宽增加5%-8%

- 铜箔粗糙度>0.5μm:有效线宽减小3-5mil

2. 制造工艺边界

| 工艺等级 | 最小线宽(mil) | 最小线距(mil) | 过孔直径(mil) | 典型应用 |

|---|---|---|---|---|

| Class 3 | 3.5 | 3.5 | 8(激光钻孔) | 5G基站天线阵列 |

| Class 4 | 2.5 | 2.5 | 6(HDI) | 智能手机主板 |

| Class 5 | 1.5 | 1.5 | 4(埋入式) | 军用雷达模块 |

设计建议:预留10%-15%工艺余量,如要求3mil线宽时按3.3mil设计。

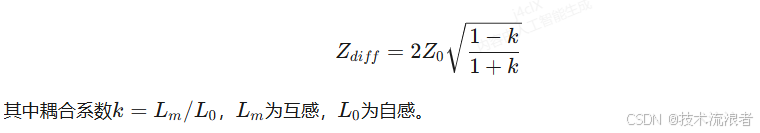

3. 电流承载与热管理

(1) 修正IPC-2152公式

(2) 邻近效应影响

- 线距<3倍线宽时,电阻增加5%-10%

- 每增加10mil线宽,载流能力提升18%-22%

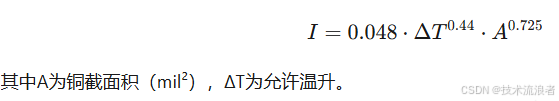

4. 信号完整性约束

(1) 时延匹配公式

(2) 串扰控制策略

- 3W原则:线距≥3倍线宽,可将40GHz频段近端串扰(NEXT)抑制至-50dB以下

- 地屏蔽过孔:每100mil间隔添加接地过孔,降低耦合电容30%

四、进阶设计技巧与误区规避

1. 动态区域规则

(1) BGA区域布线

- 0.5mm pitch BGA:线宽3.5mil,线距3.5mil

- 普通区域:线宽6mil,线距8mil

(2) 梯度过渡设计

使用Allegro Region约束功能,实现从BGA到外围区域的线宽/线距渐变。

2. 常见设计误区

(1) 过度等长绕线

- 实测数据:当偏差<15%波长时,相位误差对眼图影响可忽略

- 替代方案:采用相位补偿电路替代机械绕线

(2) 过孔效应忽视

- 损耗分析:0.3mm过孔在10GHz引入0.8dB损耗

- 解决方案:背钻技术可将损耗降低至0.2dB

(3) 地平面处理不当

- 错误案例:USB差分线下开槽导致共模阻抗突变,EMI增加6-8dB

- 正确方法:保持连续地平面,局部采用分割电容补偿

五、未来技术发展趋势

1. 异质集成技术

- 玻璃基板应用:实现0.8μm线宽/1.2μm线距,适用于112Gbps SerDes

- RDL重布线层:5μm垂直互连间距,传输损耗<0.1dB/mm@56GHz

2. AI辅助设计

- 参数优化:NVIDIA Selene超算可在24小时内完成10151015种参数组合搜索

- 缺陷预测:机器学习模型对开路/短路缺陷的预测准确率>98%

3. 三维垂直互连

- TSV硅穿孔技术:垂直间距缩小至5μm,时延降低40%

- 混合键合工艺:铜-铜直接键合实现10μm间距差分对,阻抗一致性提升30%

六、总结与设计建议

差分线设计需综合考虑电磁理论、工艺制程、信号完整性等多维度因素。建议采用以下设计流程:

- 前期规划:明确信号速率、阻抗要求、电流规格

- 叠层仿真:使用HFSS或ADS Momentum进行3D电磁场仿真

- 工艺对接:与PCB厂商确认最小线宽/线距、孔铜均匀性等参数

- 动态规则:针对BGA/连接器等瓶颈区域设置局部约束

- 后仿真验证:进行TDR测试和眼图分析,优化残余不连续点

随着5G/6G、AI计算和异构封装技术的发展,差分线设计正朝着超精细、三维化和智能化方向演进。工程师需持续关注新材料(如Low-Dk玻璃基板)、新工艺(如mSAP半加成法)以及EDA工具的算法升级,以应对未来112Gbps及以上速率的设计挑战。