EtherCAT 分布式时钟(DC)补偿技术解析

一、技术定义

EtherCAT 分布式时钟(Distributed Clock, DC)是一种基于硬件的高精度同步机制,旨在解决工业自动化系统中多设备协同控制的时间同步问题。其核心功能包括:

初始偏移补偿:消除从站本地时钟与主站系统时间的初始偏差,确保所有设备在启动阶段的时间基准一致。

传输延迟补偿:通过测量数据帧在总线上的传输延迟,动态调整各从站的时钟相位,抵消因网络拓扑和物理距离导致的时间差。

动态漂移补偿:通过周期性同步信号(如 SYNC0/SYNC1)和锁相环(PLL)技术,持续修正从站时钟的频率漂移,确保长期同步精度。

DC 技术的核心目标是实现亚微秒级(通常 < 100ns)的同步精度,支持多轴运动控制、机器人协同、精密测量等对时间敏感的应用场景。

二、具体实现方式与步骤

(一)静态补偿(初始化阶段)

参考时钟选择:

主站自动识别第一个支持 DC 功能的从站作为参考时钟源(通常为链首设备)。

参考时钟的本地时间作为整个网络的基准,通过 ARMW(Atomic Read-Modify-Write)命令周期性广播到其他从站。

拓扑结构计算:

主站通过分析从站端口状态(如 0x0900 寄存器锁存的时间戳),构建网络拓扑图,确定各从站的物理连接顺序和传输路径。

例如,从站端口转发顺序为 0→3→1→2,主站据此计算数据帧在链路上的传播延迟。

传输延迟测量与补偿:

主站发送测试帧,从站记录接收时间戳并返回,主站计算往返延迟(Round-Trip Time, RTT)。

根据 RTT 和拓扑结构,主站将单程延迟补偿值写入从站的 0x928 寄存器(参考时钟时间与本地时间偏差)。

(二)动态补偿(运行阶段)

周期性同步信号:

主站通过 ARMW 命令周期性读取参考时钟的本地时间,并通过 FRMW(Function Read-Modify-Write)子报文将时间同步到所有从站。

从站将接收到的系统时间输入到 PLL 控制器,调整本地时钟频率,消除漂移误差。

主站同步(DCM):

主站转换模式:调整主站硬件定时器(如 8254)的周期,使其与 DC 时钟主站同步。

总线转换模式:修改参考时钟从站的 0x920 寄存器(系统时间偏移),间接调整主站发送周期。

通过 PI 控制器算法计算补偿值,确保主站与从站的 SYNC 信号间隔恒定。

从站内部时序优化:

配置从站参数 0x1C32/0x1C33(如 Output Shift Time、Input Latch Time),调整数据处理与同步信号的时间关系。

例如,设置 Output Shift Time 为通讯周期的 30%,确保从站在 SYNC0 触发前完成数据复制。

三、注意事项

硬件依赖性:

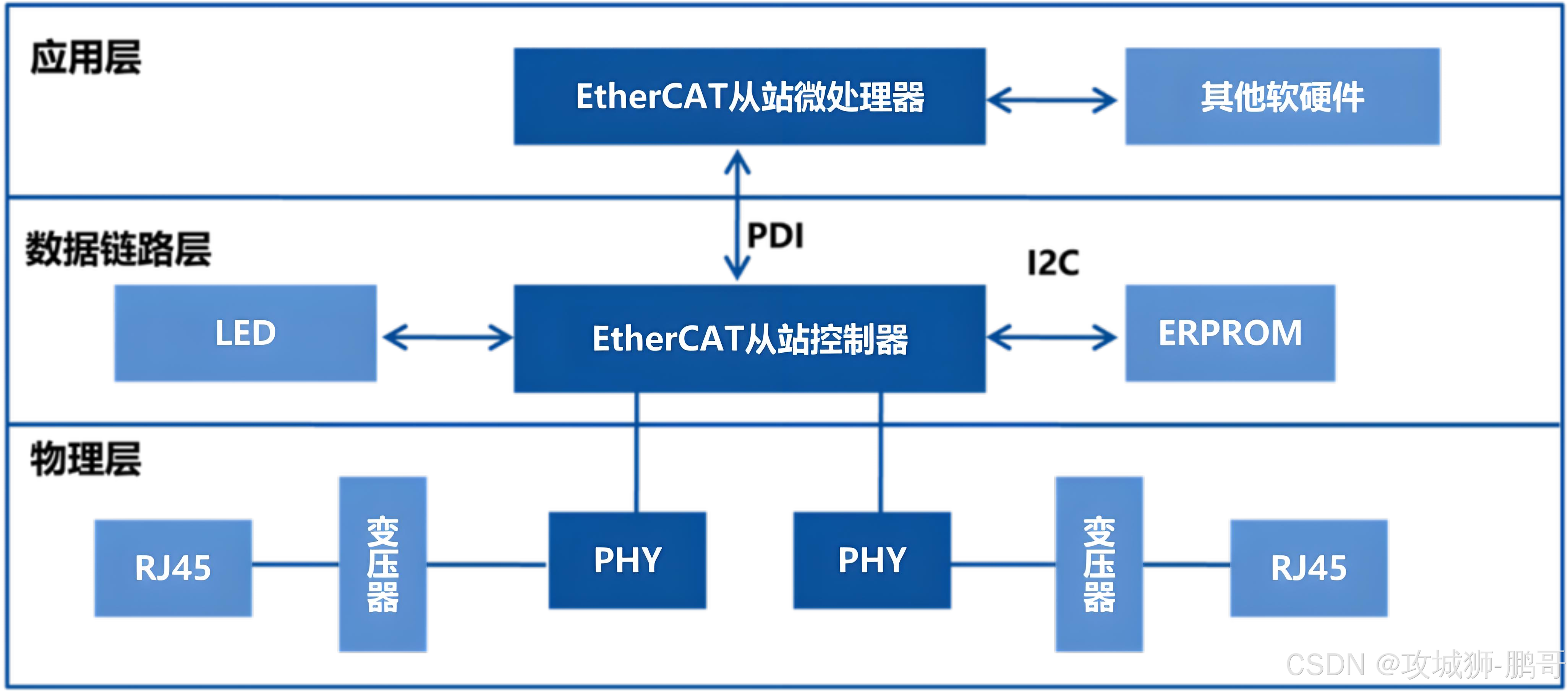

从站需使用支持 DC 功能的 ESC(EtherCAT Slave Controller)芯片,如倍福 EL6688 支持 PTPv1/v2,确保硬件级时间戳和同步信号生成。

主站需具备高精度定时器(如 FPGA 或专用实时控制器),以减少发送周期抖动。

网络拓扑影响:

线性拓扑:延迟累积显著,需严格配置从站顺序和补偿值。

环形拓扑:支持冗余路径,但需额外处理路径切换时的时间偏差。

星型拓扑:中心节点故障可能导致全局同步失效,建议采用双主站冗余。

参数调优:

SYNC Shift Time:默认值为通讯周期的 30%,需根据从站数量和处理延迟调整。

Calc and Copy Time:从站处理数据的最小时间,需确保主站周期≥从站最小循环时间。

动态场景处理:

热插拔:支持从站动态加入 / 退出,主站需重新计算拓扑和补偿值。

故障恢复:参考时钟从站故障时,主站需切换至备用参考时钟,避免同步中断。

四、优劣势分析

(一)优势

高精度同步:典型同步误差 < 100ns,满足多轴插补、精密测量等场景需求。

硬件级实现:通过 ESC 芯片内置 DC 单元,减少软件处理延迟,提升可靠性。

拓扑灵活性:支持线性、星型、树形等多种拓扑,适应复杂工业环境。

动态补偿能力:PLL 技术持续修正时钟漂移,长期稳定性高。

(二)劣势

硬件成本:需专用 ESC 芯片和主站硬件,初期投资较高。

配置复杂度:需手动计算拓扑延迟、调整参数,对工程师要求较高。

网络封闭性:仅支持 EtherCAT 设备,无法直接兼容其他协议(如 PROFINET)。

实时性依赖:主站发送周期抖动或网络拥塞可能导致同步精度下降。

五、总结

EtherCAT DC 补偿技术通过硬件级同步机制和动态算法,实现了工业自动化中高精度、低延迟的时间同步。其核心在于静态拓扑分析与动态漂移修正的结合,适用于对同步要求严苛的场景。然而,其硬件依赖性和配置复杂度限制了在低成本或非实时场景中的应用。实际部署时,需根据系统规模、拓扑结构和同步精度需求,综合权衡硬件选型与参数调优策略。