FPGA 39 ,FPGA 网络通信协议栈进阶,RGMII、ARP 与 UDP 协议与模块设计( RGMII、ARP、UDP原理与模块设计 )

目录

目录

一、核心原理

1.1 RGMII 接口:高效数据传输的物理桥梁

1.2 ARP 协议:IP 与 MAC 地址的动态映射引擎

1.3 UDP 协议:轻量级数据传输的高效选择

1.4 FPGA 实现流程

二、时序约束

2.1 时序约束理论基础

2.2 时序约束在协议栈中的应用与优势

2.2.1 RGMII 接口的时序挑战与解决

2.2.2 ARP 与 UDP 模块的时序优化

2.2.3 整体系统的时序协同

三、模块设计

3.1 RGMII 接口转换模块:数据格式的精准适配

3.2 ARP 协议模块:地址解析的全流程管控

3.3 UDP 协议模块:快速数据传输的可靠保障

3.4 辅助模块:功能强化与系统协调

3.5 模块总结

四、注意事项

五、更多操作

前言

在《FPGA 38 ,FPGA 网络通信协议栈基础,ARP 协议深度解析与模块划分( ARP与以太网帧,以及ARP模块常用文件 )》中,我们围绕 ARP 与 以太网帧展开了深入探讨,从 ARP 协议在 OSI 与 TCP/IP 模型中的定位,到以太网帧内 ARP 数据包的结构解析,再到 FPGA 中 ARP 模块的核心设计与功能实现,为 FPGA 网络通信协议栈搭建起重要的底层基石。

而网络通信的完整实现,离不开多种协议的协同运作以及对底层时序和接口的精确控制。这里将基于上篇文章的知识积累,进一步深入剖析 RGMII 接口特性、ARP 与 UDP 协议的理论要点,结合时序约束与网络基础理论,系统阐述网络通信协议栈的模块架构设计,助力构建更全面的 FPGA 网络通信认知体系。

一、核心原理

关键知识点解析,RGMII、ARP 与 UDP 的核心原理

1.1 RGMII 接口:高效数据传输的物理桥梁

RGMII(Reduced Gigabit Media Independent Interface)接口作为千兆以太网的关键接口,通过时钟双沿传输数据的特性大幅提升带宽利用率。其核心设计如下:

- 数据传输机制:在 125MHz 时钟下,利用上升沿传输低 4 位数据(RXD [3:0]/TXD [3:0]),下降沿传输高 4 位数据(RXD [7:4]/TXD [7:4]),实现 1Gbps 速率传输。

- 控制信号设计:TX_CTRL/RX_CTRL 信号在时钟上升沿传输数据使能信号(TX_EN/RX_DV),下降沿传输数据使能与错误信号(TX_ER/RX_ER)的异或值,以此确保数据有效性判断。

- 与 PHY 芯片协同:RGMII 直接对接 PHY 芯片(如 RTL8211FD),完成数字信号与以太网电信号的转换,是协议栈与物理网络连接的关键枢纽。

1.2 ARP 协议:IP 与 MAC 地址的动态映射引擎

ARP(地址解析协议)在 FPGA 网络通信中承担 “翻译官” 角色,其核心功能与设计要点如下:

- 协议流程:

- 广播请求:主机通过广播 ARP 请求包(目的 MAC 为 FF:FF:FF:FF:FF:FF),请求特定 IP 对应的 MAC 地址。

- 单播应答:目标主机接收到请求后,回复单播 ARP 应答包,携带自身 MAC 地址。

- 缓存更新:发送方将 IP-MAC 映射存入 ARP 缓存表,后续通信直接使用,减少广播开销 。

- 数据包结构:ARP 数据包(28 字节)包含硬件类型(0x0001,以太网)、协议类型(0x0800,IPv4)、操作码(1 为请求,2 为应答)、发送 / 目标 MAC 地址及 IP 地址,每个字段都需严格按协议规范填充。

- FPGA 实现重点:在 FPGA 中,ARP 模块需通过状态机控制数据发送与接收,结合 CRC32 校验确保数据完整性,并利用 Block RAM 实现动态 ARP 缓存表管理。

1.3 UDP 协议:轻量级数据传输的高效选择

UDP(用户数据报协议)以 “无连接、低延迟” 特性适用于实时性场景,其协议设计与 FPGA 实现要点如下:

- 协议特性:无需建立连接即可发送数据,适合视频流、音频通话等对延迟敏感但允许少量丢包的应用,不过可靠性需上层应用自行保障。

- 数据包结构:UDP 数据包由首部(8 字节)和数据部分组成。首部包含源端口号、目的端口号、长度(首部 + 数据)和校验和(可选,计算 UDP 伪首部 + 首部 + 数据)。

1.4 FPGA 实现流程

发送端: 在发送端,FPGA 的主要任务是构建完整的以太网帧并发送。具体流程如下:

- 构建 UDP 首部:根据应用层提供的数据,生成 UDP 首部,包括源端口号、目标端口号、UDP 数据长度以及 UDP 校验和(可选)。

- 计算 IP 首部校验和:构造 IP 首部,设置源 IP 地址、目标 IP 地址、协议类型等字段,并计算 IP 首部的校验和以确保传输过程中的完整性。

- 封装以太网帧头:将生成的 IP 包封装到以太网帧中,添加以太网帧头,包括目标 MAC 地址、源 MAC 地址以及类型字段(如 IPv4 类型为

0x0800)。- 添加 CRC32 校验:在以太网帧尾部附加 CRC32 校验码,用于接收端验证帧的完整性。

- 发送数据帧:通过 FPGA 的物理接口(如 GMII 或 RGMII),将以太网帧发送到网络中。

接收端: 在接收端,FPGA 的任务是对接收到的以太网帧进行逐层解析,提取有效数据并完成校验。具体流程如下:

- 接收以太网帧:从物理接口接收完整的以太网帧,并检查 CRC32 校验以确认帧的完整性。

- 解析以太网帧头:提取以太网帧头信息,包括目标 MAC 地址、源 MAC 地址和类型字段,判断是否为 IPv4 数据包。

- 解析 IP 首部:从数据包中提取 IP 首部,验证 IP 校验和,解析源 IP 地址、目标 IP 地址及协议类型,确认数据包的合法性。

- 解析 UDP 首部:进一步解析 UDP 首部,提取源端口号、目标端口号、数据长度等信息,并验证 UDP 校验和(如果存在)。

- 提取有效数据:从 UDP 数据段中提取应用层的有效载荷数据,并将其传递给后续处理模块或输出接口。

- 错误处理与丢弃:对于校验失败或格式不正确的数据包,进行错误标记或直接丢弃。

通过上述流程,FPGA 能够高效地实现以太网通信中的数据封装与解析,满足实时性和可靠性的要求,同时支持灵活的功能扩展和优化。

二、时序约束

时序约束与协议栈设计,深度融合

2.1 时序约束理论基础

在 FPGA 实现网络通信协议栈时,时序约束是保障设计正确性的核心要素:

- 关键术语:

- 建立时间(Tsu):时钟上升沿前数据需保持稳定的最短时间,确保寄存器正确采样。

- 保持时间(Th):时钟上升沿后数据需持续稳定的最短时间,避免采样错误。

- 时钟偏斜(Tskew):同一时钟域内不同路径时钟信号的到达时间差,可通过 BUFG 等原语优化。

- 亚稳态:当输入信号不满足 Tsu 或 Th 时,寄存器输出可能处于不确定状态,导致逻辑错误。

- 时间裕量与路径延迟:

- 建立时间裕量:实际到达时间与要求到达时间的差值,正数表示时序满足。

- 最大 / 最小延迟:最大延迟(T - Tsu)决定系统最高时钟频率,最小延迟(Th)需满足数据保持要求。

- 时序路径:确保数据路径延迟(TData = Tco + Tlogic)小于时钟周期与 Tsu 之和,即 T > Tco + Tlogic + Tsu。

2.2 时序约束在协议栈中的应用与优势

2.2.1 RGMII 接口的时序挑战与解决

RGMII 接口双沿传输数据时,对时钟与数据的相位关系要求严苛。通过时钟约束(如设置时钟周期和抖动容限)和 IO 约束(定义输入输出延时),确保数据在时钟沿稳定采样。例如,利用 IDDR 和 ODDR 原语实现数据同步时,需精确计算时钟偏斜,避免亚稳态风险,从而保障数据传输的准确性。

2.2.2 ARP 与 UDP 模块的时序优化

ARP 和 UDP 模块中,状态机控制数据包的构建与解析,涉及大量组合逻辑和寄存器操作。通过静态时序分析(STA)工具检查寄存器到寄存器路径的延时,优化关键路径逻辑,确保状态切换的及时性。以 ARP 请求发送过程为例,通过时序约束保证以太网帧头、ARP 数据和 CRC 校验的生成满足时钟周期要求,避免因逻辑延迟导致数据丢失。

2.2.3 整体系统的时序协同

协议栈各模块间的数据交互需遵循统一的时序规则。通过系统同步设计(如采用全局时钟),减少时钟域交叉带来的时序问题;结合动态时序分析(DTA)进行仿真验证,模拟不同激励下的时序表现,确保协议栈在复杂网络环境下也能稳定运行。

三、模块设计

模块设计与架构,以 RGMII、ARP、UDP 为核心的协同体系

3.1 RGMII 接口转换模块:数据格式的精准适配

- rgmii_to_gmii.v:作为顶层模块,实例化 rgmii_rx 和 rgmii_tx,将 RGMII 双沿数据转换为 GMII 单沿格式,为 ARP、UDP 模块提供统一接口。通过时序约束确保数据转换过程中时钟与数据的同步性,有效避免亚稳态。

- rgmii_rx.v:利用 BUFIO 和 BUFG 原语处理时钟信号,通过 IDDR 原语实现 RGMII 数据和控制信号的双单沿转换,确保数据准确采样。通过设置输入延时约束,进一步优化时钟与数据的相位关系。

- rgmii_tx.v:采用 ODDR 原语将 GMII 单沿数据转换为 RGMII 双沿格式,根据时钟沿生成对应控制信号,适配 PHY 芯片传输要求。通过输出延时约束,保证数据在时钟沿稳定输出。

3.2 ARP 协议模块:地址解析的全流程管控

- arp.v:ARP 顶层模块,整合 arp_tx、arp_rx 和 crc32_data,协调各模块信号,实现 ARP 协议完整功能。通过时序约束确保模块间数据交互的及时性和稳定性。

- arp_tx.v:基于状态机构建 ARP 请求 / 应答包,处理以太网帧头、ARP 数据字段填充,控制 CRC32 校验启动与结果插入。通过优化状态机逻辑,减少关键路径延时,严格满足时序要求。

- arp_rx.v:通过状态机解析接收数据,验证帧格式与 ARP 字段合法性,提取 IP-MAC 映射,输出有效数据与标志信号。利用静态时序分析检查数据解析路径,避免因逻辑复杂导致时序违例。

- crc32_data.v:为 ARP 和 UDP 模块提供 CRC32 校验服务,确保数据在链路层传输的完整性。通过时序约束保证校验计算与数据传输的同步性。

3.3 UDP 协议模块:快速数据传输的可靠保障

- udp_rx.v:利用状态机解析 UDP 数据包,验证以太网帧、IP 首部和 UDP 首部,提取有效数据,输出数据有效信号与接收完成标志。通过时序约束确保数据解析过程中各字段的校验及时完成,避免数据积压。

- udp_tx.v:基于状态机构建 UDP 数据包,计算 IP 首部校验和与 UDP 校验和,封装以太网帧头,结合 CRC32 校验后发送数据。通过优化校验和计算逻辑,减少关键路径延时,确保数据包按时发送。

3.4 辅助模块:功能强化与系统协调

- arp_ctrl.v:根据外部触发(如按键)和 ARP 接收状态,动态控制 ARP 发送策略,实现请求与应答的灵活调度。通过时序约束确保控制信号的响应速度,避免错过数据传输时机。

- en_ctrl.v:根据 ARP 和 UDP 发送使能信号,动态选择输出数据,避免协议冲突,保障数据有序传输。通过时序约束确保使能信号的切换无毛刺,防止数据丢失。

- key_fliter.v:对按键信号消抖处理,为 ARP 控制模块提供稳定触发信号,增强用户交互可靠。通过设置合适的延时参数,满足时序要求,避免误触发。

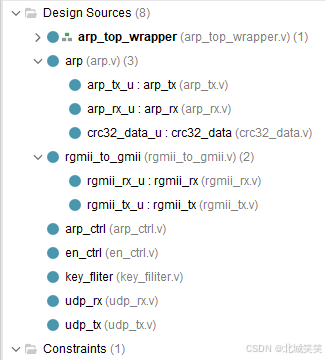

实际工程中的模块划分:

像图像中的 .v 等设计文件,实际上都是同级别组件,它们之间的上下级关系是通过写入代码后,软件会自动划分文件的上下级别。

在硬件设计中,通过Verilog实例化子模块,可将复杂设计分解为更小的部分,便于管理与复用。这种层次结构通过代码定义模块间的上下级关系,促进团队协作与设计验证。其实质是利用HDL实现设计的分层细化。

3.5 模块总结

参考以上,该工程一共12个Verilog文件,模块大致可以分为 4 大种类:

1. ARP,协议模块

- arp.v

- arp_tx.v

- arp_rx.v

- crc32_data.v

2. RGMII,接口转换模块

- rgmii_to_gmii.v

- rgmii_rx.v

- rgmii_tx.v

3. UDP,协议模块

- udp_rx.v

- udp_tx.v

4. 辅助模块

- arp_ctrl.v

- en_ctrl.v

- key_fliter.v

通过这种划分,每个大模块都能聚焦于特定的功能领域,不仅提高了代码的可读性和可维护性,还使得设计更加模块化和易于扩展。此外,这种结构也便于团队合作开发,不同成员可以专注于不同的模块而不会相互干扰。

四、注意事项

设计优势与问题解决

通过上述设计,该 FPGA 网络通信协议栈具备显著优势:

- 提升系统稳定性:严格的时序约束与分析,有效解决了 RGMII 接口数据同步、ARP/UDP 模块状态切换等场景下的亚稳态和时序违例问题,确保协议栈在高速运行时的可靠性。

- 优化资源利用:结合静态时序分析优化关键路径,减少不必要的逻辑延迟,在满足时序要求的同时降低 FPGA 资源消耗,提升设计效率。

- 增强兼容性:基于标准协议规范设计 ARP 和 UDP 模块,并通过时序约束确保与 PHY 芯片及其他网络设备的兼容性,避免因时序不匹配导致的通信故障。

- 支持高速通信:对 RGMII 接口和协议栈整体的时序优化,使其能够支持千兆以太网的数据传输速率,满足实时性应用对低延迟、高带宽的需求。

通过对 RGMII 接口、ARP 与 UDP 协议的深度剖析,结合时序约束理论进行模块设计,我们构建了一个高效、稳定的 FPGA 网络通信协议栈架构。这些设计不仅明确了各模块的功能边界,更确保了从物理层数据传输到协议层数据处理的高效协作。在下一篇文章中,我们将基于此架构,深入展开 Verilog 代码实现,将理论设计转化为可运行的数字电路,进一步探索协议栈优化与调试的实践策略。

五、更多操作

完整FPGA系列,请看

FPGA系列,文章目录![]() https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502

https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5502