vivado 时钟IP核(MMCM PLL)

CMT简介

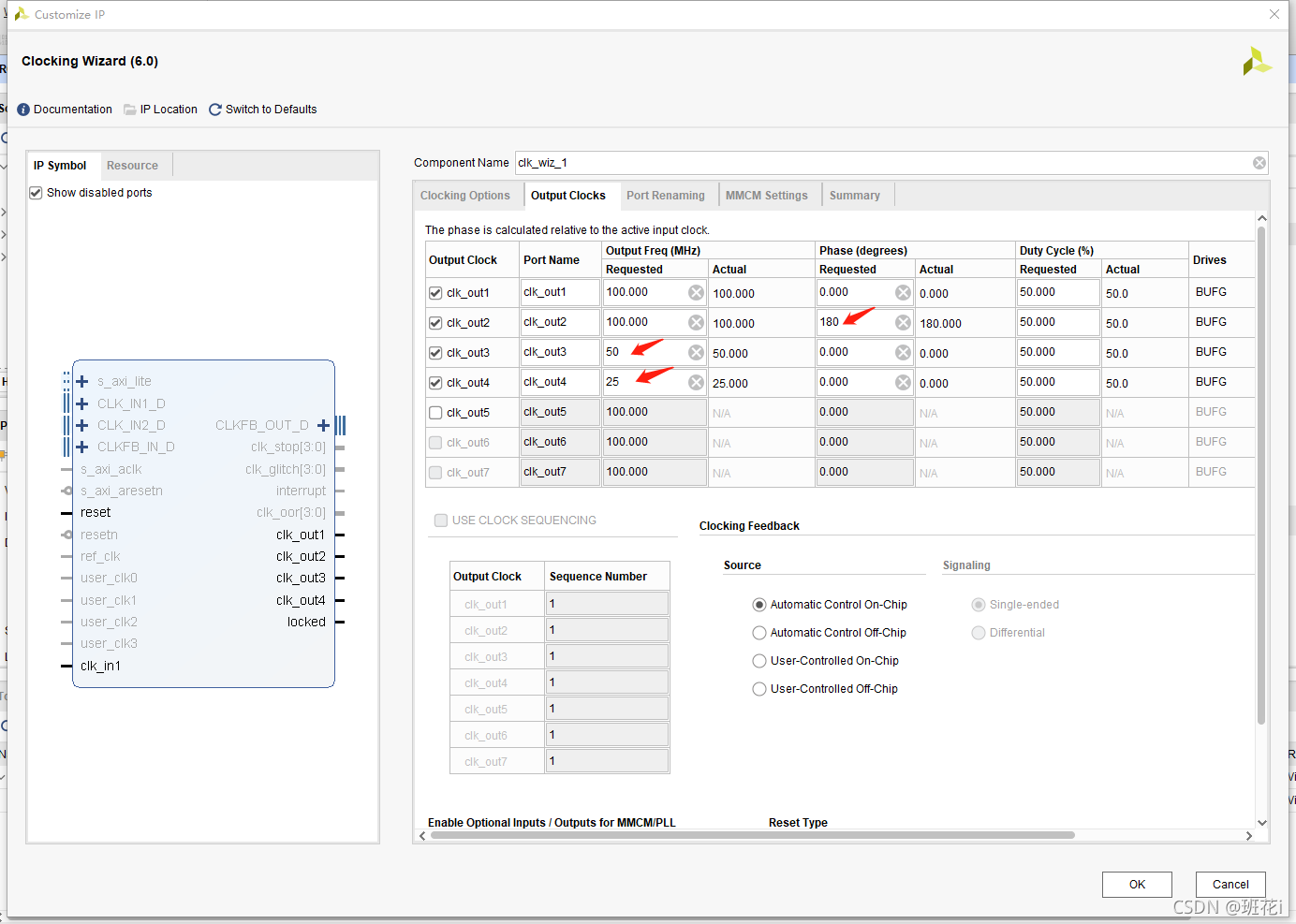

FPGA中时钟管理模块(CMT)包括PLL和MMCM,用于将时钟倍频(比如输入时钟25M,我们要产生50M时钟)、分频(在不影响系统功能的前提下,较低的工作时钟,能够降低系统功耗)、改变相位偏移或占空比等。

当需要上板时,由于板上晶振时钟固定,所以其他频率的时钟产生就要用到PLL或者MMCM。两者类似,MMCM可以完成PLL的所有功能外加一些高级功能。

时钟IP核的使用

创建和配置时钟IP核

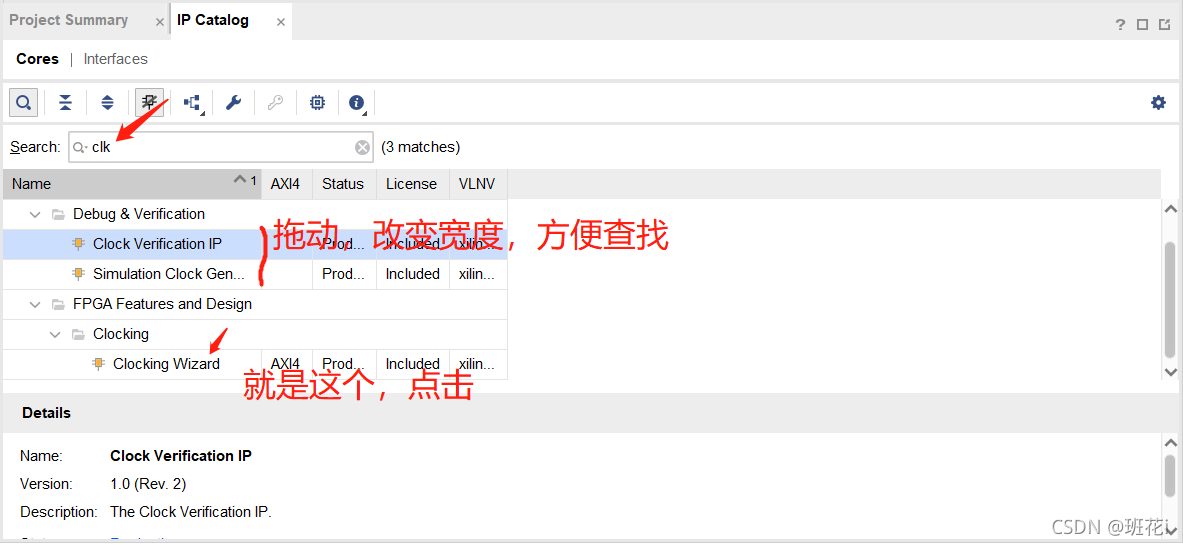

赛灵思提供的IP核在这儿

FPGA中时钟管理模块(CMT)包括PLL和MMCM,用于将时钟倍频(比如输入时钟25M,我们要产生50M时钟)、分频(在不影响系统功能的前提下,较低的工作时钟,能够降低系统功耗)、改变相位偏移或占空比等。

当需要上板时,由于板上晶振时钟固定,所以其他频率的时钟产生就要用到PLL或者MMCM。两者类似,MMCM可以完成PLL的所有功能外加一些高级功能。

赛灵思提供的IP核在这儿