FPGA_BD Block Design学习(一)

PS端开发流程详细步骤

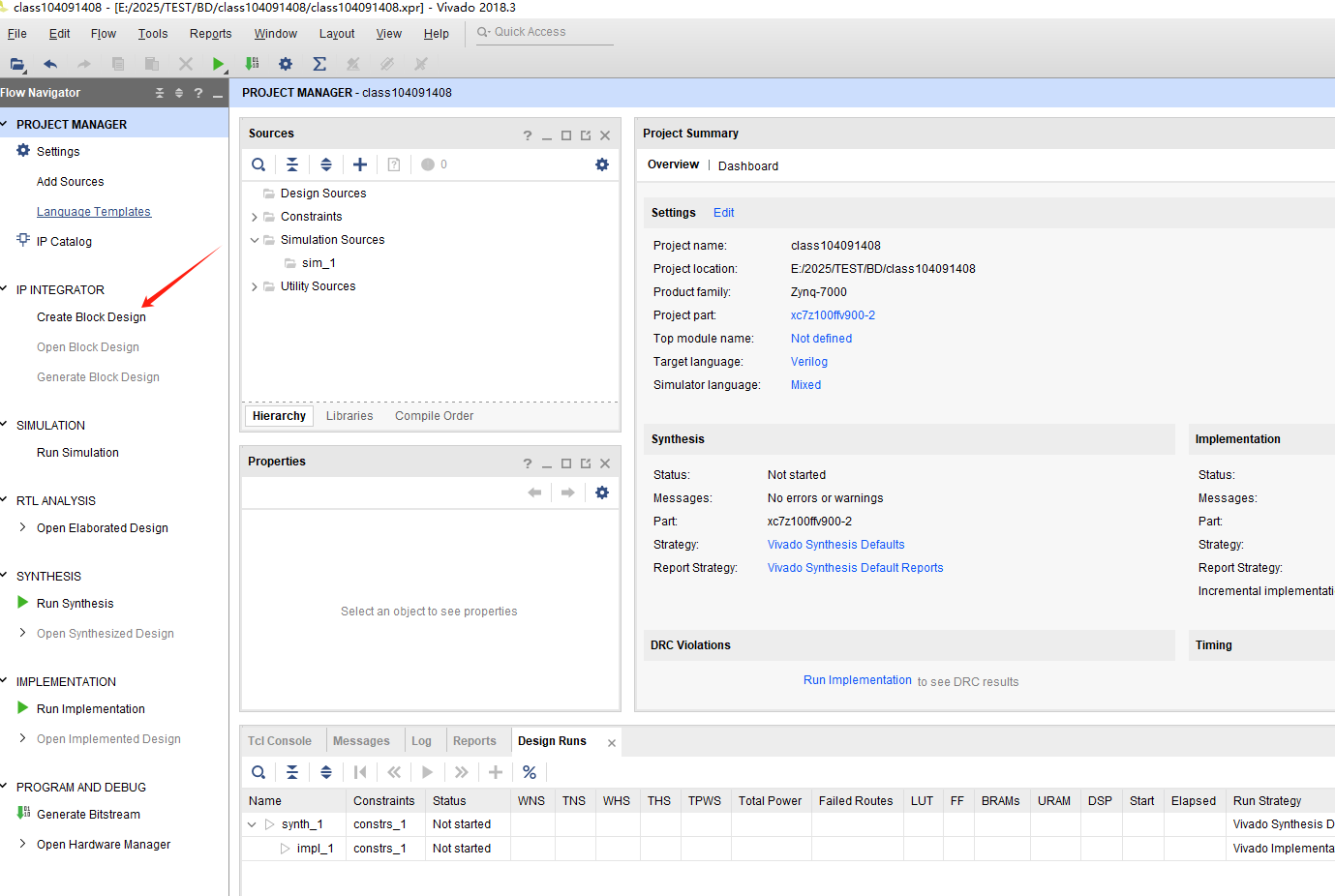

1.第一步:打开Vivado软件,创建或打开一个工程。

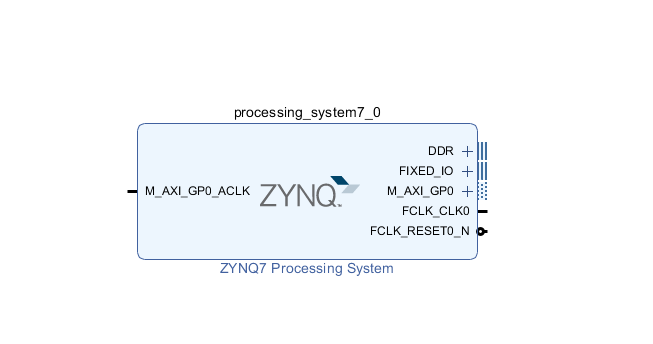

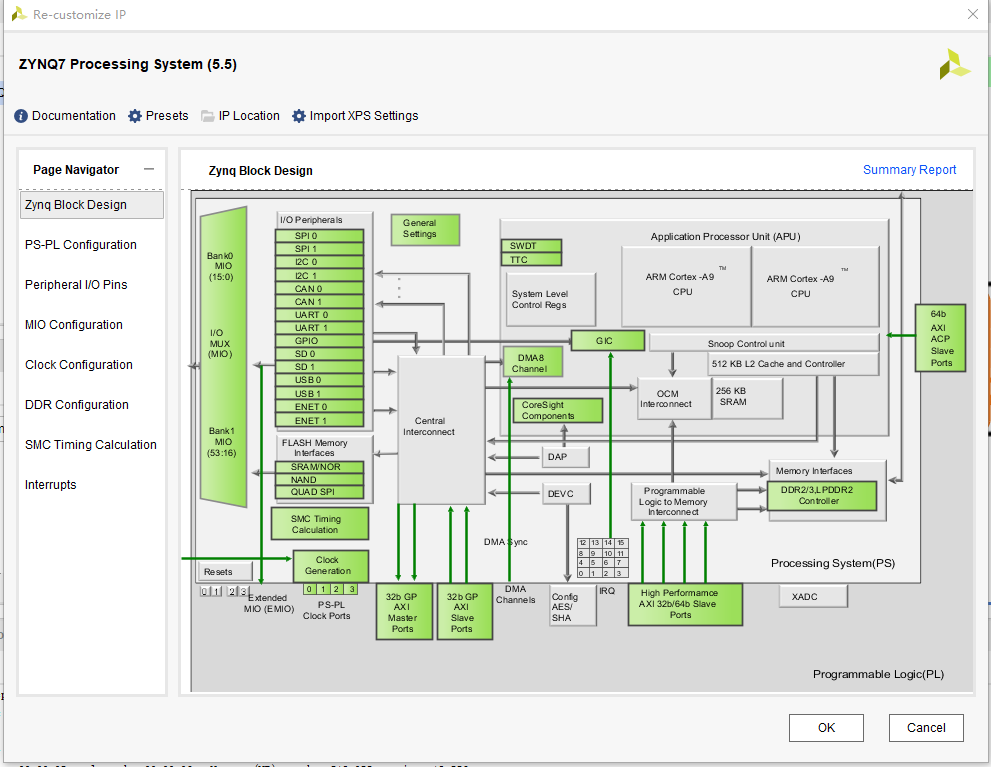

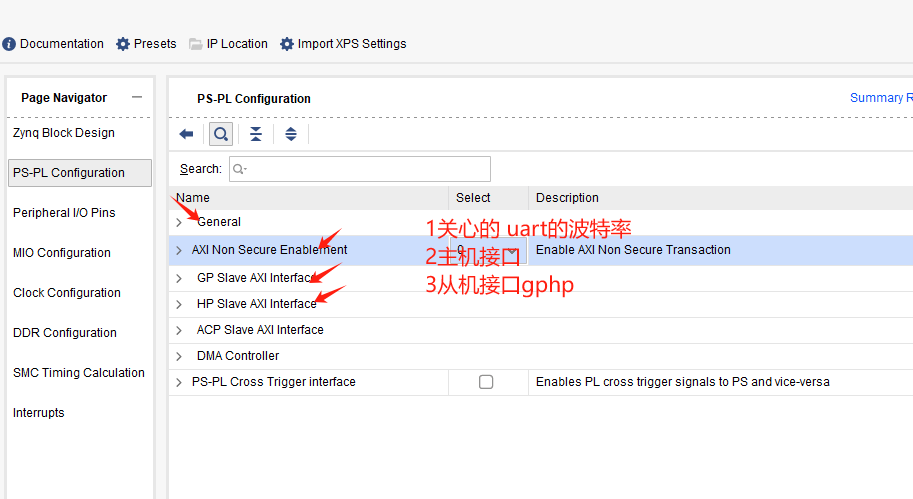

2.第二步:在Block Design中添加arm核心,并将其配置为IP核。

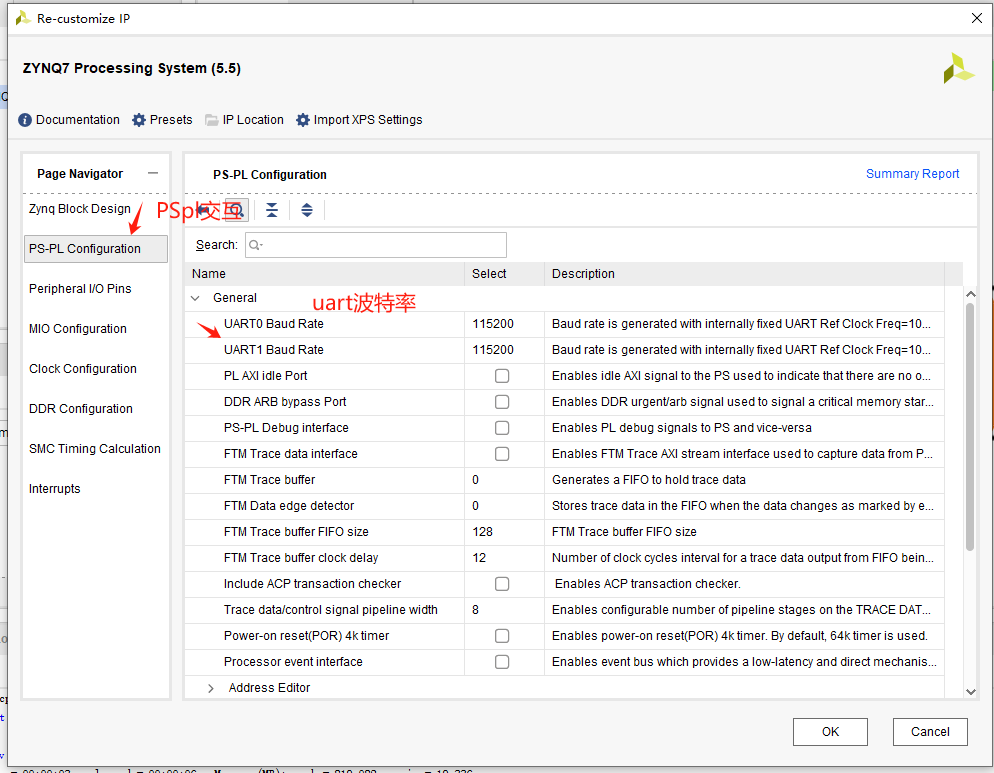

3.第三步:配置arm核心的外设信息,如DDR接口、时钟频率、UART接口等。

4.第四步:完成Block Design中的模块互联,生成PL端的比特流。 5.第五步:导出PS端的硬件信息,包括arm IP核的外设、速度、引脚和地址等信息。

BD的设计

1创建bd

2 资源介绍

2.1 最小系统

需要有ddr以及uart和时钟

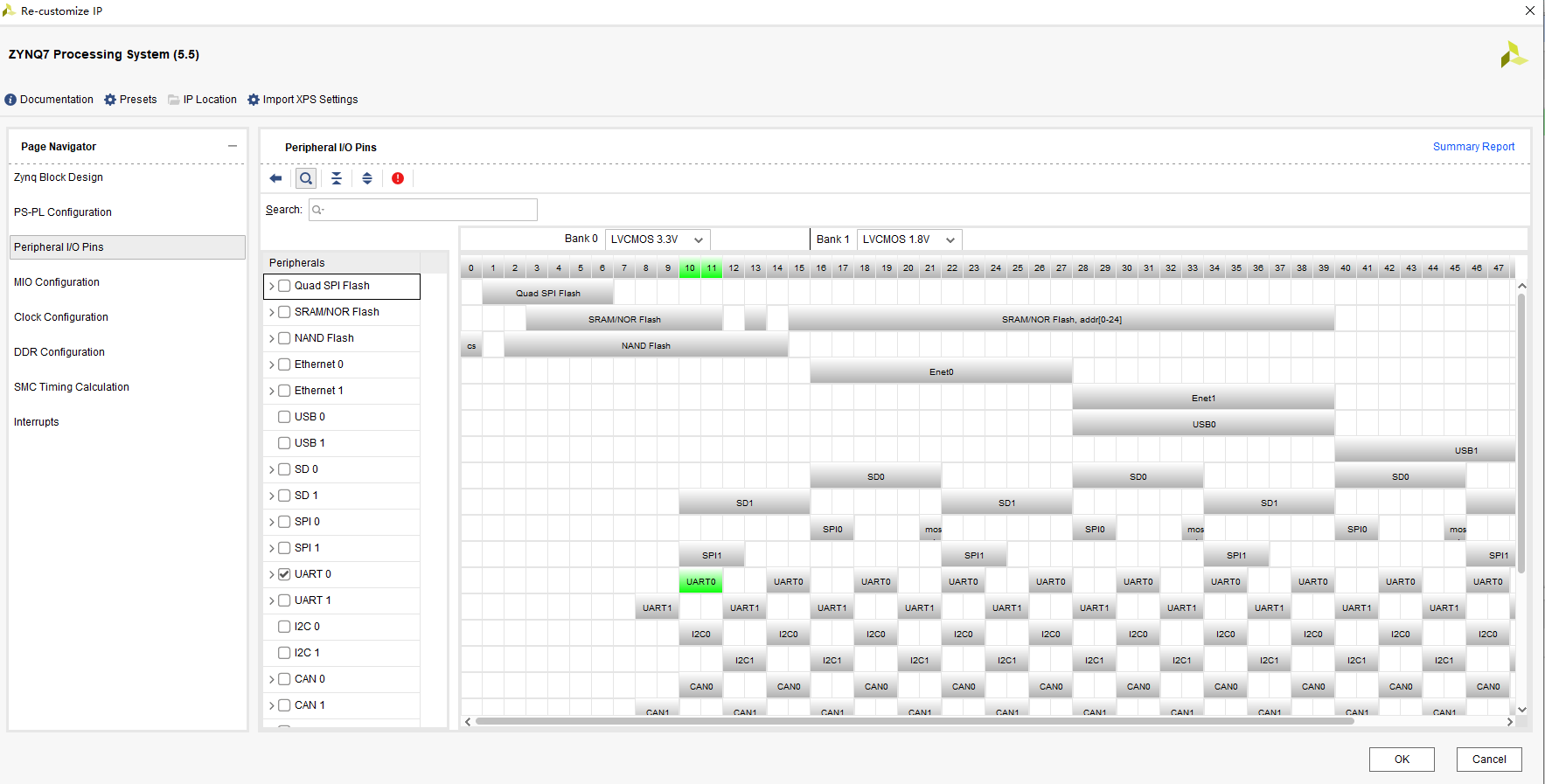

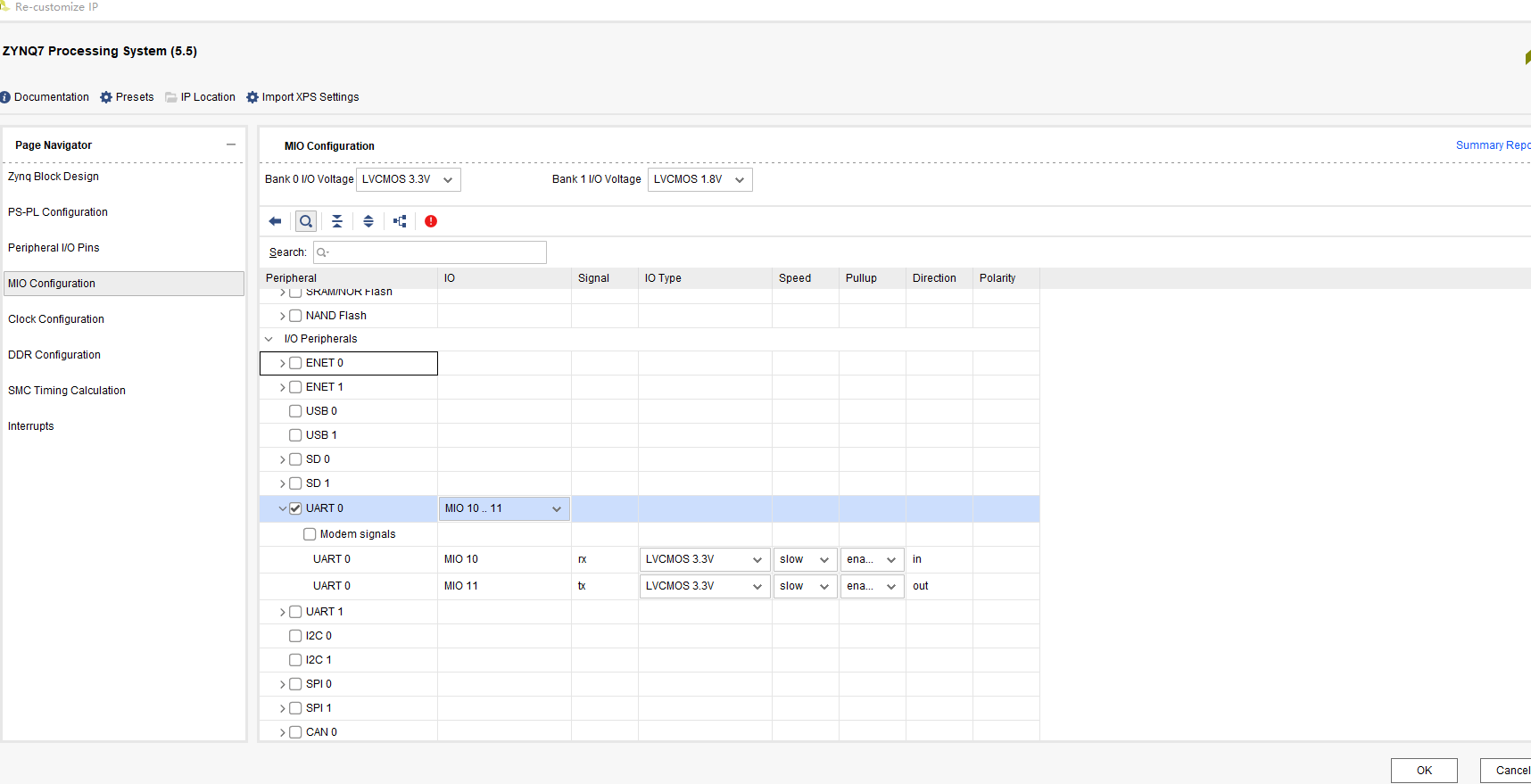

配置外设io口,这里就是zynq的管脚规定好的,根据原理图用哪个个勾选哪一个。

对外设uart的配置可以看到配置好的

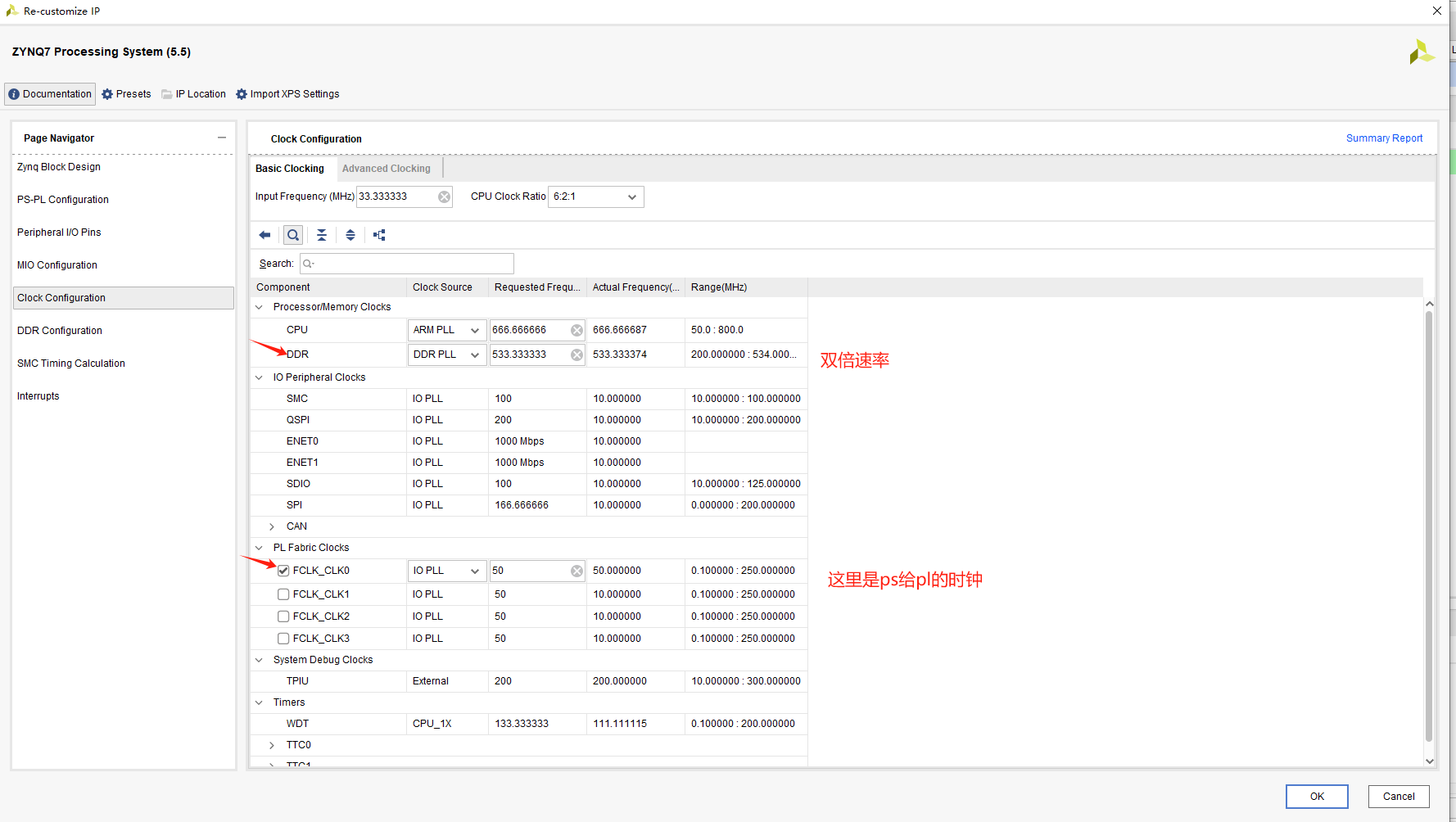

时钟的配置

ddr是双倍的

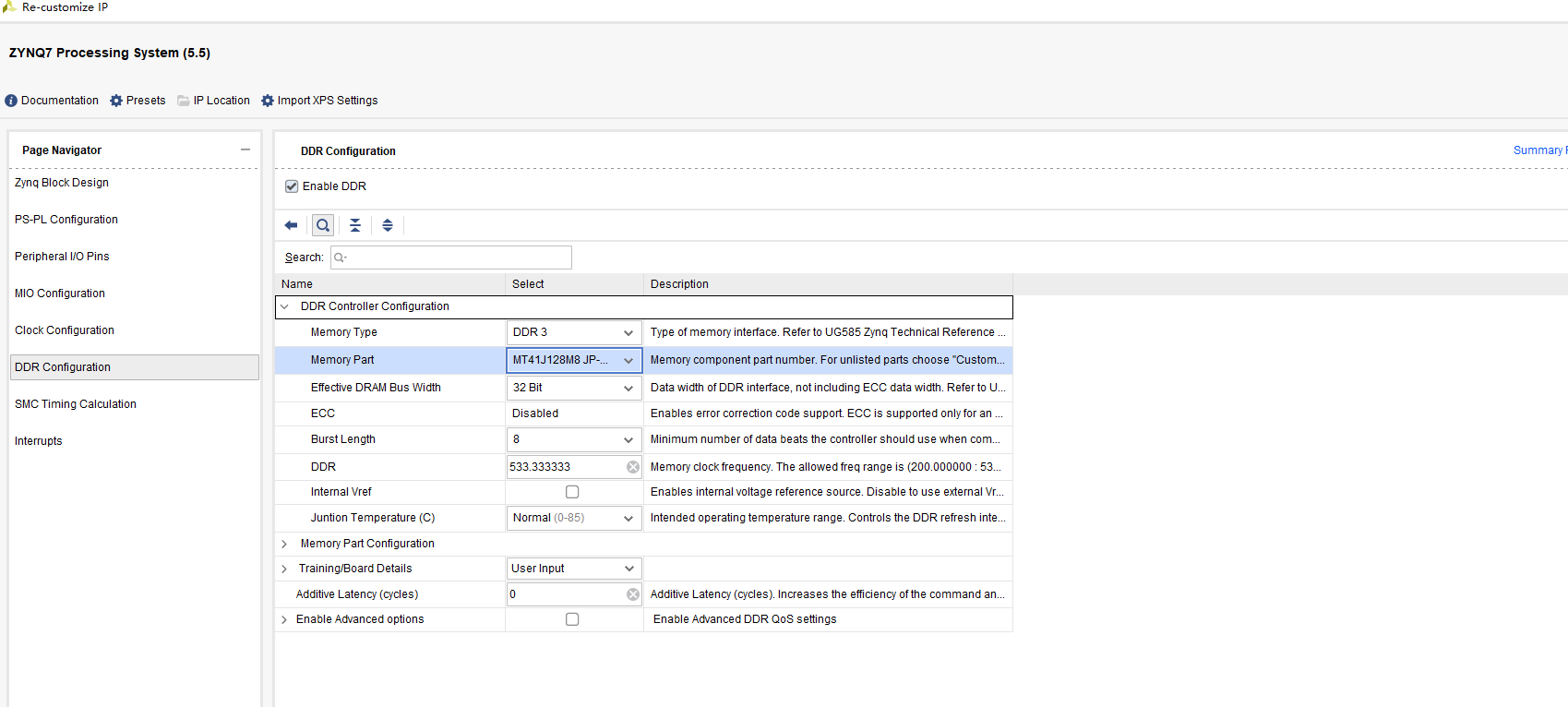

ddr的配置

如果一片是16位有两片的话那么位宽就选32

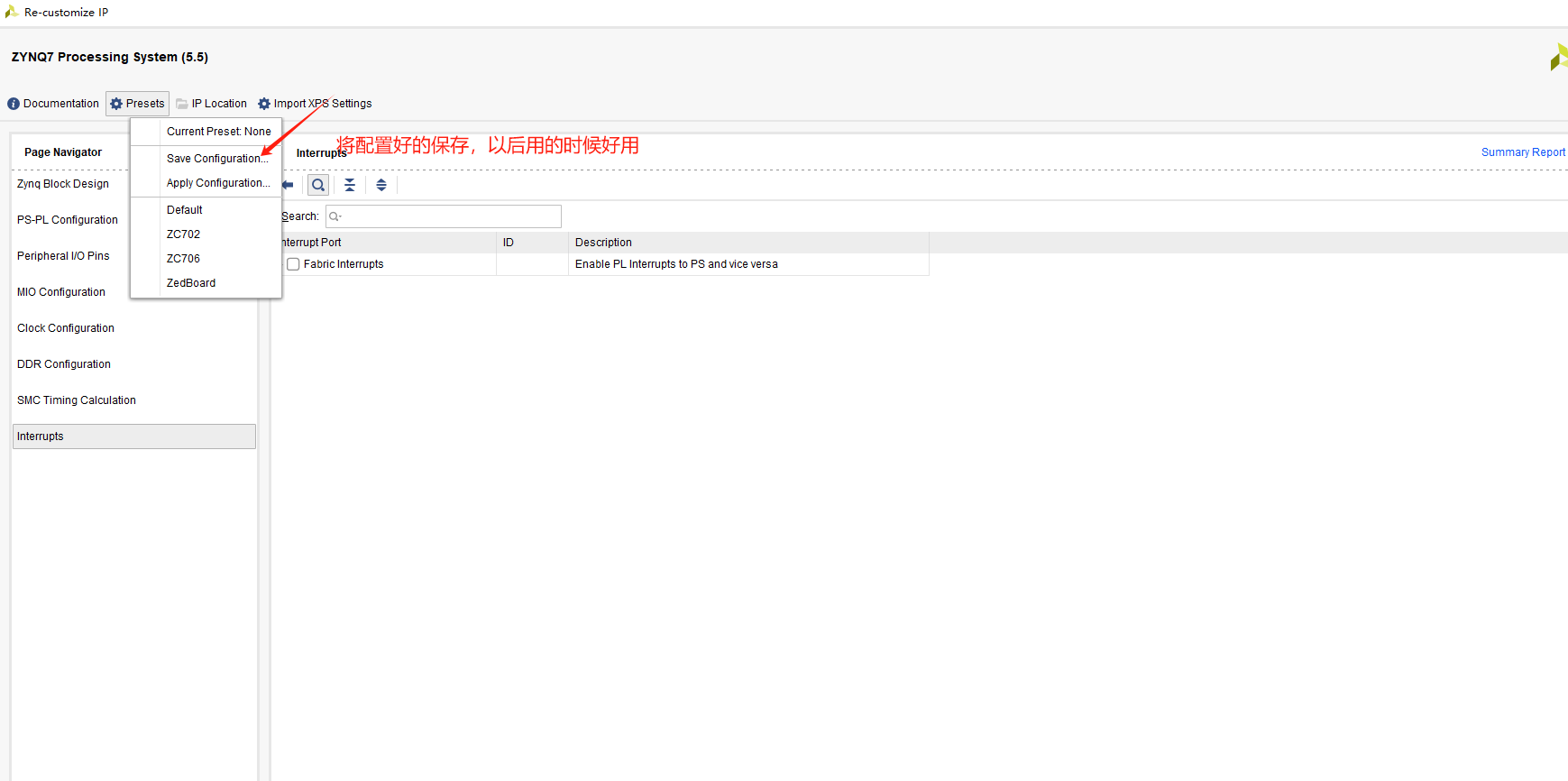

保存zyaqip

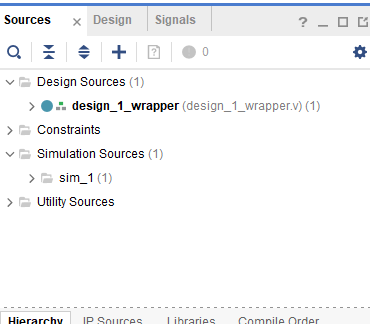

打包Generate output products 然后Create HDL wrapper

打包好后,以及自动分配好约束文件生成bit文件即可