模拟集成电路设计与仿真 : Mismatch

前情提要

- 此為作者針對 mismatch ,進行資料統整,以便日後查詢

原理

1. Mismatch (失配)

- random offset

- 靜態消除 : trimming

- 動態消除 : auto zero ,chopping

- CMRR

- linearity

- 理想差動對只有奇次諧波,沒有偶次諧波,但 mismatch 會引入殘存的偶次諧波

- PSRR

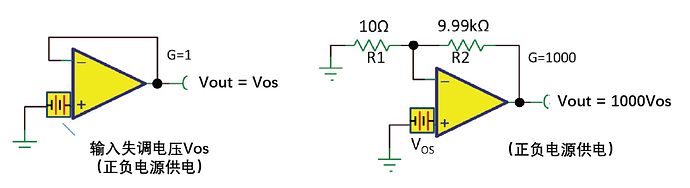

2. Input Offset Voltage (輸入失調電壓)

- 和雜訊分析一樣,整理成輸入電壓源

- CSDN : Razavi noise

- (negative feedback) closed loop gain 越大,

對 output voltage 影響越大

- open loop gain 無限大,(negative feedback) closed loop gain

- open loop gain 無限大,(negative feedback) closed loop gain

圖片來源 : 运放专题:运放输入失调电压_运放失调电压-CSDN博客

圖片來源 : https://www.digikey.cn/zh/forum/t/topic/1344

2.1 System Offset (系統失調)

- 即便沒有 mismatch ,只要電路架構不對稱就會存在,ex. differential input to single output

- 使用 cascode 減緩 (降低 channel length modulation)

- 改用 differential input to differential output 完全避開

2.2 Random Offset (隨機失調)

- mismatch 造成 (single output & differential output 都有)