第九章 VGA显示矩阵

FPGA至简设计实例

目录

FPGA至简设计实例

前言

一、项目背景

二、设计目标

三、设计实现

1. 顶层接口

2. 信号设计

四、总代码

五、综合上板

总结

前言

一、项目背景

VGA的显示背景与原理在上一章“VGA显示颜色”的案例分享中已经有了比较详细的解释,这 里就不再进行展开讲解,如果还有不理解的读者朋友可以回到上一章中的项目背景部分进行阅读学习

二、设计目标

上一章实现了VGA显示颜色的设计,这一章中将进行更高一级的设计学习——VGA显示矩阵图 像。按照至简设计法的思路,在进行设计之前首先明确设计目标。明确了设计目标后,后续的每一步 操作都是围绕设计目标进行展开。如果没有牢记设计目标就开始动手进行实践操作,最终的作品也是 东拼西凑的产物,一旦在设计过程中出现了问题就需要花费大量的精力进行寻找修复。建议初学者在 开始学习时就养成良好的设计习惯,才能在后续的职业生涯中受益。

本设计需要通过VGA连接线将显示器和开发板进行连接,FPGA在连接成功后产生640*480分 辨率,刷新频率为60Hz的VGA时序,使得显示器产生显示一幅完整的矩阵图像。这幅矩阵图像即 为显示屏边缘上显示一个宽为20像素的红色边框,在屏幕的中央显示一个长为150像素、高为100 像素的绿色矩形。

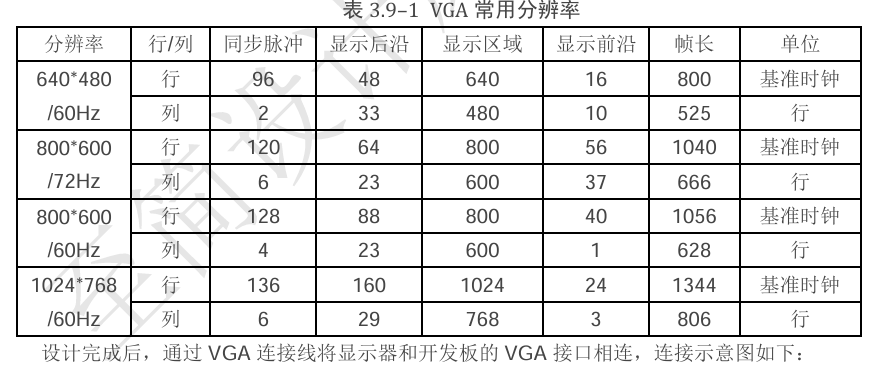

显示器一般都具有分辨率自适应功能,无须设置就能识别不同分辨率的图像。本设计的相应参数 参见表3.9-1中的第一行。其中,行的单位为“基准时钟”,即频率为25MHz、周期为40ns的时钟, 列的单位则为“行”,请读者朋友们一定要注意区分。

三、设计实现

1. 顶层接口

新建目录:D:\mdy_book\rec_exec1,在该目录中新建一个名为rec_exec1.v的文件。用GVIM 打开后开始编写代码。这里再次强调,初学者一定要按照本书提供的文件路径以及文件名进行设置, 避免后面出现未知错误。

分析设计目标可知,本设计中FPGA产生VGA时序,即控制VGA_R4~R0、VGA_G5~G0、V GA_B4~B0、VGA_HSYNC 和VGA_VSYNC,从而使显示器呈红色、绿色的矩阵显示。其中,FPG A可根据时序产生高低电平从而控制VGA_HSYNC和VGA_VSYNC。而颜色数据,由于本设计需要 的显示的颜色数据是固定的红色和绿色,可通过 FPGA 自身产生而不需要外部输入图像的数据。那 么在FPGA的工程设计中可以定义输出信号hys表示行同步,定义输出信号vys表示场同步,定义 一个16位的信号lcd_rgb进行RGB输出,其中lcd_rgb[15:11]表示VGA_R4~0、lcd_rgb[10:5]表示 VGA_G5~0、lcd_rgb[4:0]表示 VGA_B4~0。当然,本设计中还需要时钟信号clk和复位信号rst_n来 进行工程控制。

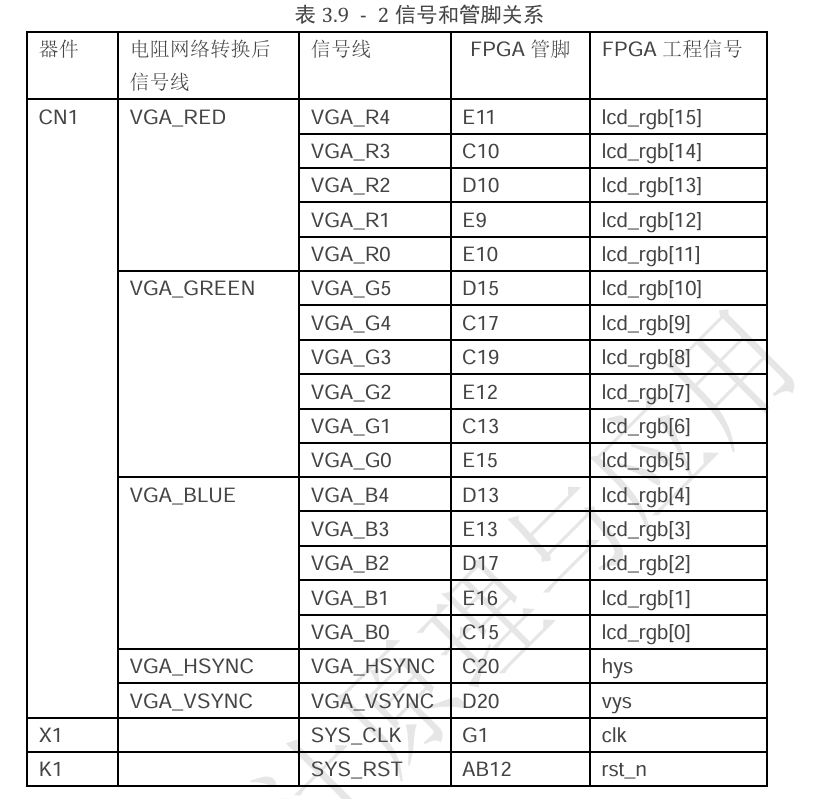

综上所述,本工程需要五个信号:时钟信号clk,复位信号rst_n,场同步信号vys、行同步信号hys和RGB输出信号lcd_rgb。信号和硬件的对应关系如下表所示。