上海手机网站开发价格seo百度首页排名业务

文章目录

- 一、关于IP软核的使用方法

- 1.PLL

- 2.RAM

- 3.FIFO

- 二、数字频率合成设计制作一个波形发生器

- 1.正弦波

- 2.方波

- 3.DDS

一、关于IP软核的使用方法

1.PLL

PLL全称Phase Locked Loop,也就是锁相环,是一种反馈控制电路。PLL对时钟网络进行系统级的时钟管理和偏移控制,具有时钟倍频、分频、相位偏移和可编程占空比的功能。

PLL是FPGA重要的资源,不同FPGA的PLL 是不一样。以我们开发板的Cyclone IV为例,它有两个PLL,每个PLL可以提供5路输出。

PLL 的时钟输入可以是PLL 所在的 Bank 的时钟输入管脚或者其他 PLL 的输出,FPGA 内部产生的信号不能驱动PLL。Cyclone IV PLL 产生的时钟可以为单端时钟信号或差分时钟信号, 可以通过GCLK 网络直接驱动 FPGA 外部的 IO 口。

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效output c0 ,output c1 ,output c2 ,output c3 ,output locked ,

);

// //PLLpll pll_inst (.areset ( ~rst_n ),//IP复位高有效.inclk0 ( clk ),//输入时钟.c0 ( c0 ),//输出时钟.c1 ( c1 ),//输出时钟.c2 ( c2 ),//输出时钟.c3 ( c3 ),//输出时钟.locked ( locked ) //时钟输出锁--锁定不稳定时钟输出);

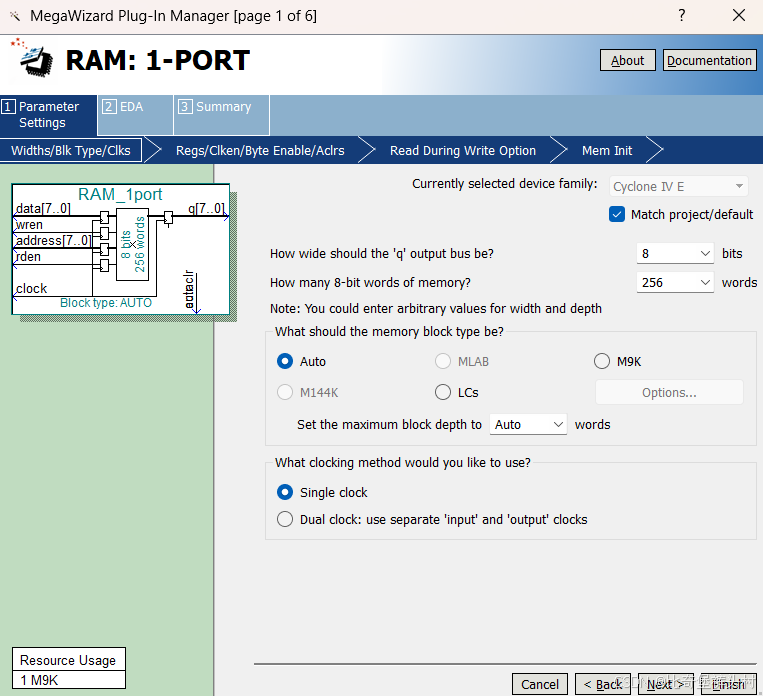

endmodule2.RAM

RAM介绍:

RAM的英文全称是Random Access Memory,即随机存取存储器,它可以随时把数据写入任一指定地址的存储单元,也可以随时从任一指定地址中读出数据。其读写速度是由时钟频率决定的。RAM主要用来存放程序及程序执行过程中产生的中间数据、运算结果等。其特点适合双向交换数据。

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效input rden ,input wren ,input [7:0] address ,input [7:0] data ,output [7:0] q

);//RAM_1portRAM_1port RAM_1port_inst (.aclr ( ~rst_n ),.address ( address ),.clock ( clk ),.data ( data ),.rden ( rden ),.wren ( wren ),.q ( q ));

endmodule3.FIFO

FIFO的英文全称是First In First Out,即先进先出。FPGA使用的FIFO一般指的是对数据的存储具有先进先出特性的一个缓存器,常被用于数据的缓存或者高速异步数据的交互,也即所谓的跨时钟域信号传递。

它与FPGA内部的RAM和ROM的区别是没有外部读写地址线,采取顺序写入数据,顺序读出数据的方式,使用起来简单方便,由此带来的缺点就是不能像RAM和ROM那样可以由地址线决定读取或写入某个指定的地址。

module test_IP(input clk ,//时钟信号input rst_n ,//上电复位低有效input [7:0] data ,input rdreq ,input wrreq ,output empty ,output full ,output [7:0] q ,output [7:0] usedw );// //FIFOfifo fifo_inst (.aclr ( ~rst_n ),.clock ( clk ),.data ( data ),.rdreq ( rdreq ),.wrreq ( wrreq ),.empty ( empty ),.full ( full ),.q ( q ),.usedw ( usedw ));

endmodule二、数字频率合成设计制作一个波形发生器

1.正弦波

module phase_accumulator (input clk,input [31:0] freq_word,output reg [31:0] phase

);

always @(posedge clk) beginphase <= phase + freq_word;

end

endmodule

2.方波

module square_wave (input [31:0] phase,output reg wave_out

);

always @(phase) beginwave_out = phase[31]; // 取最高位作为方波输出

end

endmodule

3.DDS

module dds_generator (input clk,input [31:0] freq_word,output [11:0] sine_out,output square_out

);

wire [31:0] phase;

phase_accumulator acc (.clk(clk),.freq_word(freq_word),.phase(phase)

);

// 正弦波ROM(实例化IP核)

sine_rom rom (.address(phase[31:22]), // 取高10位作为ROM地址.clock(clk),.q(sine_out)

);

square_wave sq (.phase(phase),.wave_out(square_out)

);

endmodule