S32K144入门笔记(十一):PDB的解读

目录

1. 概述

1.1 输入触发源连接

1.2 背靠背链路

1.3 脉冲输出使能寄存器的实现

1.3 PDB特性

1.4 PDB的操作

2. 功能描述

2.1 PDB预触发和触发输出

2.2 PDB触发输入源选择

2.3 脉冲输出

2.4 更新延迟寄存器

2.5 中断与DMA

2.6 使用预分频器和乘法因子对时序分辨率的影响

1. 概述

PDB是一个S32K144的延时触发模块,每个芯片上的PDB有两个模块:PDB0和PDB1,每个模块有两个插槽(也可以认为是通道,那么S32K144共有4个通道,每个PDB模块有2个通道),每个通道由1个触发源、1个脉冲输出和8个预触发器组成。根据笔者对于官网手册的理解,这个PDB模块与ADC模块有着对应的关系,那么这个模块的设计初衷最重要的一点就是让ADC的使用更加灵活(最新版的用户手册把PDB也归类为模拟模块,可见它的主要用处就是与ADC联动,提供更加灵活的功能)。

1.1 输入触发源连接

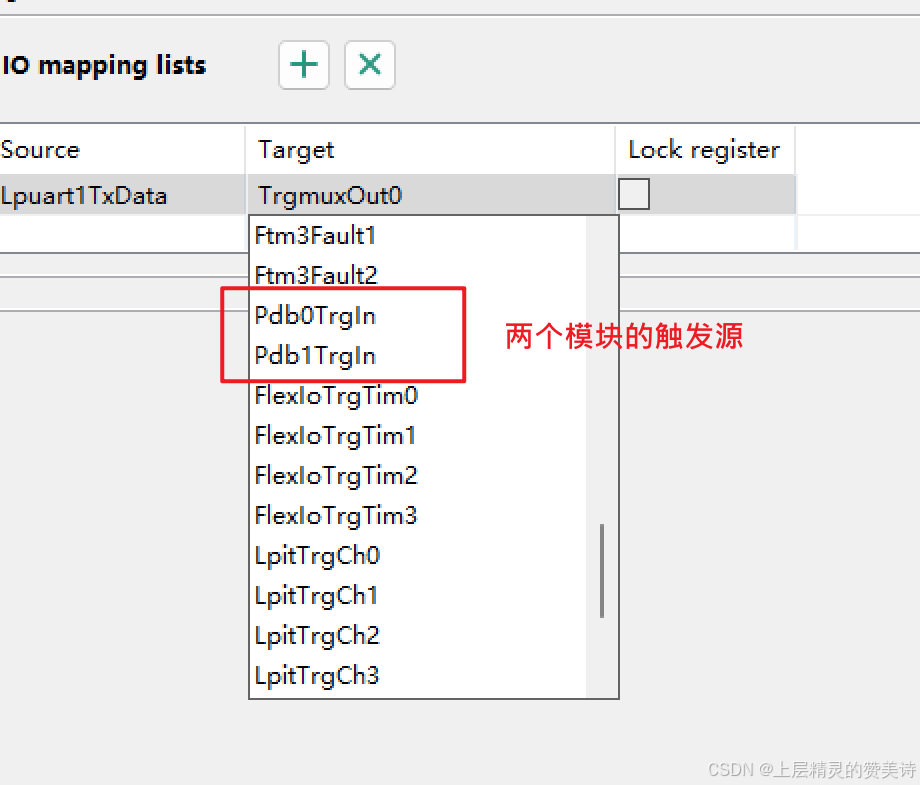

在S32K144芯片中,PDB 触发源选择通过 TRGMUX 模块实现(即PDB的触发源来源于TRGMUX的输出)。对于每个 PDB 单元,只有一个来自 TRGMUX 的触发输入,但它支持不同的触发源。此时,PDB内部的内部触发复用器不再可用。关于触发源的数量可以在配置工具中得到证实,如图1所示。

表1为PDB与ADC和TRGMUX的相互关联信息。

| PDB的触发输出 | 相互关联 |

|---|---|

| 通道0触发 | 同时连接ADC和TRGMUX |

| 通道1触发 | 连接ADC |

| 通道2触发 | 连接ADC |

| 通道3触发 | 连接ADC |

| 预触发 | 连接TRGMUX |

除了特定的PDB-ADC触发方式之外,PDB通道也可以通过TRGMUX触发源的方式与除了ADC以外其他外设模块连接。现表1中提及的4个通道是S32K148的通道数,对于S32K144仅有通道0和通道1(吐槽一下,NXP应该给表格做个批注)。

1.2 背靠背链路

背靠背操作使得 ADC 转换完成能够触发下一个 PDB 通道的预触发和触发输出(通过分析字面意思,大概是利用这个背靠背功能实现ADC的多通道的触发)。

PDB的背靠背操作确认连接是基于 SIM_CHIPCTL[PDB_BB_SEL]位设置来实现的。PDB背靠背操作在每个PDB的所有通道上都得到支持。每个 PDB 的通道 0 以及通道 0 和通道 1 的累积,支持形成一个链路。

PDB的背靠背模式提供了一个非常灵活的通道内和跨通道的链路模式,可以通过配置寄存器的三个位实现(实际上S32K14x系列只有一个可配置位域,只有S32K14xW的三个位域可用,而S32K11x系列则三个位域均为保留位),见表2。

| PDB_BB_SE_2/ SIM_CHIPCTL[23] | PDB_BB_SE_1/ SIM_CHIPCTL[22] | PDB_BB_SE/ SIM_CHIPCTL[13] | 描述 |

| 0 | 0 | 0 | PDB0和PDB1的通道0的通道内独立链路 |

| 0 | 0 | 1 | PDB0和PDB1的通道0与通道0的链路 |

| 0 | 1 | X | PDB0的通道0与通道1的跨通道链路 |

| 1 | 0 | X | PDB1的通道0与通道1的跨通道链路 |

| 1 | 1 | X | PDB0的通道0与通道1以及PDB1的通道0与通道1同时链路 |

对于不同的器件,背靠背模式的可能配置有些不同,如表3所示。

| 器件 | 支持的配置 |

| S32K11x | 不支持链路,相关寄存器位保留 |

| S32K14x | 支持PB0与PB1的通道0之间的链路 PDB_BB_SEL可配置 PDB_BB_SEL_1和PDB_BB_SEL_2保留 |

| S32K14xW | 支持PB0与PB1的通道0之间的链路 支持PB0的通道0和通道1之间的链路以及PB1的独立链路 支持PDB0 和 PDB1 的 CH0 - CH1 同时链路 PDB_BB_SEL、PDB_BB_SEL_1以及PDB_BB_SEL_2可配置 |

由此可知,S32K144实际上只支持两种链路模式,即:

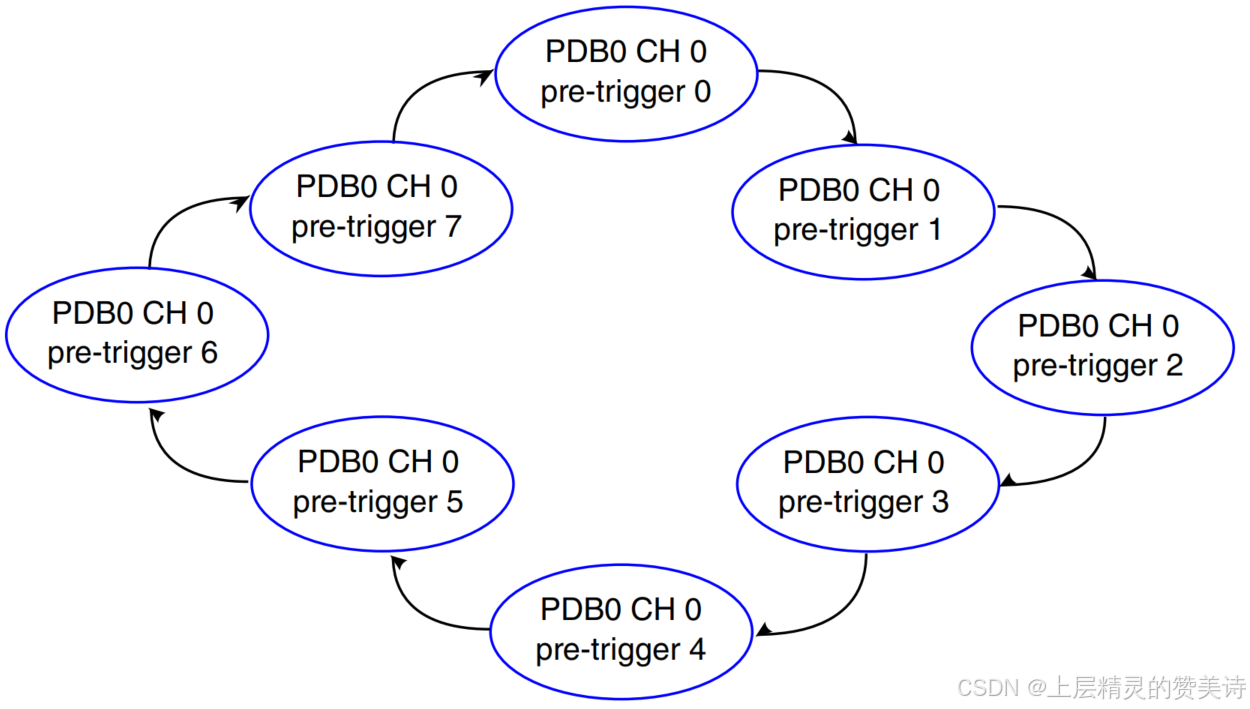

当SIM_CHIPCTL[PDB_BB_SEL]设置为0时,PDB背对背操作确认连接在每个PDB单元内以环的形式实现。图2为PDB0内部背靠背环路的示意图。

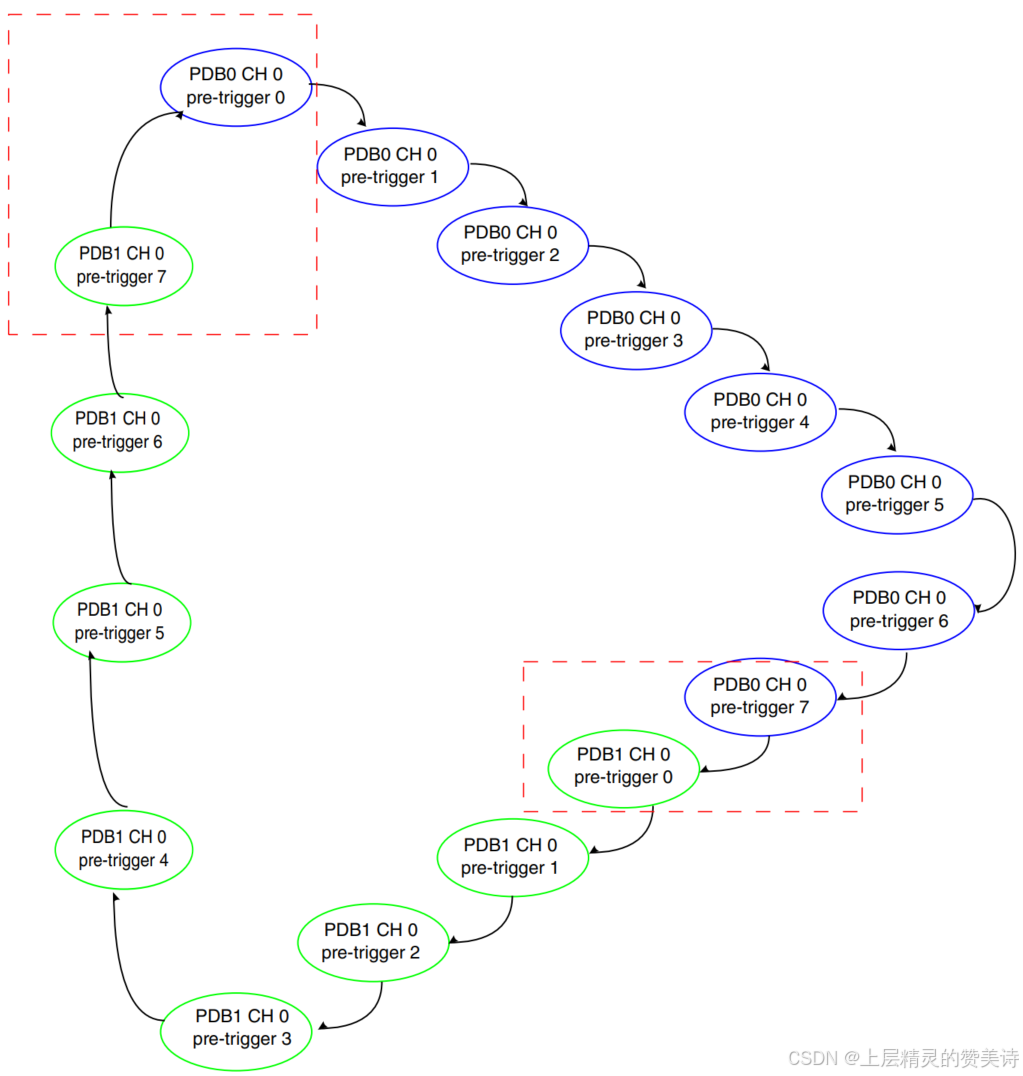

当SIM_CHIPCTL[PDB_BB_SEL]设置为1时,PDB背对背操作是将所有PDB单元的通道0作为一个环来实现的。示意图如图3所示。

应用程序代码可以设置 PDBx_CHnC1[BB] 位,以将 PDB 预触发器配置为单个链路或多个链路。

链路的起始预触发信号应由 PDB 提供(例如通过设置 CHnDLY1 和 CHnC1[EN] 位),同时需清除 PDBx_CHnC1[BB] 位。

1.3 脉冲输出使能寄存器的实现

每个PDB模块将包含一个脉冲输出通道。该脉冲输出通道连接到 TRGMUX,从而可灵活配置为任意比较器(CMP)模块的采样窗口。

1.3 PDB特性

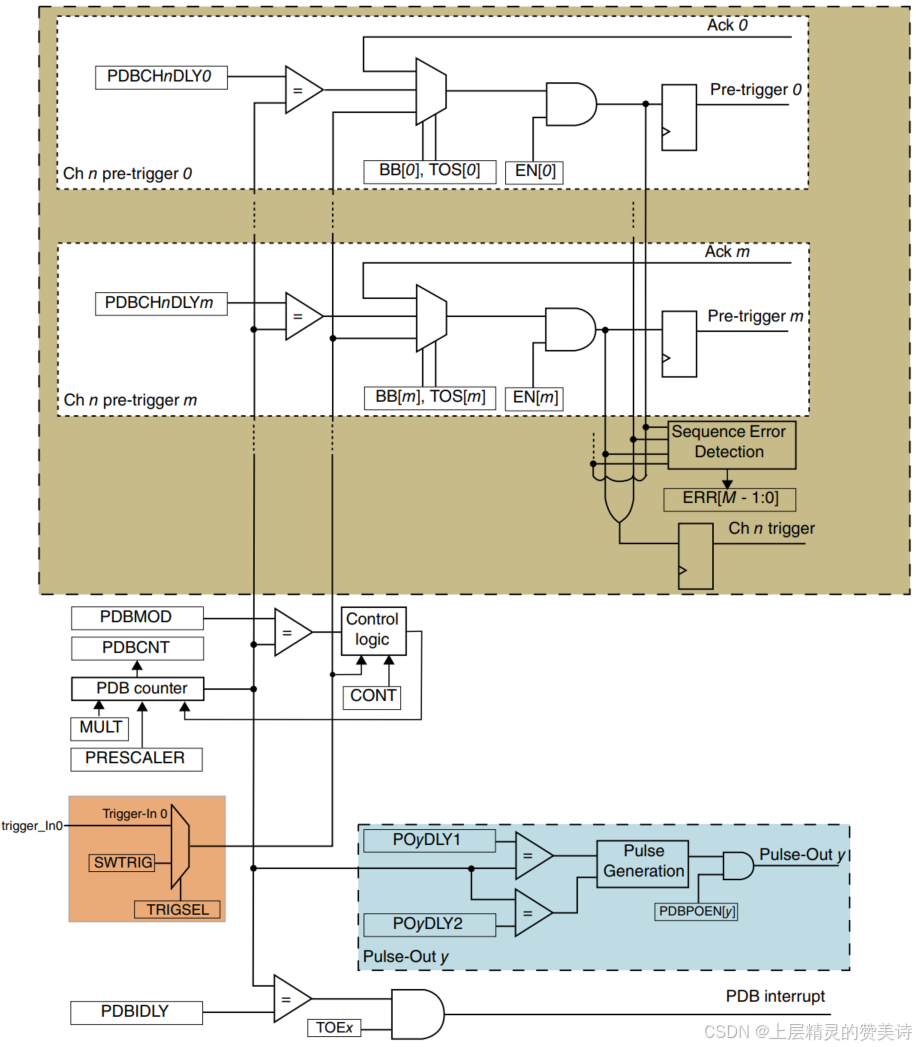

可编程延迟块(PDB)从内部或外部触发,或可编程间隔时钟,为 ADC 的硬件触发输入提供可控延迟。PDB 可以选择提供脉冲输出(Pulse-Outs),这些脉冲输出在 CMP 块中用作采样窗口。

- 最多2个触发输入源和一个软件触发源

- 多达8个可配置的PDB通道用于ADC硬件触发

- 一个PDB通道与一个ADC相关联(PDB0-ADC0,PDB1-ADC1)

- 每个PDB通道有一个用于ADC硬件触发的触发输出和多达8个用于ADC触发选择的预触发输出

- 触发器输出可以独立使能或禁用

- 每个预触发输出包含一个16位延迟寄存器

- 预触发输出延迟寄存器可被旁路

- 可以配置为单次或连续模式

- 可选的背靠背模式操作,使ADC转换完成以触发下一个PDB通道

- 一个可编程的延迟中断

- 一个序列错误中断

- 每个预触发器拥有一个通道标志和一个序列错误标志

- DMA支持

- 多达8个脉冲输出

- 脉冲输出可以独立的使能和禁用

- 可编程的脉冲宽度

PDB模块框图如图4。

1.4 PDB的操作

PDB ADC触发操作以下列模式操作:

- 禁用:如果PDB未处于旁路模式的背靠背操作,计数器关闭,所有预触发和触发输出均为低。

- Debug:当处理器处于调试模式时,计数器暂停

- 启用单次触发:计数器在接收到所选触发输入源的正边沿时被启用并在计数为零时重新启动,或者选择软件触发并将 1 写入 SC[SWTRIG]。在每个 PDB 通道中,启用的预触发在每个触发输入事件时断言一次。只要有任何预触发被断言,触发输出就会断言。

- 启用连续模式:计数器被启用并在计数为零时重新启动。当计数达到模数寄存器中指定的值时,计数器再次翻转回零,并重新开始计数。这样,单个触发输入事件就会产生连续的预触发/触发输出流。

- 启用旁路模式:在所选触发输入源出现正边沿后,或选择软件触发并将 1 写入 SC[SWTRIG]后,预触发和触发输出会立即断言,即延迟寄存器被旁路。可以旁路任意一个或多个延迟寄存器;因此,此模式可与单次触发或连续模式结合使用。

2. 功能描述

2.1 PDB预触发和触发输出

PDB包含一个计数器,其输出会与多个不同的数字值进行比较。若 PDB 已启用,触发输入事件将复位计数器并使其开始计数。触发输入事件的定义为:在选定的触发输入源上检测到上升沿,或若选择软件触发且向软件触发位(SC[SWTRIG])写入 1。对于每个通道,延迟值 m 决定了从触发输入事件断言开始,到预触发 m 输出信号的变化开始生效之间的时间间隔。时间被定义为:

- 触发输入事件到预触发 m =(预分频器×乘法因子×延迟 m) + 2 个外设时钟周期

- 向确定通道触发输出发生变化的时间添加 1 个额外的外设时钟周期。

每个通道与 1 个 ADC 模块相关联。PDB 通道 n 的预触发输出为 0 到 M;每个预触发输出都连接到 ADC 硬件触发选择和硬件触发输入。预触发用于在实际触发发生之前对 ADC 模块进行预处理。当 ADC 接收到触发的上升沿时,ADC 将根据预触发确定的预处理条件开始转换。ADC 包含 M 组配置和结果寄存器,使其能够在 M 个不同的模拟源之间交替转换(就像乒乓球比赛一样)。预触发输出用于指定接下来将对哪个信号进行采样。当预触发 m 被断言时,ADC 转换将使用配置和结果寄存器的第 m 组进行触发。

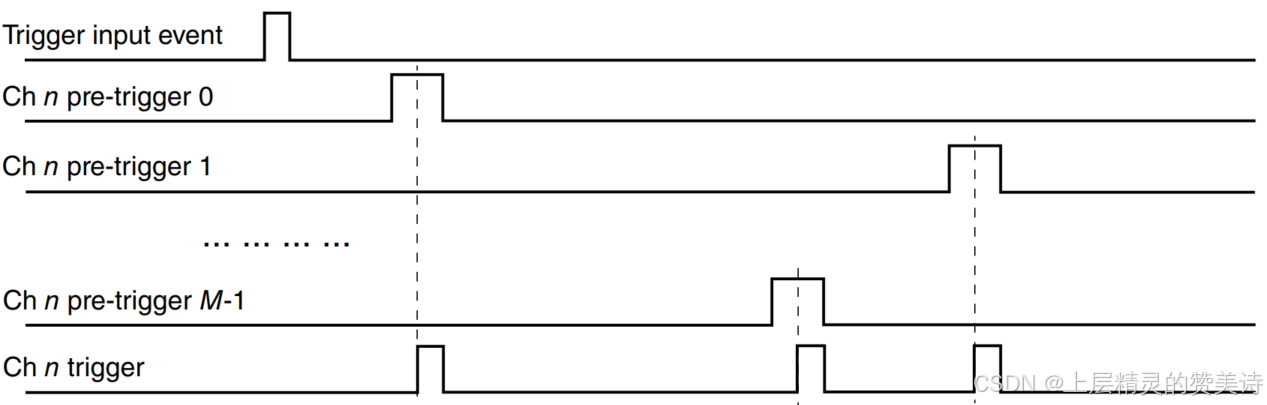

图4中的波形图展示了 PDB 通道 n 的预触发和触发输出。延迟可通过通道延迟寄存器(CHnDLYm)进行独立设置,而预触发则可通过 PDB 通道预触发使能寄存器(CHnC1[EN[m]])启用或禁用。

若清除了PDB通道预触发输出选择位(CHnC1[TOS[m]]),则可以选择绕过通道延迟寄存器(CHnDLYm)中的延迟。在这种情况下,当触发输入事件发生时,预触发m将在2个外设时钟周期后被断言。

PDB可配置为背靠背操作。背靠背操作使得 ADC 转换完成能够触发下一个 PDB 通道的预触发(pre-trigger)和触发输出,从而在下一组配置和结果寄存器上触发 ADC 转换。当通过设置 PDB 通道预触发背靠背操作使能位(CHnC1[BB[m]])启用背靠背操作时,延迟 m 将被忽略,且预触发 m 会在接收到确认信号 m 后的 2 个外设时钟周期 被断言。芯片中的确认连接机制详见 背靠背确认连接 部分。

当来自 PDB 通道 n 的预触发被置位时,与该预触发相关的锁将变为活动状态。该相关锁由相应的 ADCnSC1[COCO] 的上升沿释放;在读取转换结果后应清除 ADCnSC1[COCO],以便后续 ADCnSC1[COCO] 的上升沿能够再次清除锁。锁处于非活动状态的情况为:

- 对应的 ADCnSC1[COCO] 上升沿出现,

- 或者对应的 PDB 预触发被禁用,

- 或者 PDB 被禁用

当通道 n 中任何预触发锁处于激活状态时,通道 n 的触发输出将被抑制。

- 如果在 PDB 通道 n 中有活动锁时,一个新的预触发 m 被断言,那么与该预触发 m 相关联的 PDB 通道序列错误标志(CHnS[ERR[m]])就会被设置。如果 PDB 序列错误中断使能(SC[PDBEIE])被设置,那么序列错误中断就会产生。序列错误通常是因为延迟 m 设置得太短,并且预触发 m 在之前触发的 ADC 转换完成之前被断言而发生的。

- 如果预触发延迟为 0 个周期,那么两个通道都会标记一个 PDB 通道序列错误,并且 ADC 将不会执行转换。

PDB 仅在同一通道内的预触发出现时报告通道序列错误。当通过不同 PDB 通道进行触发时,软件必须确保预触发之间设置足够的延迟间隔以避免冲突。

当 PDB 计数器达到值(CNT + 1)时,PDB 中断标志(SC[PDBIF])被设置。如果 PDB 序列错误中断使能(SC[PDBEIE])被设置且 DMA 使能(SC[DMAEN])被清除,则可以产生 PDB 中断。如果 DMA 使能(SC[DMAEN])被设置,那么当 PDB 中断标志(SC[PDBIF])被设置时,PDB 会请求进行 DMA 传输。

模数寄存器(MOD)中的模数值用于在计数器达到设定值时将其复位至零。如果连续模式使能(SC[CONT])被设置,则计数器将重新开始新一轮计数;否则,计数器将停止运行,直到下一次触发输入事件发生。

2.2 PDB触发输入源选择

PDB 最多有 3 个触发输入源:软件触发、内部触发、外部触发(通过引脚)。它们连接到片上或片外事件源。PDB 可以通过软件经由 SC[SWTRIG]触发。

2.3 脉冲输出

PDB 可以产生宽度可配置的脉冲输出。

- 当 PDB 计数器达到 POyDLY[DLY1] 中设置的值时,那么脉冲输出变为高电平。

- 当 PDB 计数器达到 POyDLY[DLY2] 时,那么它变为低电平。

POyDLY[DLY2] 可以被设置为大于或小于 POyDLY[DLY1]。

ADC 预触发/触发输出与脉冲输出生成共享同一时间基准,因为它们均使用 PDB 计数器。本 MCU 中实现的脉冲输出连接方式在设备的芯片配置详情中描述。

2.4 更新延迟寄存器

2.5 中断与DMA

PDB 可以产生两个中断:PDB 中断和 PDB 序列错误中断。

如果 SC[DMAEN] 被设置,当 SC[PDBIF] 被设置时,PDB 可以产生一个 DMA 传输请求。当 DMA 被启用时,PDB 中断不会被发出。

2.6 使用预分频器和乘法因子对时序分辨率的影响

使用大于 1 的预分频器和乘法因子会限制计数/延迟的精度(以外围时钟周期为单位,受限于预分频器 × 乘法因子的模数)。如果乘法因子设置为 1,预分频器设置为 2,则能够检测到的总外设时钟周期值只能是偶数值;如果预分频器设置为 4,则能够被解码为检测到的总外设时钟周期值只能是 4 的倍数,以此类推。如果应用需要非常长的延迟值,并将预分频器设置为 128,则分辨率将被限制为 128 个外设时钟周期。因此,对于给定的应用,使用尽可能低的预分频器和乘法因子。