计算机组成原理(第五章 CPU)

5.1CPU的功能和基本结构

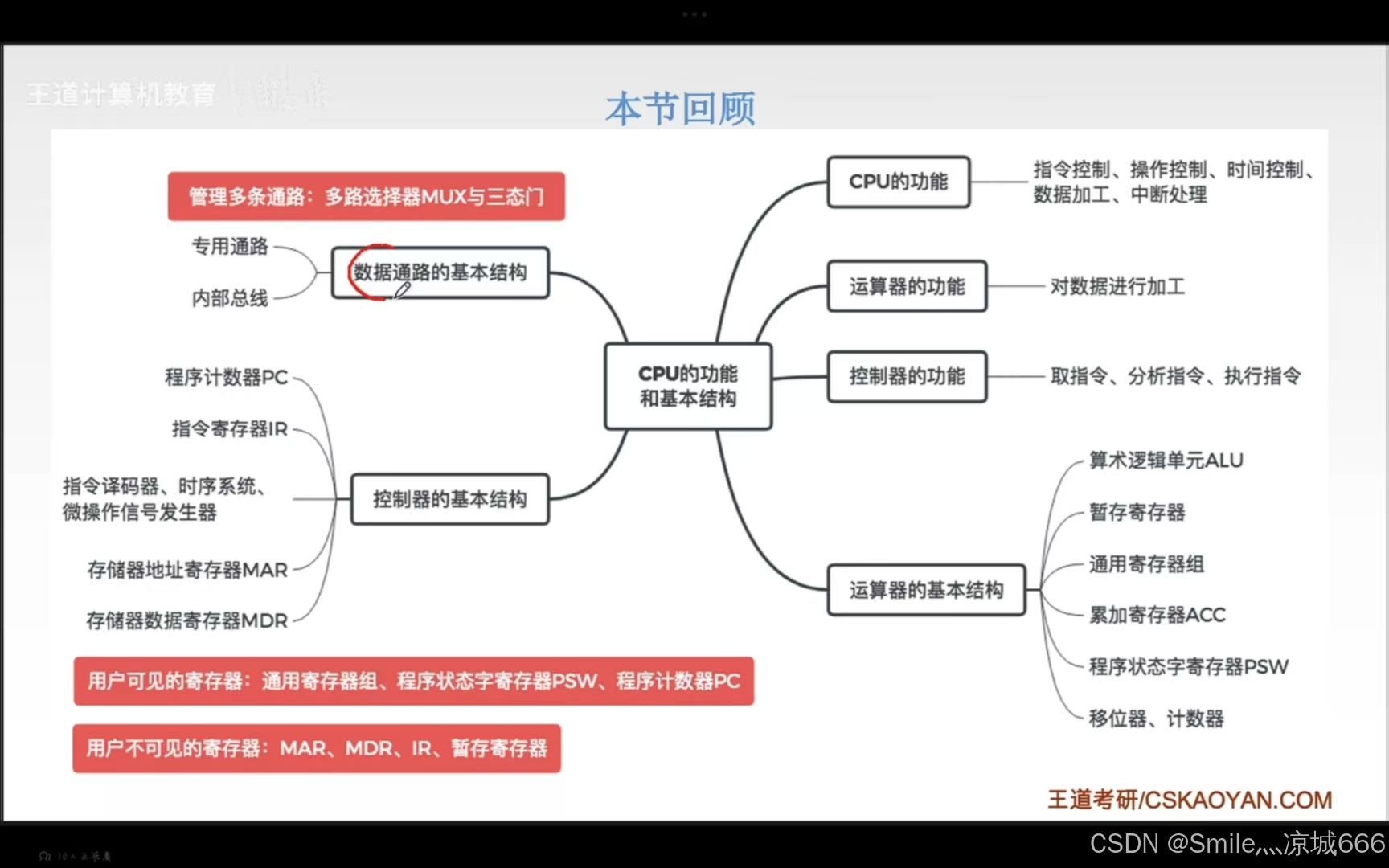

CPU的功能

- 指令控制:完成取指令,分析指令,执行指令

- 操作控制:一条指令往往是由若干的操作信号的组合来实现的,CPU管理并产生由内存取出的每条指令的操作信号,把各种操作信号送往相应的部件

- 时间控制:对各种信号加以时间控制,时间控制要为每条指令按时间顺序提供应有的控制信号

- 数据加工:对数据进行算数和逻辑运算

- 中断处理:对计算机运行过程中出现的异常情况和特殊请求进行处理

运算器的功能

- 对数据进行加工

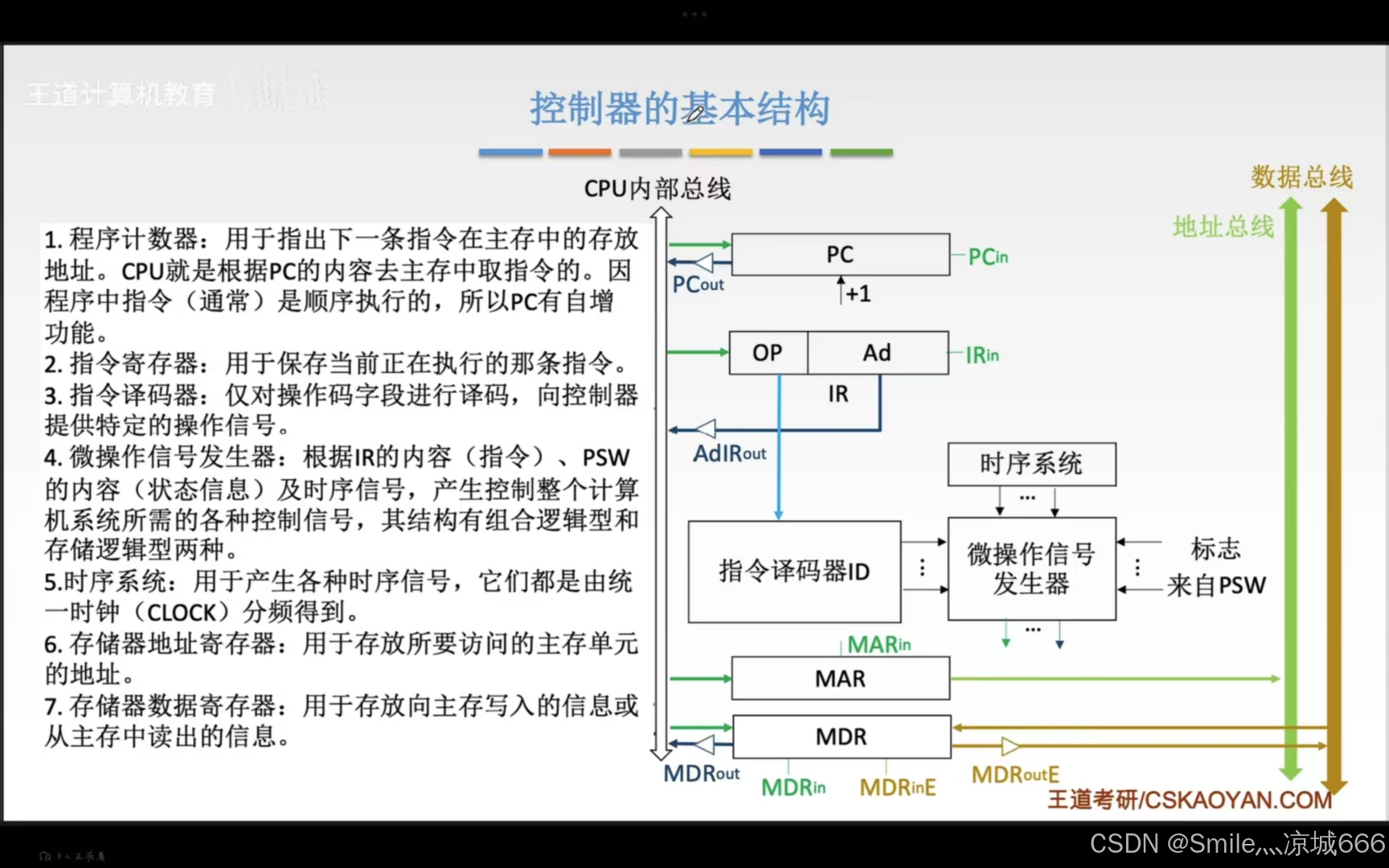

控制器的功能

- 协调并控制计算机各部件执行程序的指令序列

- 取指令:自动形成指令地址(自动+1),自动发出取指令的命令

- 分析指令:操作码译码(分析需要什么操作),产生操作数的有效地址

- 执行指令:根据分析指令得到“操作命令”和“操作数地址”,形成操作信号控制序列,控制部件完成相应的操作

- 每执行一遍之后,要进行一次中断处理

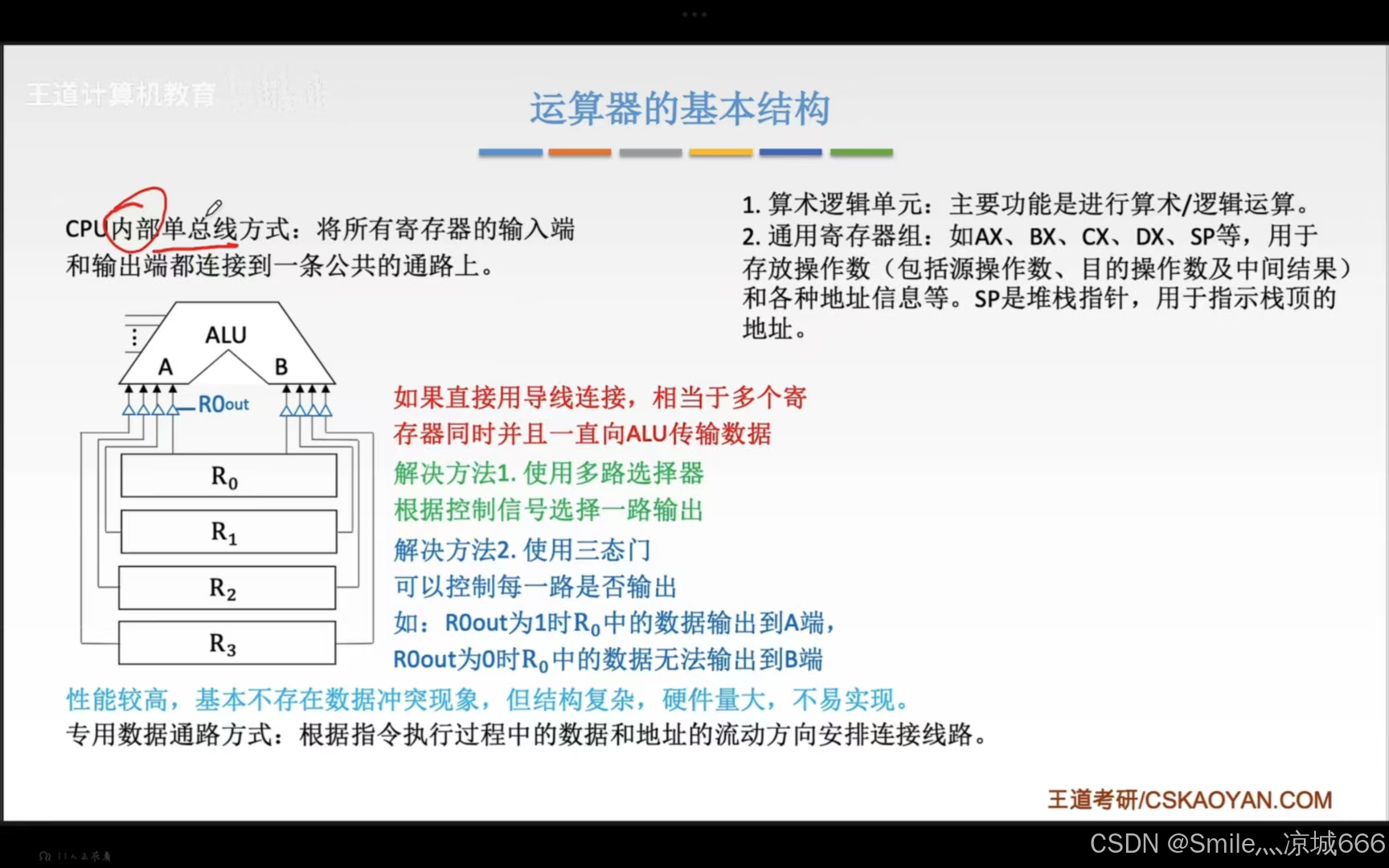

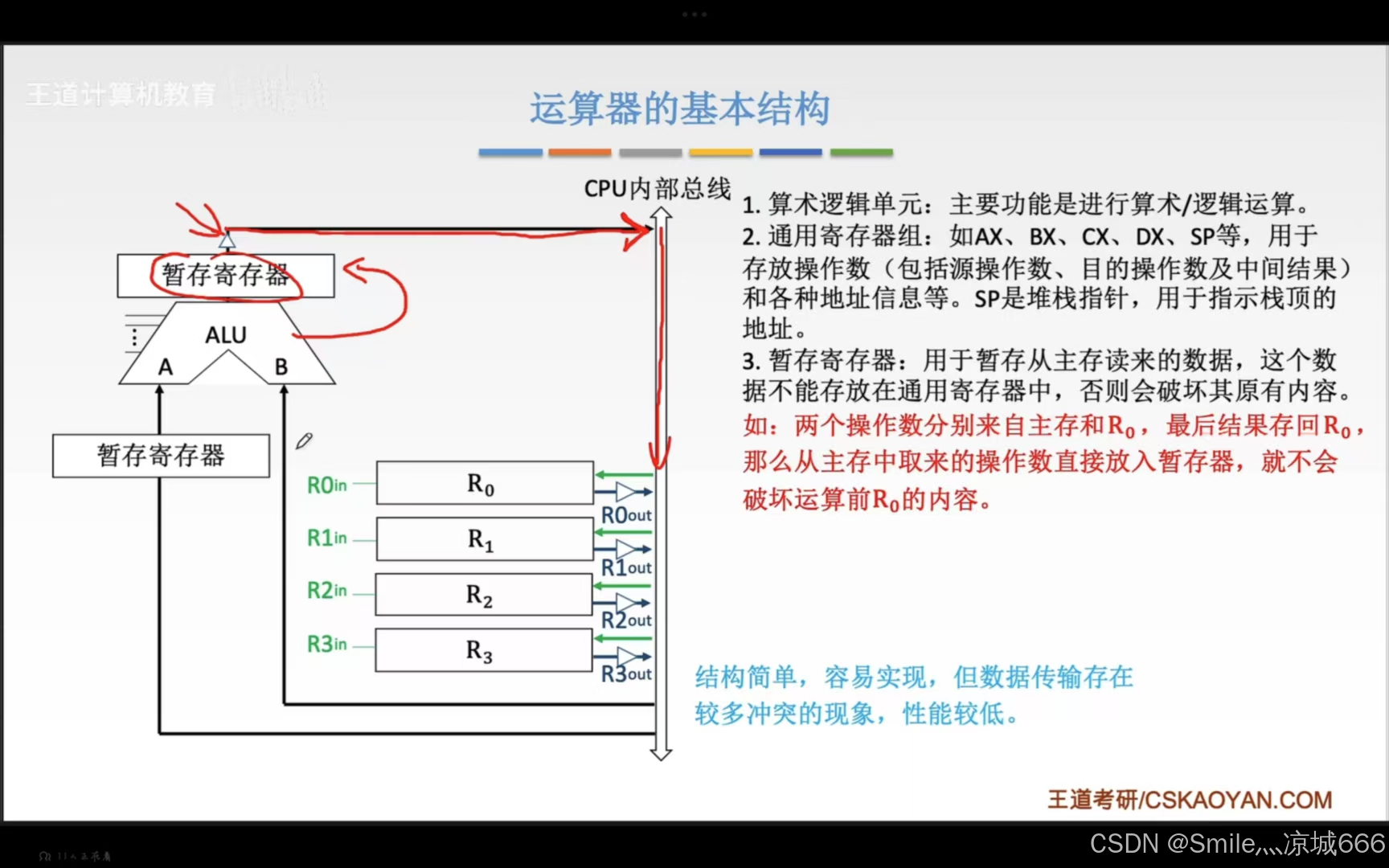

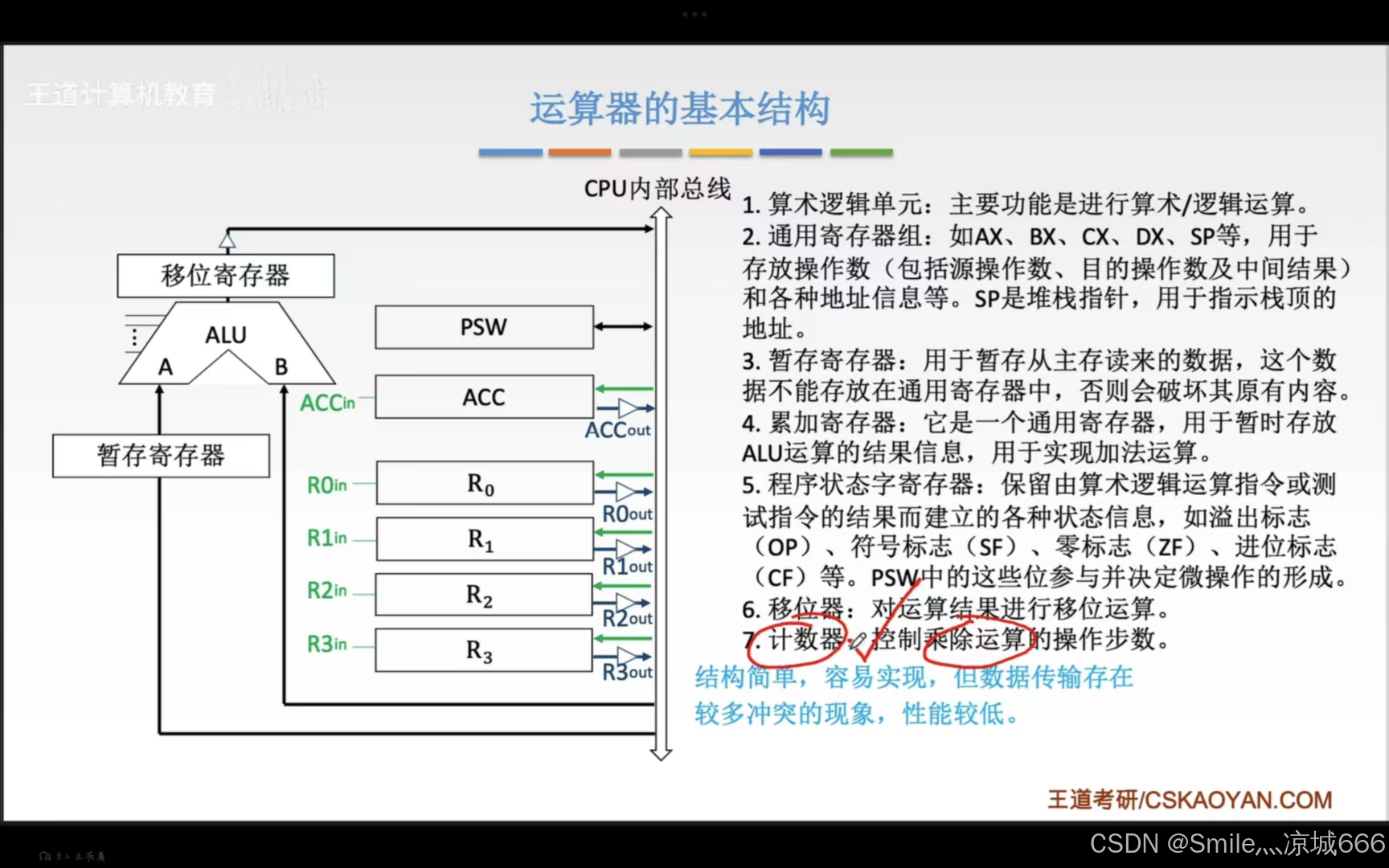

运算器的基本结构

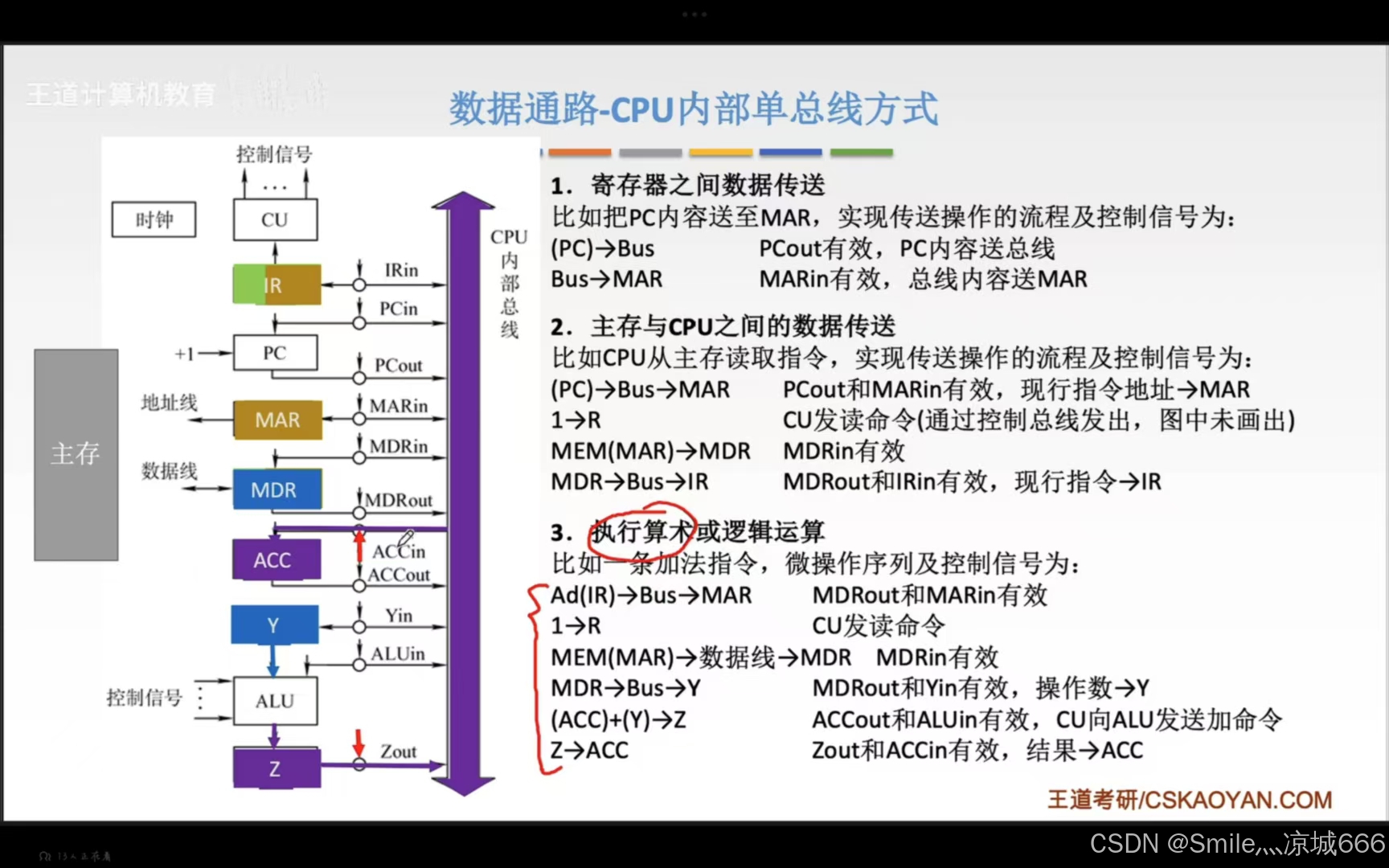

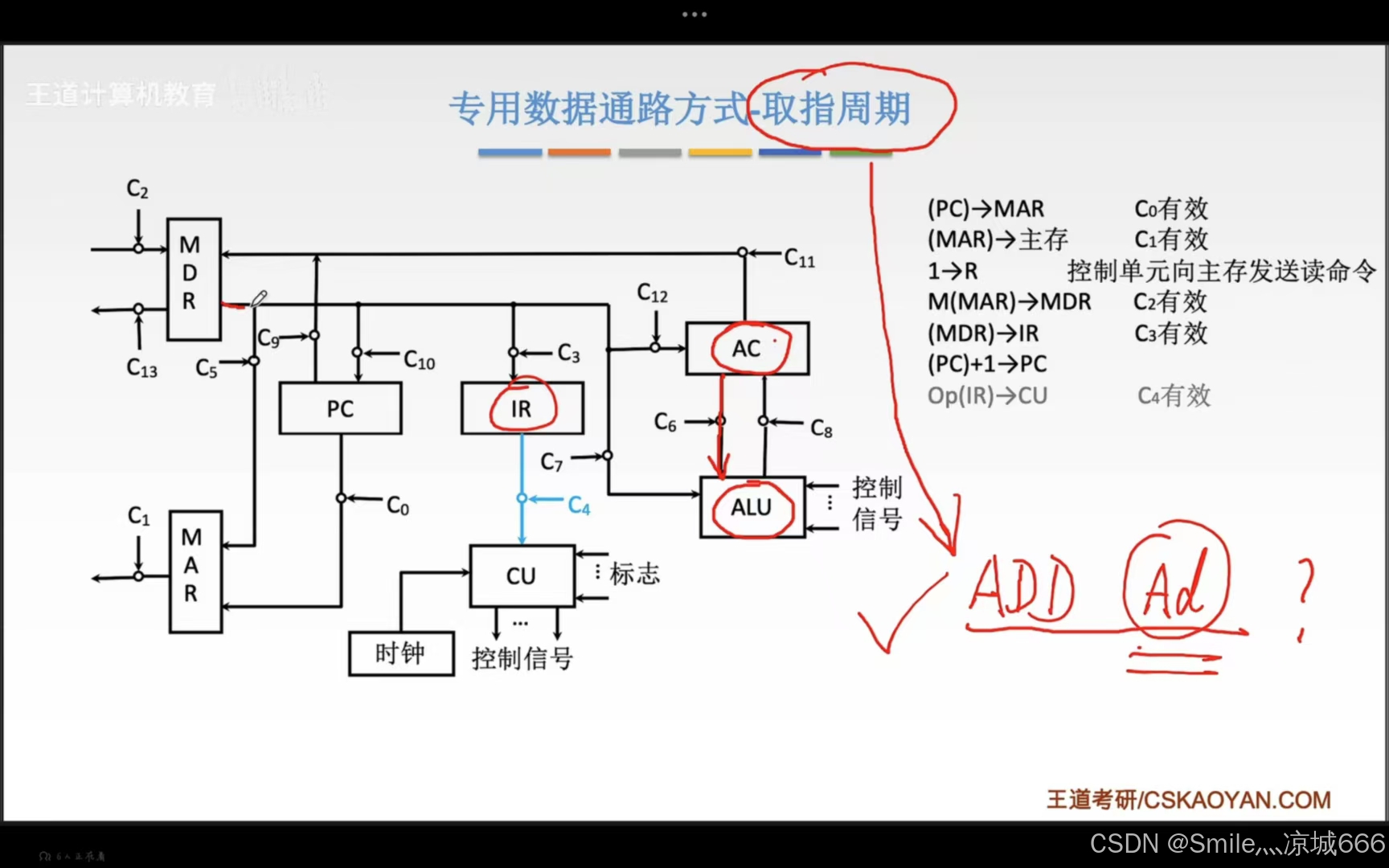

专用数据通路方式

内部单总线方式

上面暂存寄存器的作用:因为刚结束的时候电信号不稳定,输出到寄存器的可能是个错误的数值,

上面暂存寄存器的作用:因为刚结束的时候电信号不稳定,输出到寄存器的可能是个错误的数值,

所以加了个暂存寄存器和三态门(ALU的两端要一起输入)

控制器的基本结构

总结

5.2指令的执行过成

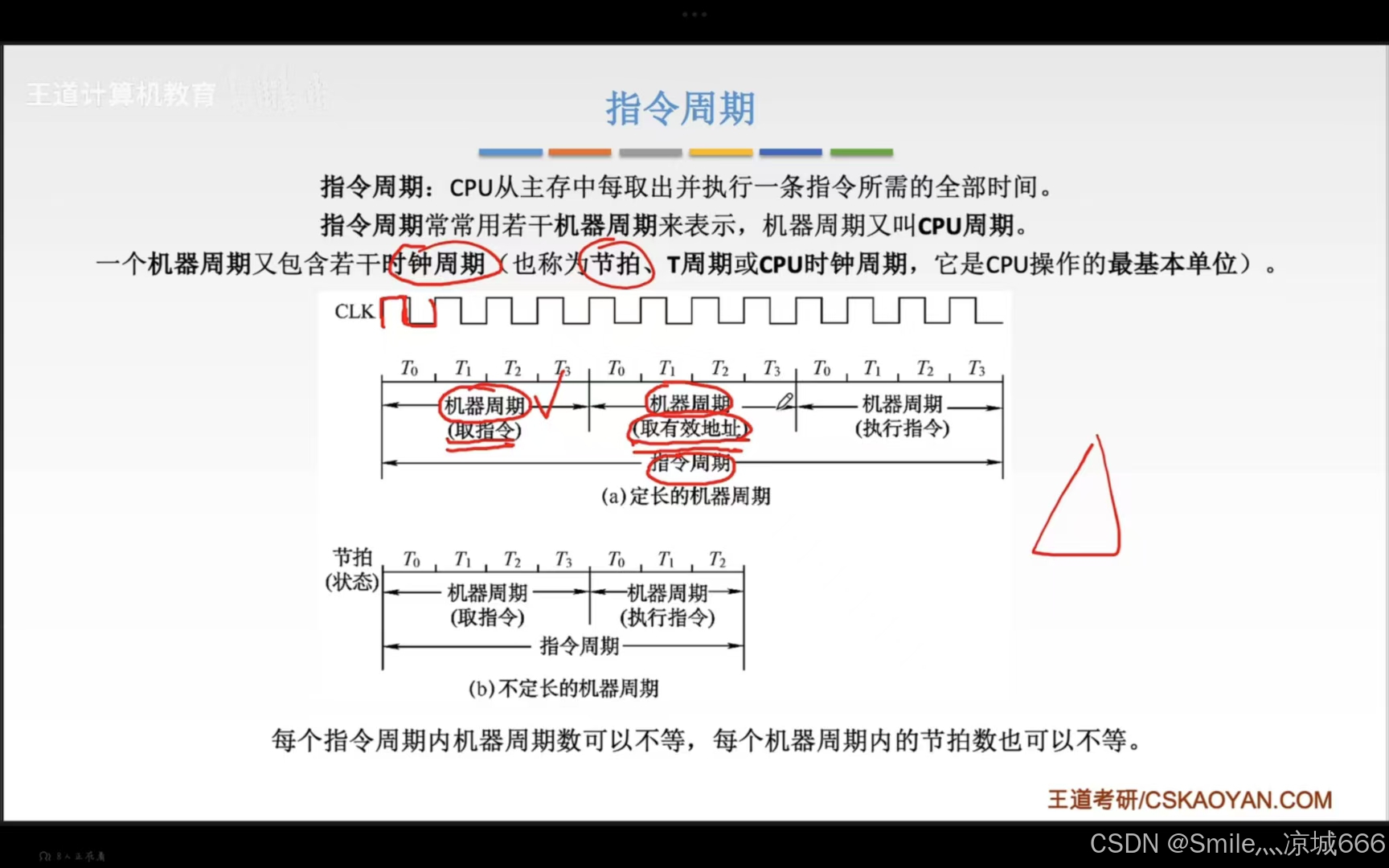

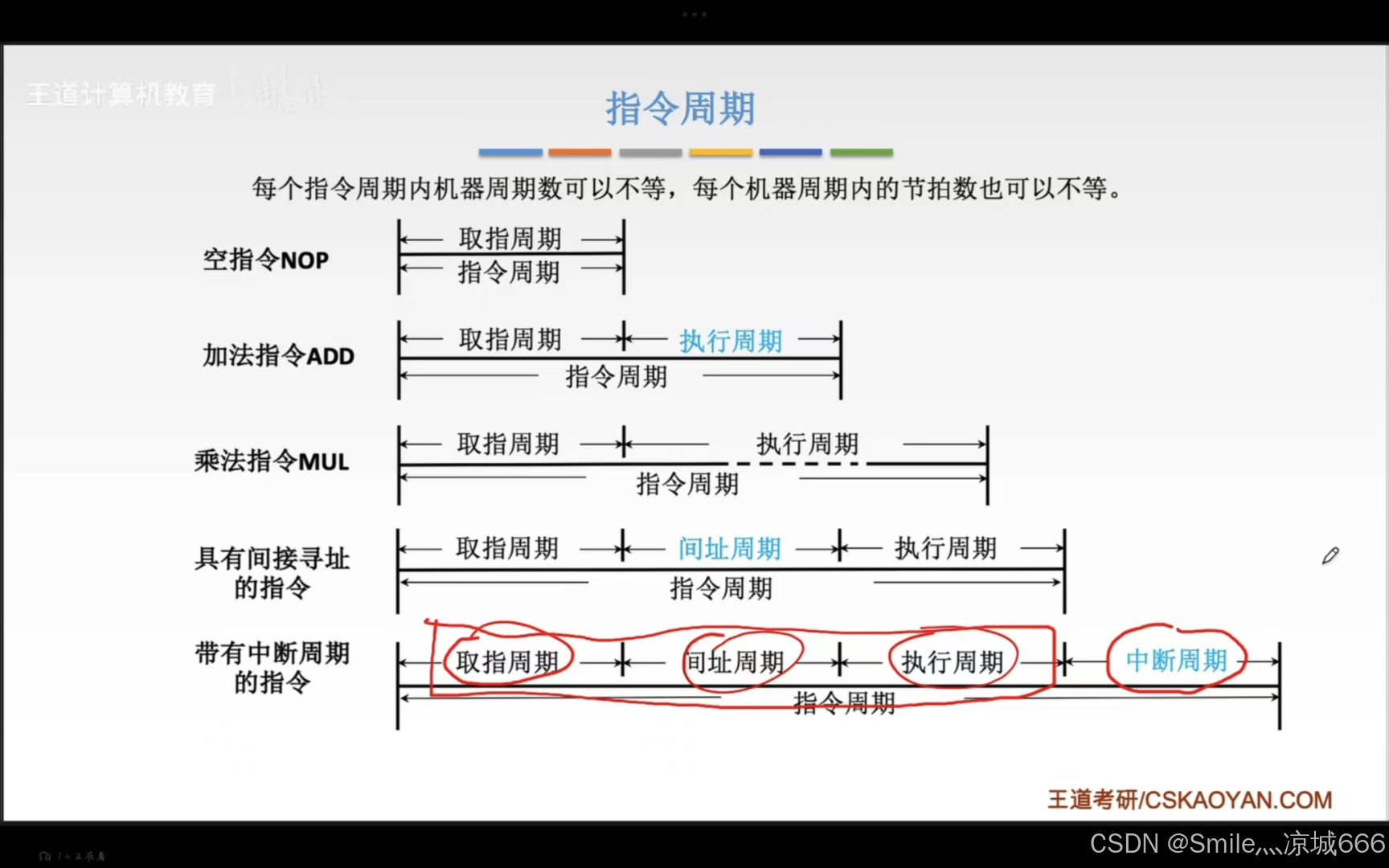

指令周期:

分析指令是很快的

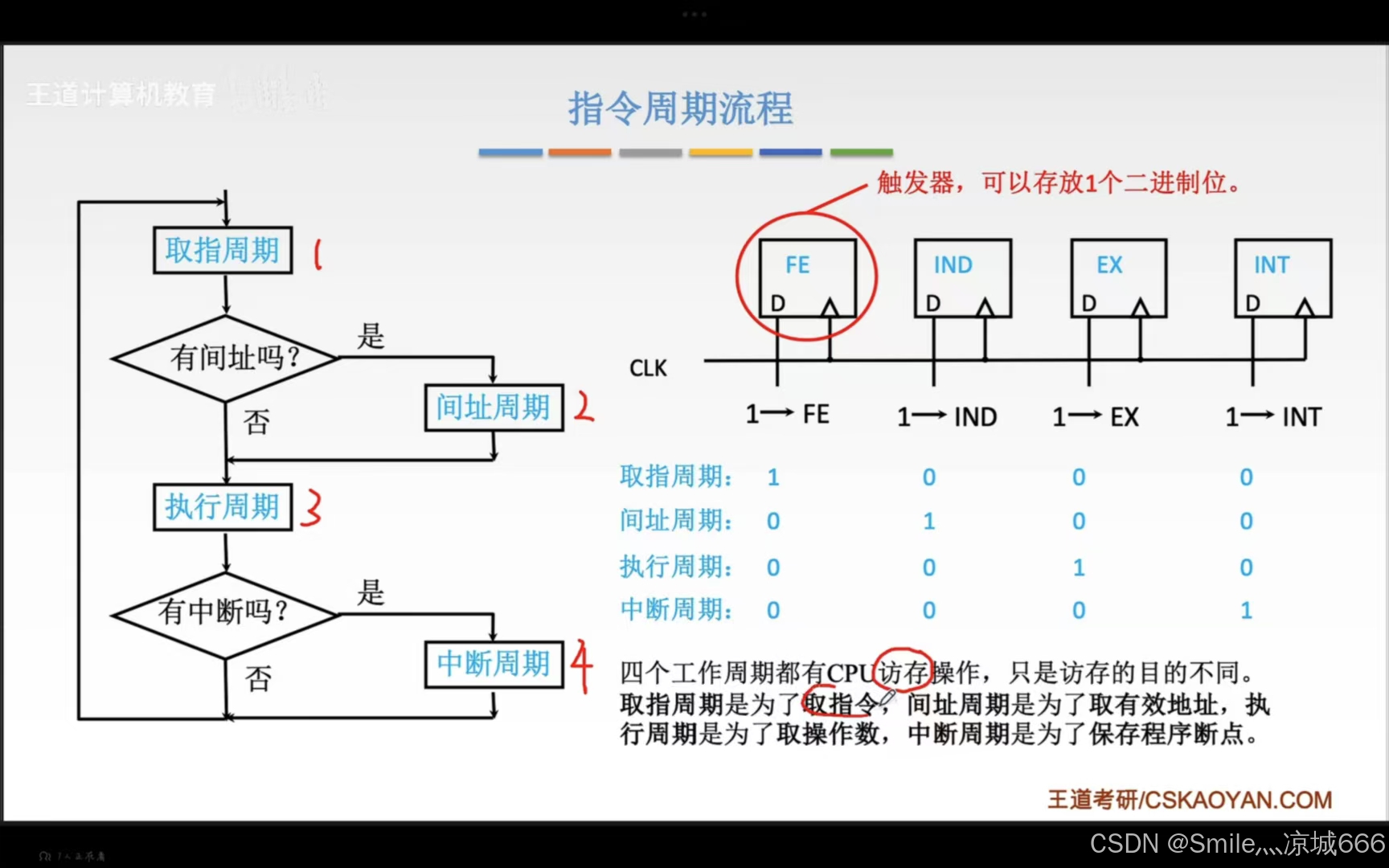

指令周期的流程

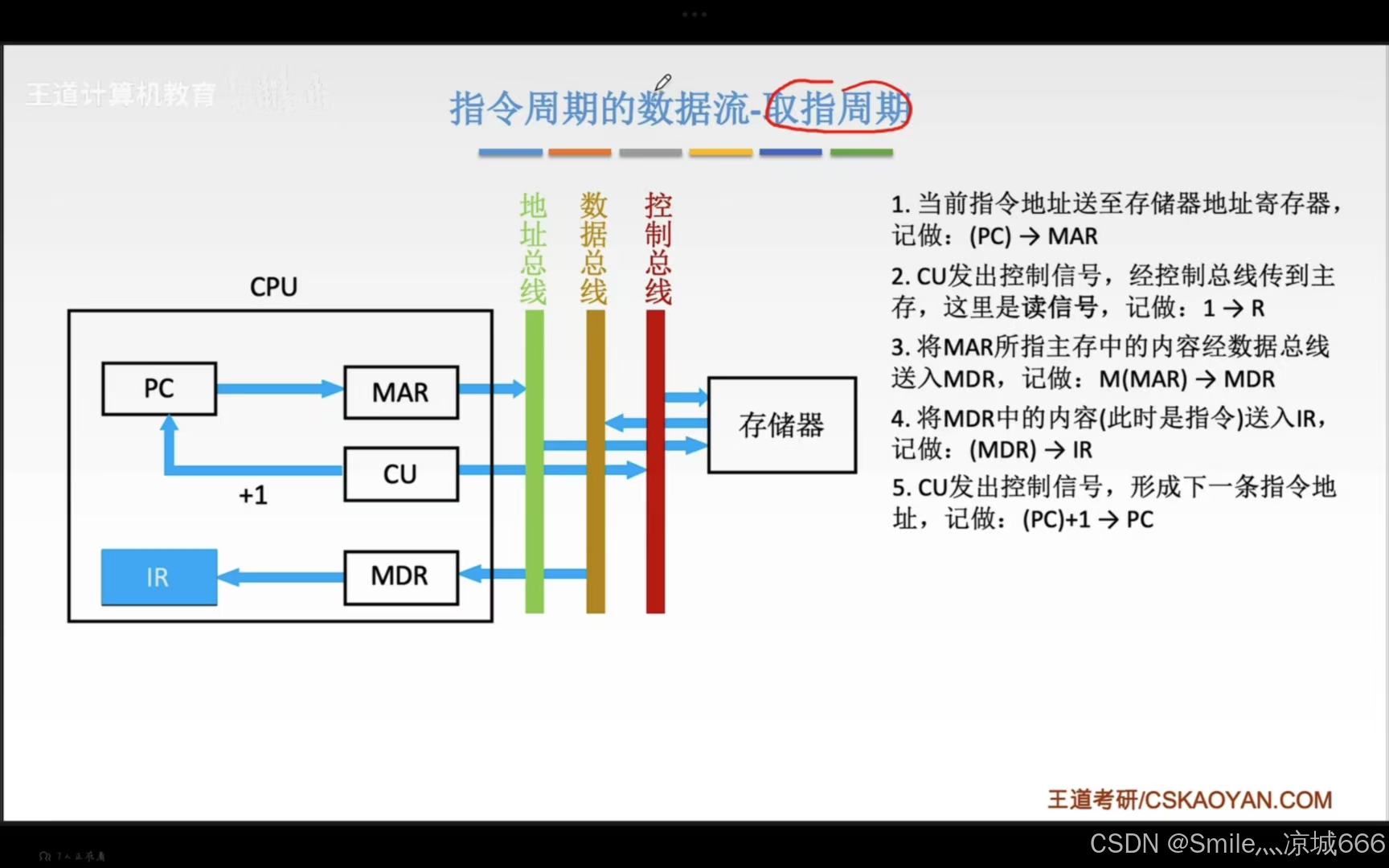

指令周期的数据流

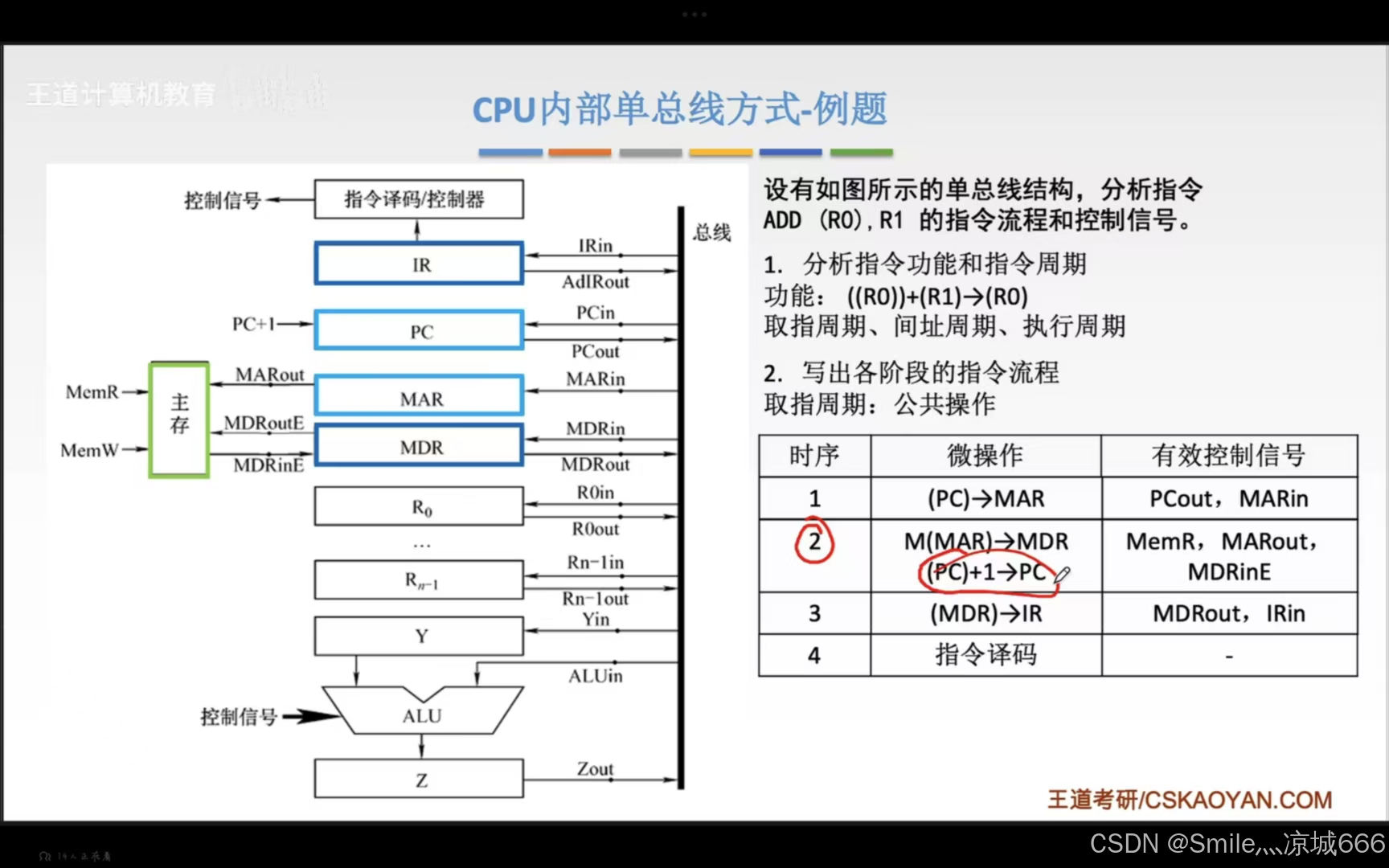

取指周期

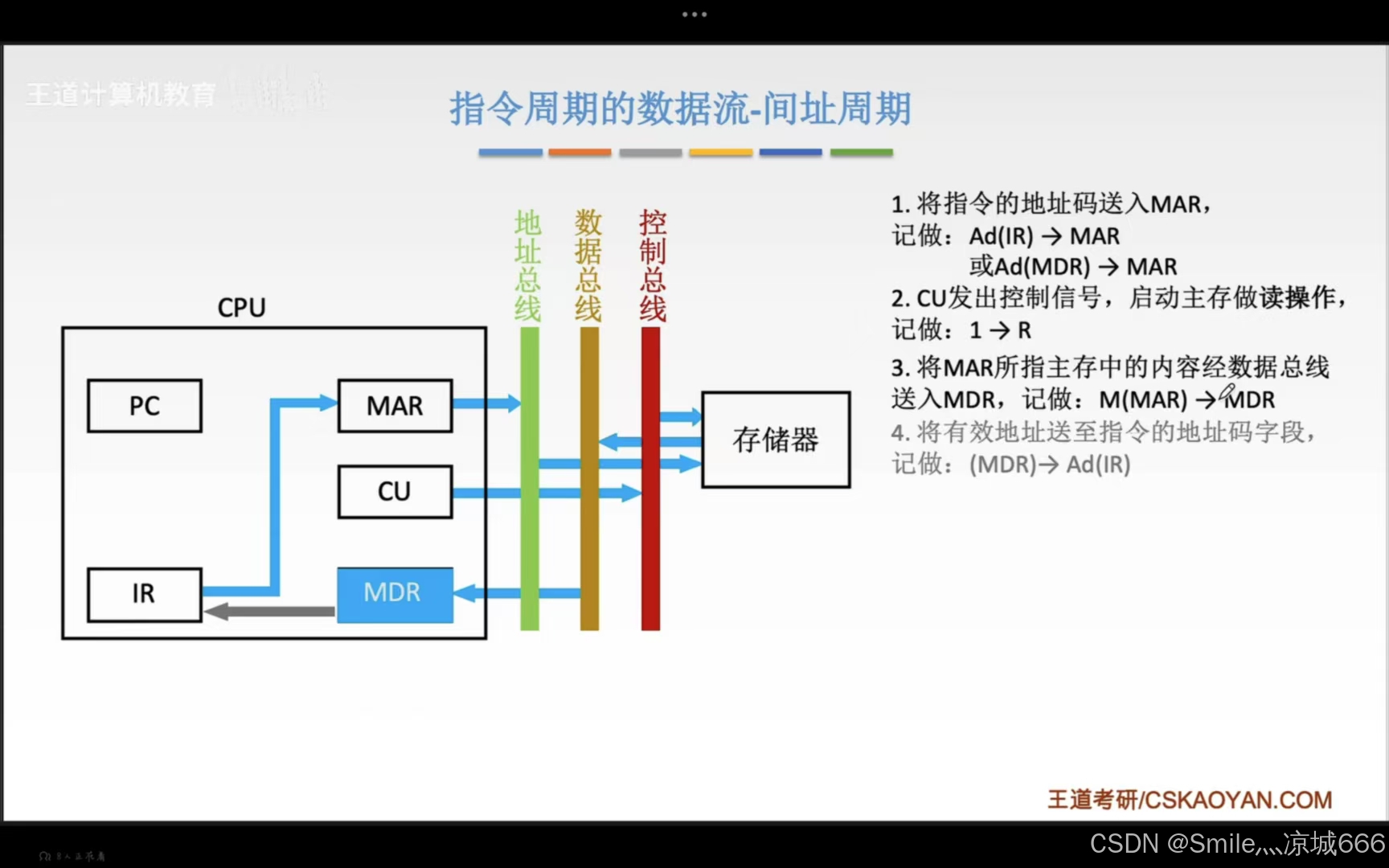

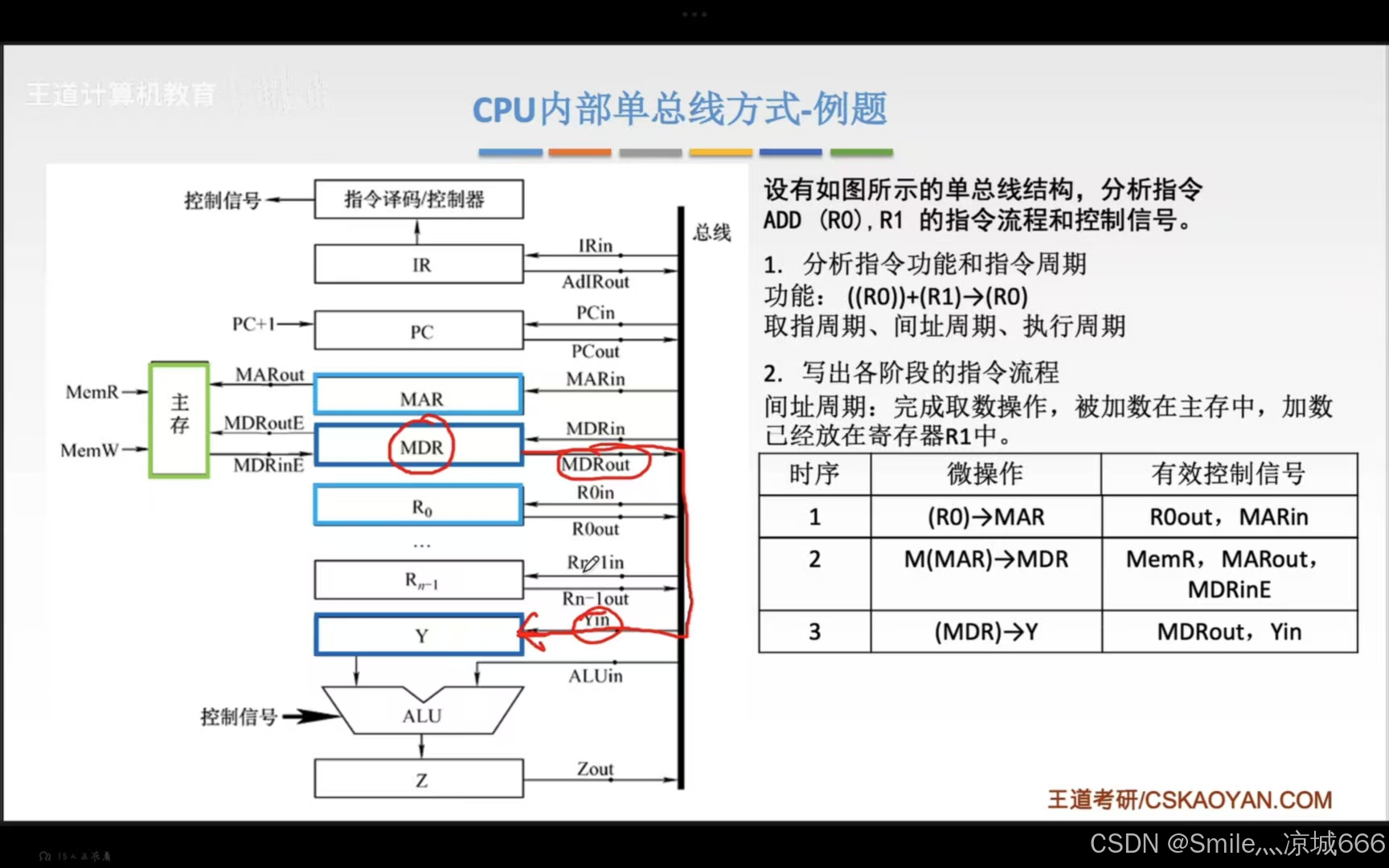

间址周期

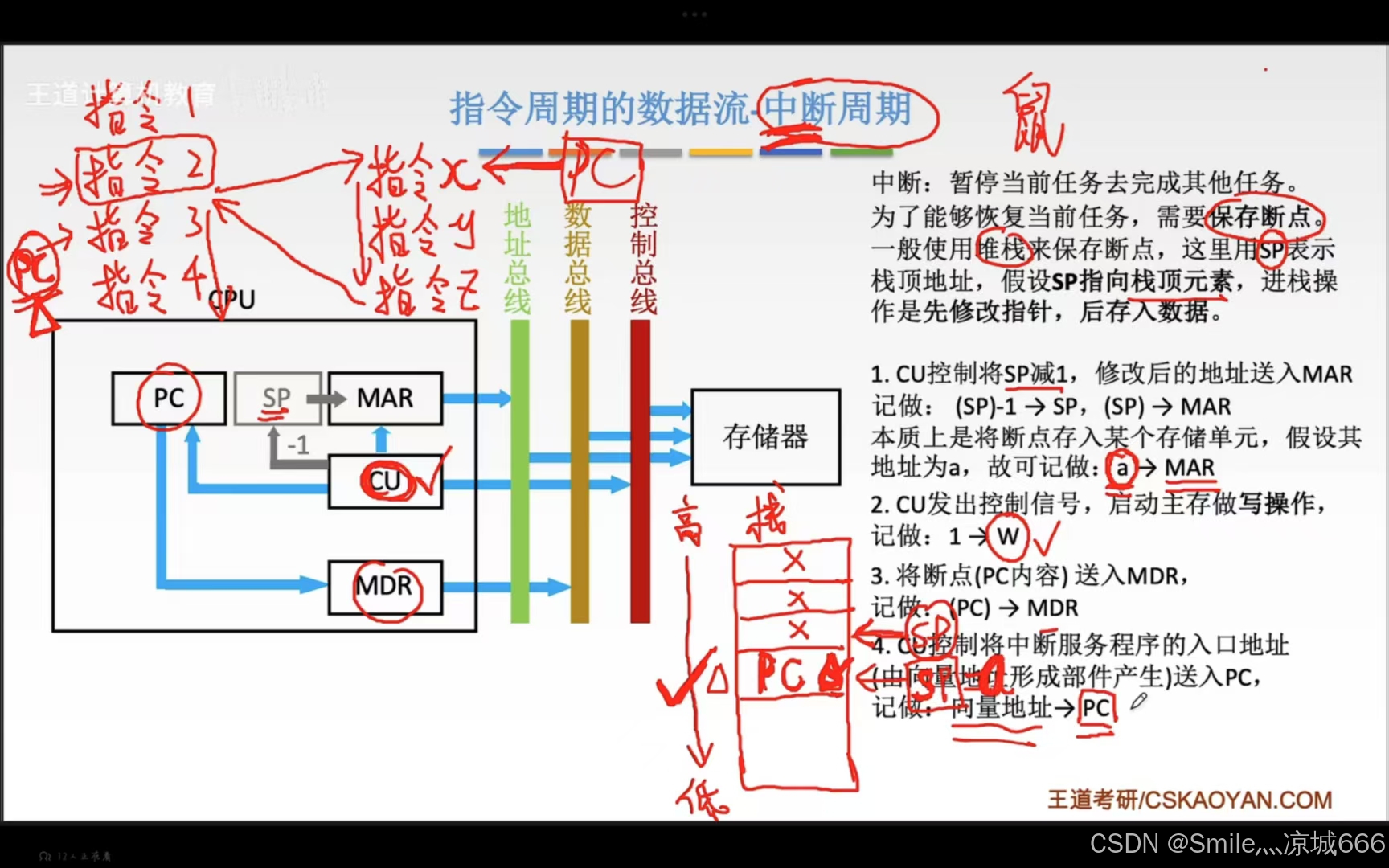

中断周期

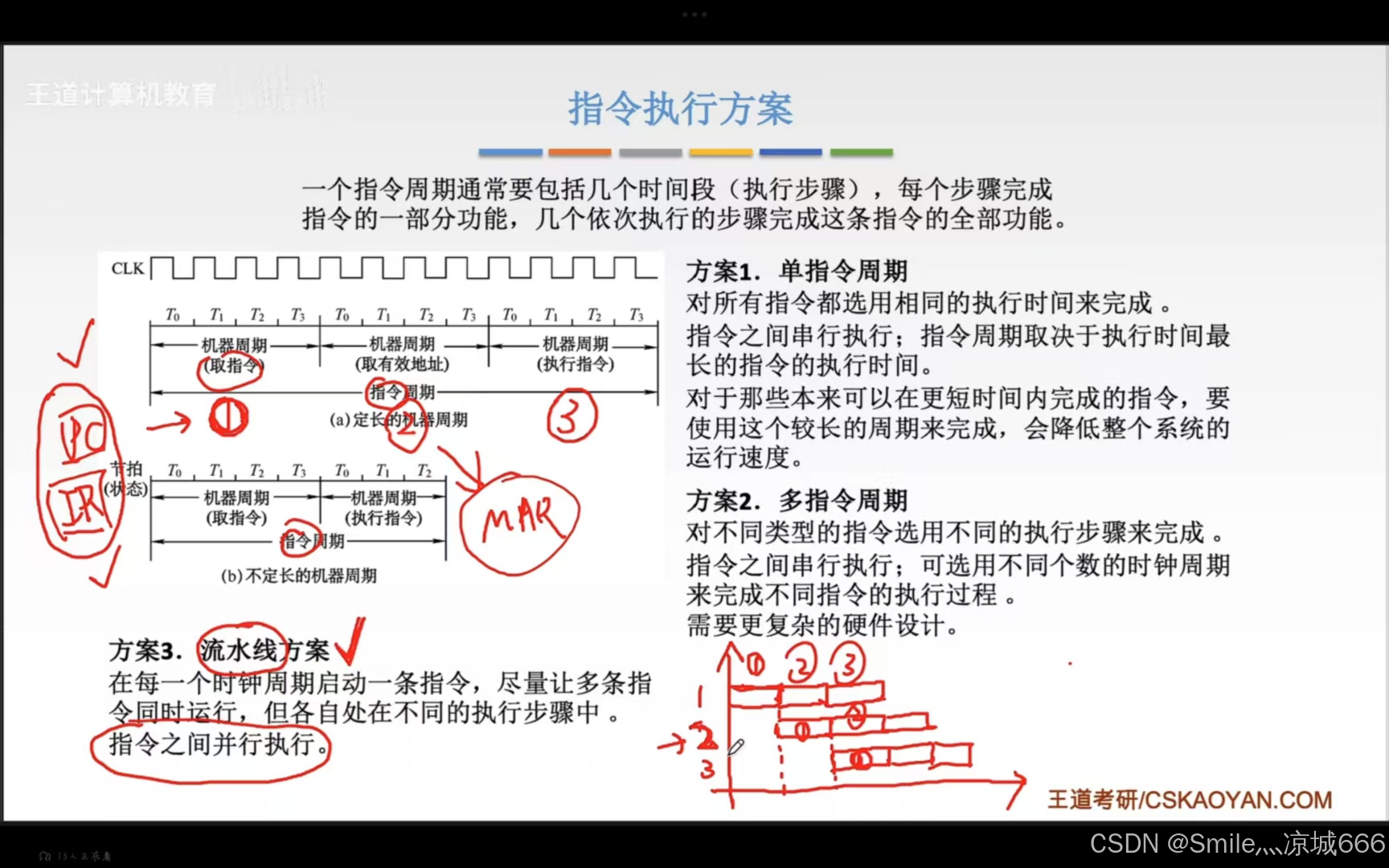

指令的执行方案

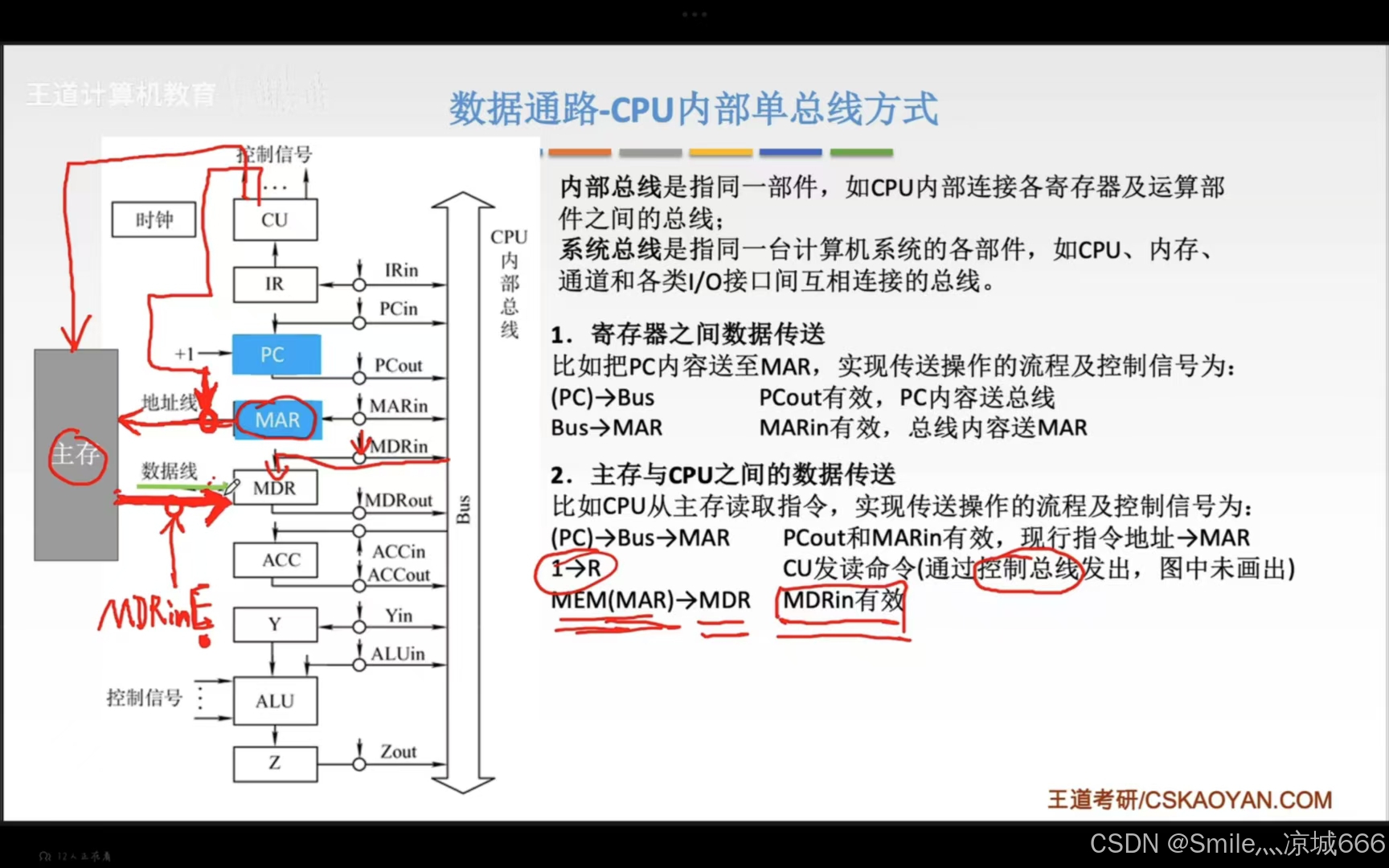

5.3_1数据通路-单总线通路结构

数据通路:数据在功能部件之间的路径

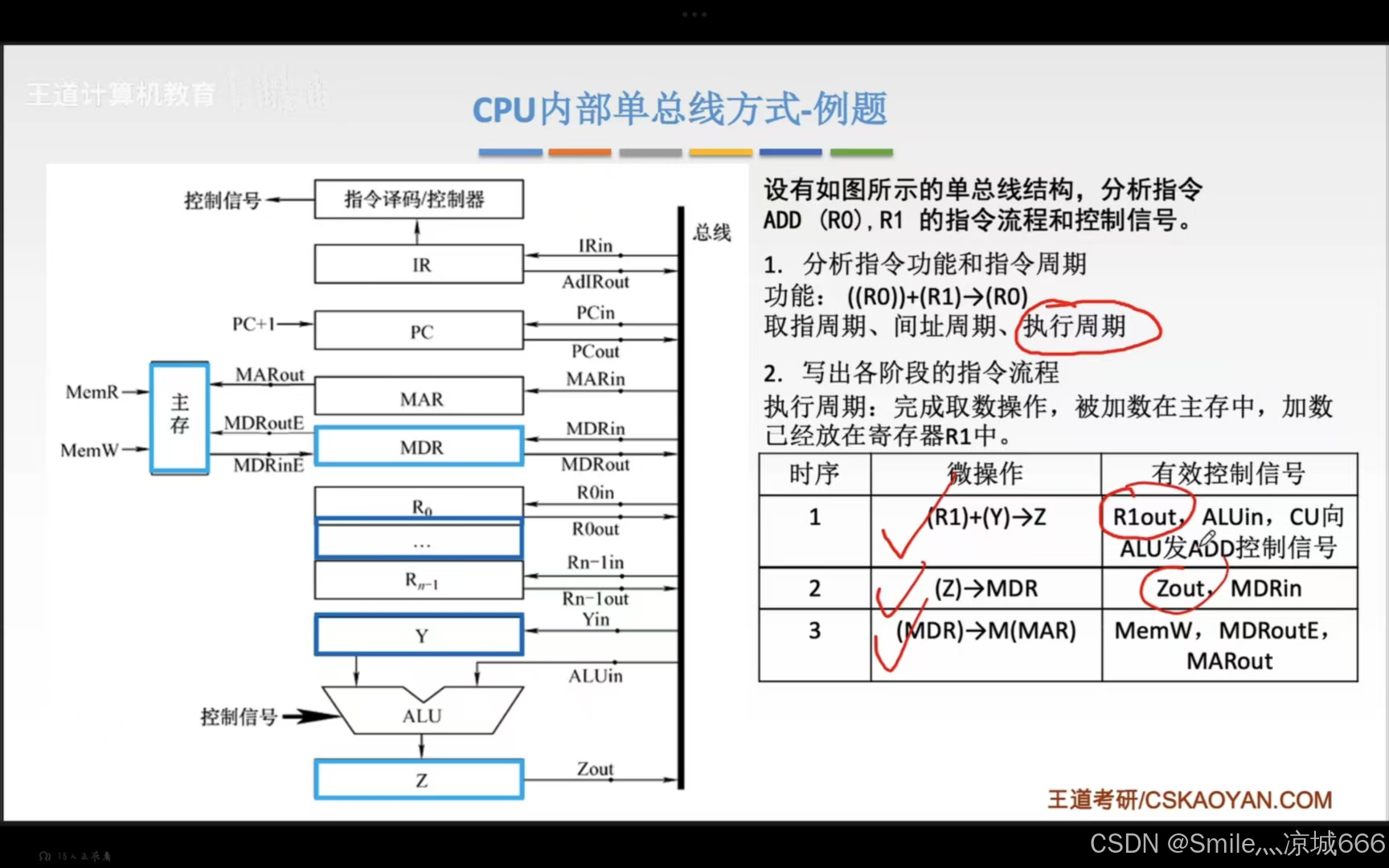

例题(出过几年的大题)

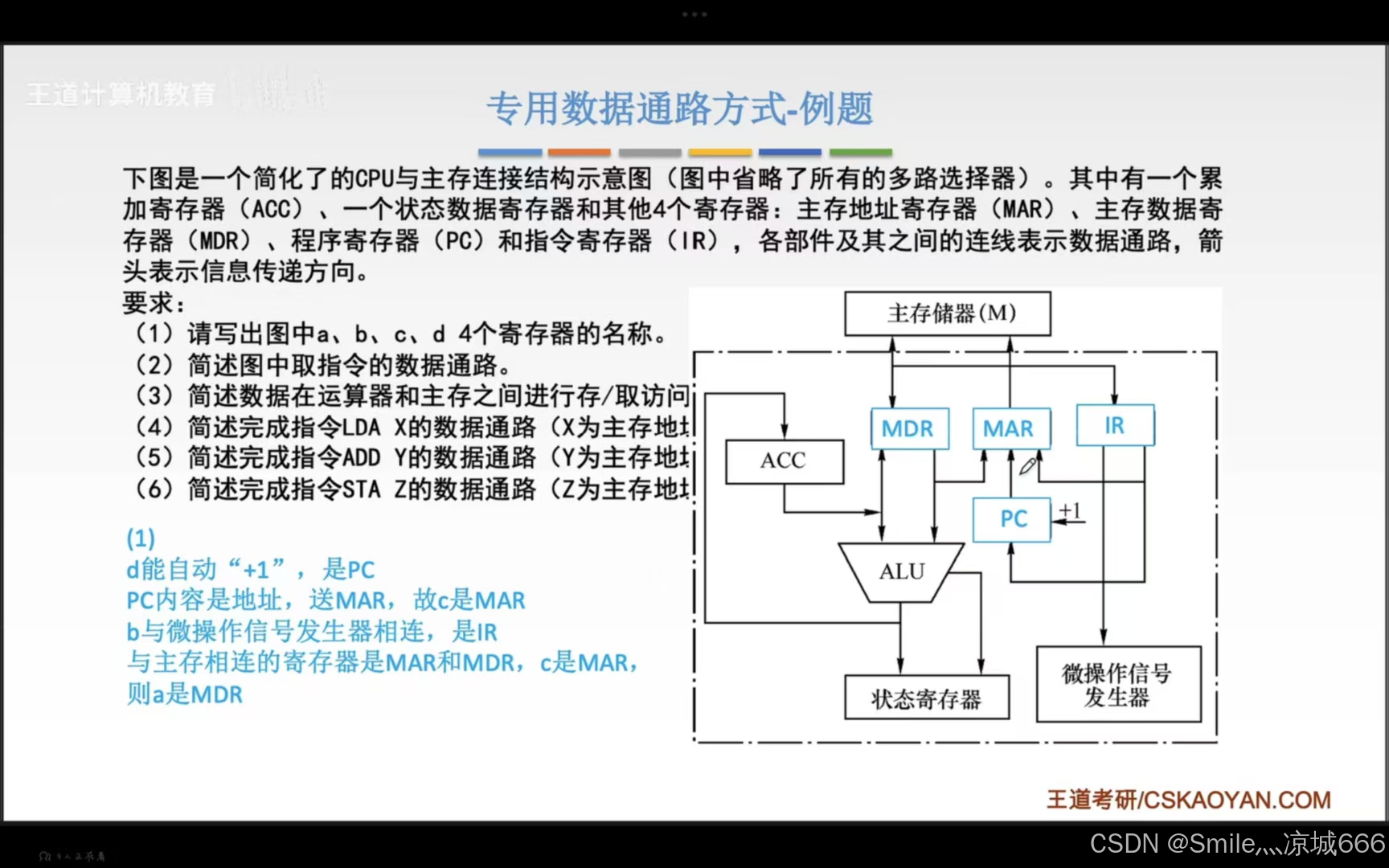

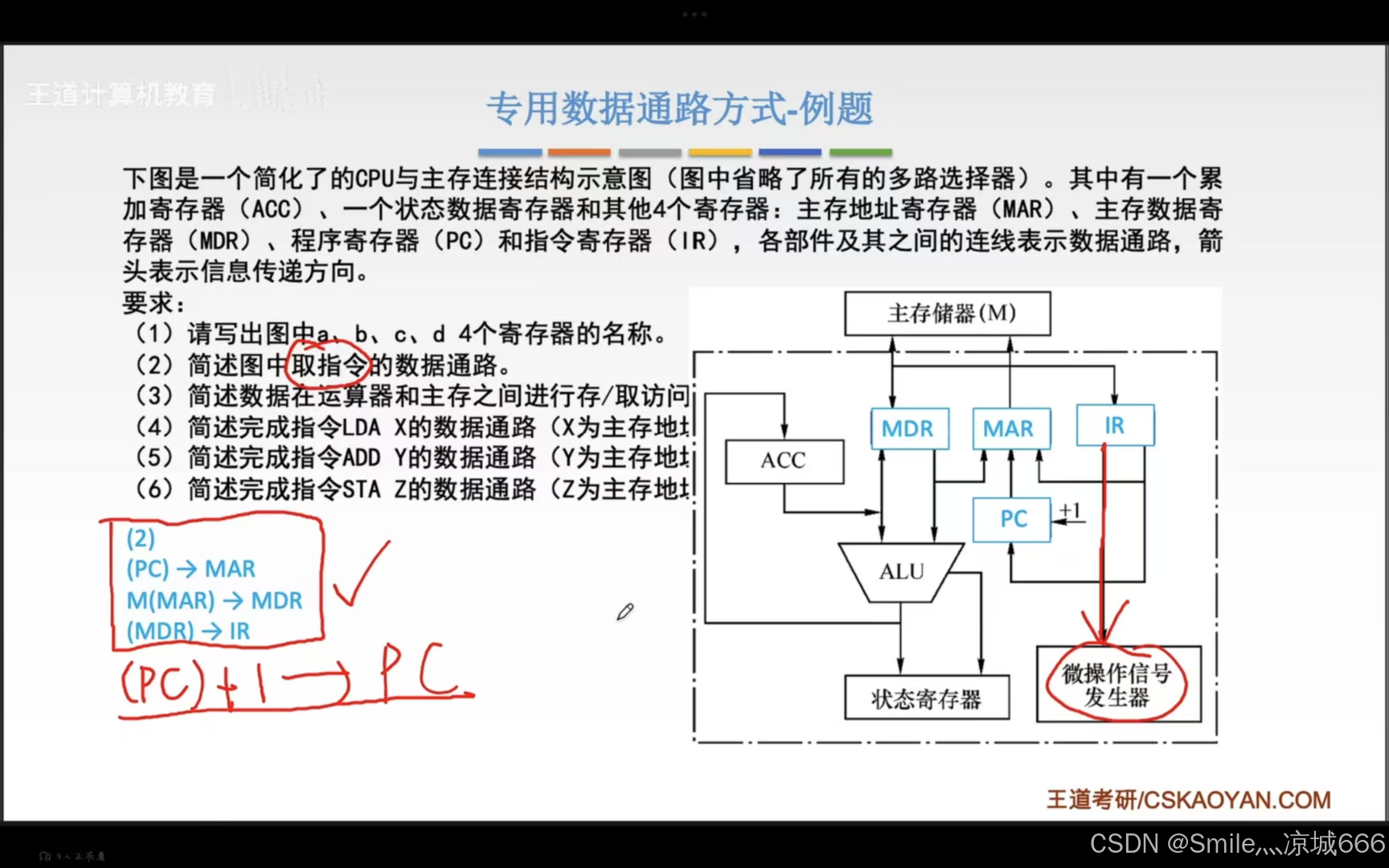

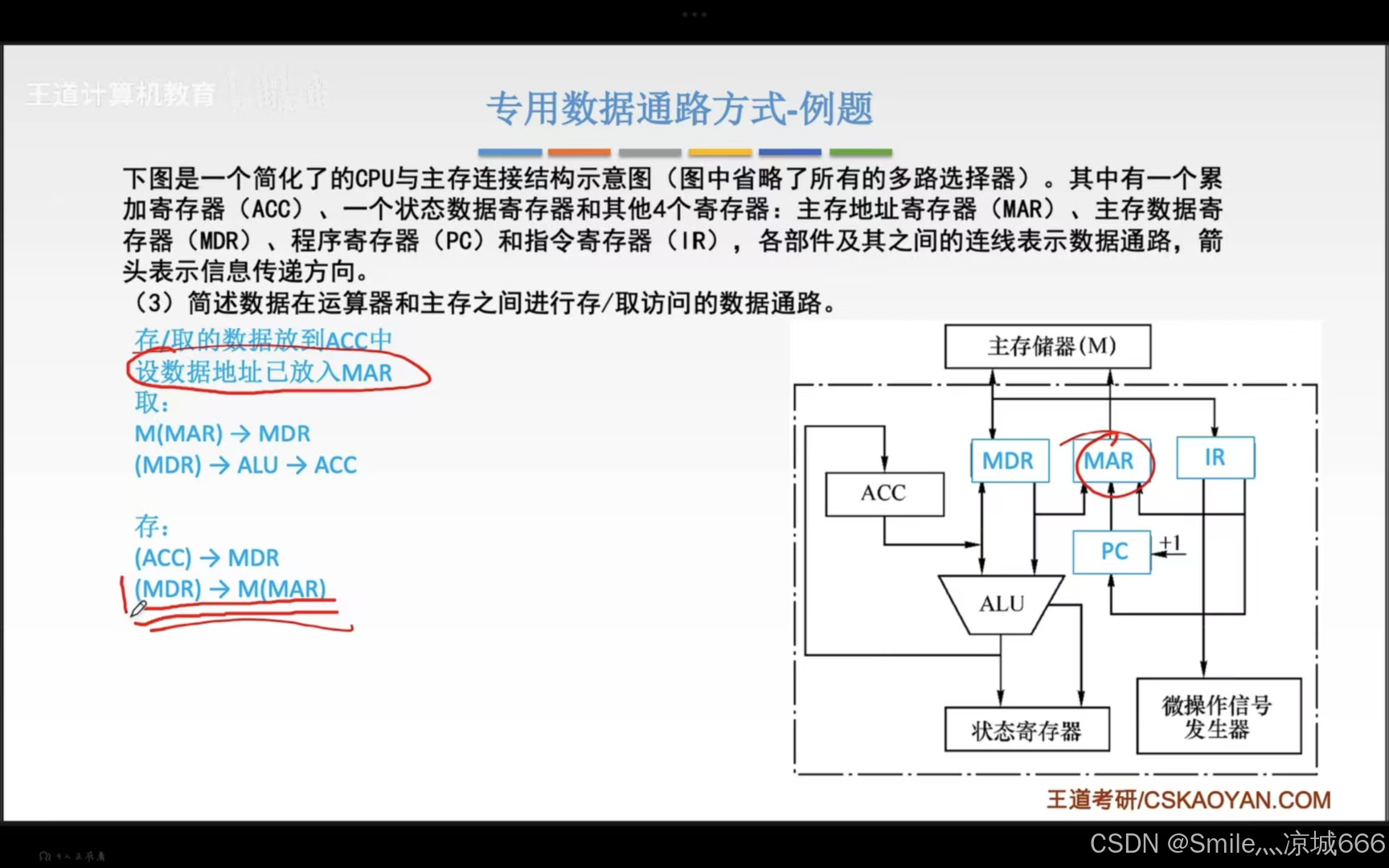

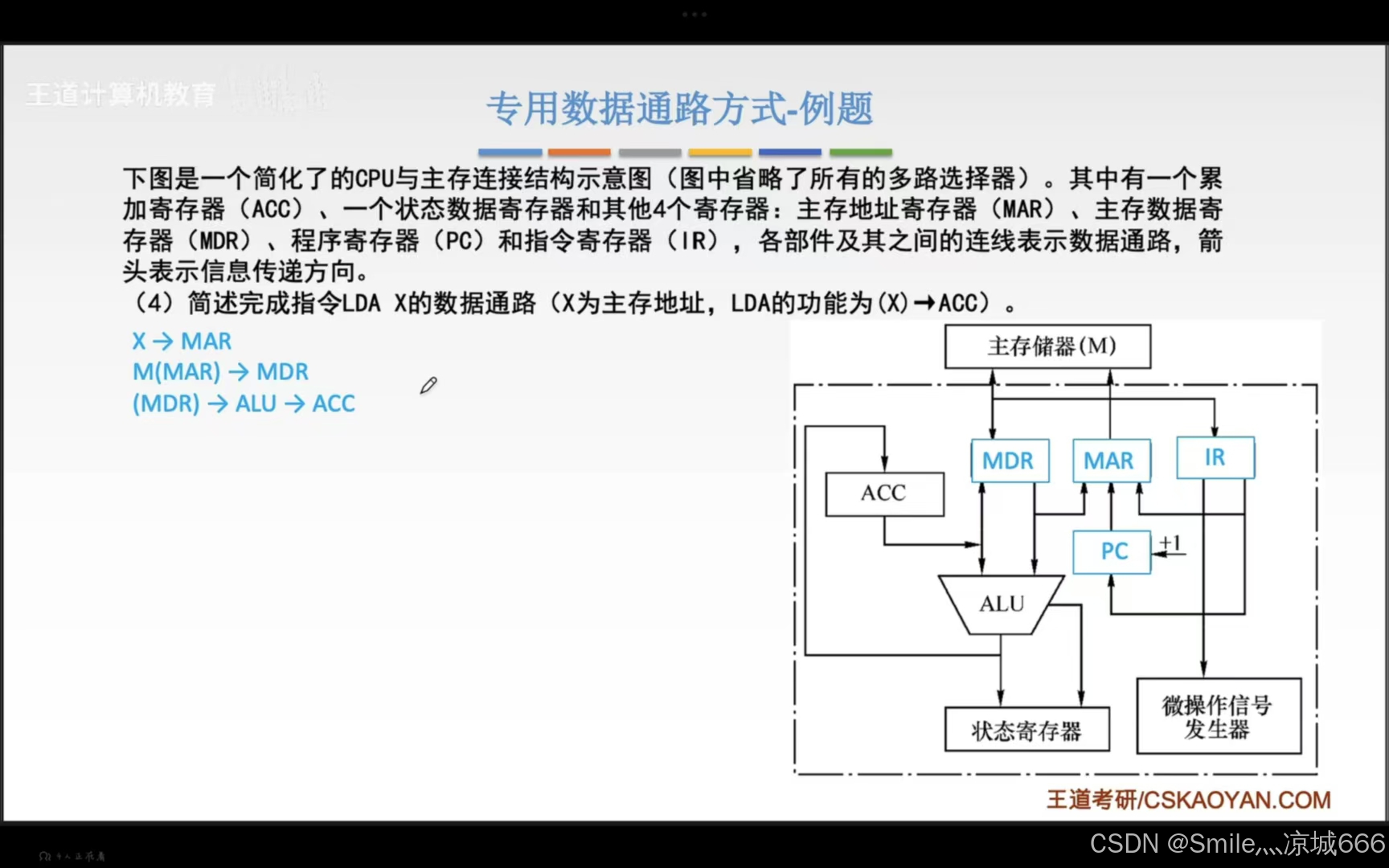

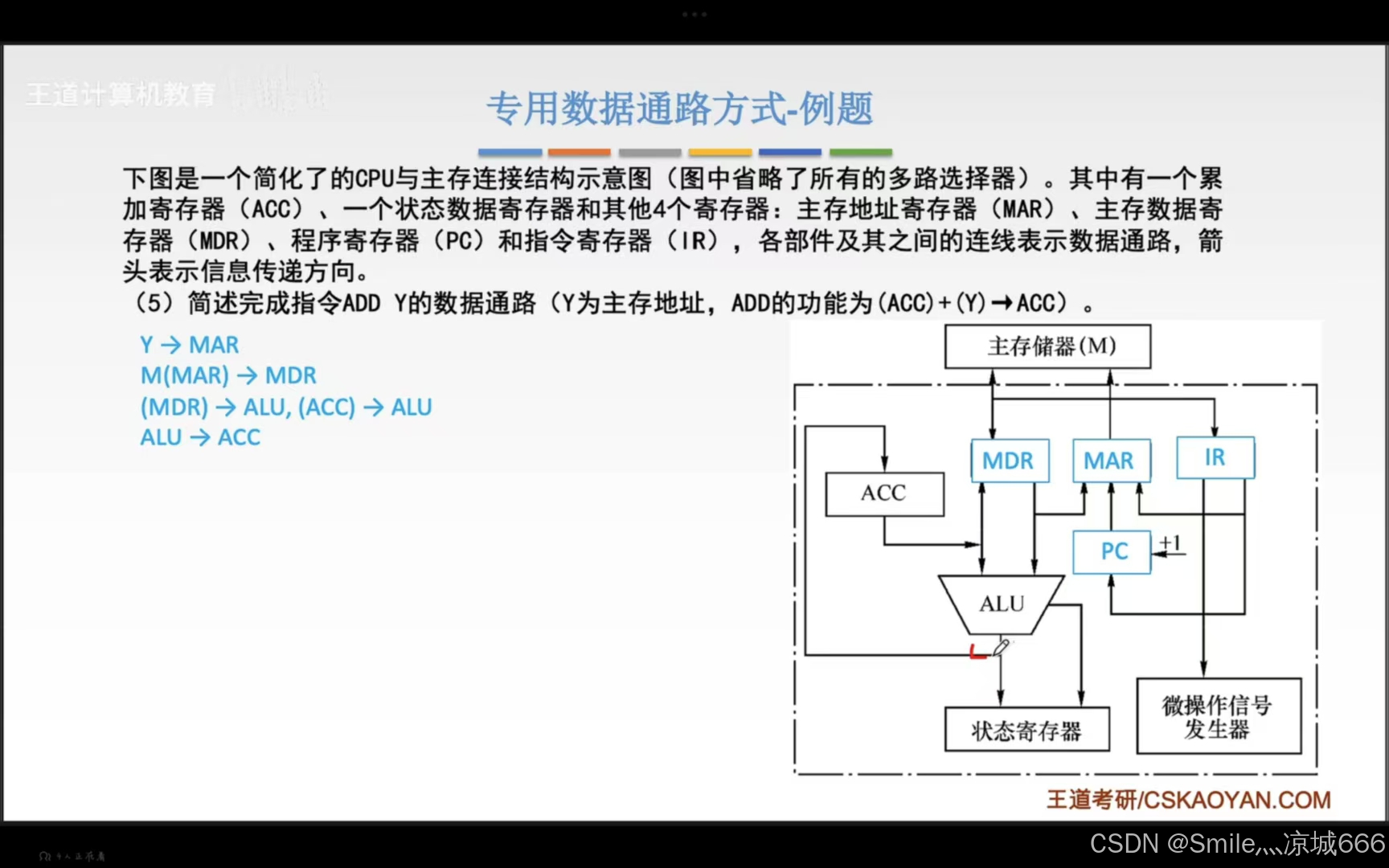

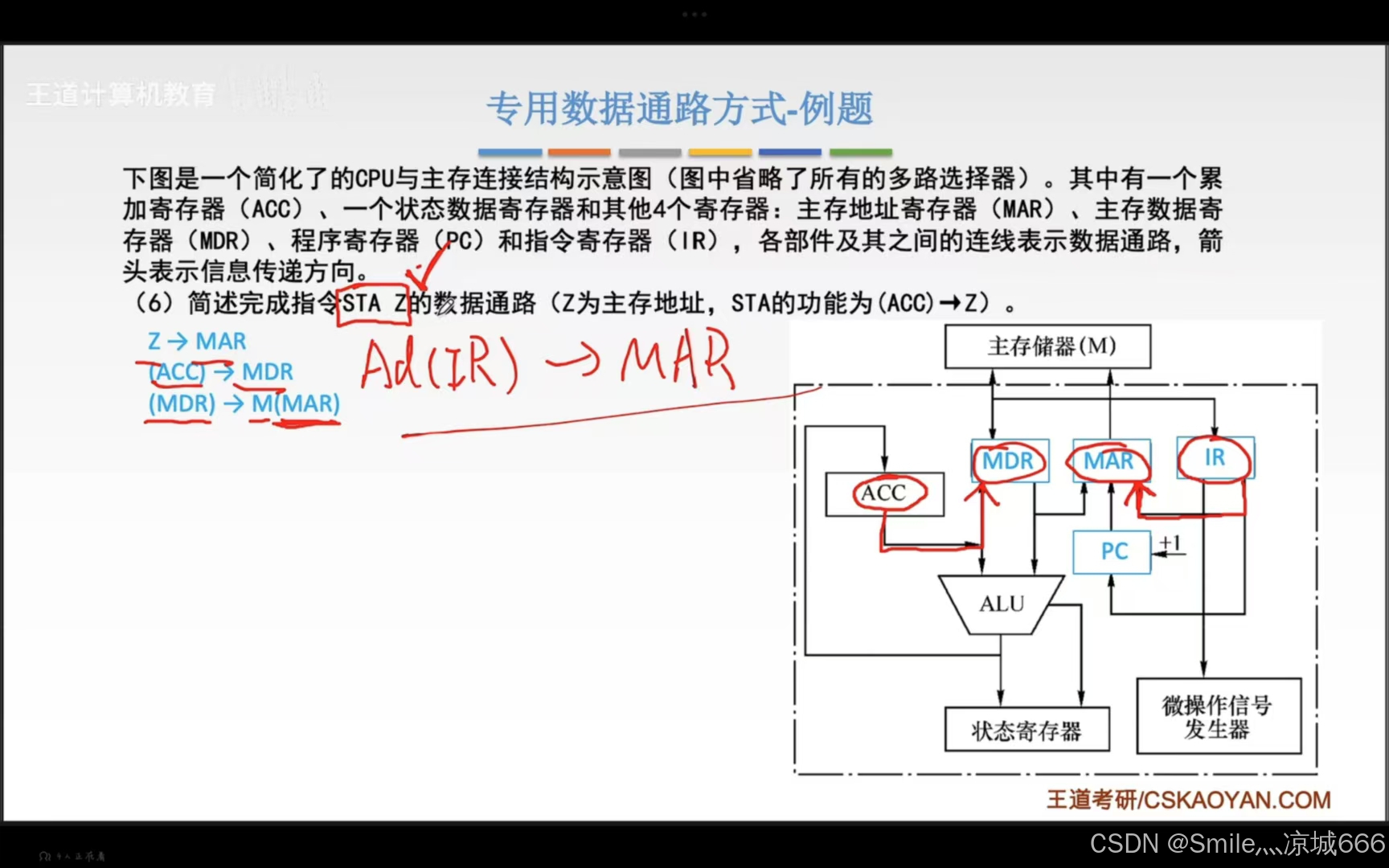

5.3_2数据通路-专用通路结构

ALU中的数据储存在ACC中

例题

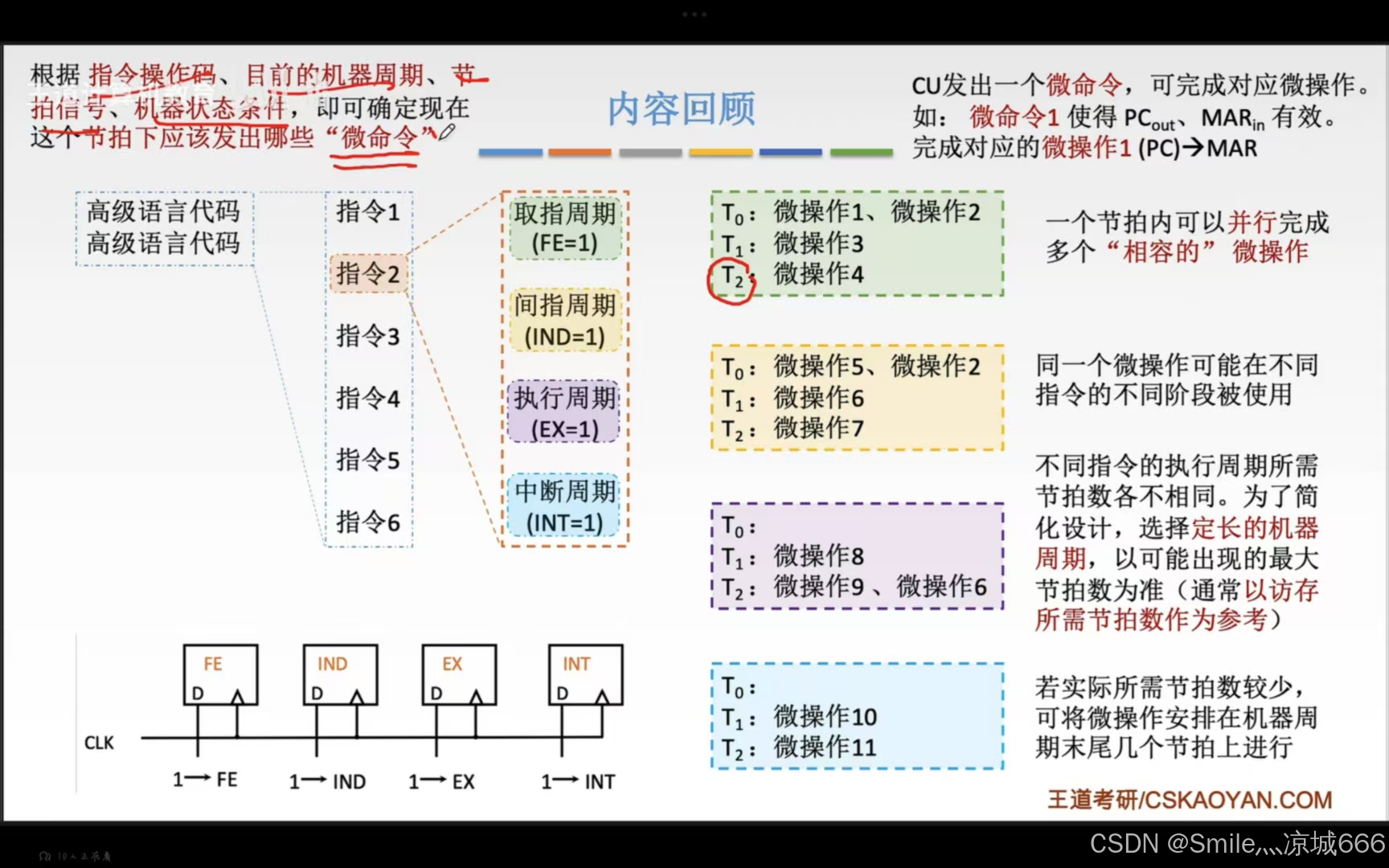

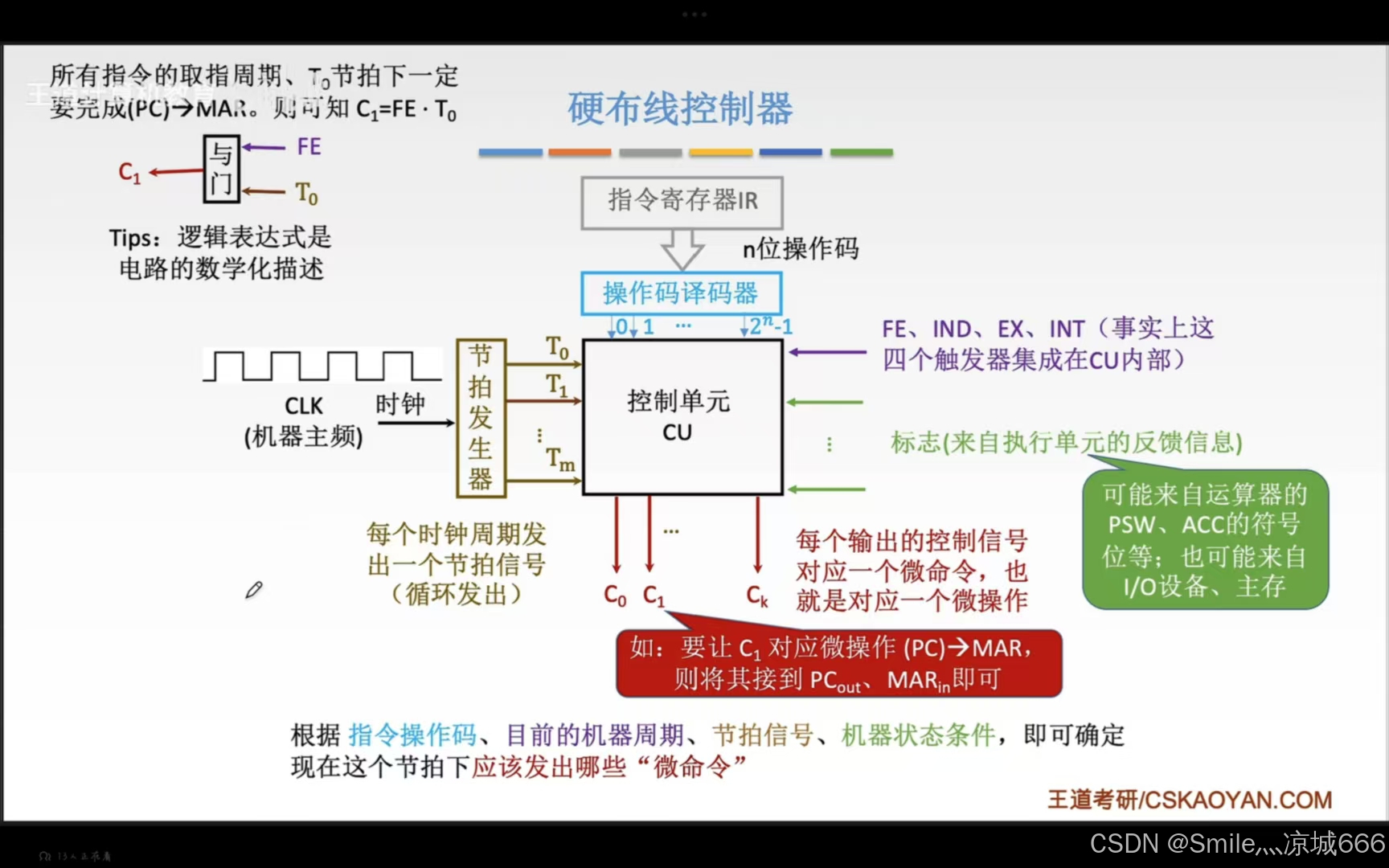

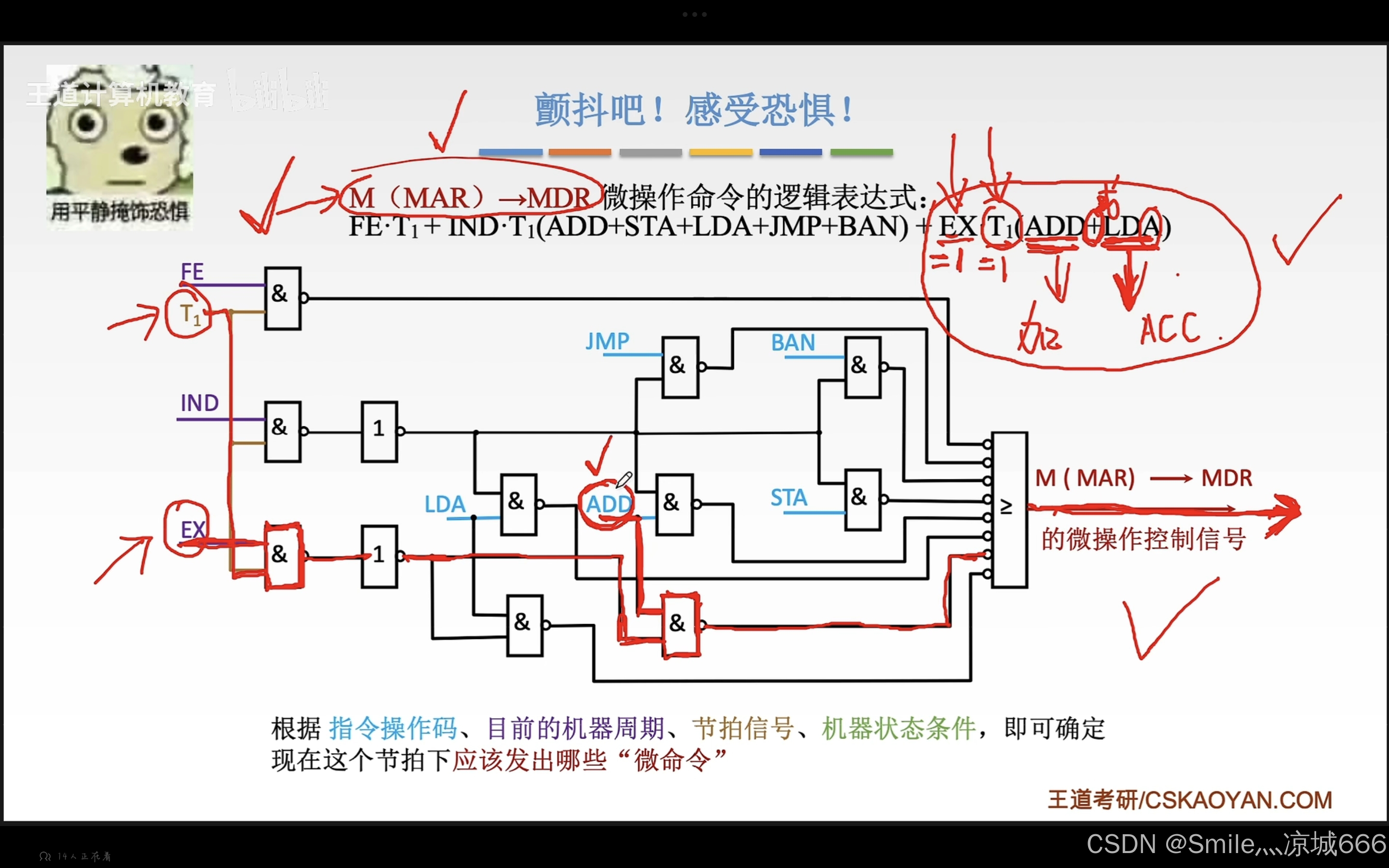

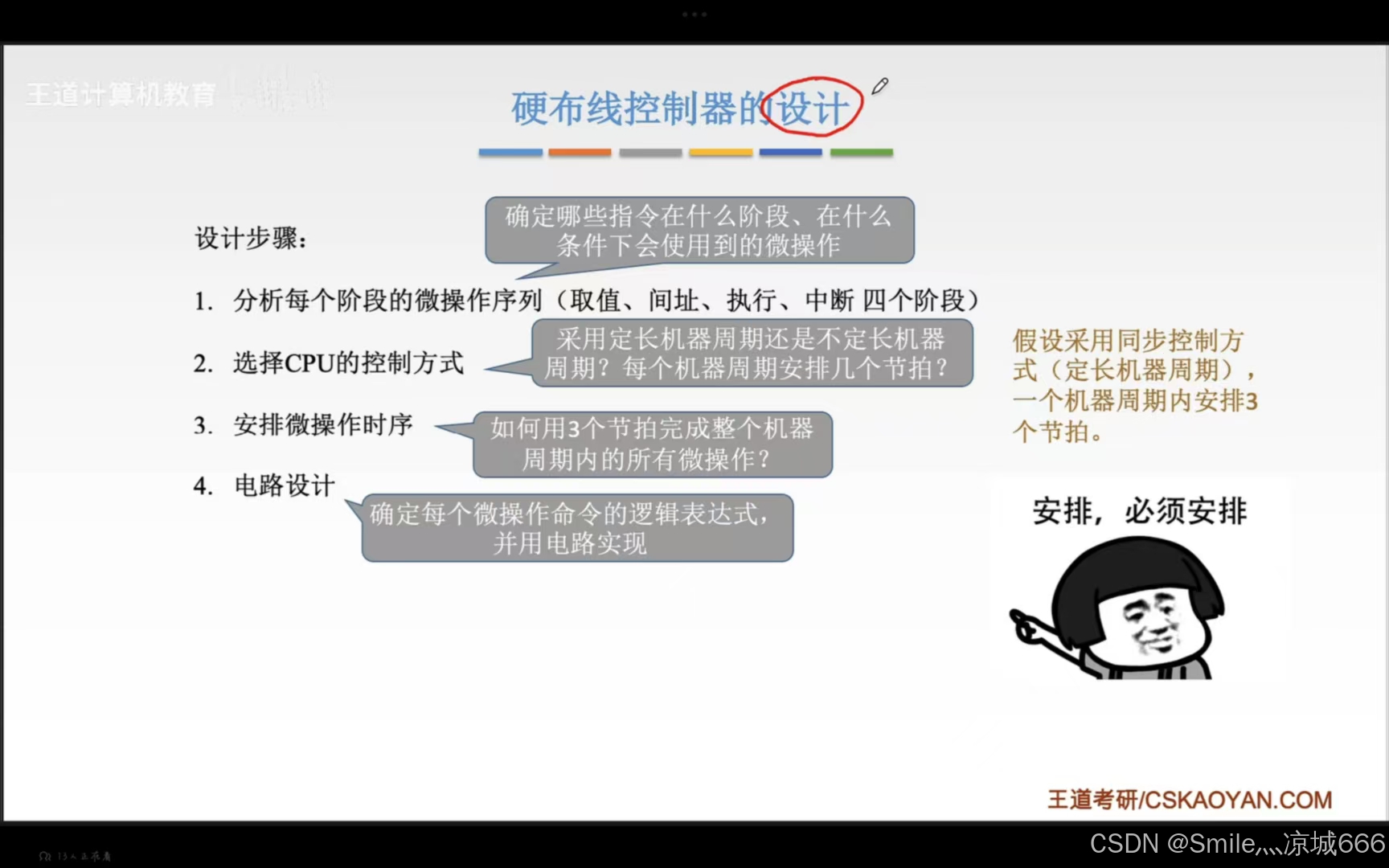

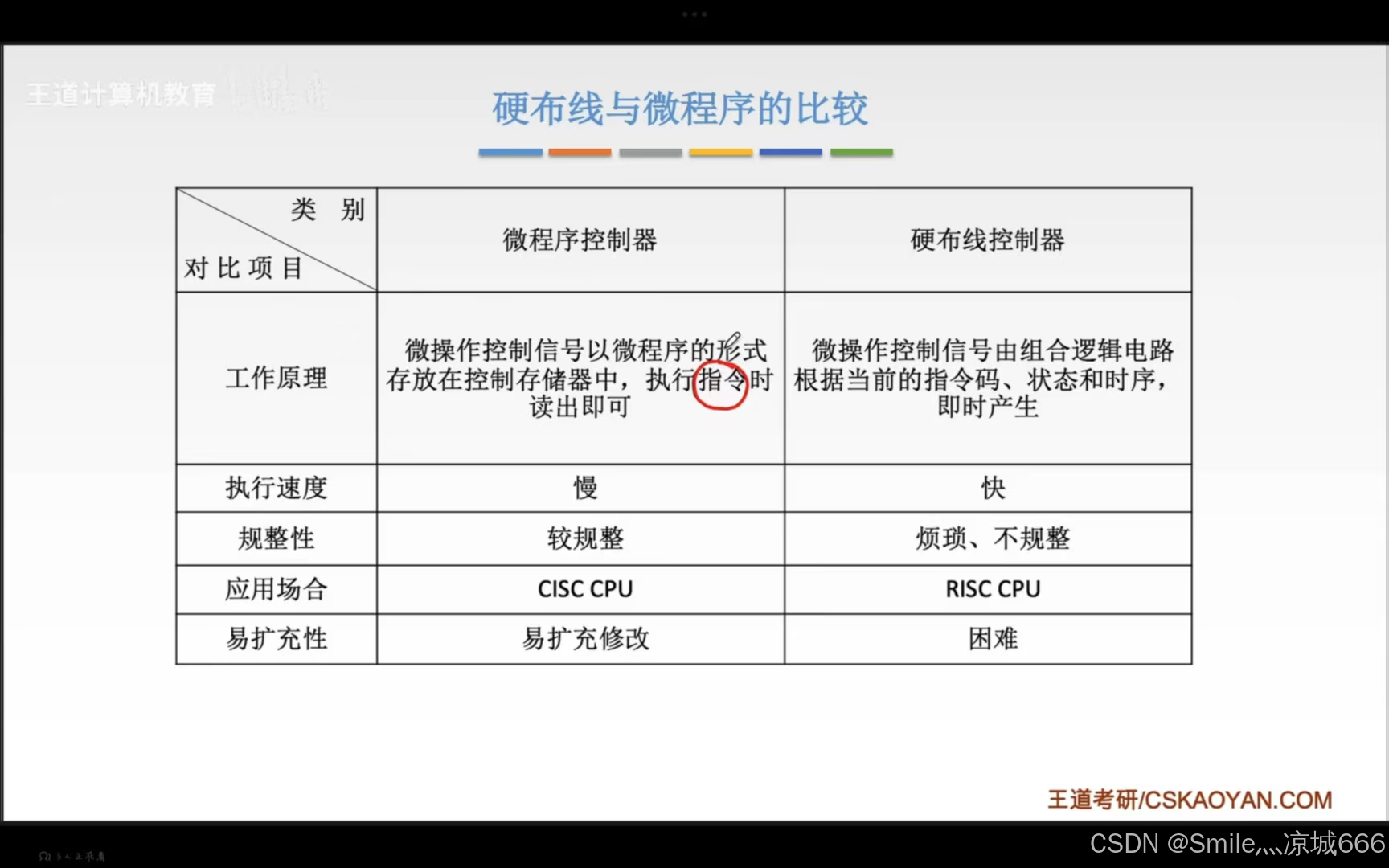

5.4_1硬布线控制器

内容回顾

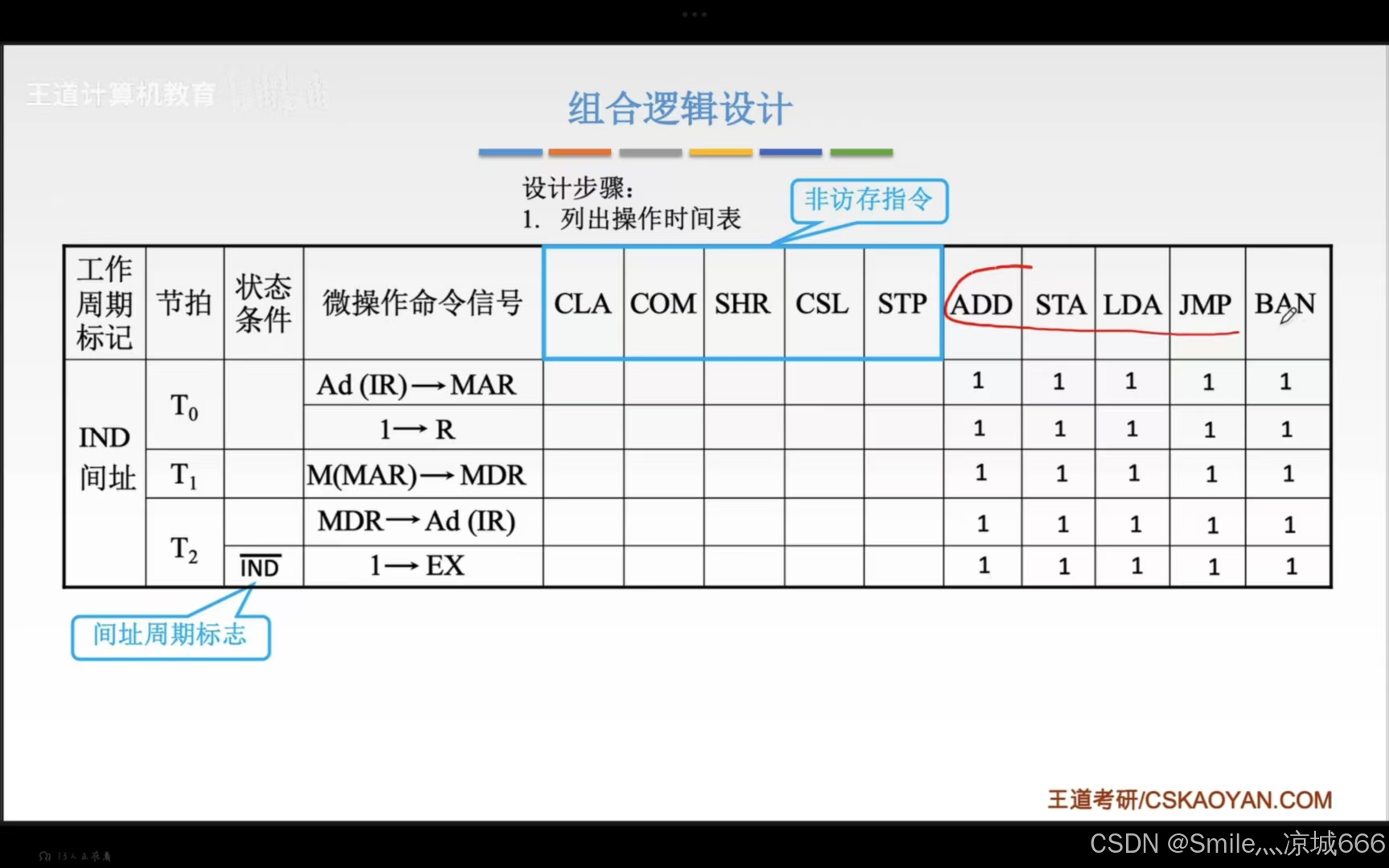

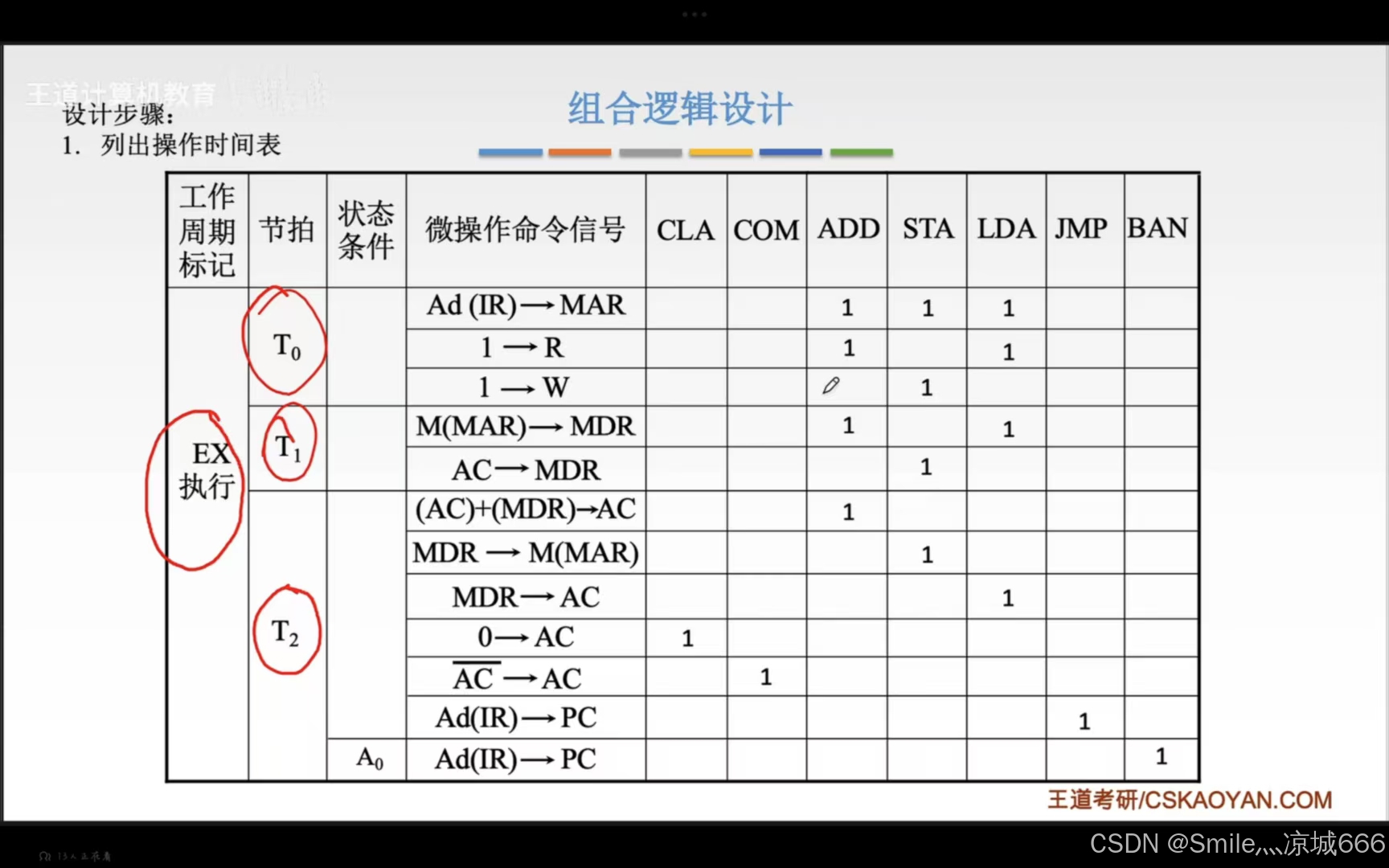

设计步骤

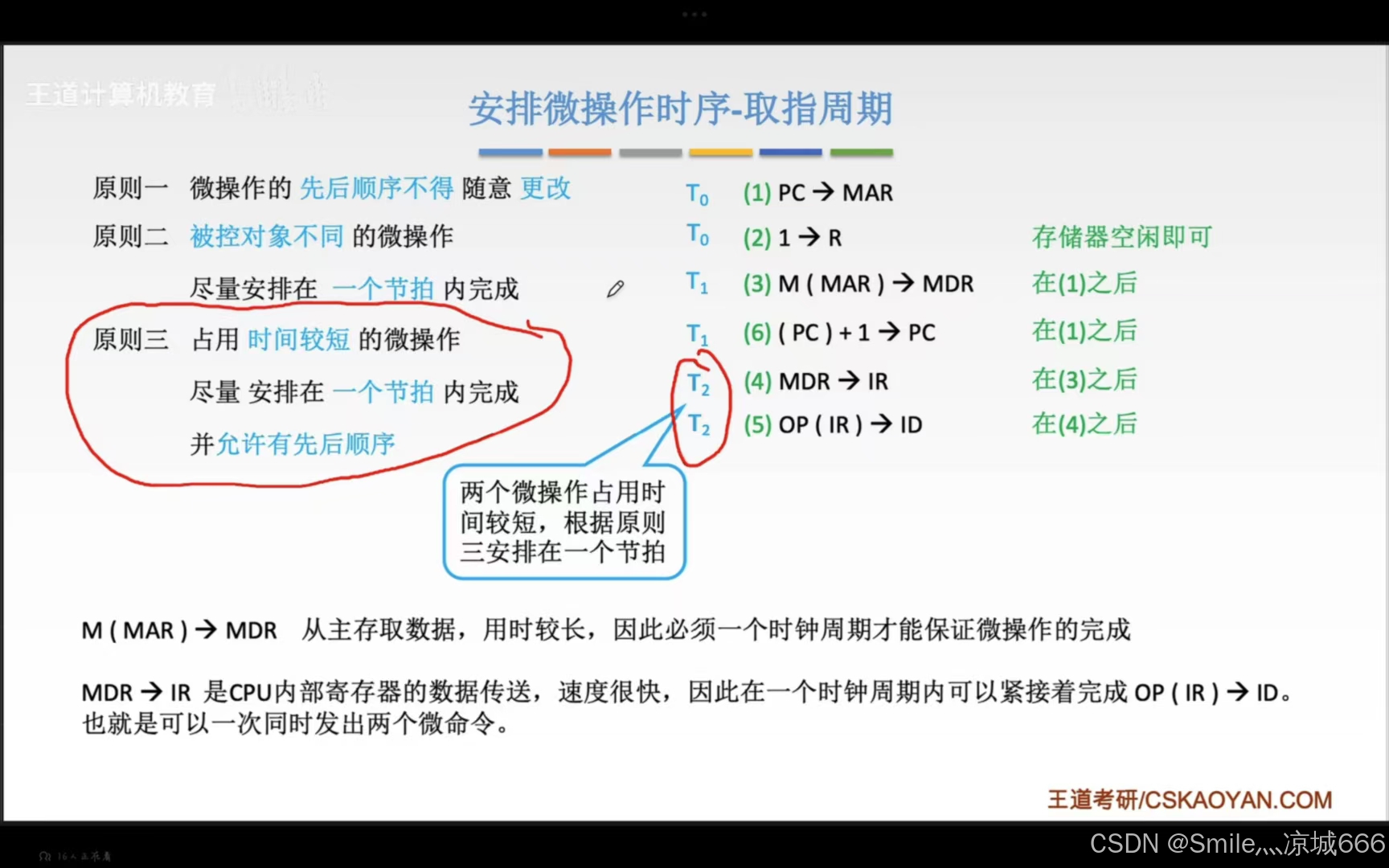

取址周期

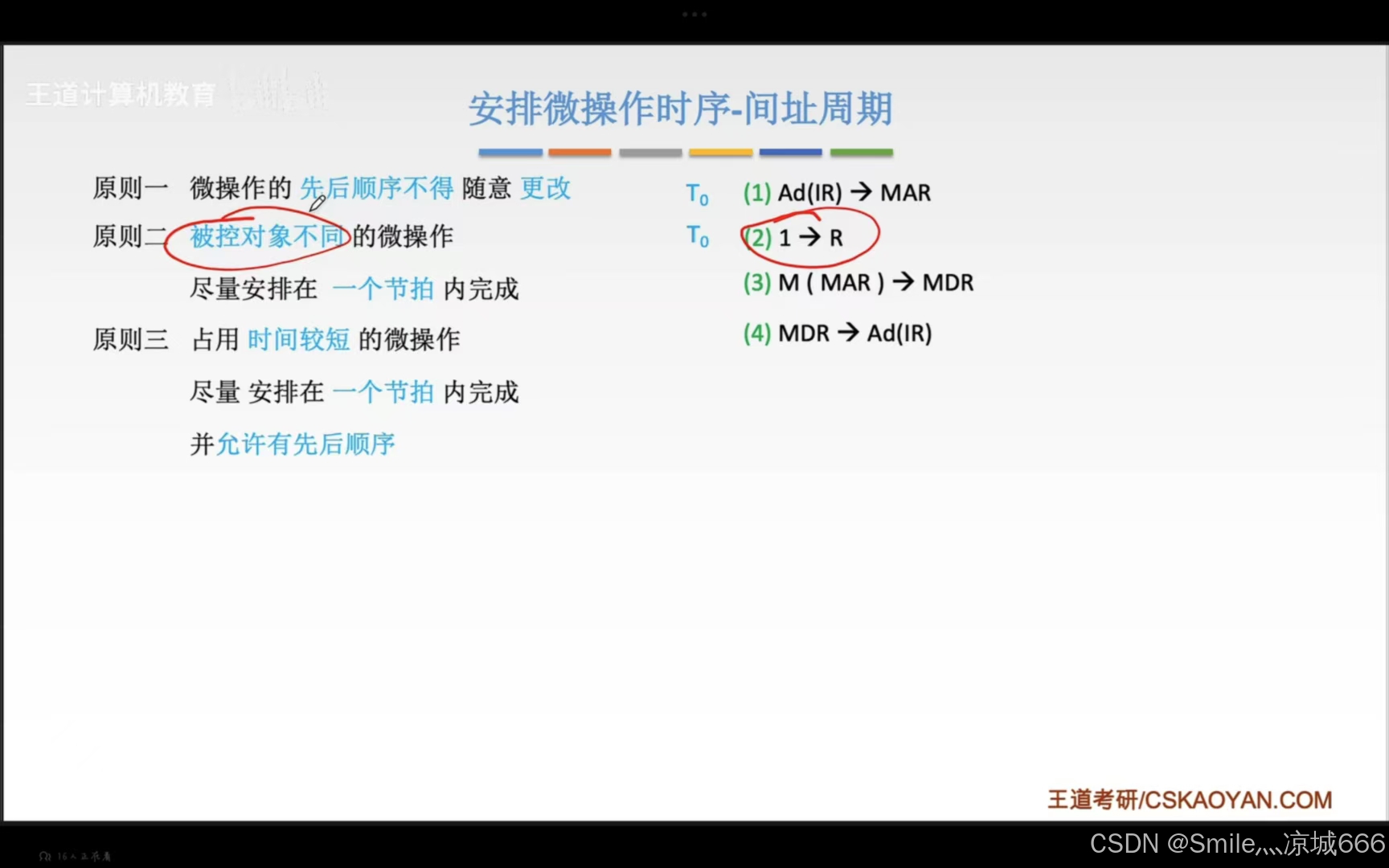

间址周期

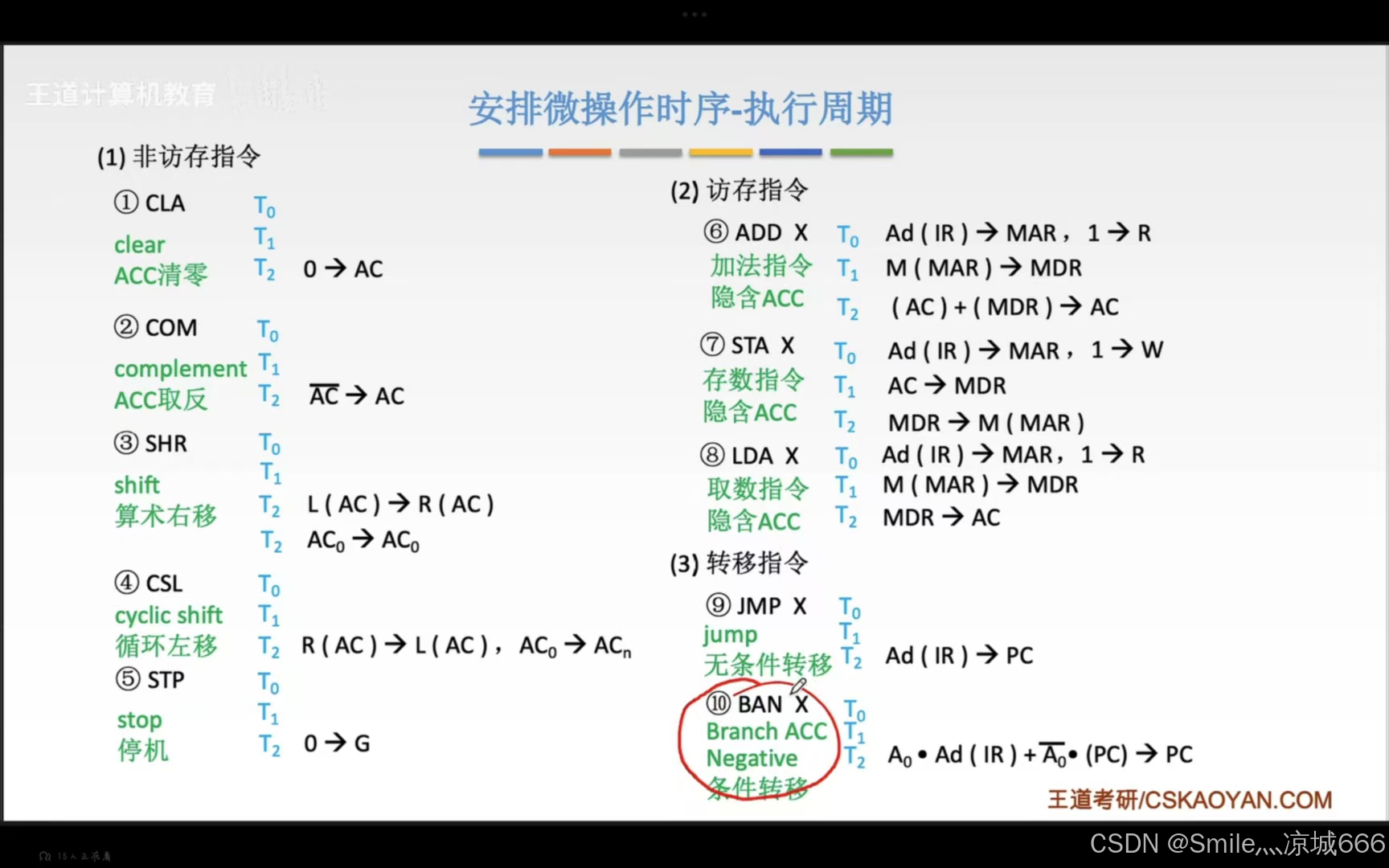

执行周期

要判断IND是否为0,不为0继续进行间址周期

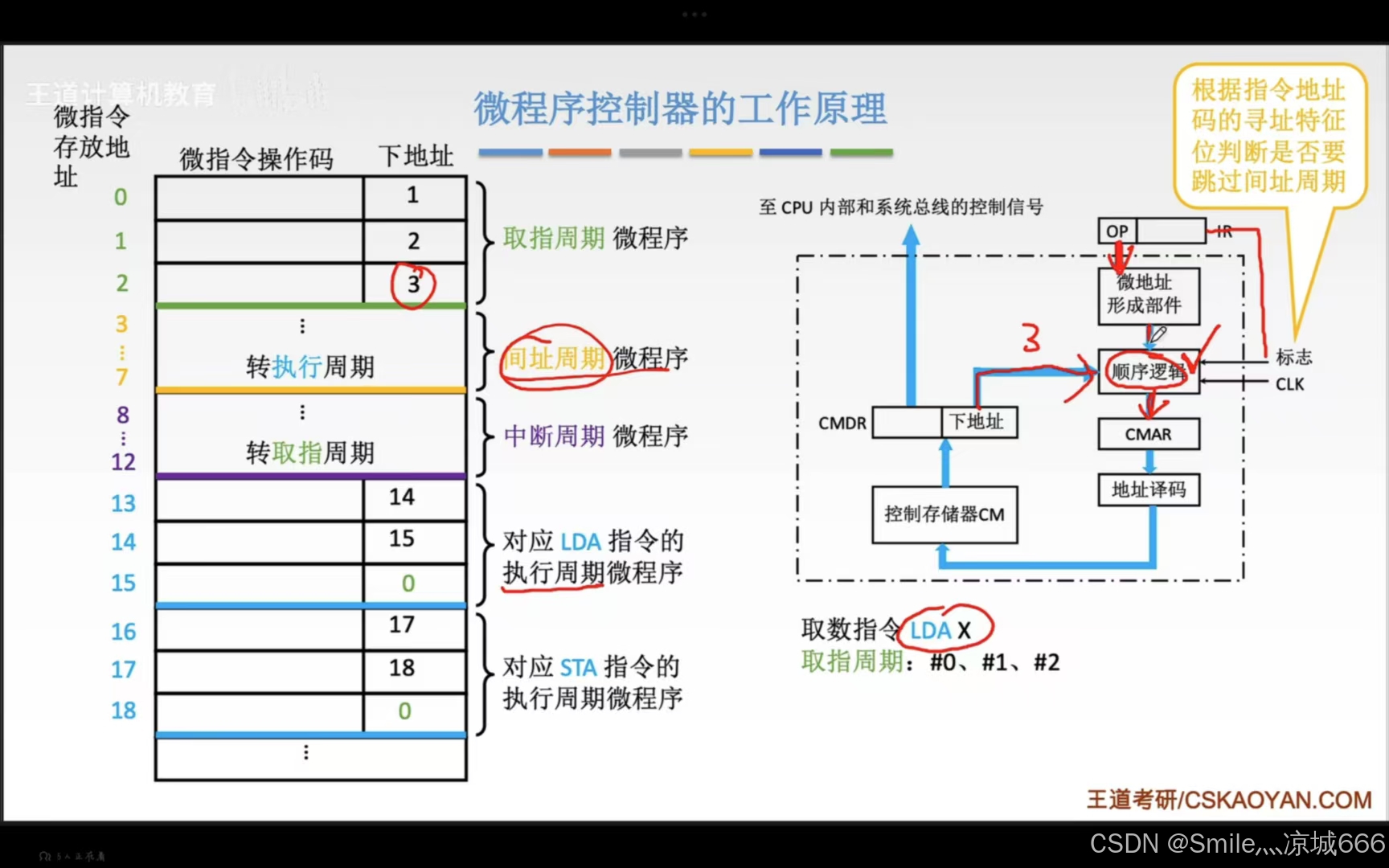

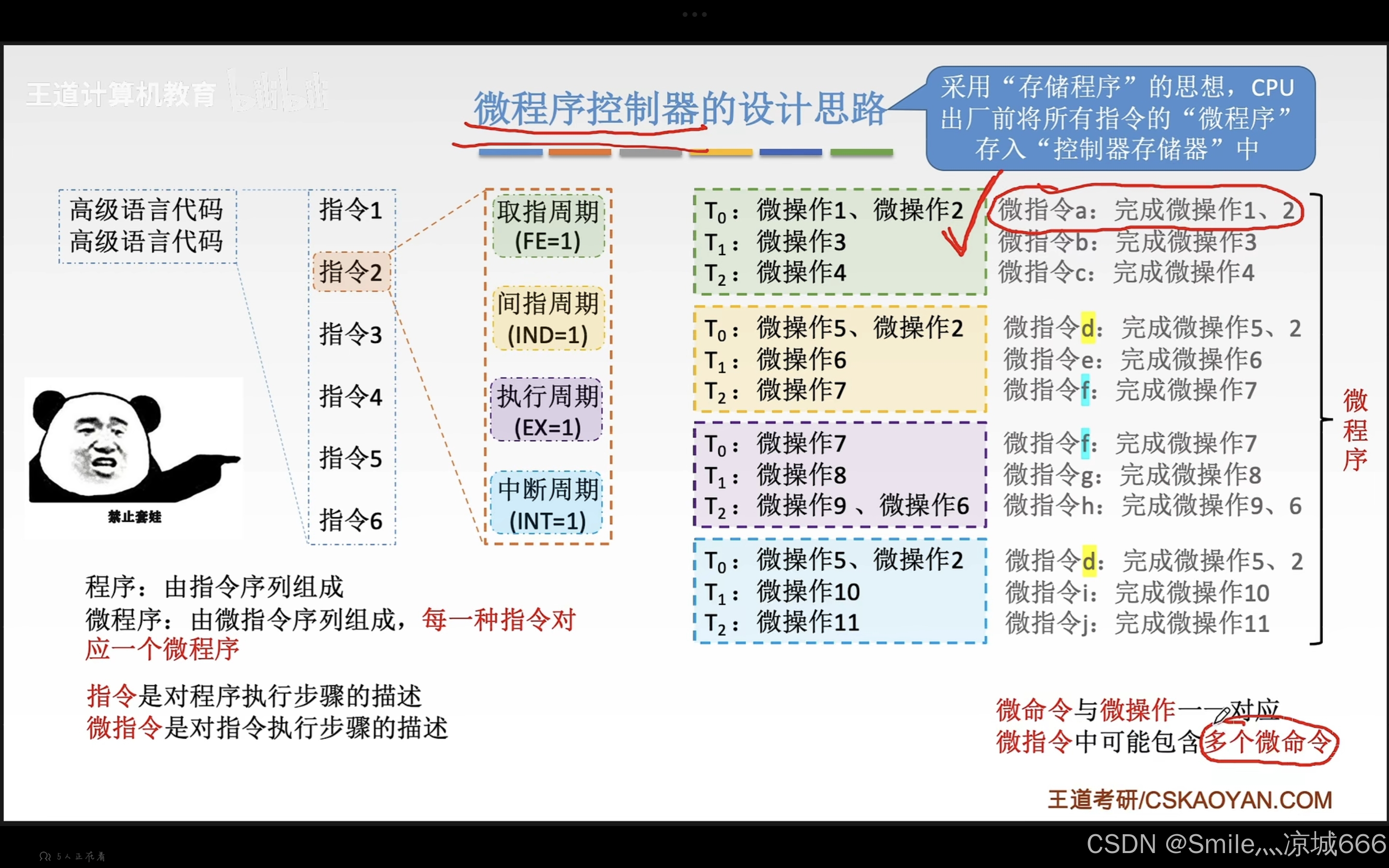

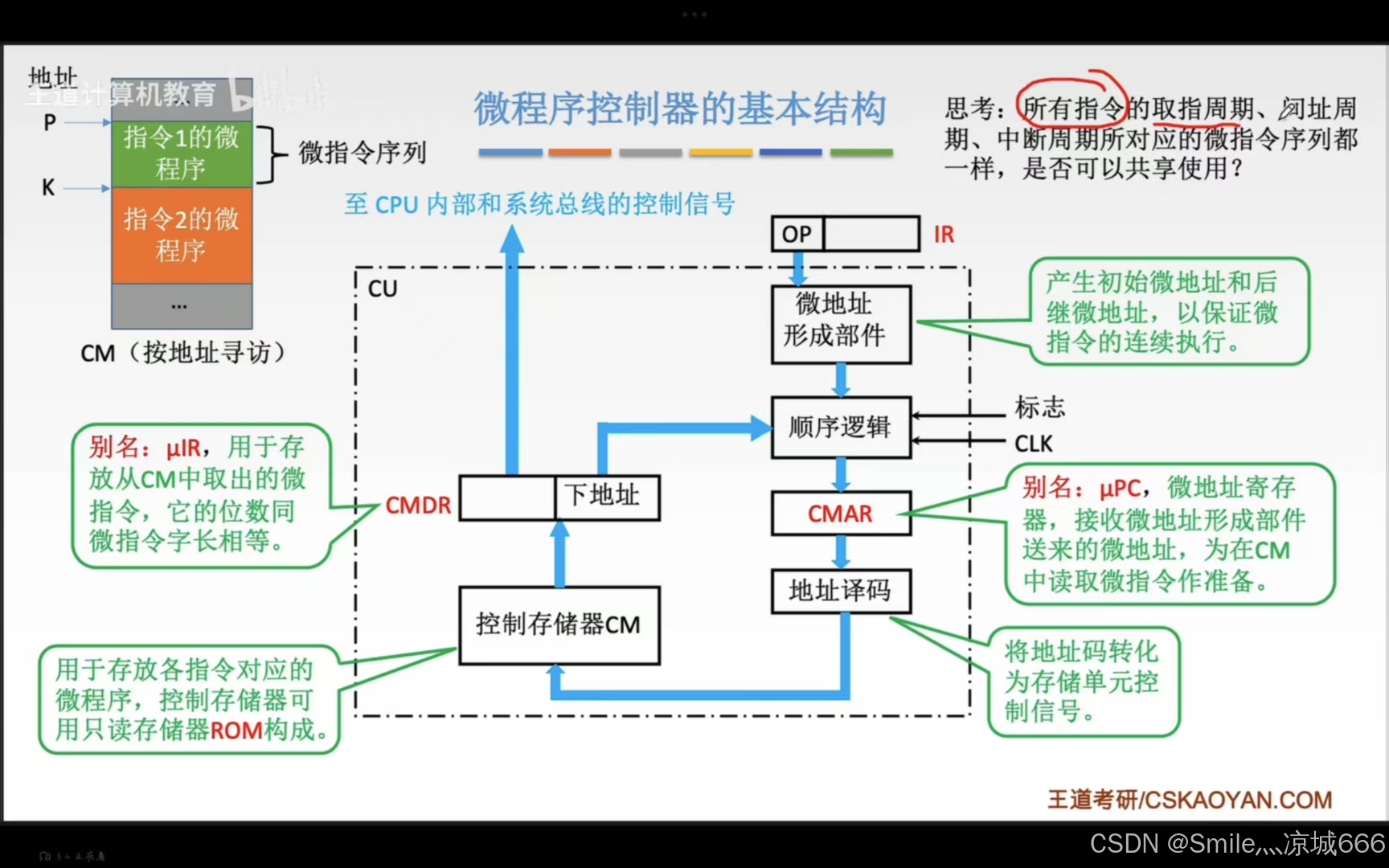

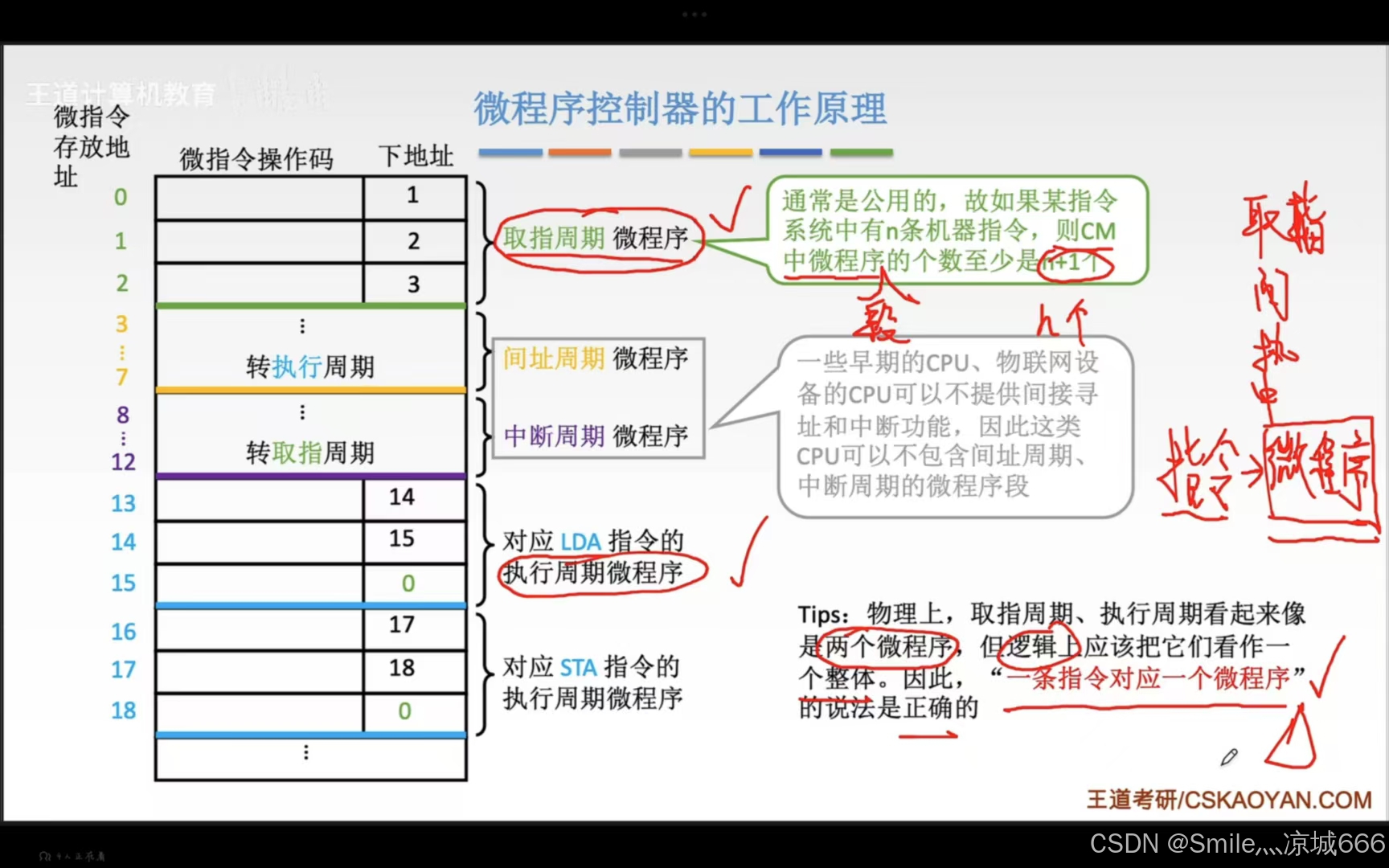

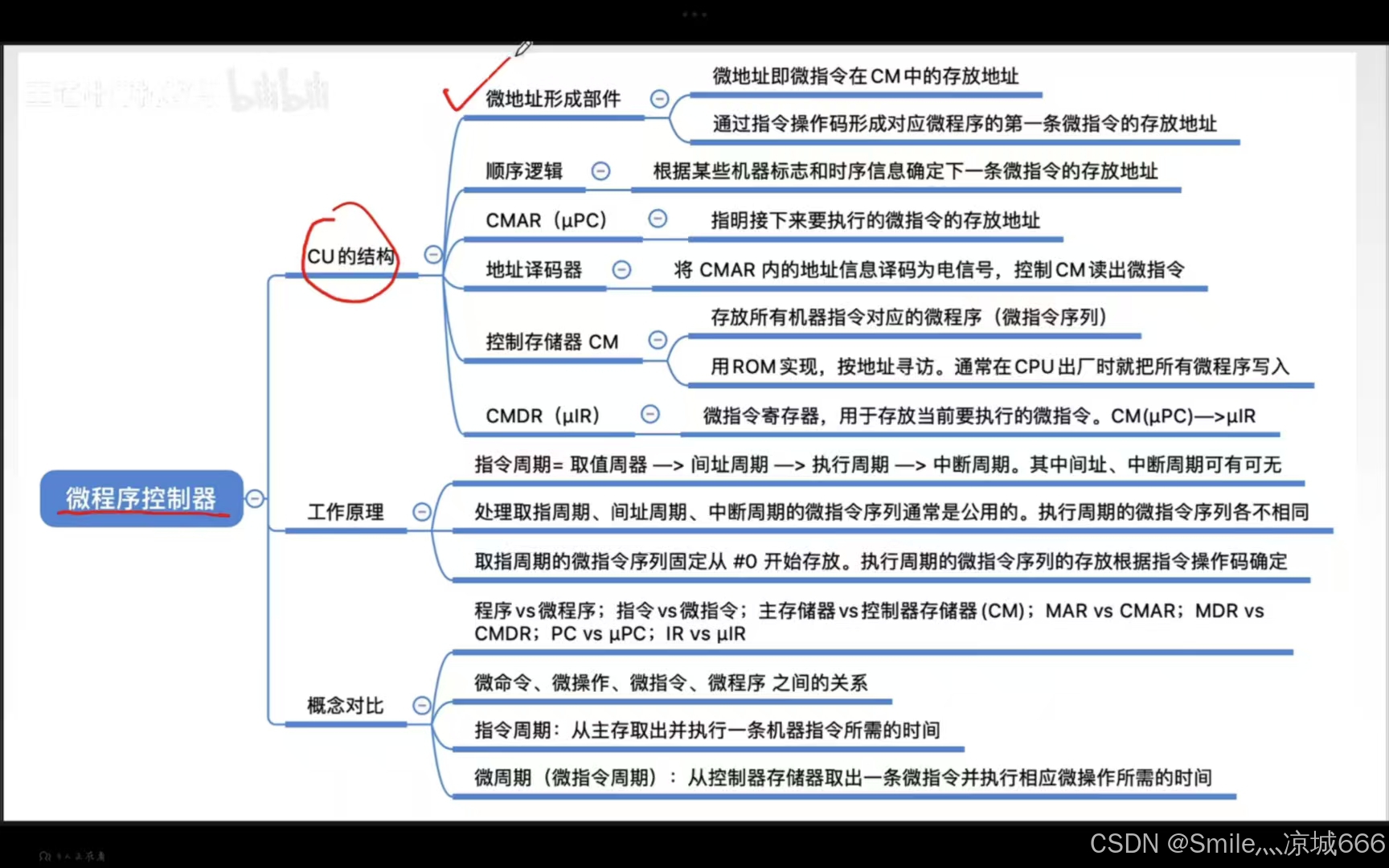

5.4_2微程序控制器的基本原理

顺序逻辑的会检测标志位,根据标志位判断是否需要进行间址周期和中断周期

5.4_3微指令的设计

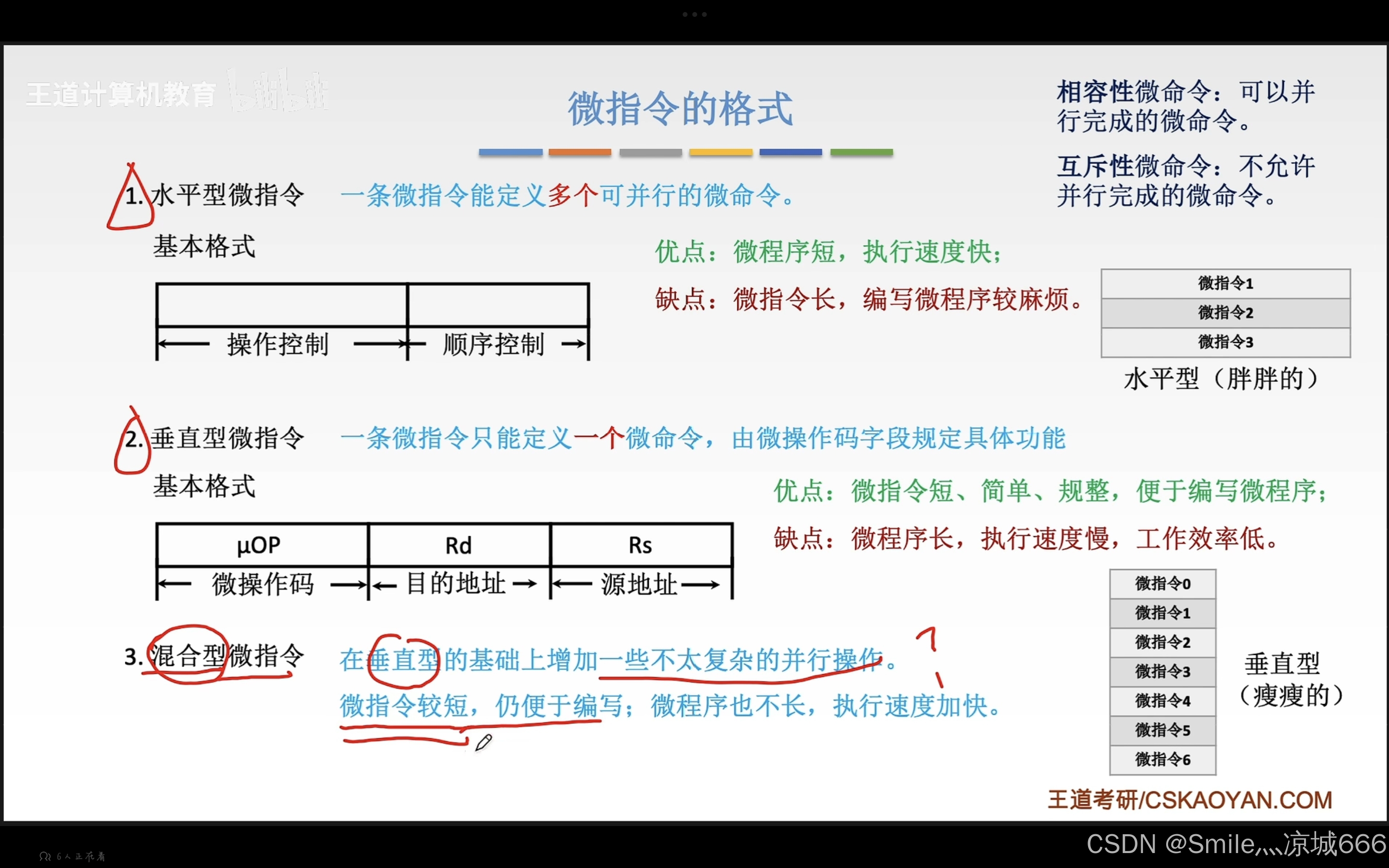

微命令的格式

相容性微命令:可以并行完成微命令

互斥性微命令:不允许并行完成微命令

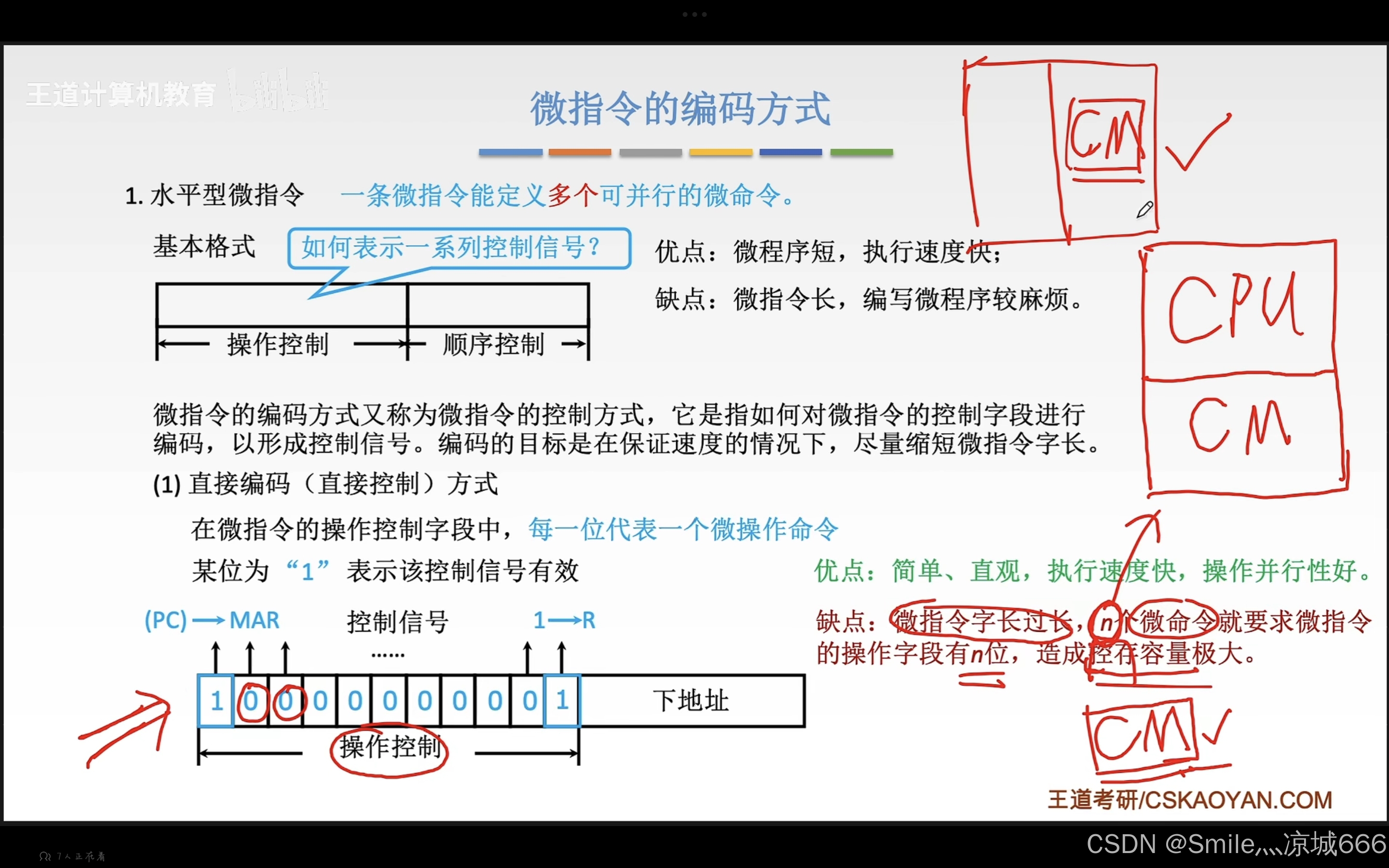

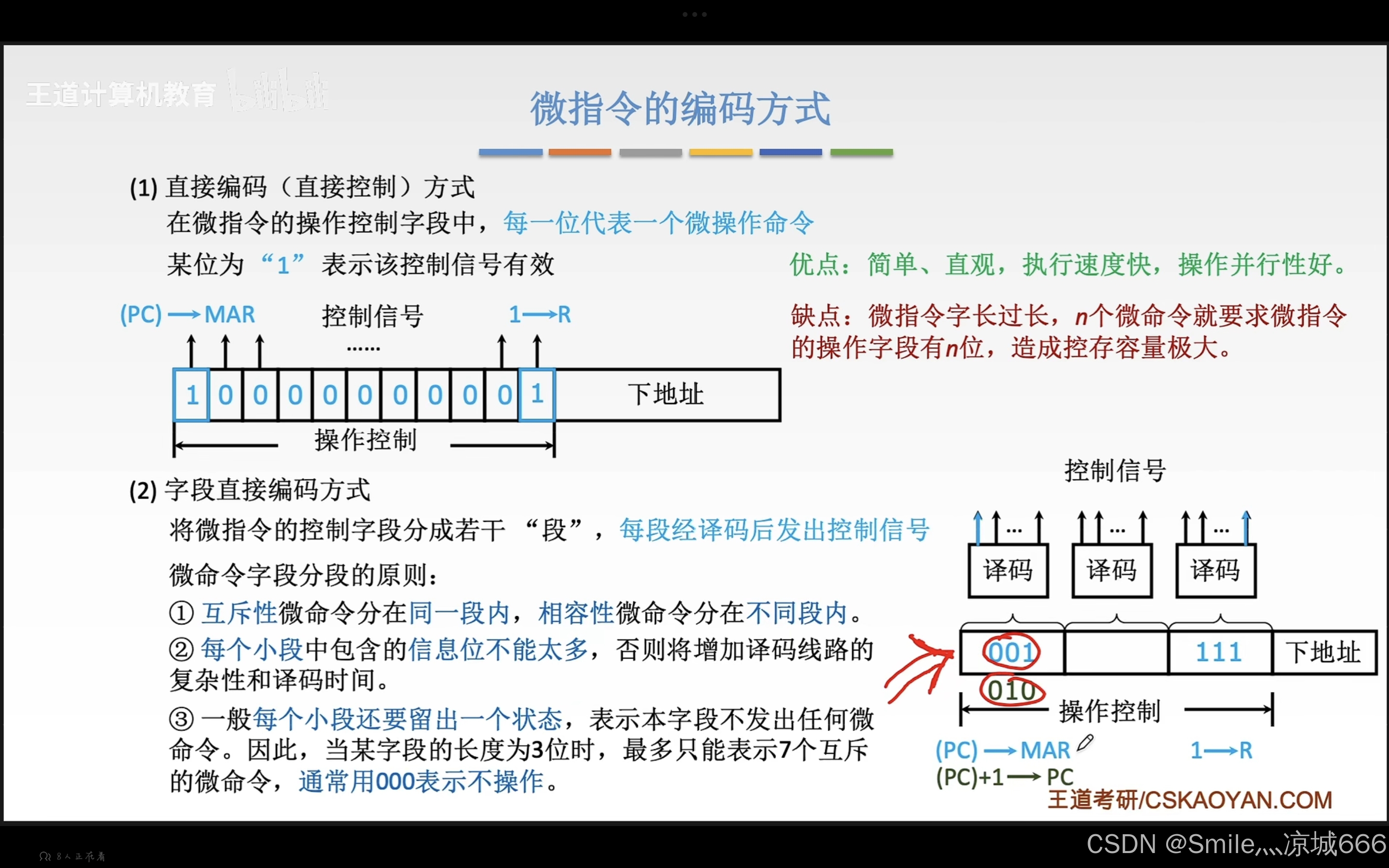

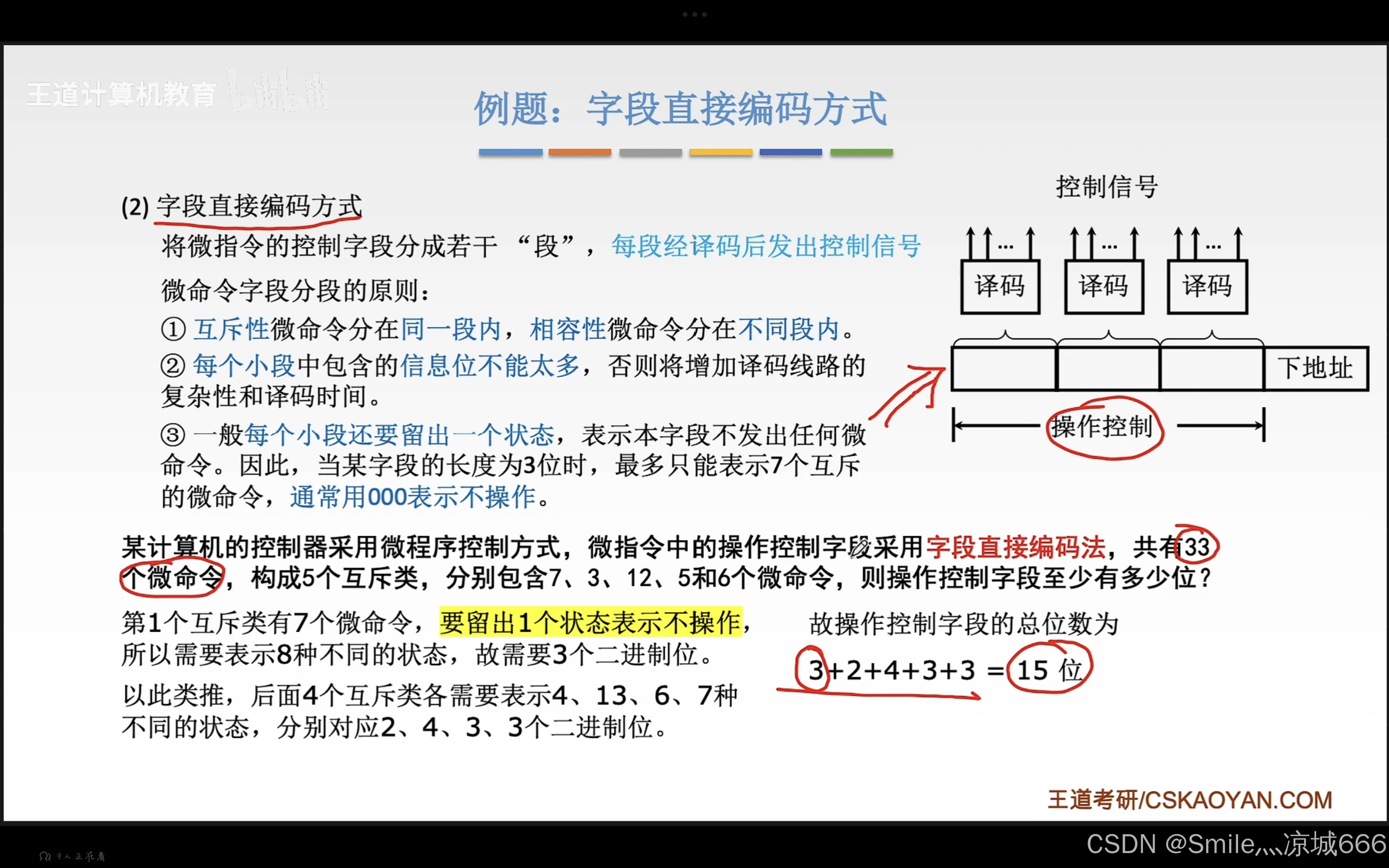

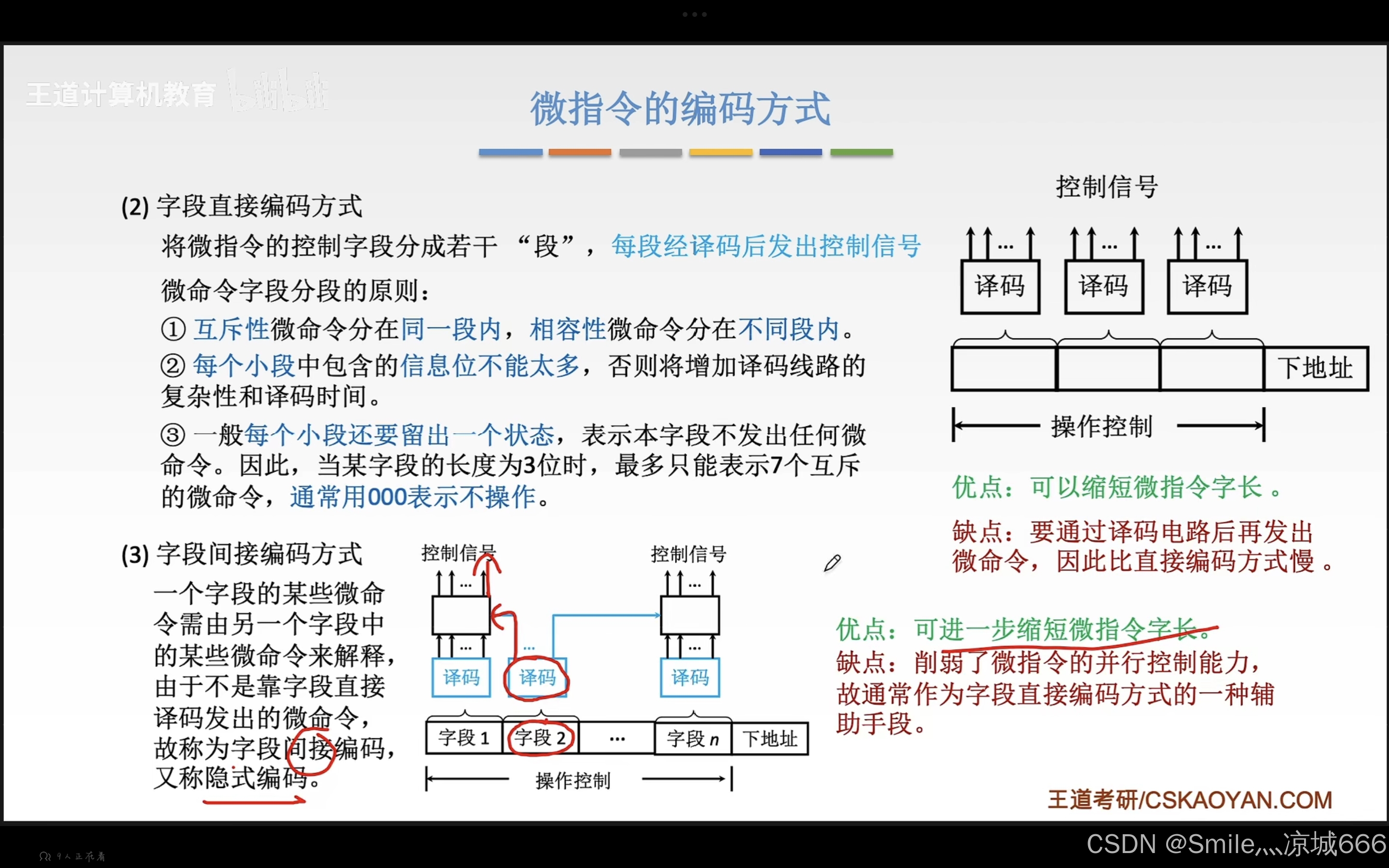

微指令的编码方式

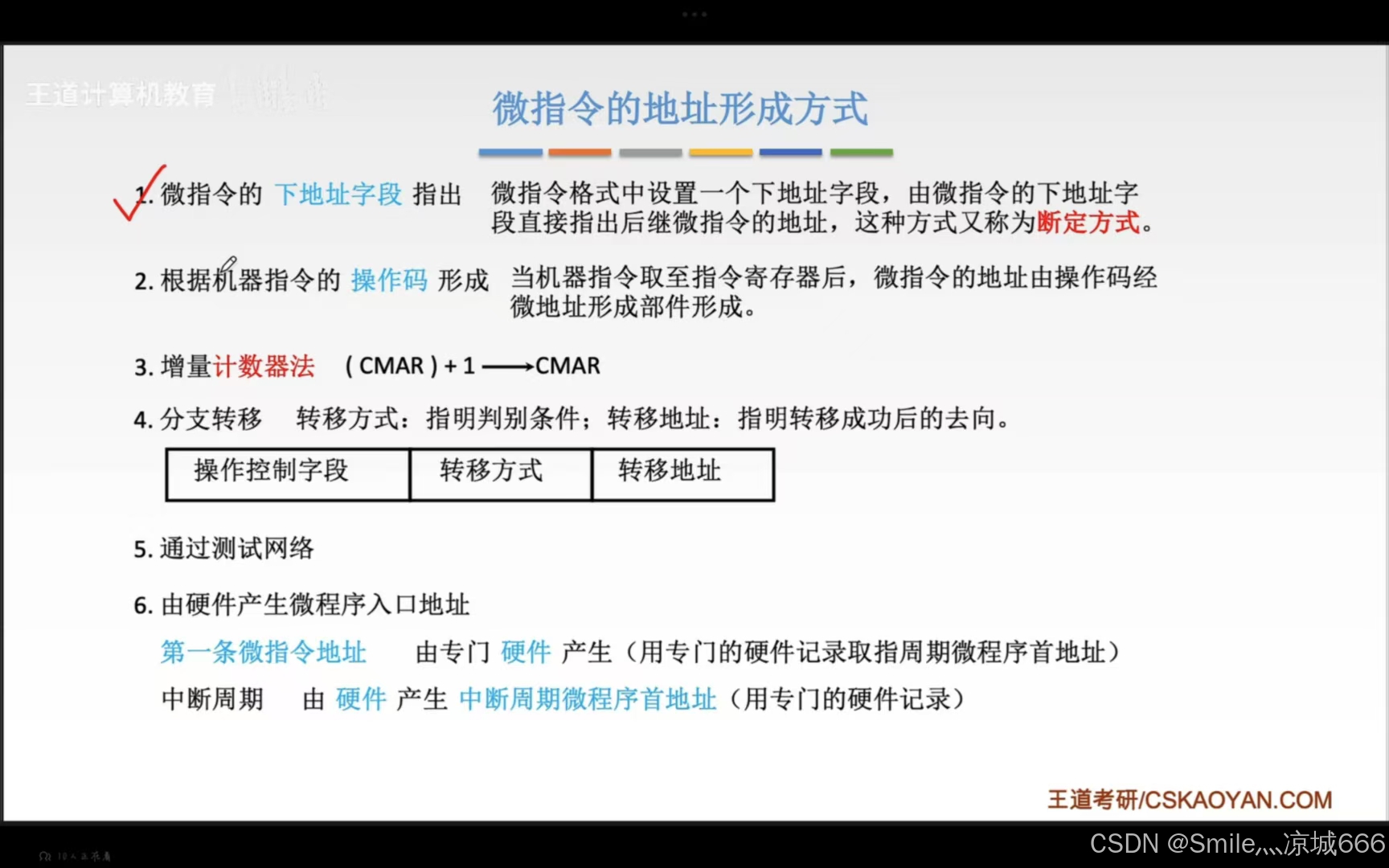

微指令的地址形成

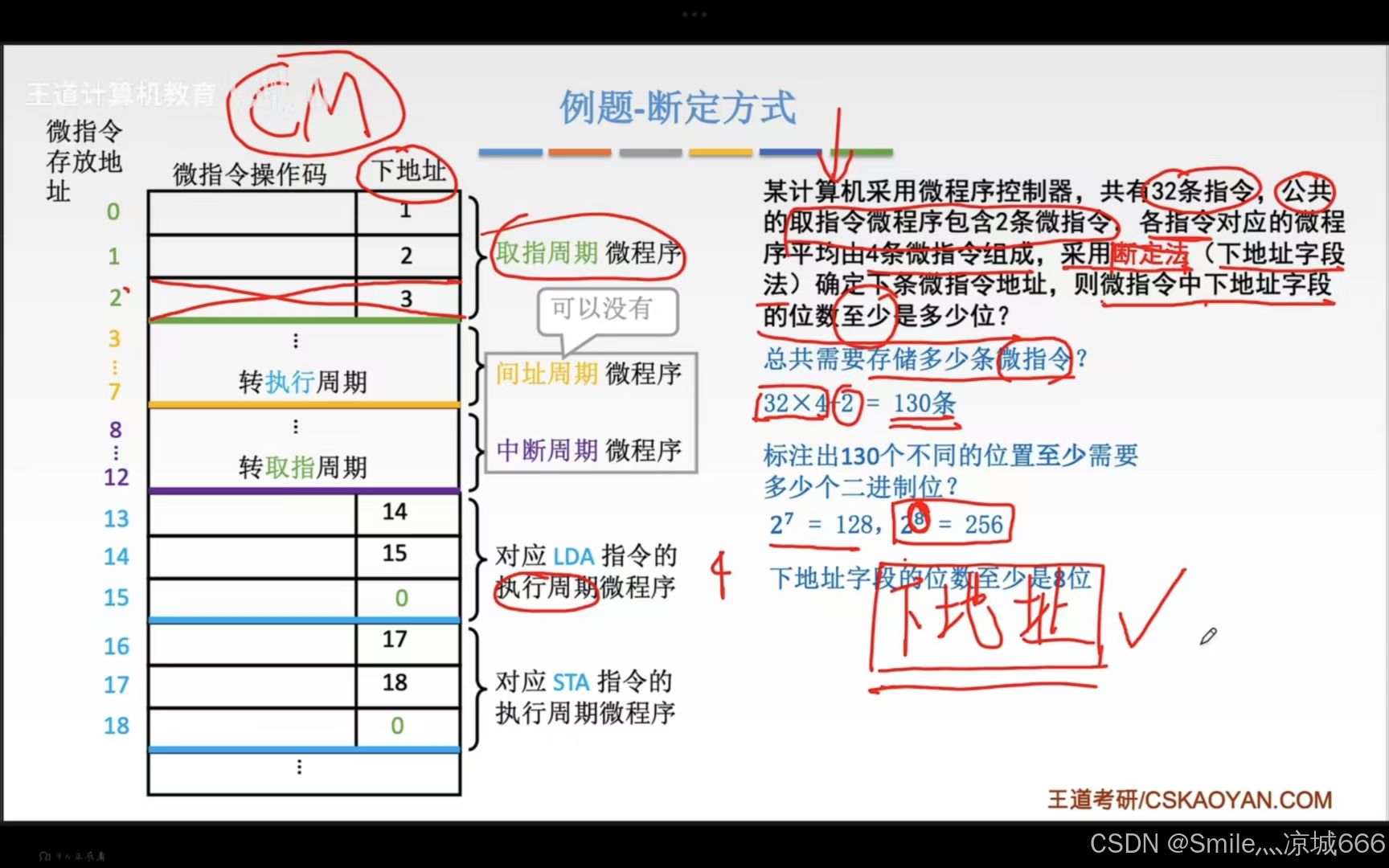

例题

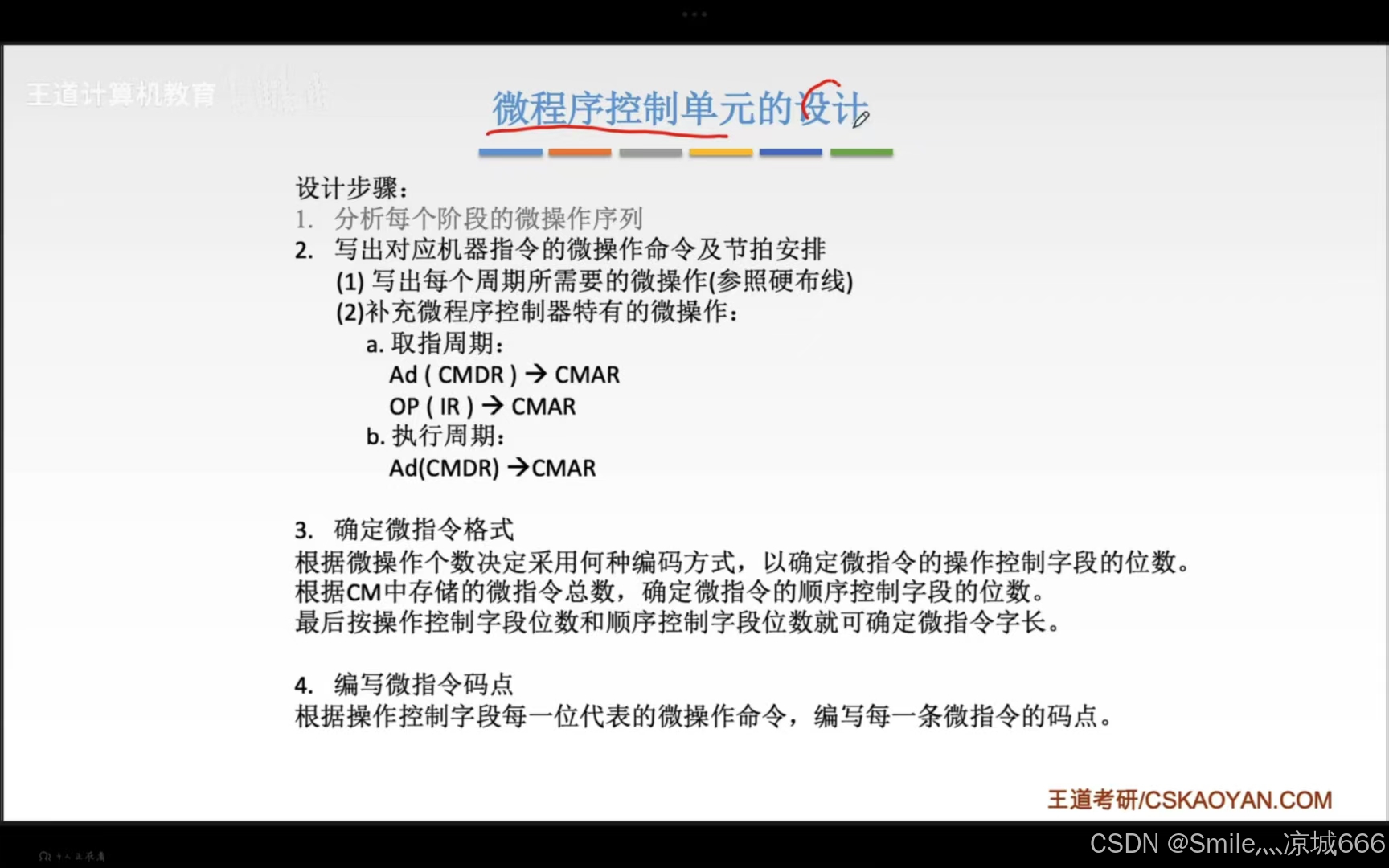

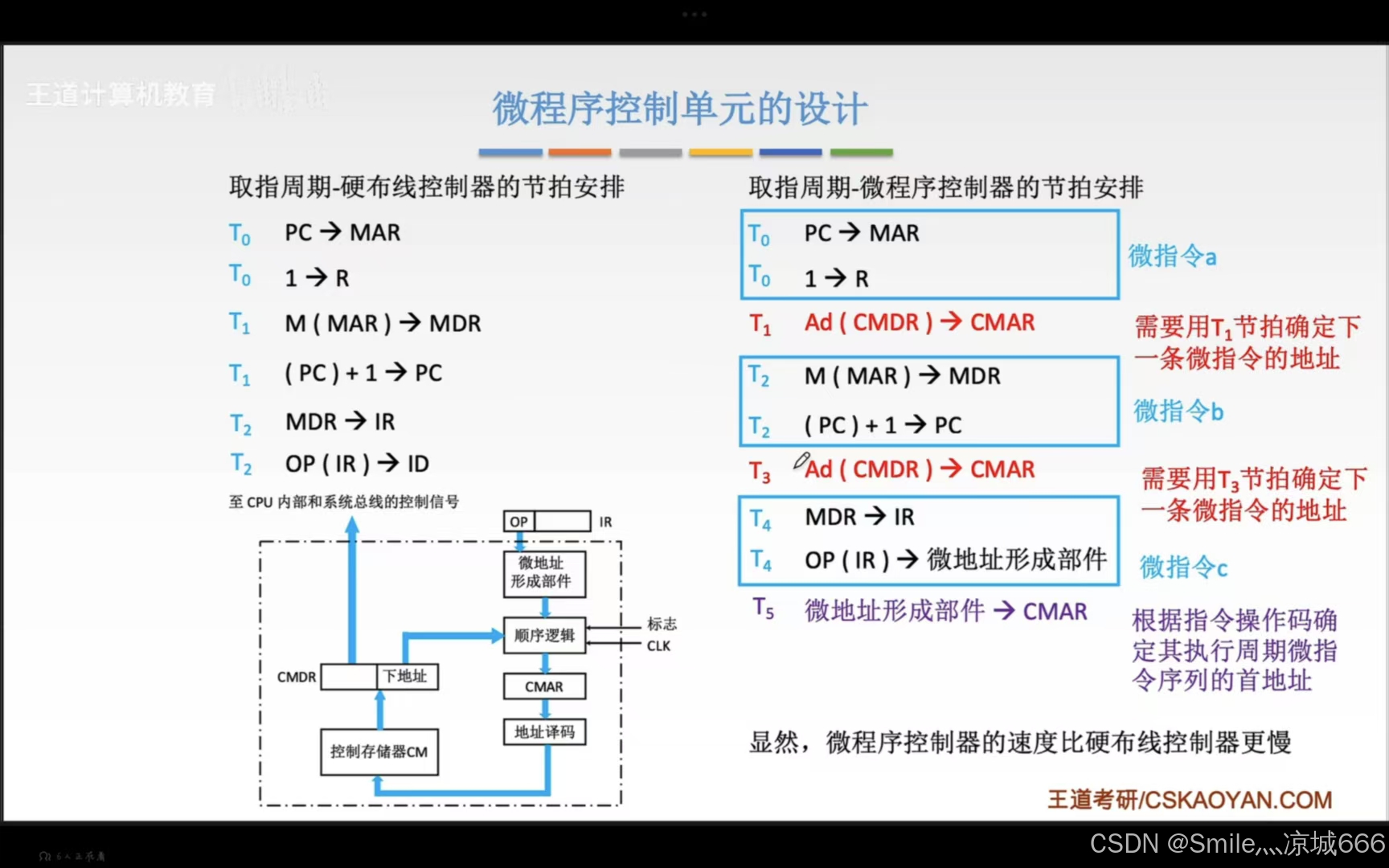

5.4_4微程序控制单元的设计

设计

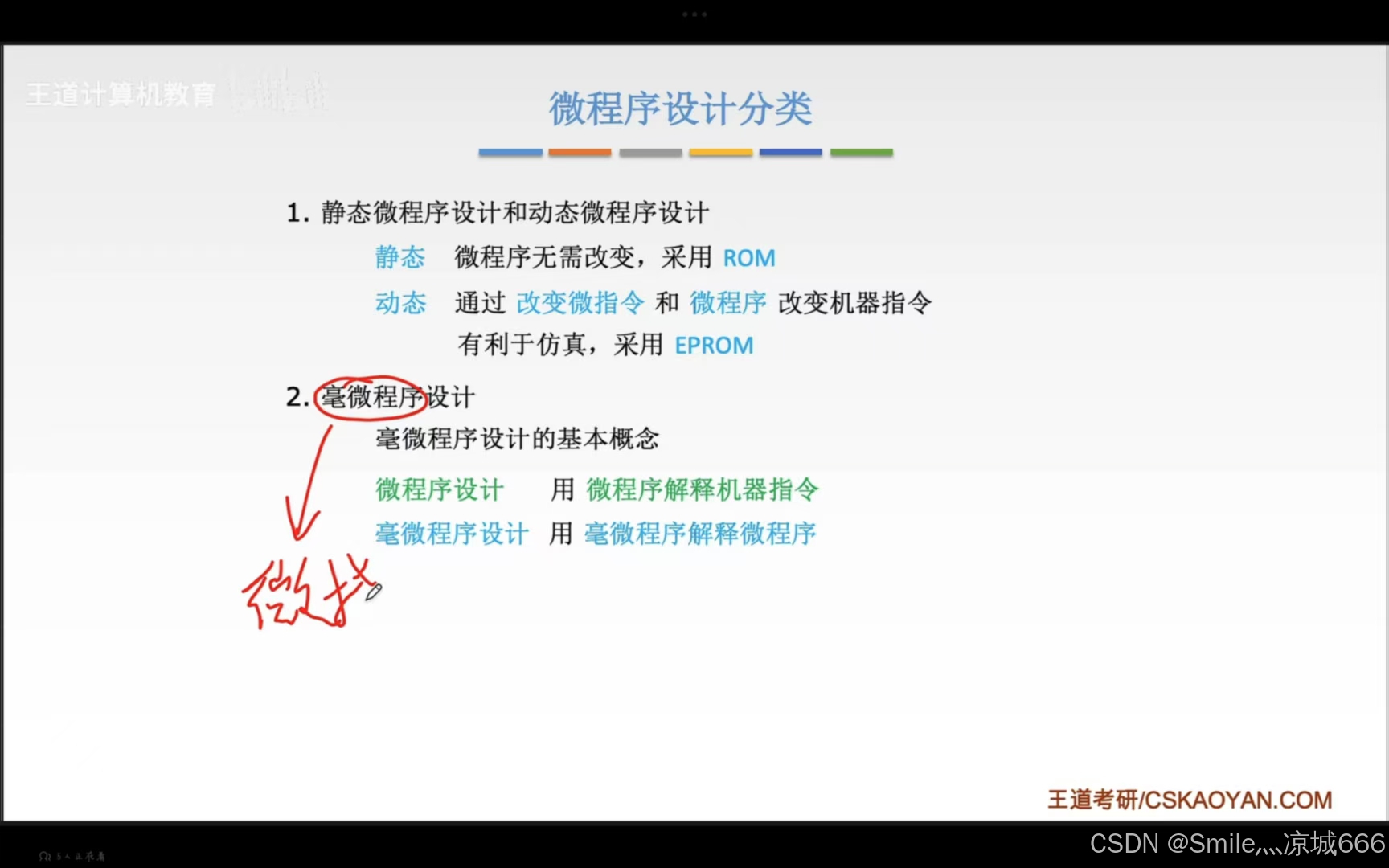

分类

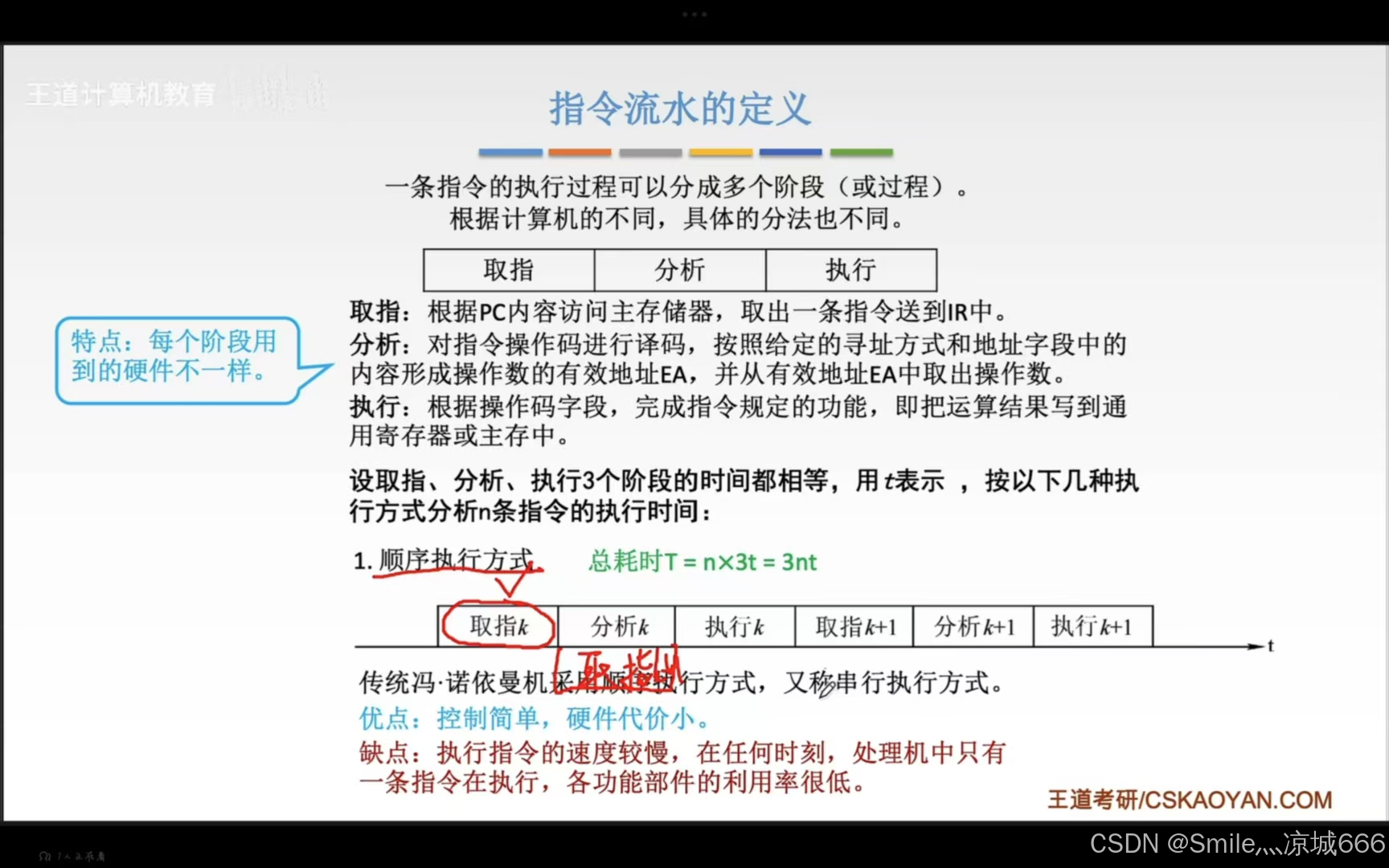

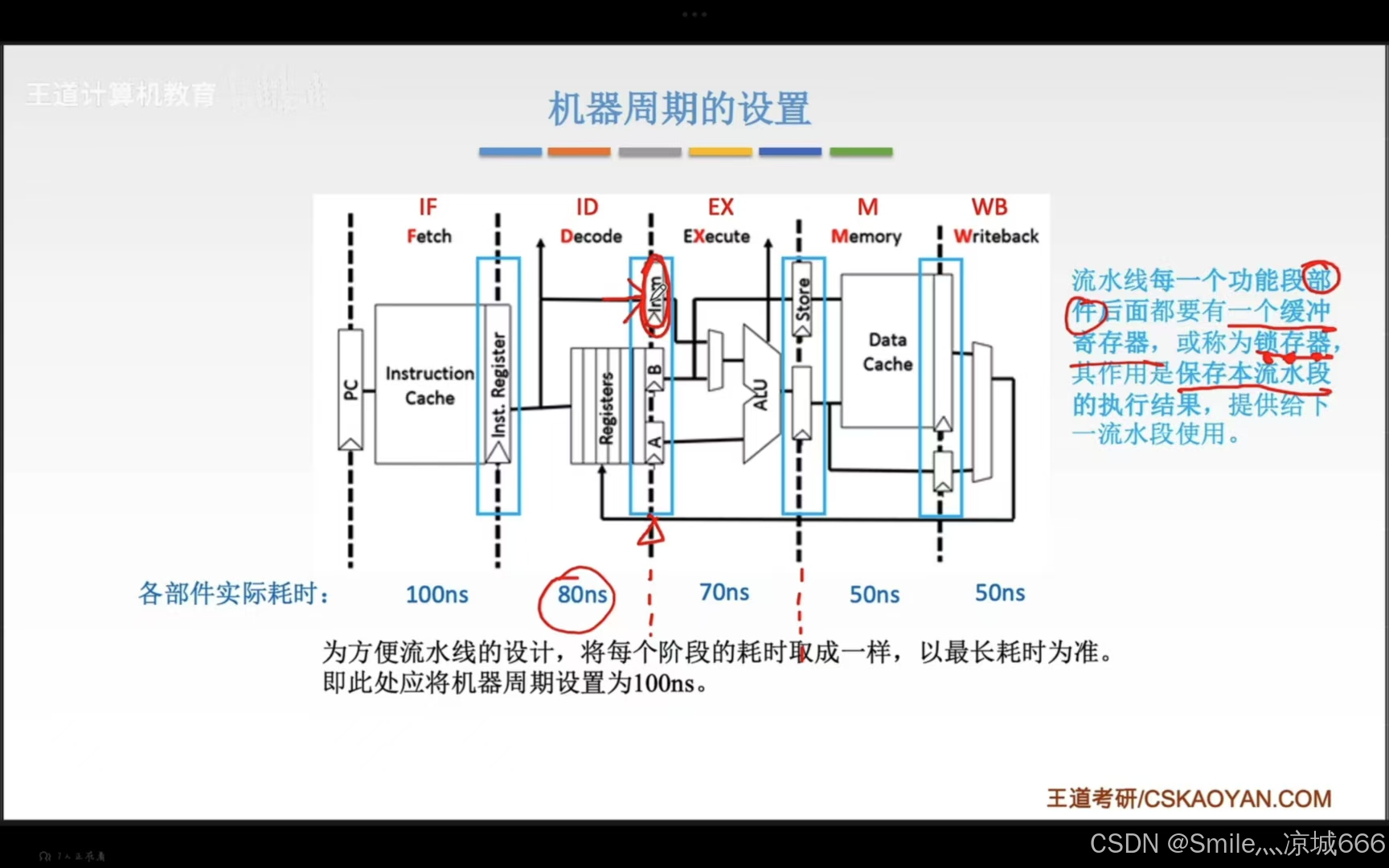

5.6_1指令流水线的基本概念和性能指标

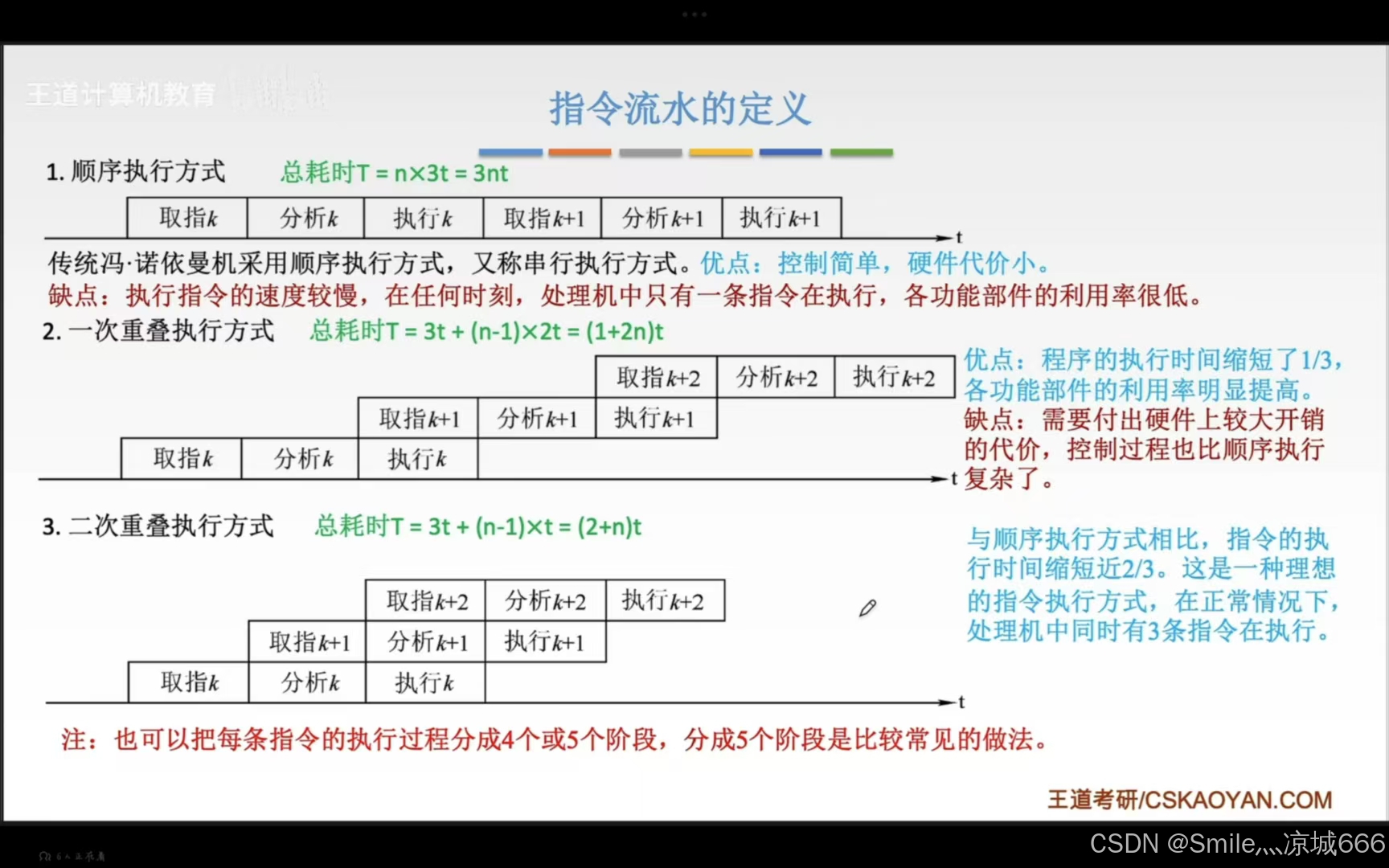

定义

执行方式

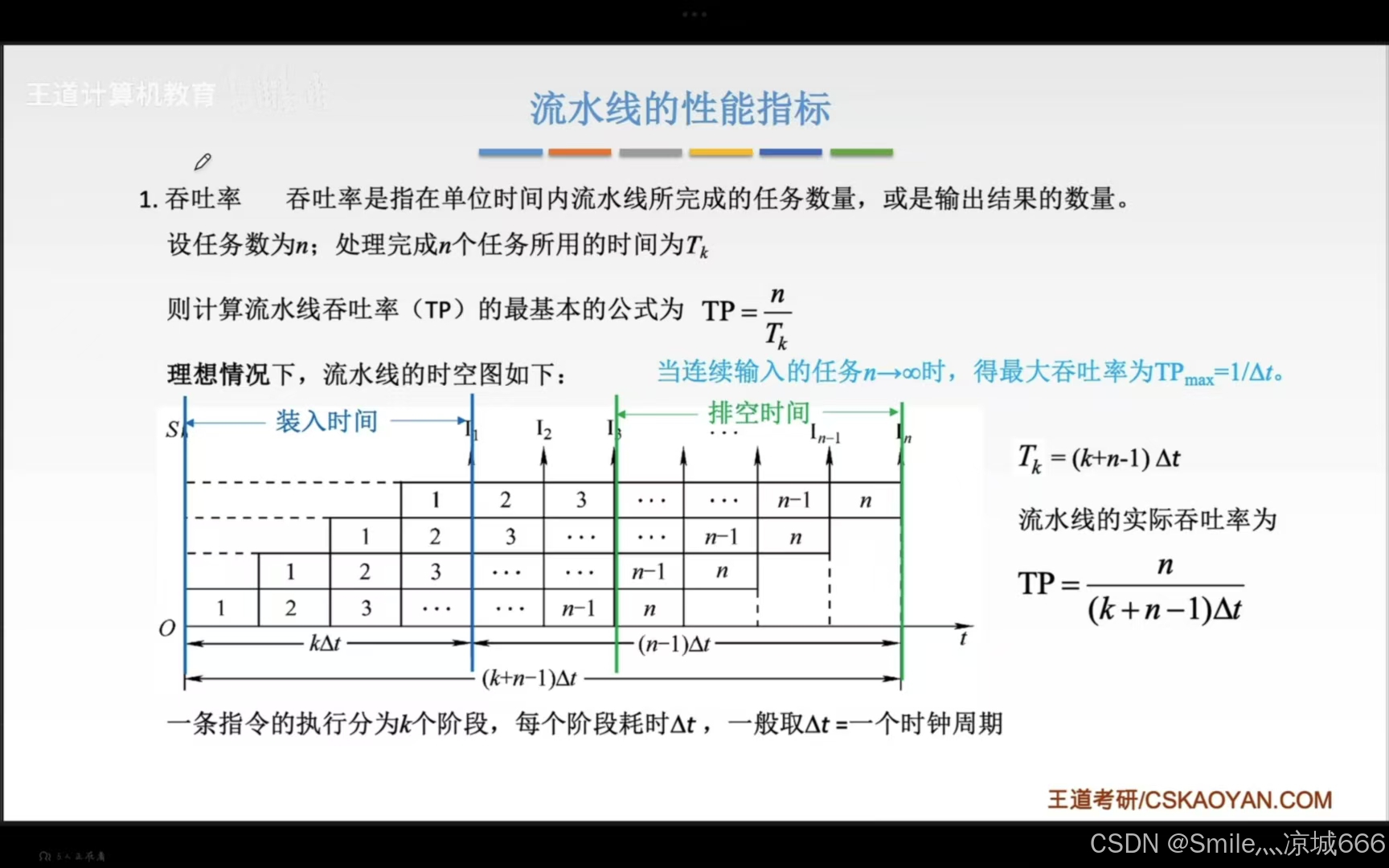

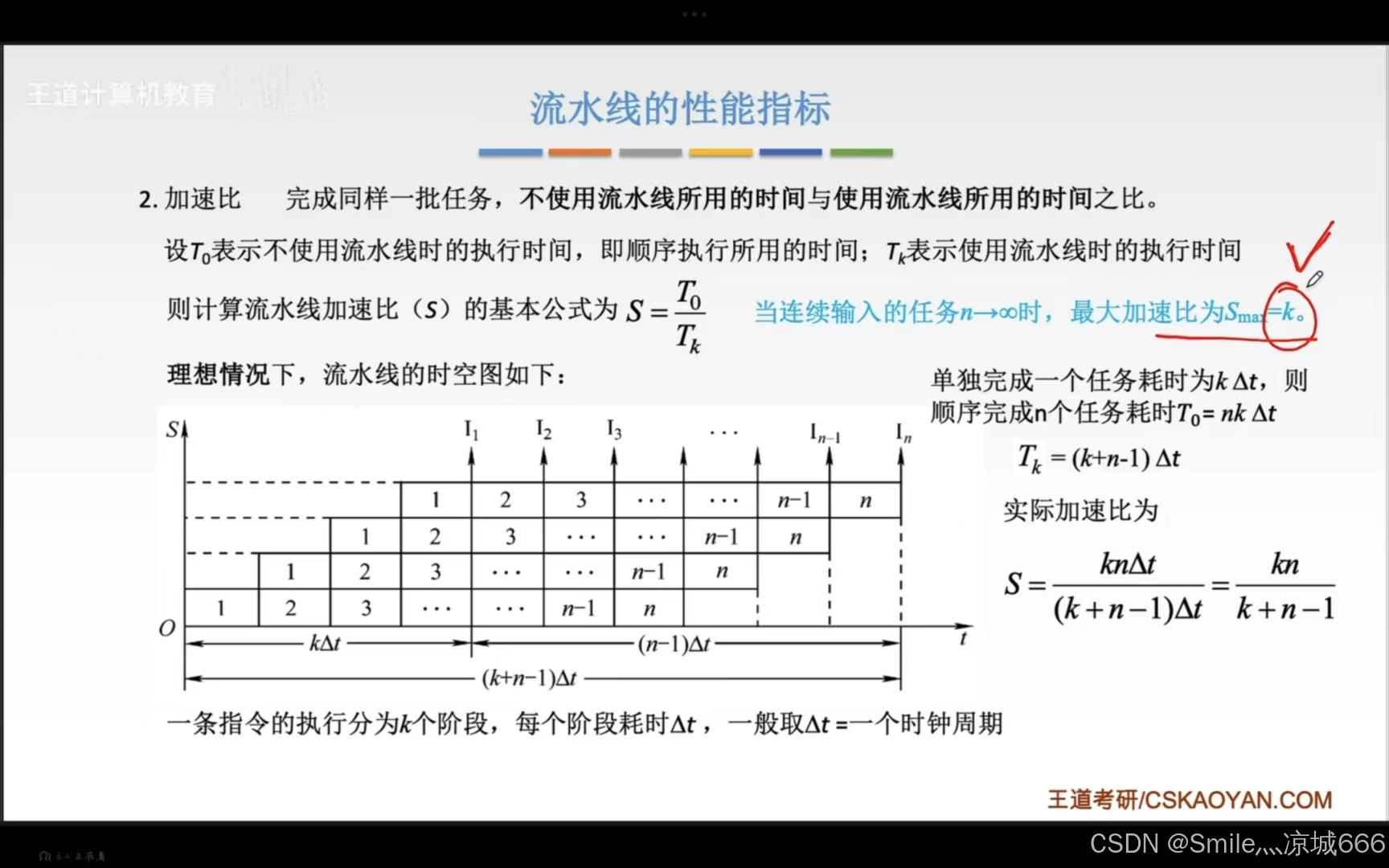

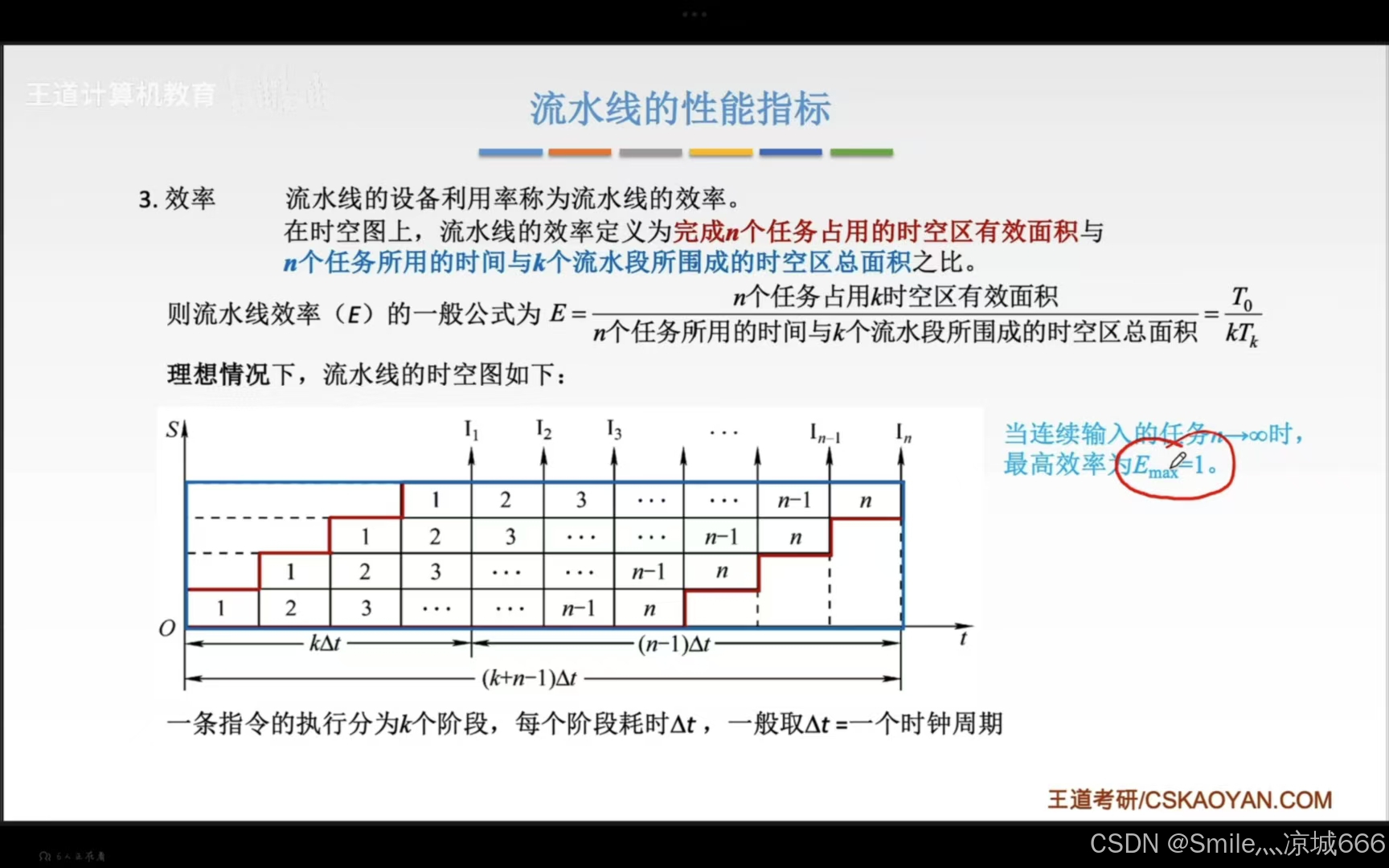

流水线的性能指标

吞吐率

加速比

效率

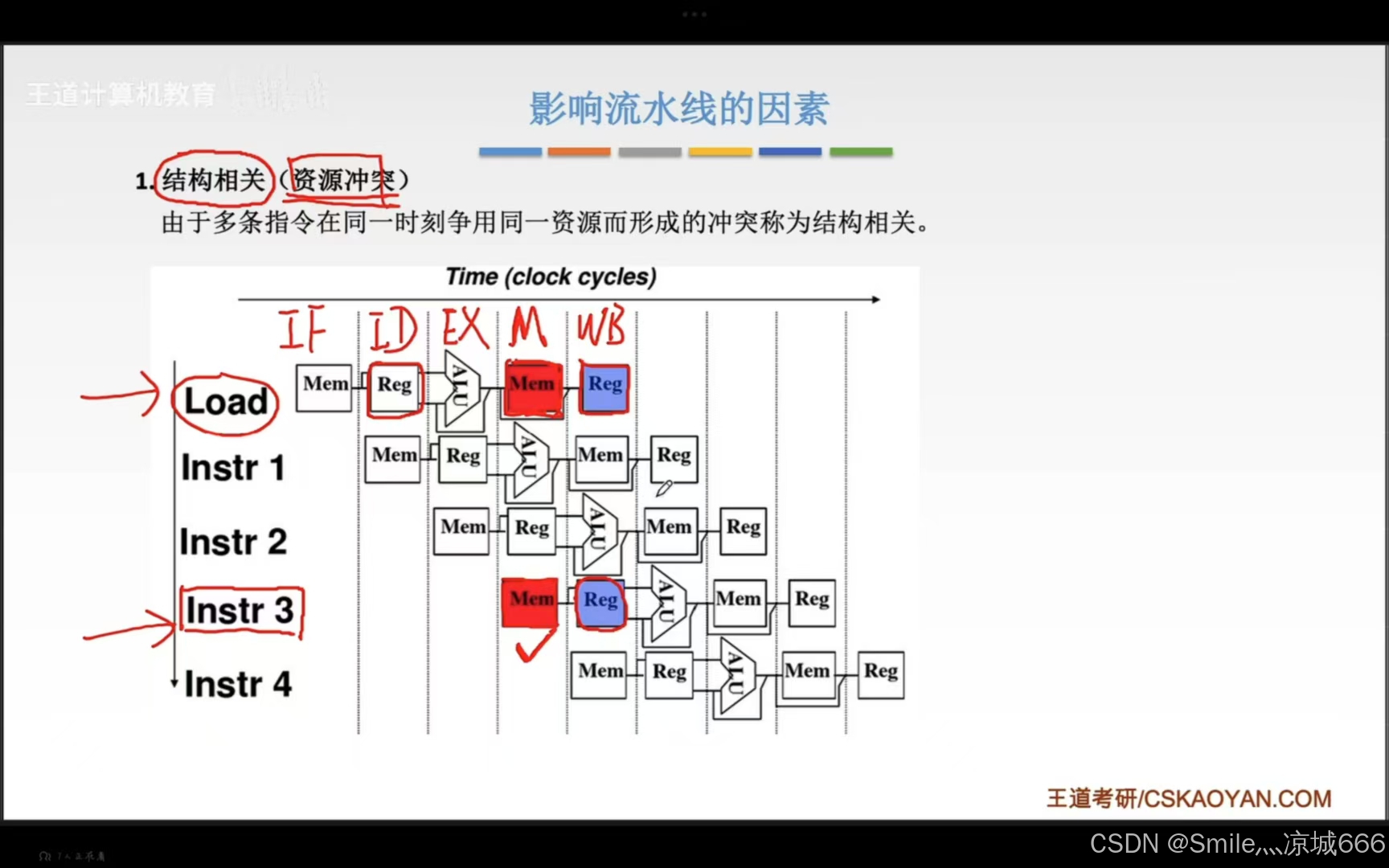

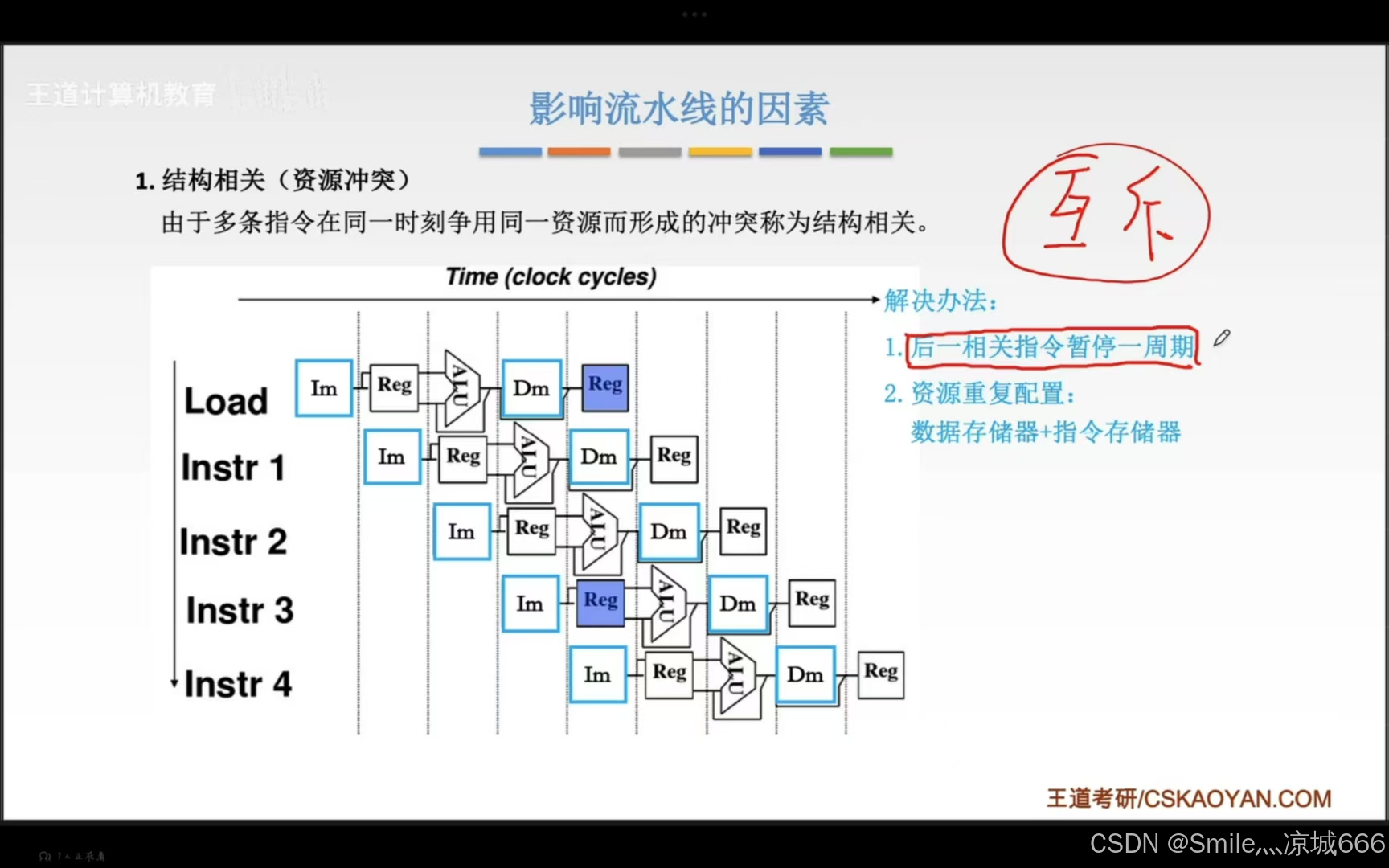

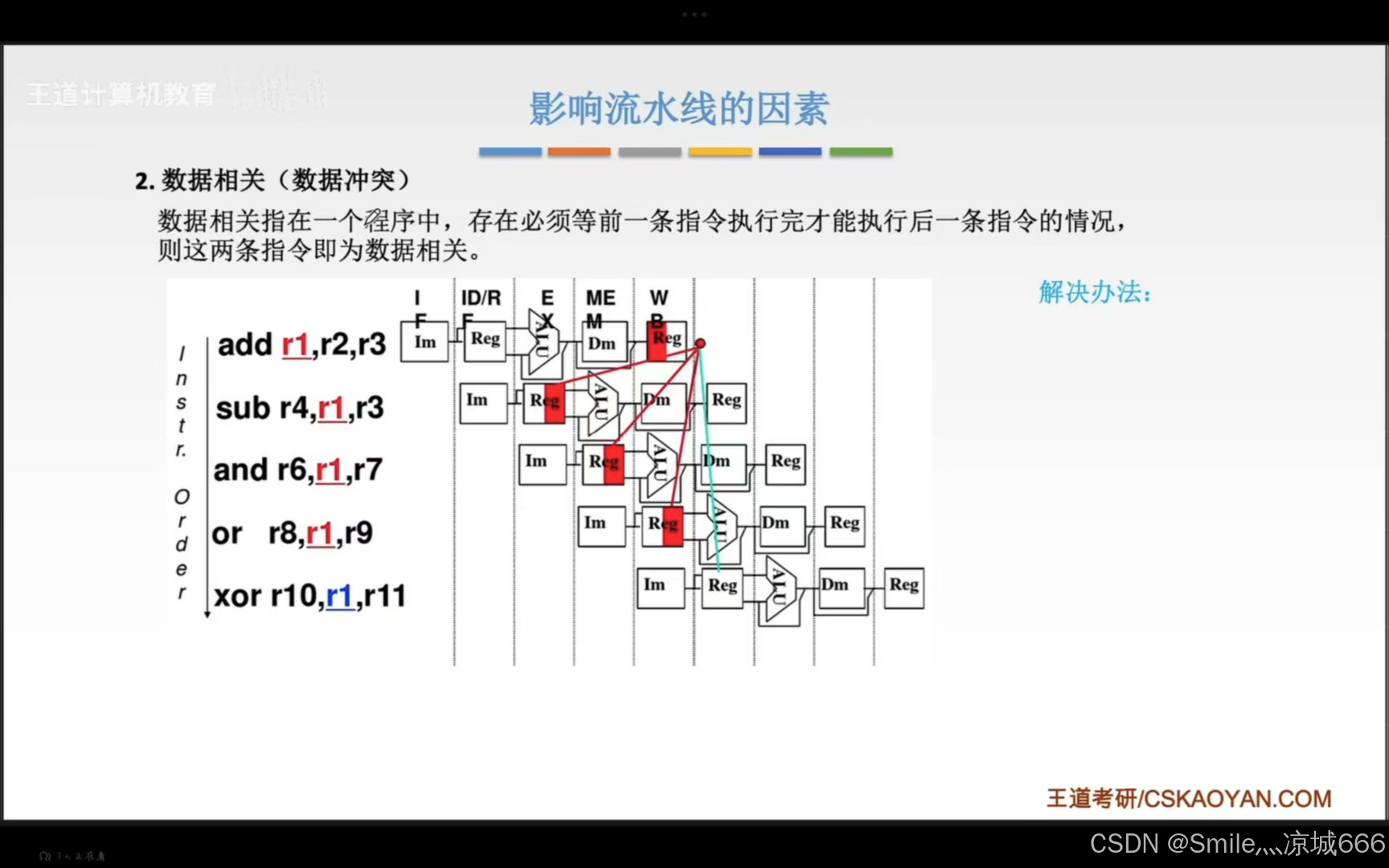

5.6_2指令流水线的影响因素

ID取数的时候只能在通用寄存器里取数,不能来自主存中,如果来自于主存,就必须放在寄存器中

IMM里存储的是立即数(就是个数字,不是地址)

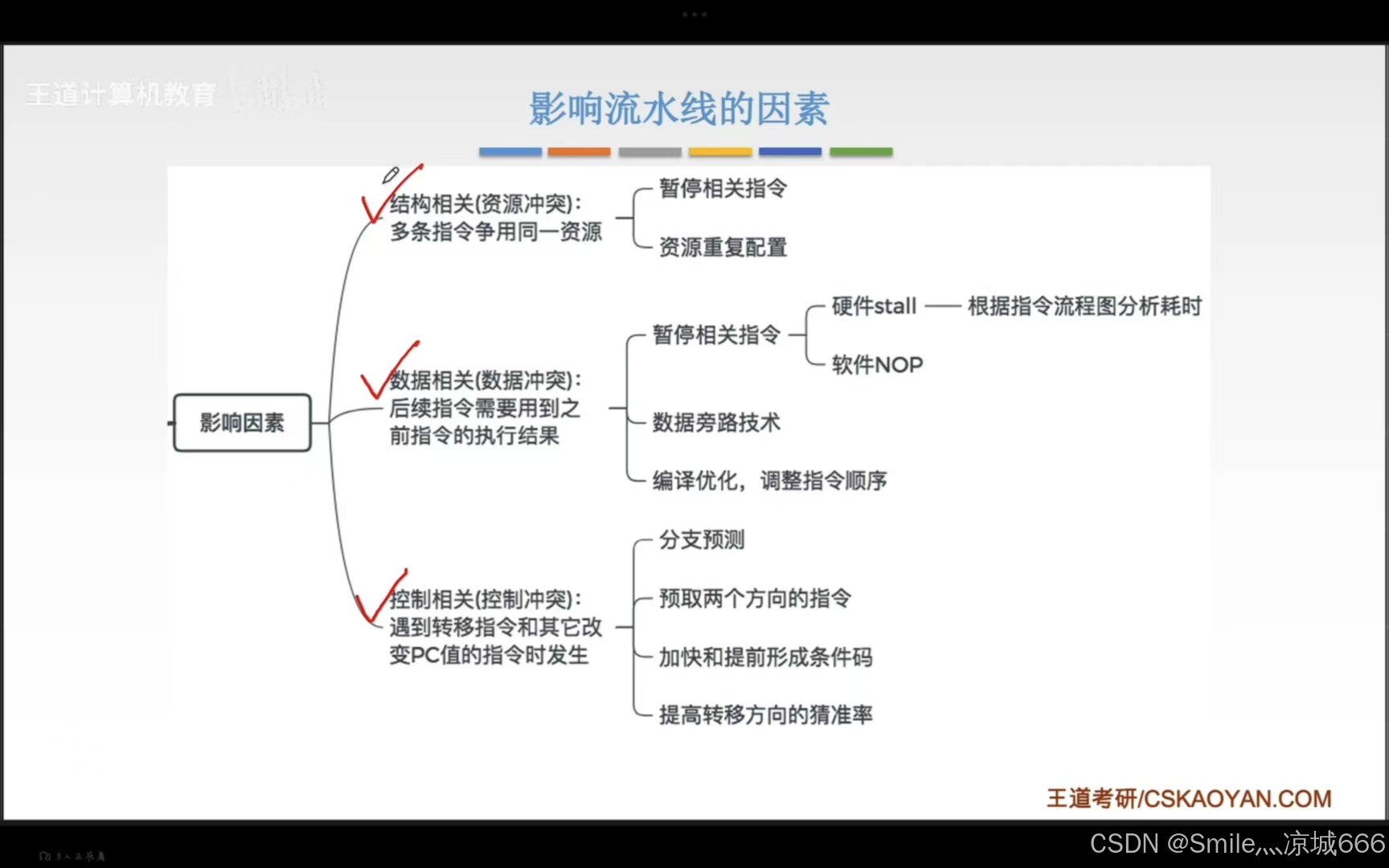

资源冲突

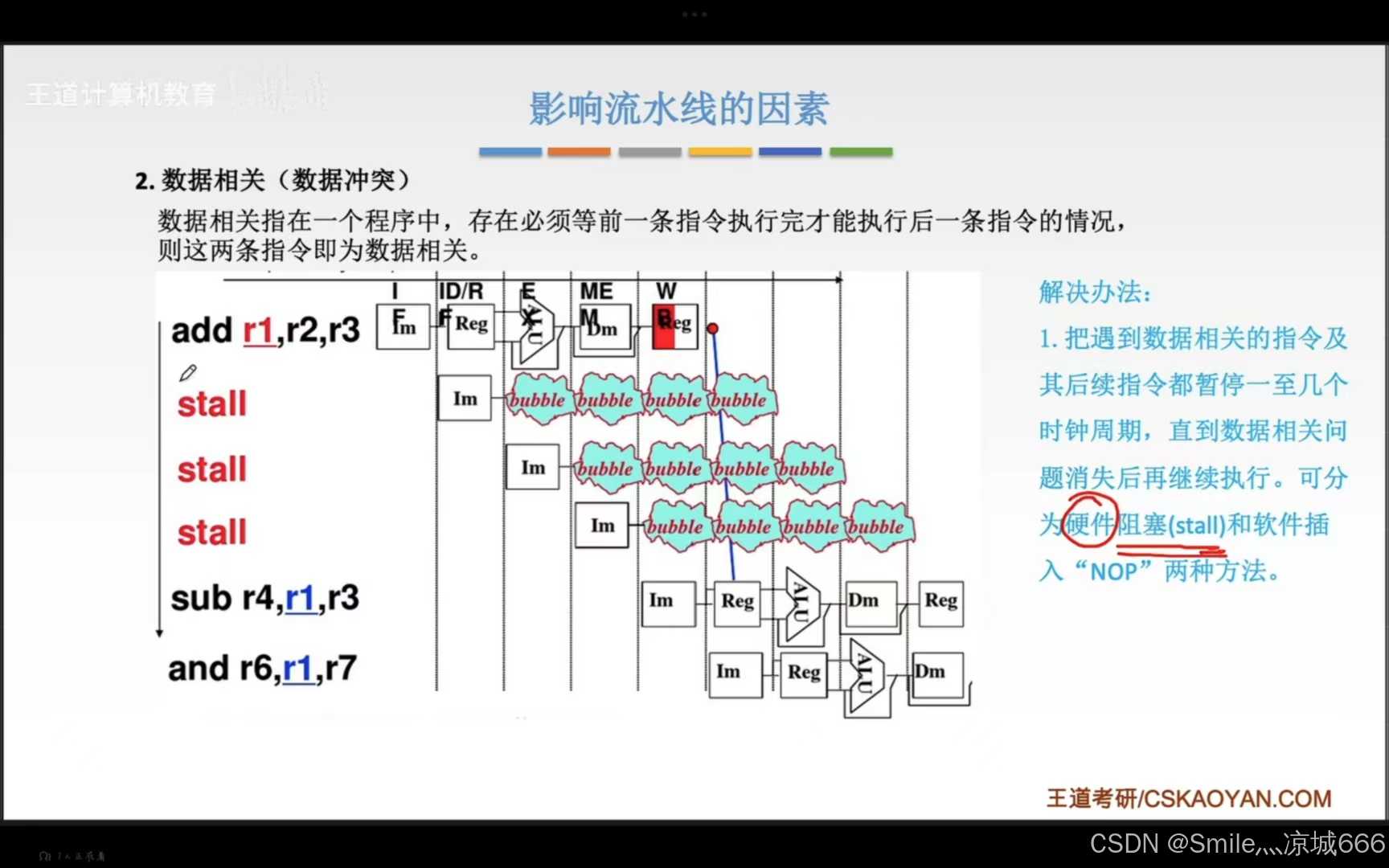

数据冲突

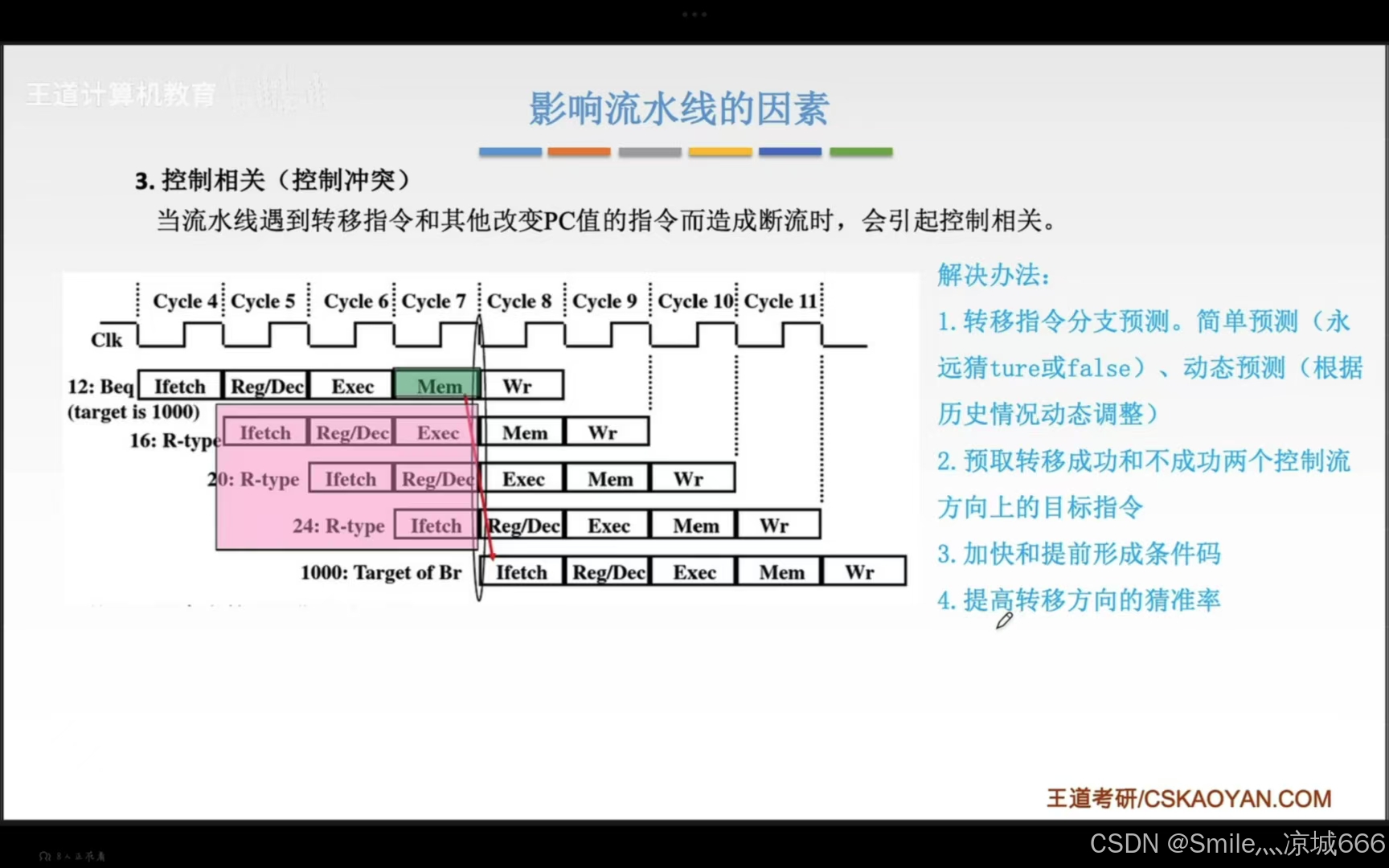

控制冲突

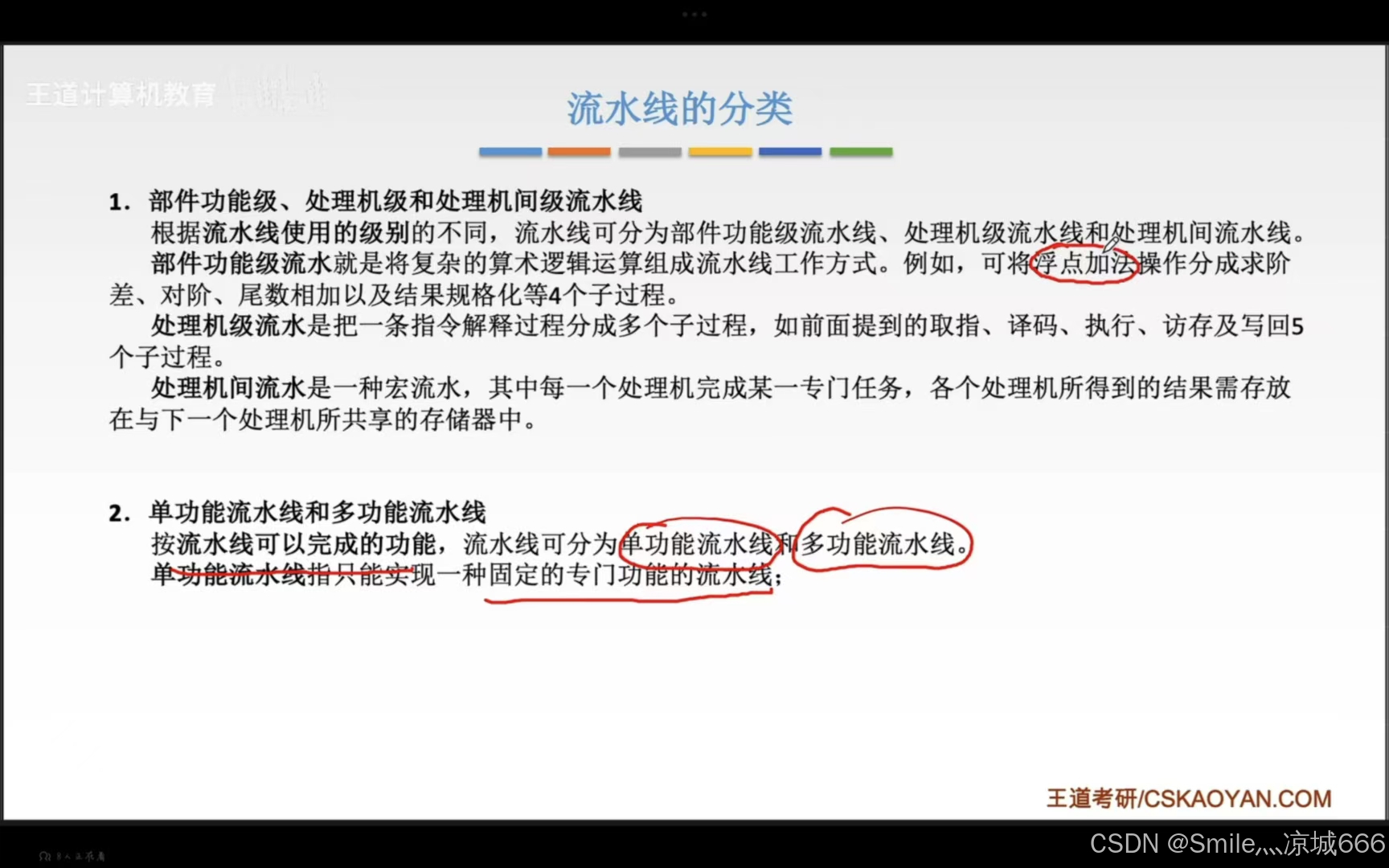

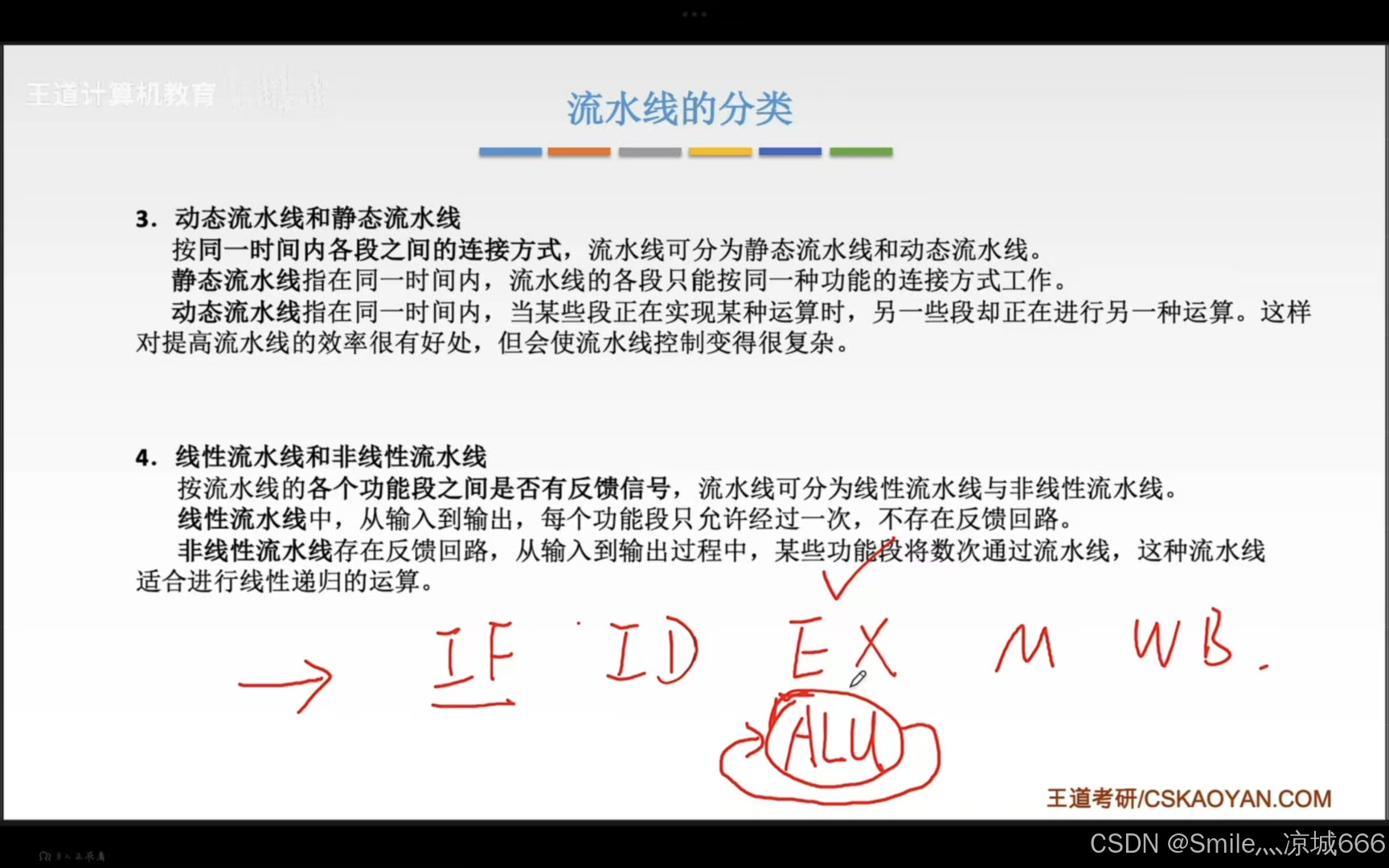

分类

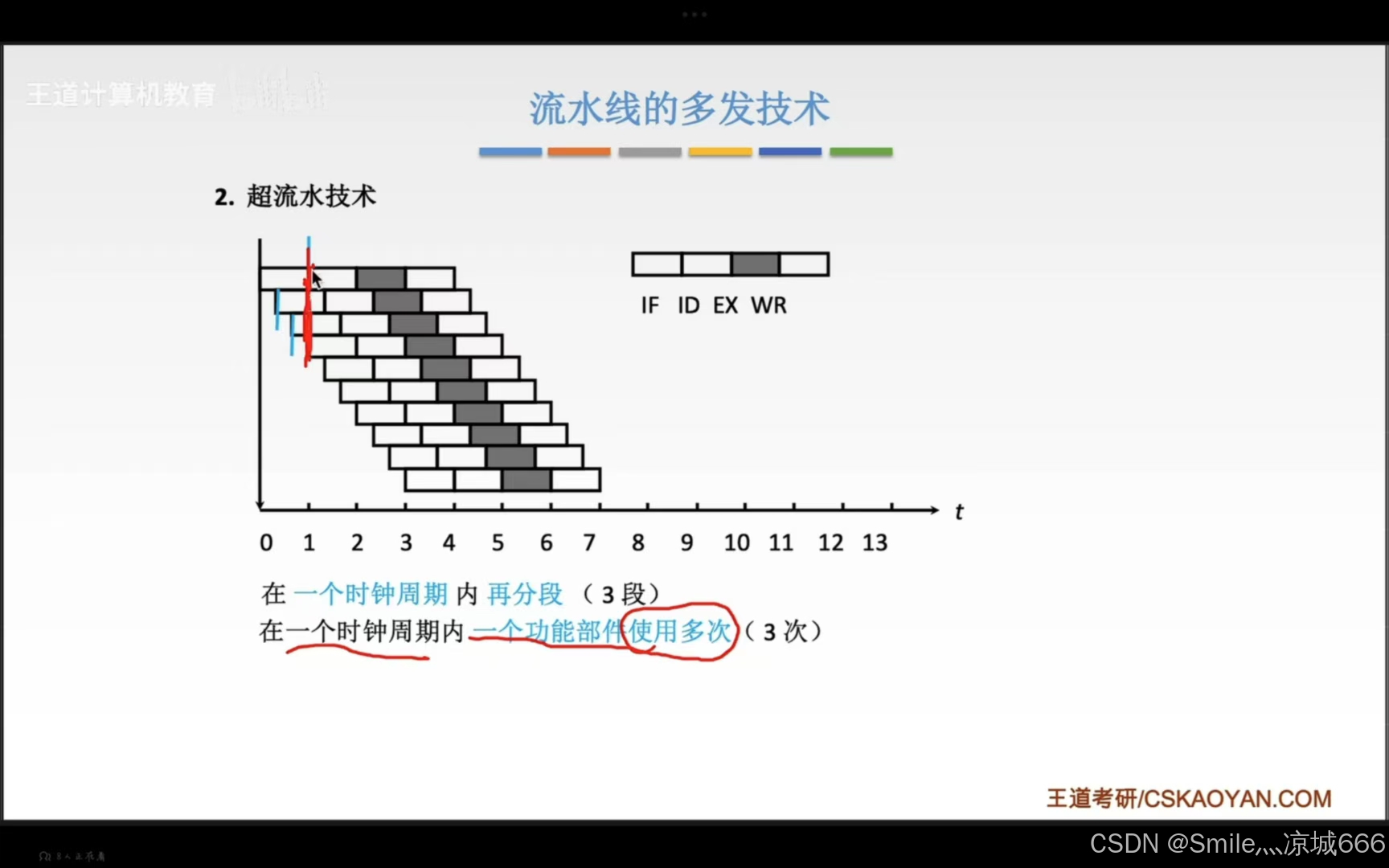

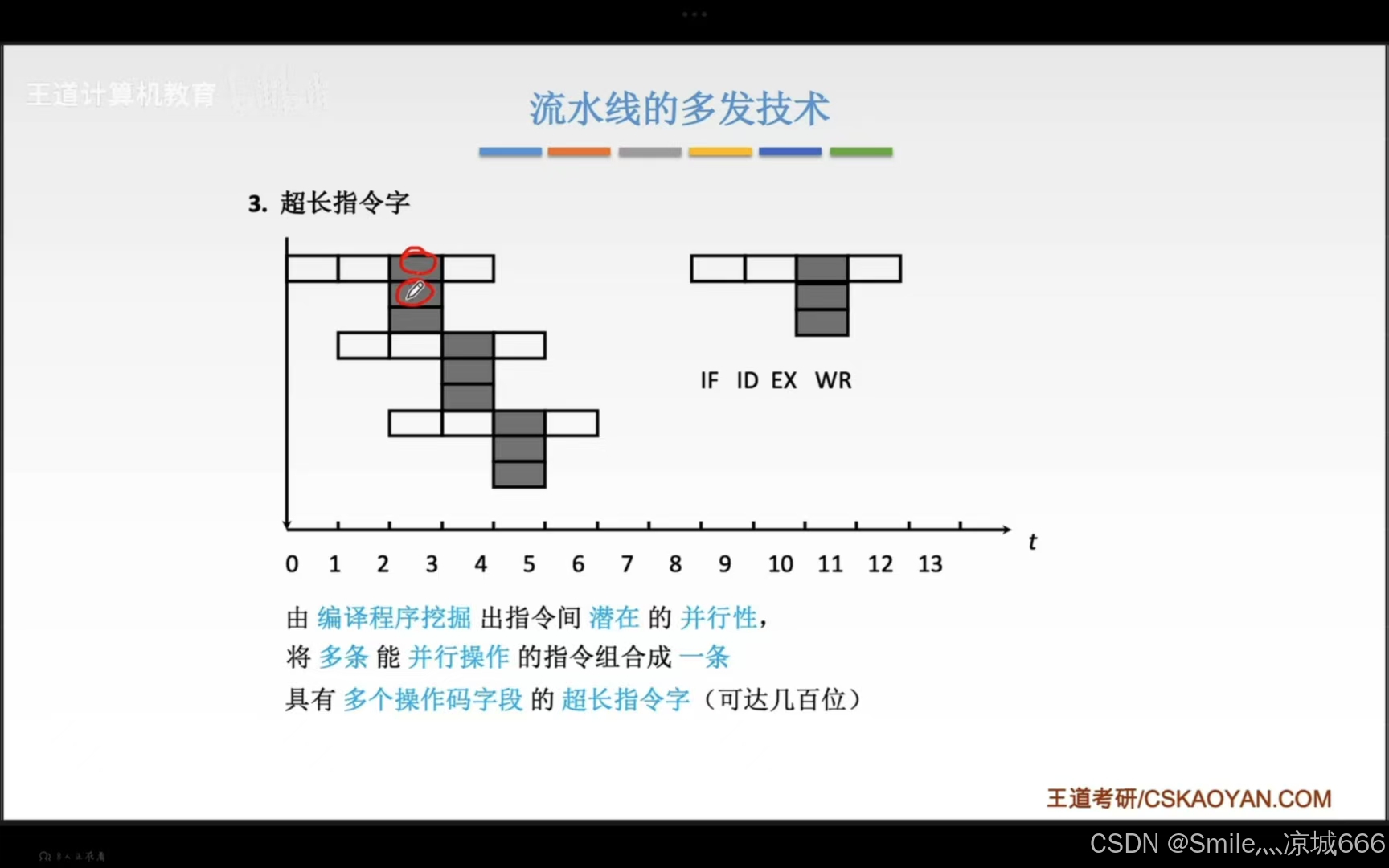

流水线的多发技术