数电基础:时序逻辑电路的分析方法

目录

一、时序逻辑电路的定义

二、小规模时序逻辑电路的分析方法

(1)补充说明基本触发器的特性方程

(2)7位加法计数器

(2)为什么真值表中考虑Q都是从0开始的?

(3)4位加/减法计数器

如果说组合逻辑电路是数字世界的本能反应,那时序逻辑电路便是其拥有了“记忆”与“时间”观念的开始。它的当前输出,不仅取决于此刻的输入,更与过去的历史状态息息相关,而这“记忆”的载体,便是触发器。本文旨在剥离复杂的设计过程,聚焦于一个更基础且关键的核心技能——时序电路的分析。我们将以一套清晰的方法论,逐步拆解两个经典电路(7位加法计数器与4位加/减计数器),亲手揭开“黑箱”的奥秘,理解从逻辑方程到最终功能的完整映射,为后续深入理解状态机和复杂数字系统打下坚实基础。

然而本文只是用作时序电路的引子,并未讨论较为深入的知识,知识简单定性的讨论了如何对一款电路进行时序分析。关于时序设计的部分会在后续文章逐步讲解。

一、时序逻辑电路的定义

时序逻辑电路当前时刻的输出不仅与当前时刻的输入有关,还和之前的状态有关。需要用到前面学的组合逻辑电路+触发器。

而其中最为关键的是触发器。一个时序逻辑电路可以没有组合电路,但必须得有触发器电路进行状态循环。因此,时序逻辑电路也可以称为状态机,或者有限状态机。

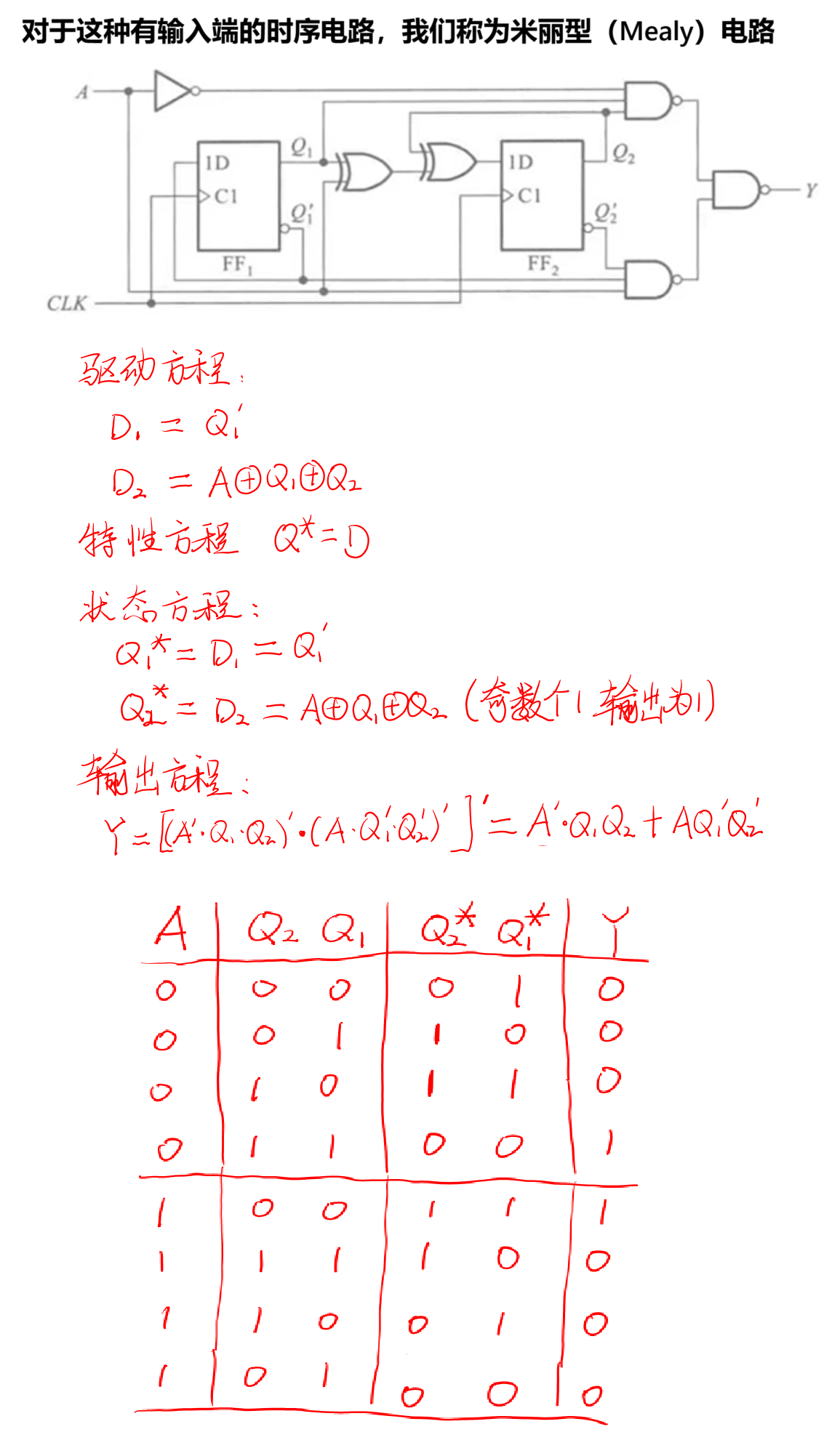

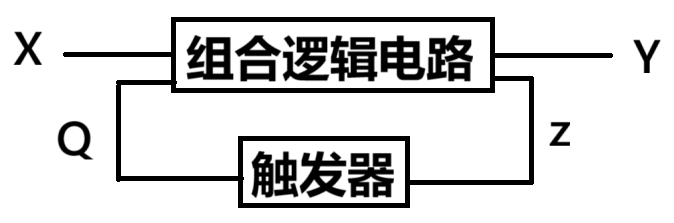

从这个图中可以看出有4个重要的变量。

其中,X、Y表示整体电路的输入和输出量。而Z表示触发器的输入量、Q表示触发器的输出量。

这里面只有X是我们需要从外端输入的。我们现在对剩下三个分别写出方程表达式(因为时序逻辑电路中,列写逻辑方程是非常关键的,不再像以前的组合电路一样列真值表了)。

所谓的驱动方程和状态方程其实就是触发器的输入和输出方程。这是一个时序电路中最为关键的一部。当你分析出了各个触发器的状态方程后,就可以直接写出输出值Y的表达式,最后通过真值表即可分析出电路的用途。

二、小规模时序逻辑电路的分析方法

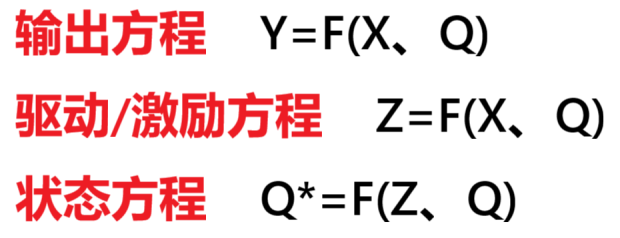

(1)补充说明基本触发器的特性方程

前面一篇文章我们详细分析了各种触发器的工作原理,但是并没有对此做一个总结,而在时序电路中,触发器的应用是非常广泛的,所以必须要用到特性方程,不要像以前一样再慢慢分析原理图了。

而虽然SR、JK触发器等会在CLK=1期间出现毛刺干扰问题,但是在时序电路中我们不考虑这些影响,而认为波形都是理想的,所以可以直接套用特性方程。

(1)无论是水平触发的D触发器、还是上升沿触发的D触发器。都满足Q*=D。

(2)脉冲触发的JK触发器。Q*=JQ'+K'Q。

(3)水平、脉冲SR触发器由于太过古老,且相较于D、JK没有任何优势,所以往往不会使用,且由于他的输入局限,无法直接写出特性方程。

(2)7位加法计数器

以后遇到任何电路都是一样的分析方式:列写驱动、特性方程,画出真值表。

从这个图中可以发现这是一个7位计数器,Q1Q2Q3每变化7次,Y只会产生一次从0->1和一次从1->0的跳变。

(2)为什么真值表中考虑Q都是从0开始的?

如果你用过logisim搭建过时序电路会发现一个问题:很多带有反馈线的电路(如JK触发器)需要先设置完状态后再连接反馈线,否则会陷入触发器死锁问题。

而现实中,工程师们为了避免该问题,通常会设计一个复位电路,在电源电压VCC从0上升到稳定值的过程中,POR电路会产生一个短暂的复位脉冲。这个脉冲通过一些门电路后正确的输入到各个触发器的端口,将其设置为输出0的状态。这个过程和我们先设置状态再连接反馈线是等价的。

以后我们只需要记住,一般芯片的复位键都会将输出置为0,这也是画真值表的基础。然而具体芯片还需要具体分析其手册,不能一概而论。

(3)4位加/减法计数器

可以看到该真值表在输入A不同的时候,Q和Y的变化特点是不同的。

当A=0时,是一个加法计数器,Q1Q2不断累加,当达到4时。Y对外输出一个1。

当A=1时,是一个减法计数器,Q1Q2从3减小到0。当恢复成4时,Y对外输出一个1。