【STM32】知识点介绍四:时钟体系

文章目录

- 一、简介

- 1.时钟源

- 2.时钟树

- 二、PLL(锁相环)

- 1.概述

- 2.基本组成

- 3.类比说明

- 4.PLL配置参数

- 三、时钟源配置

- 四、寄存器边界地址

一、简介

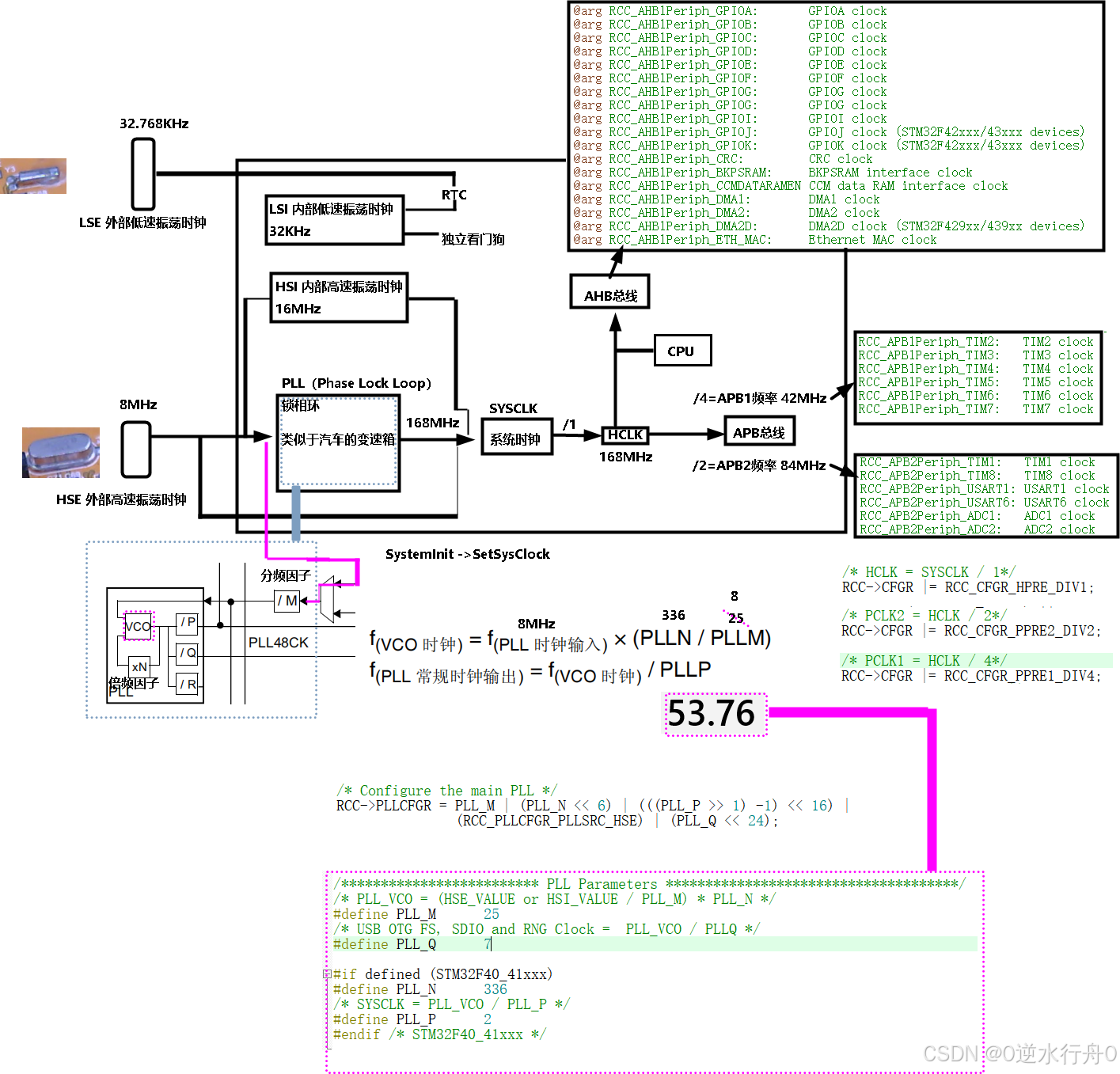

时钟是给单片机提供一个时钟信号(一个非常稳定的频率信号),使单片机各内部组件同步工作,并且在和外部设备通信时是也能达到同步,动态调整运行频率,就可以控制性能与功耗。

STM32 的时钟系统由外部晶振、PLL(锁相环)和内部 RC 振荡器组成。时钟系统主要提供了处理器时钟,以及可选的外设时钟和RTC模块时钟。

其作用包括:

- 为处理器提供准确的时钟信号,保证处理器、总线和外设的正确工作

- 通过 PLL 的倍频功能,产生多种频率的时钟信号,满足不同外设的时钟需求

- 通过时钟系统提供的时钟分频器、预分频器等功能,进一步调整时钟频率,以适应不同的应用场景

1.时钟源

(1)可以使用三种不同的时钟源来驱动系统时钟 (SYSCLK),CPU 运行的频率为 168MHz:

- HSI 振荡器时钟(16MHz),也就是高速内部时钟,一般来说很少用,因为精度没有外部高速时钟那么高

- HSE 振荡器时钟,也就是高速外部时钟,通常使用 8MHz

- 主 PLL (PLL) 时钟

(2)器件具有以下两个次级时钟源:

- 32 kHz 低速内部 RC (LSI RC),该 RC 用于驱动独立看门狗,也可选择提供给 RTC 用于停机/待机模式下的自动唤醒

- 32.768 kHz 低速外部晶振(LSE 晶振),用于驱动 RTC 时钟 (RTCCLK)对于每个时钟源来说,在未使用时都可单独打开或者关闭,以降低功耗

2.时钟树

时钟树就是关注时钟源和时钟的流向,嵌入式系统中的模块和外设工作都以时钟为基准。有了时钟树,就有了时钟域。嵌入式中除了内核,还有各个单元,每个单元工作在不同的时钟频率下,给每个单元提供不同的时钟。

二、PLL(锁相环)

1.概述

PLL(Phase Locked Loop): 为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取资料等。PLL基于振荡器中的反馈技术。

一般的晶振由于工艺与成本原因,做不到很高的频率,而在需要高频应用时,由相应的器件VCO,实现转成高频,但并不稳定,故利用锁相环路就可以实现稳定且高频的时钟信号

2.基本组成

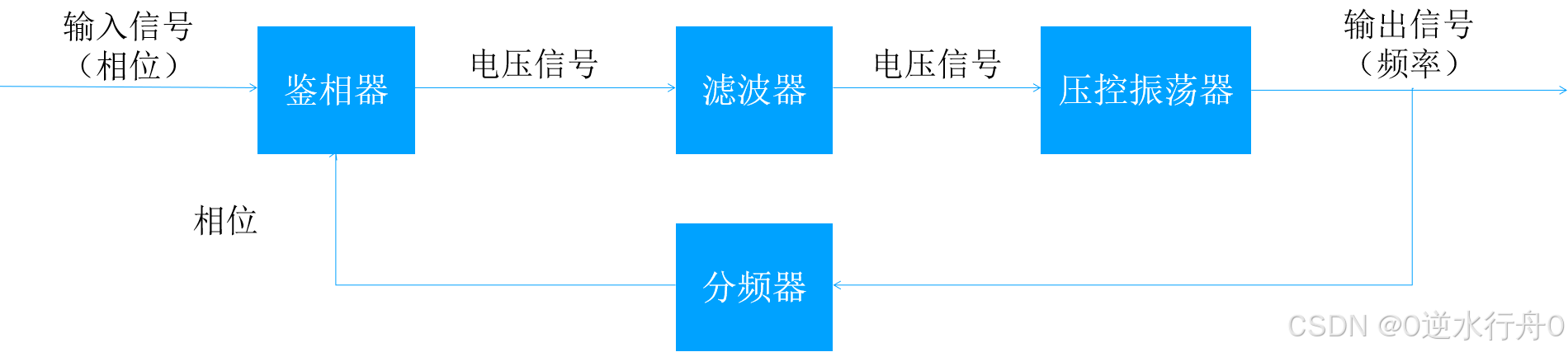

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-Locked Loop)。锁相环的特点是:利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成。

锁相环的工作原理是检测输入信号和输出信号的相位差,并将检测出的相位差信号通过鉴相器转换成电压信号输出,经低通滤波器滤波后形成压控振荡器的控制电压,对振荡器输出信号的频率实施控制,再通过反馈通路把振荡器输出信号的频率、相位反馈到鉴相器。

锁相环在工作过程中,当输出信号的频率成比例地反映输入信号的频率时,输出电压与输入电压保持固定的相位差值,这样输出电压与输入电压的相位就被锁住了。

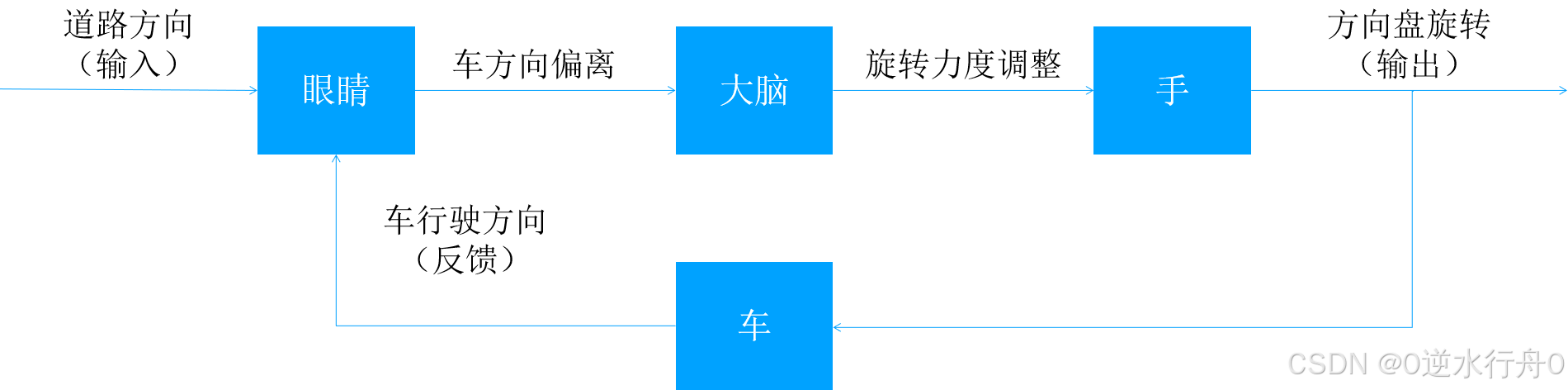

3.类比说明

我们刚开始学车的时候,在道路上开车,眼睛就好像一个鉴相器,负责发现车行驶的方向(反馈)和前方的路(输入)是否有差别,把差别输入大脑进行判断,然后指挥双手旋转方向盘,旋转方向盘的动作转换成车的行驶方向,我们通过这么一个闭环过程不断地调节方向盘,保证车行驶在正道上。如下图所示。

4.PLL配置参数

不同的芯片,倍频(频率翻倍)公式是不一样的,需要查询芯片手册!

三、时钟源配置

在特殊的应用场景,为了达到最高的能效比,没有必要使用到PLL,可将HSE、HSI作为系统时钟源。例如,在智能手表锁屏的情况下,如果使用PLL配置过后输出的频率会造成过多的功耗,降低自身的续航能力;同时要维持计步与测量心率功能。因此,PLL在锁屏下的应用场景并不合适,在保证功能实现的前提下,尽可能降低功耗,可以切换频率更低的时钟源提供给系统时钟

(1)选择PLL作为系统时钟源

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= RCC_CFGR_SW_PLL;或RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

(2)选择HSI作为系统时钟源

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= RCC_CFGR_SW_HSI;或RCC_SYSCLKConfig(RCC_SYSCLKSource_HSI);

(3)选择HSE作为系统时钟源

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= RCC_CFGR_SW_HSE;或RCC_SYSCLKConfig(RCC_SYSCLKSource_HSE);

四、寄存器边界地址

详见《STM32F4xx中文参考手册》的P52 ~ P54页,部分展示如下: