ASP4644电源芯片 Buck变换器双PLL频率同步机制分析

1.引言

现代便携式电子设备与分布式电源系统对DC-DC变换器提出了高频化、低EMI及快速瞬态响应的复合要求。恒定导通时间(COT)控制架构凭借其环路结构简洁、瞬态响应迅速等固有优势,在降压型Buck变换器领域获得广泛应用。然而,传统COT架构的开关频率随输入电压、负载电流及外部元件参数漂移而显著变化,导致EMI频谱难以预测、多相并联时均流精度恶化,并可能引发音频噪声干扰等工程问题。国科安芯推出的ASP4644芯片采用双锁相环(Dual-PLL)协同控制架构,通过内置伪PLL与外同步PLL的级联耦合机制,实现了开关频率对外部参考时钟或内部可编程频率的自适应精确跟踪,为上述技术挑战提供了一种创新的解决路径。

2.系统架构与功能划分

ASP4644基于BCD工艺实现,其系统架构体现功能模块化设计理念,主要划分为七大功能单元:

环路控制模块(Loop):包含误差放大器(EA)、软启动电路(SS)、电流采样电路(CURRENTSENSE)、电流比较器(ICOMP)及反流比较器(IREV)。该模块完成反馈电压与基准电压的比较放大、软启动斜坡生成、电感电流信息采样及功率管通断控制等核心闭环功能。

输出电压检测模块(Powergood):通过双比较器架构监测反馈电压VFB,当输出电压偏离额定值±10%时触发保护状态,并输出PGOOD标志信号。

电源管理模块(Powersupply):采用两级降压架构,预偏置电路将3.6V-20V宽输入电压降至约2.5V,为基准及LDO提供前置稳压;内部LDO输出3.3V的INTVCC,为模拟控制电路供电。

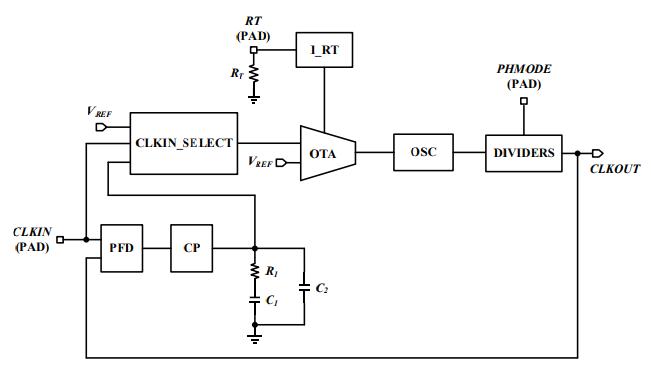

频率同步PLL模块:由PFD、电荷泵(CP)、跨导OTA、RT电流产生电路、张弛振荡器及分频器构成,实现振荡器频率的锁定与多相相位生成。

时钟同步PLL模块:构成外环频率锁定回路,通过调节Ton产生电路的充电电流,实现功率级开关频率对参考时钟的跟踪。

开关逻辑模块(SwitchLogic):实现占空比调控、死区时间管理、模式切换(FCCM/Burst)及各类保护逻辑的整合。

驱动模块(Driver):采用多级放大结构驱动上、下功率MOSFET,确保大尺寸功率管的快速开关。

3.双PLL频率同步机制原理

ASP4644的双PLL架构由外同步PLL与内置伪PLL两级构成,二者通过跨导线性环实现信号耦合。

3.1 外同步PLL工作机制

外同步PLL的核心功能为实现振荡器频率的可编程设定或外部同步。当SYNC引脚悬空、接地或接电源时,时钟选择电路判定为无外同步状态,振荡器频率由RT引脚外接电阻设定的电流决定;当检测到有效外部时钟信号时,PFD比较外部时钟与振荡器输出相位,CP将相位误差转换为电压,经OTA转化为电流调节振荡器偏置,实现频率锁定。振荡器采用六级差分环振结构,每级通过电容充放电延迟产生相移,整体频率由偏置电流与电容比值决定,并可通过 trimming 端口修调。

3.2 内置伪PLL调控机制

内置伪PLL构成频率锁定外环,其参考频率为振荡器输出fCLK,反馈信号来自SW节点经电平转换后的开关频率。伪PLL的PFD输出经OTA转换为调整电流Iclk,注入跨导线性环。该环路由双极型晶体管Q1-Q4构成,形成发射结电压闭环约束。依据跨导线性原理,环路电流满足约束关系:Q1集电极电流(含外同步电流IPLL与调整电流Iclk)与Q2集电极电流(VIN比例电流IIN)的乘积关系,决定了Q4输出的Ton充电电流Ion,进而调节导通时间以修正开关频率偏差。

3.3 时间超前AOT产生电路

AOT电路实现Ton与VOUT成正比、与VIN成反比的自适应特性。VIN比例电流通过匹配电阻网络生成0.1×VIN采样信号,经V-I转换后注入跨导线性环。Ton产生电路通过电容C的恒流充电过程计时,当电容电压达到VON阈值时比较器翻转,结束导通期。在Burst模式下,DCM_add信号控制附加电容并入,延长Ton以降低轻载开关频率,提升效率。

4.关键模块电路技术分析

4.1 基准源设计

电压基准:采用三极管自偏置带隙基准架构,Q1与Q2电流密度比1:8产生PTAT电流,与VBE负温度系数叠加输出约1.25V基准。核心创新在于采用Q3-Q4电流密度匹配钳位,替代传统高增益运放,简化电路并降低功耗。M6管作为隔离级,抑制VPRE波动对VBG的耦合,改善中低频PSRR。启动电路采用交叉耦合结构,避免了零电流简并态,无需额外启动支路。

电流基准:采用运放缓冲结构将VBG转换为低温度系数电流。运放选用套筒式共源共栅架构,在3.3V电源下实现高增益与低失调的平衡。该结构输出的IREF为跨导OTA提供偏置,并生成辅助基准电压。

4.2 内部LDO设计

LDO采用PMOS功率管架构,以满足3.6V转3.3V的低压差要求。预偏置电路通过三极管交叉耦合与高压DMOS管M1,将输入电压预降压至2.5V,为差分输入级供电。此设计显著降低高压器件使用比例,简化版图复杂度。功率管M14在低压差条件下工作于深线性区,其导通电阻需满足30mA满载输出能力。保护电路M15-M16在启动或过流时钳位M14栅极,防止VIN高压输入时栅氧击穿。

设计权衡点:预偏置电阻R3的取值需在高压输入时的功耗与低压输入时的电流匹配之间折中。

4.3 高速比较器设计

ICOMP比较器:实现电感电流谷值与VC控制信号的比较,采用四级放大结构。前两级采用电阻负载预放大级,利用电阻的低寄生电容特性将主极点推向高频,展宽带宽。偏置电流采用PTAT设计,补偿高温下跨导衰减,确保-40℃至125℃范围内增益稳定。电感电流采样采用Rds(on)检测技术,通过开关管阵列在导通期间采样SW-PGND压差,避免串联检流电阻的损耗。

反流比较器:采用三级放大结构,第一级为电阻负载预放大,第二级五管差分对实现双端转单端,第三级共源放大进一步提升增益。通过PGND-SW分压采样判断电流过零点,当下管电压由负变正时关断同步整流管,防止电流倒灌。

4.4 SW电平转换电路

该电路实现高压域SW信号到低压域逻辑的快速转换,为内置伪PLL提供真实反馈。采用高压DMOS管MN1做隔离,配合level shift结构将信号转换至3.3V逻辑域。

5.保护机制与模式管理

UVOV保护:采用迟滞比较器架构,当VFB超出0.54V-0.66V窗口达10%时触发。迟滞通过MN5反馈管注入失调电流实现,延时电容C1滤除瞬态毛刺。触发后强制进入CCM模式并拉低PGOOD,确保系统级联可靠性。

模式选择:MODE引脚通过三态检测电路识别三种状态:接地为FCCM模式,接INTVCC或悬空为Burst模式,输入时钟则自动切换至外同步FCCM。外时钟检测电路利用窄脉冲充电机制,当频率高于阈值时SYNCOK置位。

6.结论

ASP4644通过双PLL级联架构与跨导线性环的协同设计,在理论层面为COT Buck变换器的频率稳定问题提供了创新解决方案。外同步PLL锁定振荡器频率,内置伪PLL调节导通时间,二者通过电流模式跨导线性环耦合,形成频率-时间双闭环控制。AOT电路实现输入电压前馈,提升瞬态响应速度;分级供电与敏感信号隔离设计增强了抗干扰能力。