一个FPGA通加载不同程序实现4K edp和V-by-One

一个FPGA通过烧录不同程序实现edp和VBO是一个非常经典和实用的FPGA应用场景。这个方案的核心是创建一个基于FPGA的超高性能、可重构的视频接口平台。因为 V-by-One和 4K eDP 都是高性能接口,对FPGA的资源、引脚和设计方法提出了较高的要求。

一、核心概念:FPGA作为“万能”硬件

FPGA(现场可编程门阵列)的最大特点就是其可重构性。您可以通过烧写不同的比特流文件,在硬件层面改变其内部逻辑电路的功能。这就好比一块“万能”的硬件底板:

-

烧录程序A -> FPGA内部形成了eDP接口控制器和相关的视频处理电路。

-

烧录程序B -> FPGA内部形成了VBO接口控制器和相关的视频处理电路。

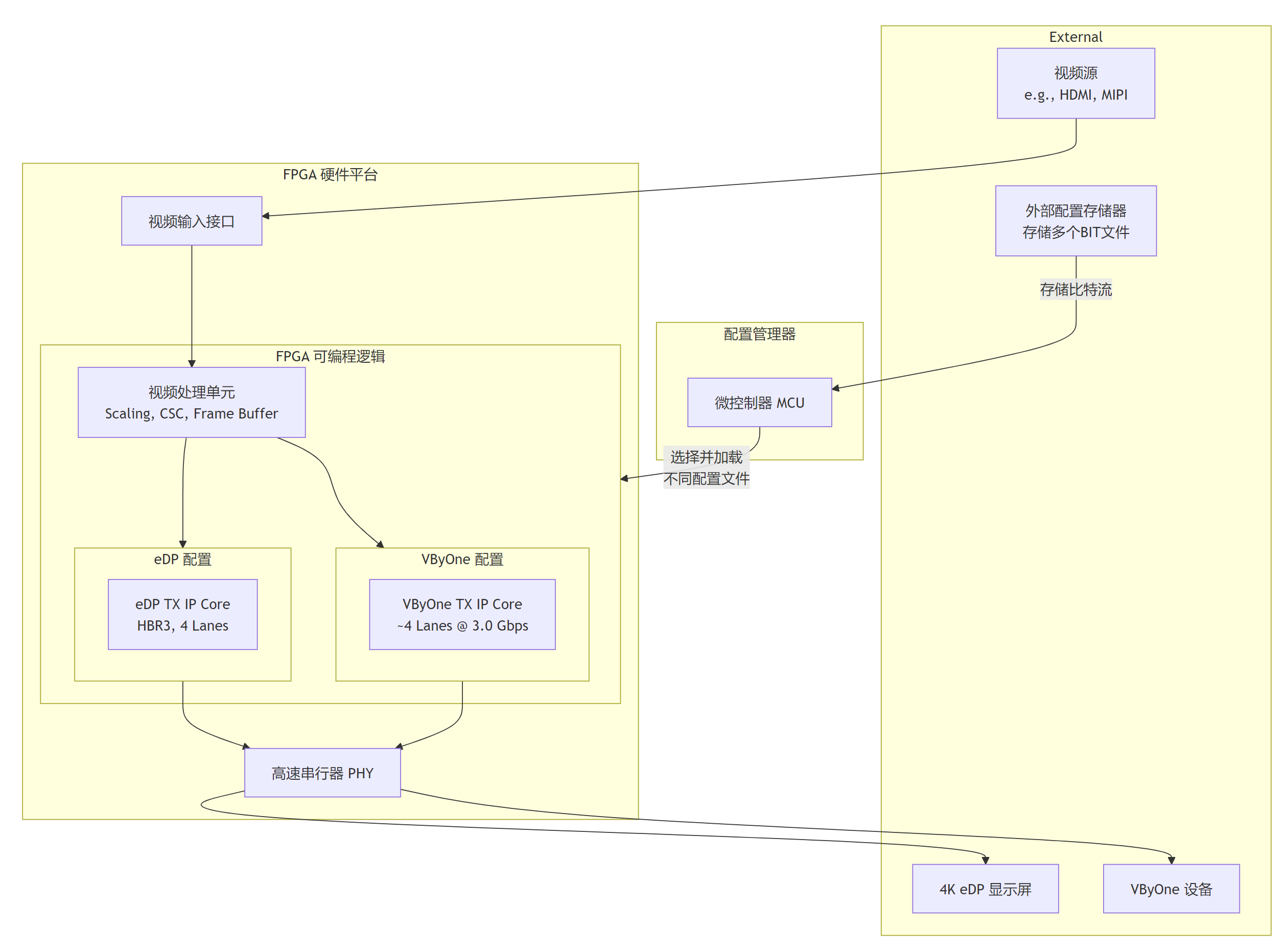

二、系统总体架构

下图展示了一个FPGA通过加载不同比特流,分别实现4K eDP TX和VByOne TX功能的系统框图:

三、实现 4K eDP 的关键细节

-

核心IP: 必须使用FPGA厂商的 DisplayPort/eDP TX IP Core。

-

Xilinx: DisplayPort 1.4 TX Subsystem

-

Intel: DisplayPort IP Core

-

-

链路配置:

-

4 Lanes, HBR3 (8.1 Gbps/lane): 总带宽 4 * 8.1 = 32.4 Gbps,轻松满足 4K@60Hz (~12.5 Gbps) 并有余量用于音频和辅助数据。

-

-

关键功能:

-

MST (Multi-Stream Transport): 为未来多显示器支持做准备。

-

DSC (Display Stream Compression): 如果支持,可以传输更高分辨率或刷新率。

-

Panel Self-Refresh: 实现节能。

-

四、实现 VByOne 的关键细节

-

核心IP: 这是最大的挑战。VByOne IP通常由专业IP供应商(如 Thine Electronics)提供(本博主有 IP源码)。

-

与 eDP 的标准化IP不同,VByOne IP可能需要额外的许可费用。

-

-

链路配置:

-

VBy-One HS 每 Lane 速率可达 3.0 Gbps / 4.0 Gbps。

-

对于 4K@60fps RGB 8bpc (~12.5 Gbps),需要 4 Lanes @ 3.0 Gbps 或 3 Lanes @ 4.0 Gbps。

-

-

关键特性:

-

嵌入式时钟: 无需单独的时钟对,减少布线和引脚。

-

CDR (Clock Data Recovery): 接收端通过CDR从数据流中恢复时钟。

-

Training序列: 上电后需要进行链路训练以锁定时钟和相位。

-

4. 本博主IP接口:

// tx-vboinput HTPDN_IN , // (i) Hot Plug Detectinput LOCKN_IN , // (i) Lock Detectoutput vx1tx_clk,input [TX_LANES-1:0] vx1tx_vsync , // (i) Vsync Inputinput [TX_LANES-1:0] vx1tx_hsync , // (i) Hsync Inputinput [TX_LANES-1:0] vx1tx_de , // (i) Pixel Data Valid Inputinput [TX_LANES*40-1:0] vx1tx_data , // (i) Pixel Data Input [39:0]input [TX_LANES*24-1:0] vx1tx_ctrl , // (i) Pixel Control Data Input [23:0]

五、巨大的挑战与解决方案

1:引脚兼容性

这是最严峻的硬件设计挑战。eDP 和 VByOne 都使用高速串行接口,但它们的电气特性、协议和训练机制完全不同。

-

最优方案: 设计一个PCB,让同一组高速串行引脚既能连接到eDP显示器的连接器,又能连接到VByOne设备的连接器。可通不同屏线实现连接。既提高了FPGA资源利用率,又降低了生产成本。

-

一般方案:

-

独立的物理连接器: PCB上同时放置一个eDP连接器和一个VByOne连接器。

-

FPGA引脚分配: 将 eDP 的 Lane 分配到 FPGA 的某一组高速 Bank,将 VByOne 的 Lane 分配到另一组高速 Bank。

-

程序切换逻辑: 当加载

edp_4k.bit时,只有 eDP 对应的 Bank 被激活,输出 eDP 信号;当加载vbo_4k.bit时,只有 VByOne 对应的 Bank 被激活,输出 VByOne 信号。

-

2:高的性能与资源消耗

-

FPGA选型: 必须选择中高端FPGA,例如:

-

Xilinx: Artix-7/Kintex-7 高配型号,或 UltraScale/UltraScale+ 系列。

-

Intel: Cyclone V/V10 高配型号,或 Arria 10 系列。

-

-

关键资源:

-

高速收发器数量: 需要至少 8 个(4 for eDP + 4 for VByOne,如果同时布局)。

-

逻辑单元 (LUT/FF): 需要大量资源来处理两个高性能协议。

-

块存储器 (BRAM): 用于视频帧缓冲和协议栈。

-

DSP块: 用于可能的视频处理算法。

-

3:IP获取与集成

-

eDP IP: 相对容易,可从FPGA厂商直接获得。

-

VByOne IP: 难度高。需要联系专门的IP供应商(如Thine)或FPGA厂商的合作伙伴,通常涉及商业授权。可能需要自己实现部分PHY层,但这极其困难。(但是本博主有 IP源码,并有成熟解决方案https://blog.csdn.net/Js_cold/article/details/144302449)。

六、实现步骤总结

-

硬件设计:

-

选择一款具有足够高速收发器和高逻辑资源的中高端FPGA。

-

PCB设计包含独立的eDP和VByOne连接器。

-

将FPGA的高速Bank分别路由到这两个连接器。

-

包含一个外部Flash和MCU用于管理多重配置。

-

-

IP获取与集成:

-

从FPGA厂商获取 eDP TX IP Core。

-

从第三方供应商购买或授权 VByOne IP Core。

-

分别构建两个独立的FPGA项目(

edp_4k和vbo_4k)。

-

-

固件开发:

-

在两个项目中实现通用的视频处理前端(输入、缩放、色彩空间转换)。

-

分别集成并配置 eDP 和 VByOne IP核。

-

生成两个完整的比特流文件。

-

-

系统集成与测试:

-

将两个比特流文件存储在外部Flash的指定位置。

-

开发MCU固件,根据用户命令或自动检测来触发比特流重配置。

-

分别连接eDP显示器和VByOne设备进行严格测试。

-

七、优势

-

硬件复用,降低成本: 无需设计两套不同的硬件板卡,一套FPGA平台即可应对两种需求,降低了BOM成本和PCB面积。

-

灵活性高: 未来如果协议有更新,或者需要支持第三种接口,只需更新FPGA程序即可,无需改动硬件。

-

快速原型开发: 在项目初期,当接口标准尚未最终确定时,使用FPGA可以快速进行验证和切换。

八、结论

一个FPGA通过烧录不同程序实现4K eDP和VByOne在技术上是可行的,但它是一个高成本、高复杂度的专业级解决方案。它非常适合需要高带宽接口灵活性的场合,例如:

-

高端视频测试设备

-

专业广播级视频切换台

-

数字标牌媒体播放器(需要驱动不同类型的高分显示器)

这个方案成功的关键在于:合适的FPGA选型、成功的PCB设计、以及获得稳定可靠的VByOne IP核。