【计算机组成原理】第一章 计算机系统概述

第一章 计算机系统概述

- 1.1 计算机硬件的基本组成

- (1)早期冯诺依曼机

- (2)现代计算机结构

- 1.2 各个硬件的工作原理

- (1)主存储器

- (2)运算器

- (3)控制器

- (4)计算机的工作过程

- 1.3 计算机软件

- 1.3.1 三种级别的语言

- 1.3.2 软件和硬件的逻辑功能等价性

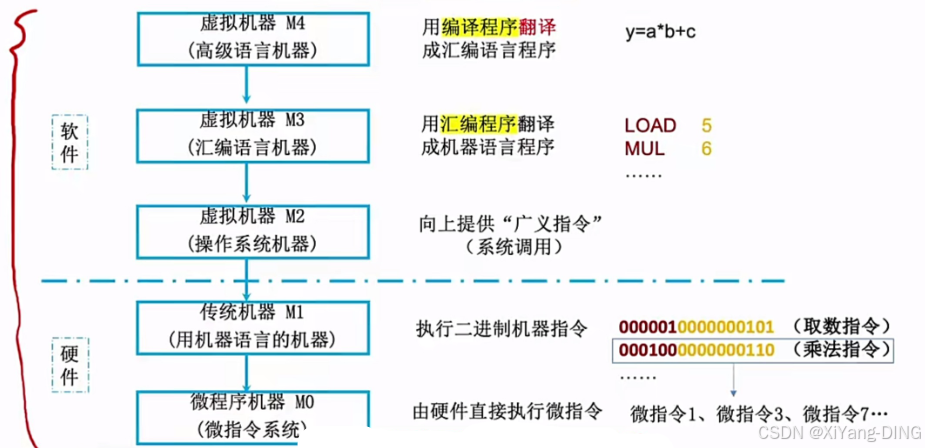

- 1.4 计算机系统的层次结构

- 1.5 计算机性能指标

- (1)总容量

- (2)CPU性能

- (3)系统整体性能指标

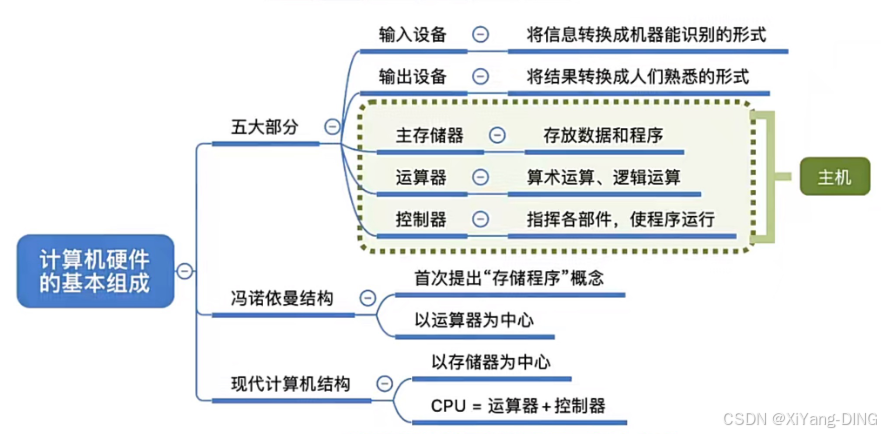

1.1 计算机硬件的基本组成

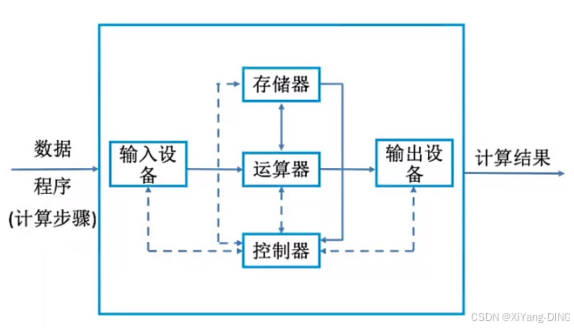

(1)早期冯诺依曼机

- 冯·诺依曼计算机的特点:

- 计算机由五大部件组成

- 指令和数据以同等地位存于存储器,可按地址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 存储程序:程序运行之前会把指令和数据提前存入主存中

- 以运算器为中心

数据的传输需要运算器作为中转

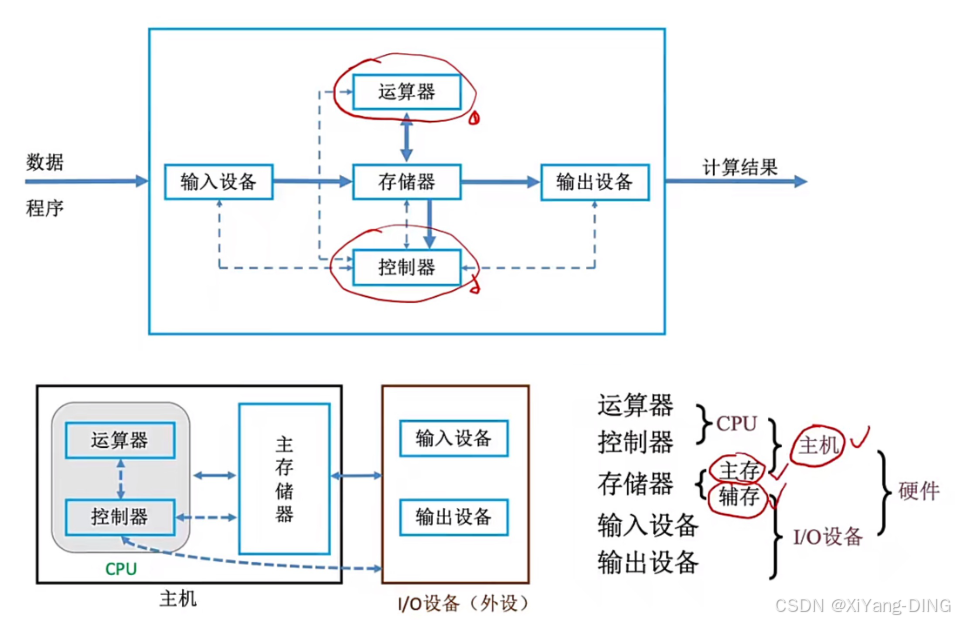

(2)现代计算机结构

- 以存储器为中心

1.2 各个硬件的工作原理

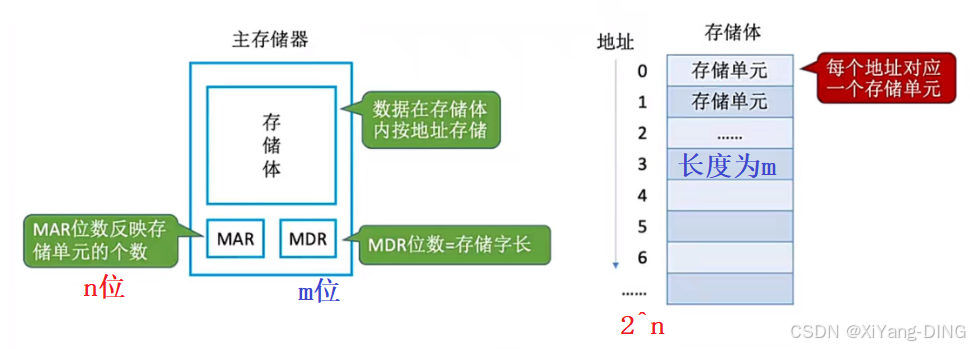

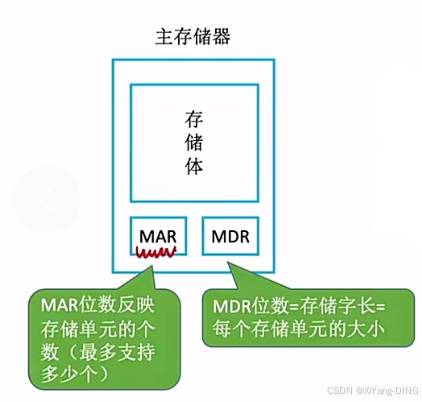

(1)主存储器

- MAR:表示存储器地址寄存器(Memory Address Register),用于存放要访问的内存地址。

- MDR:表示存储器数据寄存器(Memory Data Register),用于存放从内存中读取或要写入内存的数据。

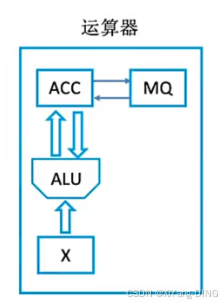

(2)运算器

运算器:用于实现算术运算(如:加减乘除)、逻辑运算(如:与或非)

- ACC:累加器,用于存放操作数,或运算结果。

- MQ:乘商寄存器,在乘、除运算时,用于存放操作数或运算结果。

- X:通用的操作数寄存器,用于存放操作数

- ALU:算术逻辑单元,通过内部复杂的电路实现算数运算、逻辑运算

| 加 (Addition) | 减 (Subtraction) | 乘 (Multiplication) | 除 (Division) | |

|---|---|---|---|---|

| ACC | 被加载、和 | 被减数、差 | 乘积高位 | 被除数、余数 |

| MQ | 乘数、乘积低位 | 商 | ||

| X | 加载 | 减数 | 被乘数 | 除数 |

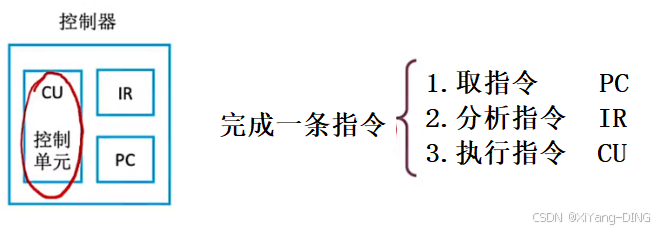

(3)控制器

- CU:控制单元,分析指令,给出控制信号

- IR:指令寄存器,存放当前执行的指令

- PC:程序计数器,有存放下一条指令地址,自动加1功能

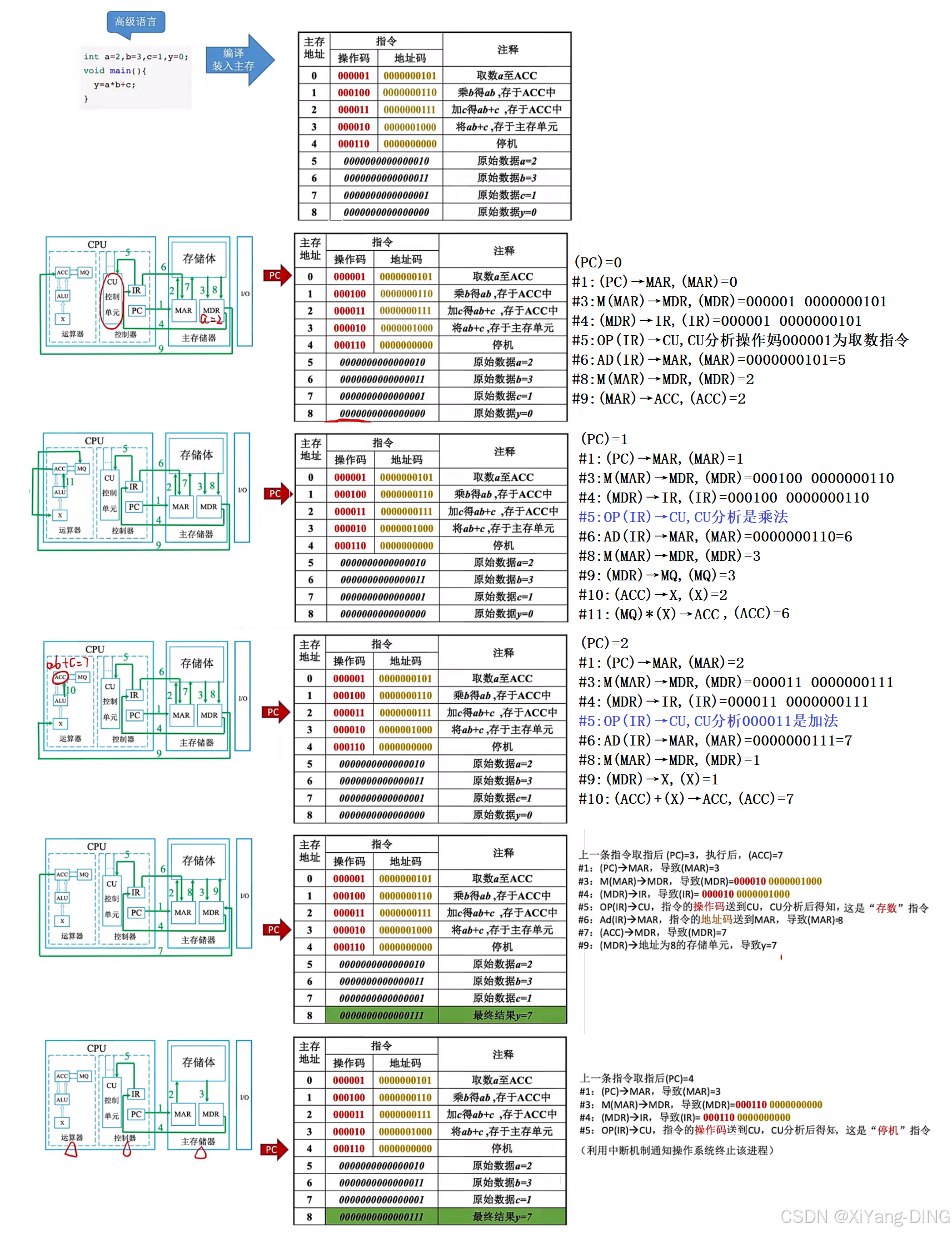

(4)计算机的工作过程

- M:表示主存储器(Main Memory),也就是计算机的内存。

- M(MAR):表示主存储器中地址为MAR的内容。

- M(MAR) → MDR:表示将主存储器中地址为MAR的数据读取到MDR中。

- OP(IR):表示取操作码

- AD(IR):表示去操作数

1.3 计算机软件

1.3.1 三种级别的语言

解释性语言与编译性语言

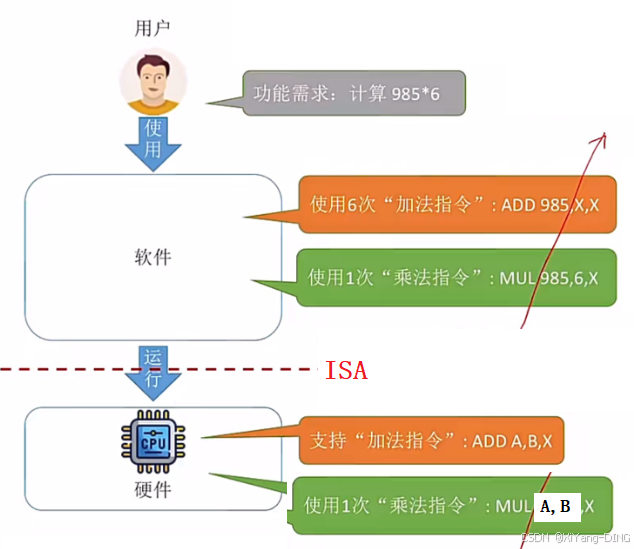

1.3.2 软件和硬件的逻辑功能等价性

- 软件和硬件的逻辑功能等价性:同一个功能,既可以用硬件实现(性能高成本高),也可以用软件实

现(性能低成本也低) - 指令集体系结构(ISA):软件和硬件之间的界面,设计计算机系统的ISA,就是要定义一台计算机可以支持哪些指令,以及每条指令的作用是什么、每条指令的用法是什么。

1.4 计算机系统的层次结构

1.5 计算机性能指标

(1)总容量

总容量=存储单元个数

∗

存储字长

b

i

t

=

存储单元个数

∗

存储字长

/

8

B

y

t

e

总容量=存储单元个数*存储字长bit=存储单元个数*存储字长/8Byte

总容量=存储单元个数∗存储字长bit=存储单元个数∗存储字长/8Byte

K

=

2

10

,

M

=

2

20

,

G

=

2

30

,

T

=

2

40

K=2^{10},M=2^{20},G=2^{30},T=2^{40}

K=210,M=220,G=230,T=240

Eg:MAR为32位,MDR为8位

总容量= 2^(32)*8 bit = 4GB

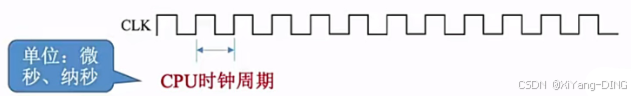

(2)CPU性能

- CPU主频:CPU内数字脉冲信号振荡的频率。

C P U 主频(时钟频率) = 1 / C P U 时钟周期 CPU主频(时钟频率)=1/CPU时钟周期 CPU主频(时钟频率)=1/CPU时钟周期

- CPI(Clock cycle Per Instruction):执行一条指令所需的时钟周期数

- 执行一条指令的耗时=CPI*CPU时钟周期

- IPs(Instructions Per Second):每秒执行多少条指令

(3)系统整体性能指标

- 数据通路带宽:数据总线一次所能并行传送信息的位数(各硬件部件通过数据总线传输数据)

- 吞吐量:指系统在单位时间内处理请求的数量

- 响应时间:指从用户向计算机发送一个请求,到系统对该请求做出响应并获得它所需要的结果的等待时间。

- 基准程序是用来测量计算机处理速度的一种实用程序,以便于被测量的计算机性能可以与运行相

同权子的其它计算机性能进行比较。(跑分软件)