电源完整性08-电容网络配置方法

常用的去耦电容网络设计方法主要有以下两种:BIG-V法、MP法

在低速设计时代,通常的做法就是在芯片的每个供电引脚上添加几个0.1 pF的电容,另外再加几个百微法级的板级滤波电容,这种方法就是BIG-V方法。

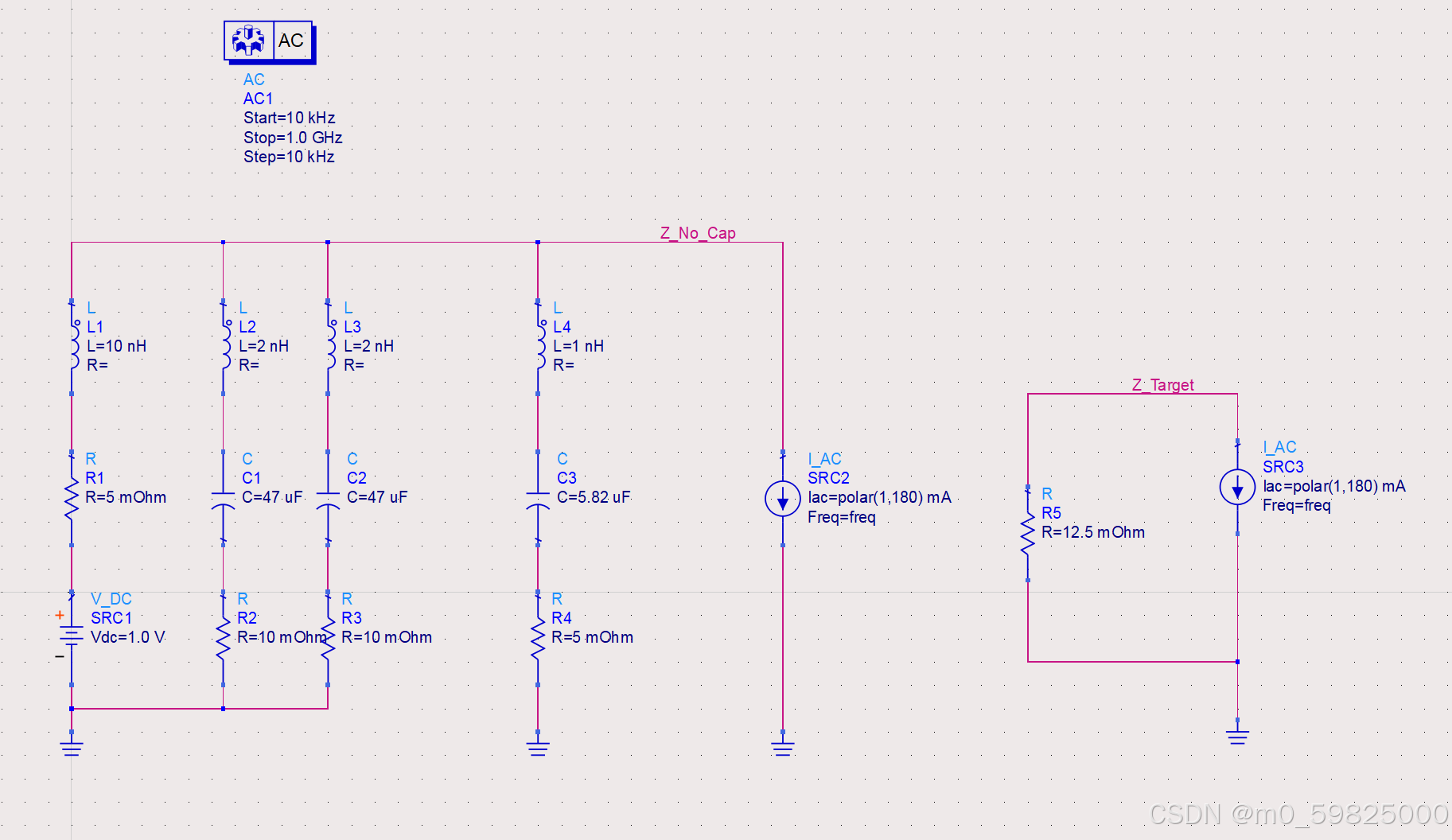

下面用ADS仿真使用BIG-V法配置电容网络,查看该方法对PDN系统的影响,首先配置VRM与大电容模型:

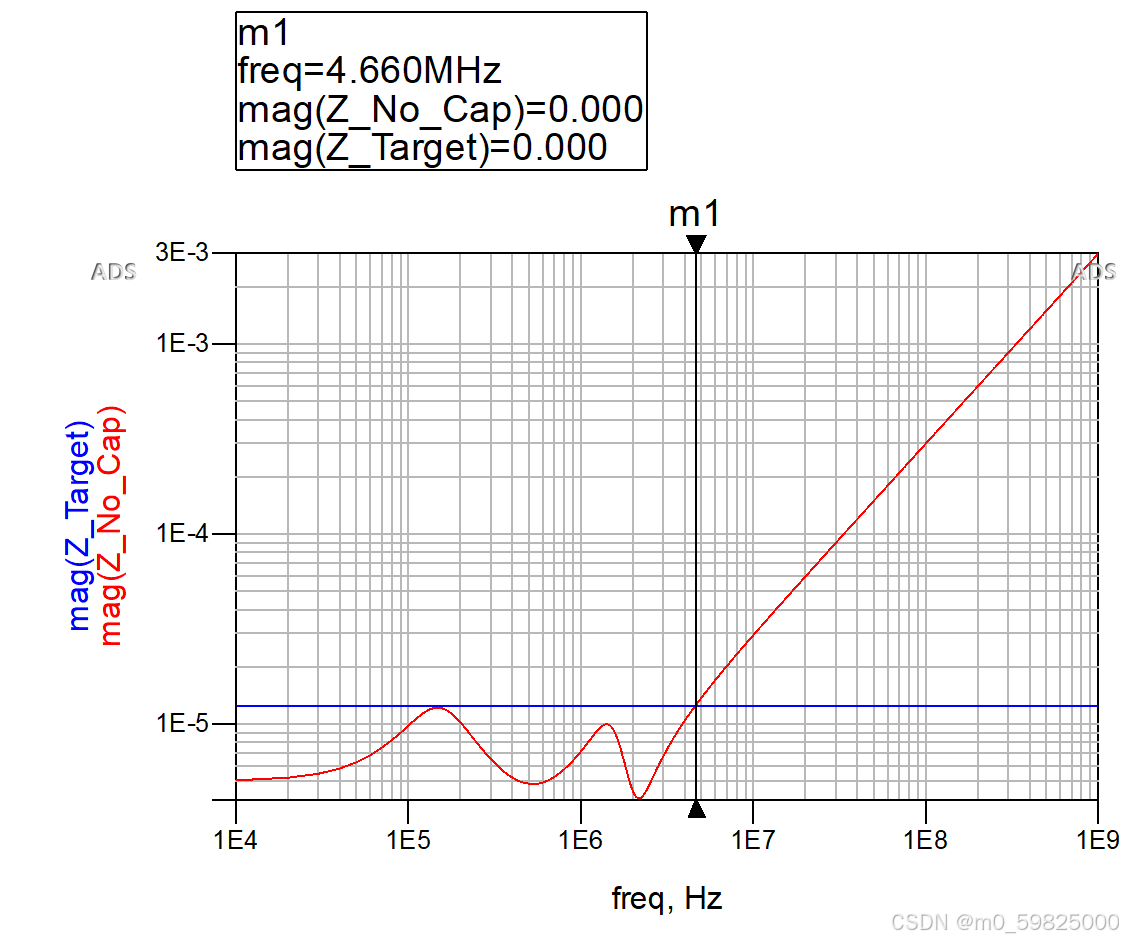

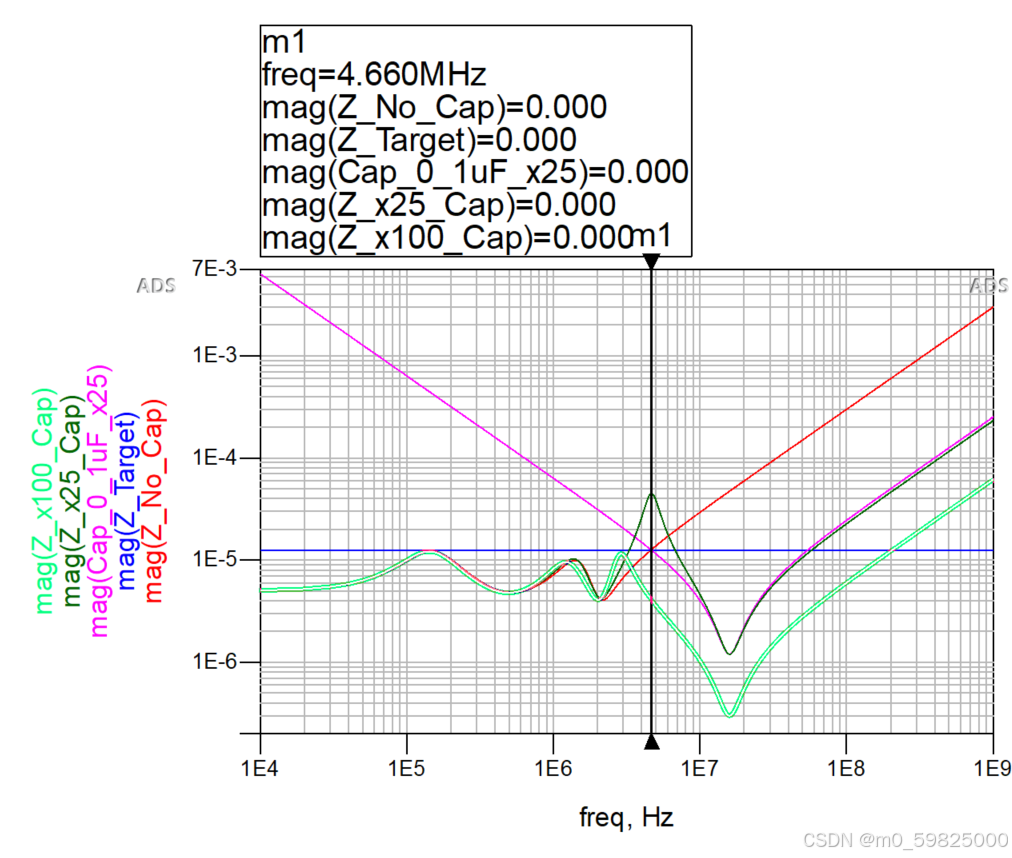

仿真曲线如下:

可见在4.7MHz前PDN系统满足阻抗要求,但是4.7MHz后并不满足。

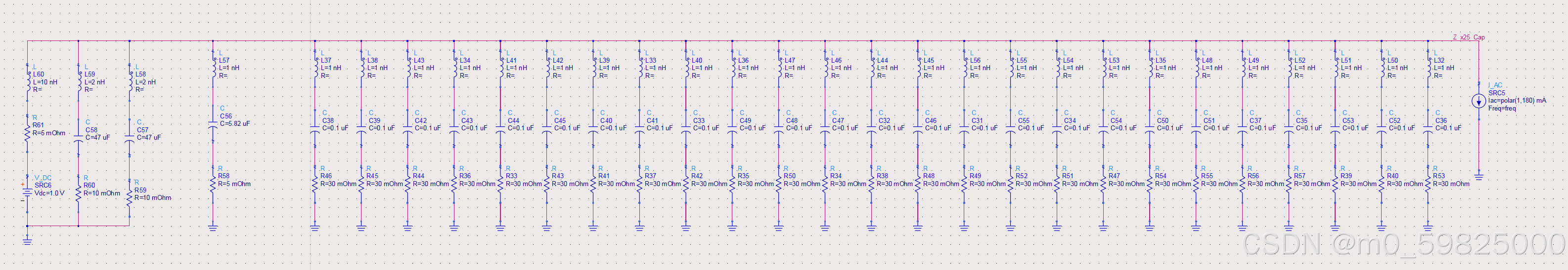

使用BIG-V法往PDN系统中加入25个0.1uF电容,观察PDN系统阻抗曲线变化:

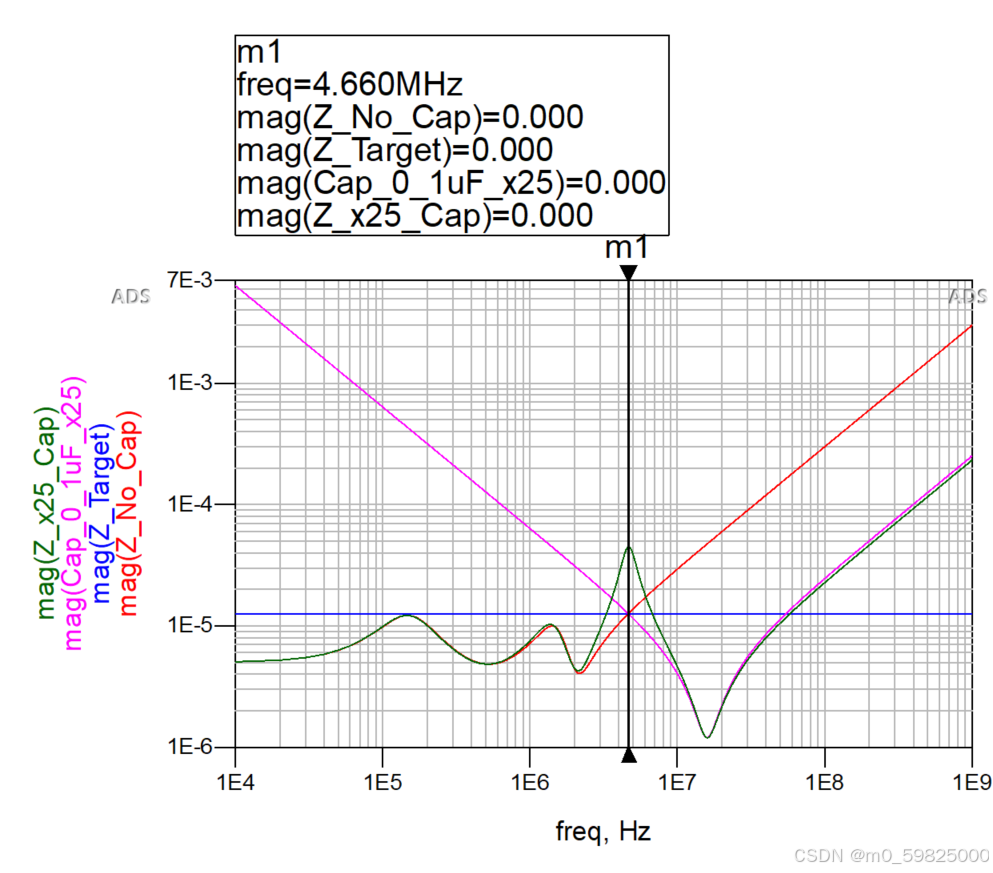

Cap_0_1uF_x25为25个0.1uF电容并联的阻抗曲线,Z_x25_Cap为将25个电容并联到PDN网络中后的阻抗曲线,可以发现处在0.1uF电容自谐振处阻抗确实有改善,但是在4.7Mhz出现并联谐振峰。

BIG-V方法很难控制并联谐振峰,普通的大电容ESR 在欧姆级,少量几个大电容对并联谐振峰的抑制作用非常有限。

如果想把并联谐振峰压低到目标阻抗曲线以 下,可能需要很多电容并联,或者使用特殊的低ESR大电容,即使能够达到目的,成本也会急剧增加,且很多时候PCB上空间限制可能无法放下如此多的电容,因此BIG-V法中阻抗控制存在困难。

下面加入100个0.1uF的电容到PDN网络中,观察阻抗曲线的变化:

可以看到曲线Z_x100_Cap满足PDN阻抗要求,但电容数量太大并不实用。

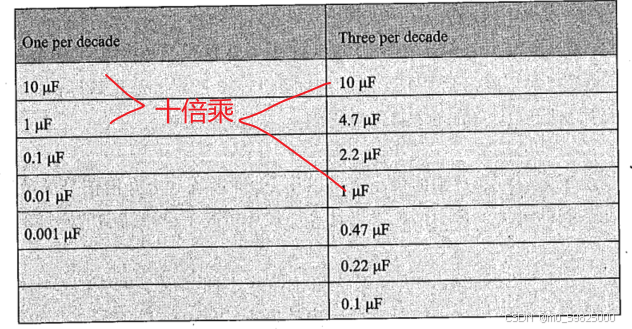

MP法是目前设计最常用的方法,使用多种电容组合起来,共同构建去耦网络。常用的两种方式:One per decade和Three per decade。

One per decade方法在每十倍乘范围内选择一种电容值

Three per decade方法在每十倍乘范围内选择三种电容值

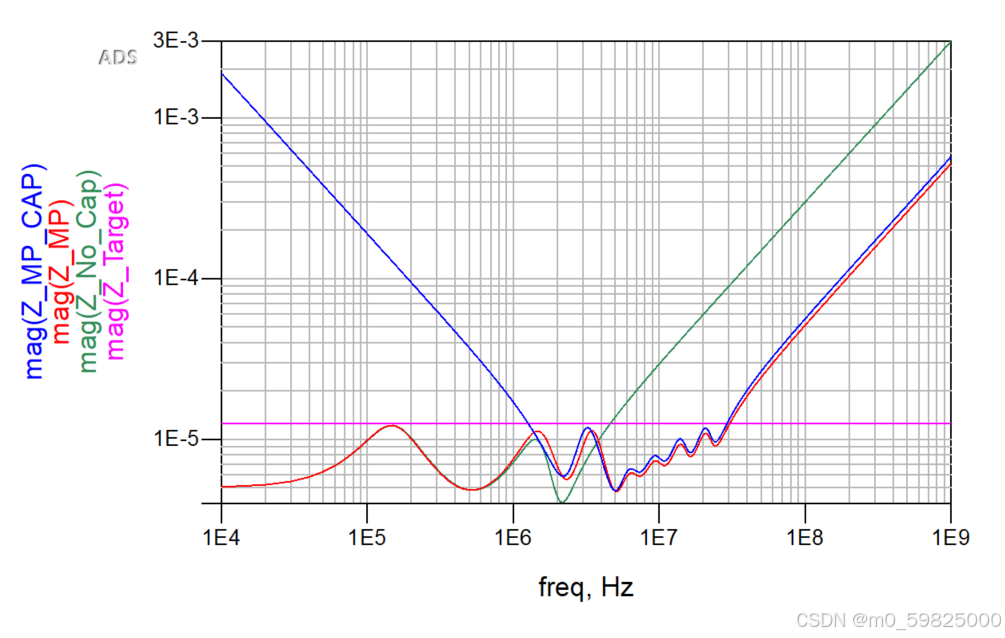

下面用ADS使用MP法观察PDN阻抗曲线的变化:

在PDN网络中加入1个4.7uF、2个1uF、2个0.47uF、2个0.22uF、2个0.1uF、2个0.047uF电容

Z_MP_CAP为单独电容并联的阻抗曲线、Z_MP为电容并联后接入PDN网络的阻抗曲线,可以看到满足阻抗要求且阻抗曲线较平坦。