BLE芯片跳频算法设计

1. 软件(C语言)控制寄存器方案

在这种方案中,跳频序列的选择、定时和信道评估等逻辑算法由运行在CPU(如ARM Cortex-M系列)上的C语言程序实现。

- 工作方式:

- 软件根据蓝牙协议规范,通过算法计算出下一个要跳频到的信道。

- 软件通过写入特定的寄存器,来配置射频前端的频率合成器,将其锁定到目标信道。

- 软件负责处理基带数据包的时序,确保在跳频瞬间没有数据收发。

- 优点:

- 灵活性高:协议更新、跳频算法优化(例如自适应跳频以避开Wi-Fi干扰)都可以通过软件升级轻松完成,无需改动硬件。

- 开发成本低:使用标准的C语言开发和调试,工具链成熟,人力成本相对较低。

- 功耗可能更低:对于低复杂度的任务,专用的硬件可能比唤醒CPU并执行代码更节能,但对于复杂的决策逻辑,软件可以更“聪明”地休眠。

- 缺点:

- 速度和实时性差:CPU需要执行多条指令来完成跳频操作,这会引入微秒级的延迟。在蓝牙高速数据传输时,这个延迟是不可接受的,因为蓝牙在每个1250微秒的时隙内都可能需要跳频。

- 占用CPU资源:跳频是一个高实时性、周期性的任务,会频繁中断CPU处理上层应用(如音频编解码、用户交互等),导致系统效率低下。

2. 硬件(FPGA/ASIC)方案

在这种方案中,跳频的逻辑被设计成专用的数字电路。

- 工作方式:

- 一个硬件状态机根据预定义的规则(如根据蓝牙地址和时钟计算)自动生成跳频序列。

- 一个高精度的硬件定时器在精确的时刻触发跳频动作。

- 硬件电路直接控制频率合成器切换到目标信道。

- 优点:

- 极致的速度和实时性:硬件电路可以在纳秒级别内完成响应和操作,完全满足蓝牙协议的严格时序要求。

- 高可靠性:作为专用电路,其行为是确定性的,不会像软件那样因为中断冲突或代码错误而错过时序。

- 零CPU占用:一旦初始化完成,跳频过程完全由硬件自主完成,CPU可以专注于其他任务或进入低功耗睡眠状态。

- 缺点:

- 灵活性差:电路一旦制造完成(ASIC)或烧录到FPGA,其逻辑就固定了。要修改跳频算法(例如修复一个协议漏洞或引入新的抗干扰技术)几乎是不可能的,或者成本极高。

- 开发成本和复杂度高:需要硬件工程师使用VHDL/Verilog等语言进行设计、仿真和验证,流程更复杂。

- FPGA成本高:对于量产的蓝牙芯片,使用FPGA作为载体是非常不经济的,功耗和面积都远大于ASIC。

3. 主流方案:软硬协同的混合架构

正是为了兼顾实时性和灵活性,几乎所有现代的蓝牙芯片都采用了一种混合架构:

- 硬件负责“执行”:芯片内部会有一个专用的硬件基带处理器或状态机(通常是ASIC实现)。这个硬件单元负责:

- 在精确的微秒级时刻,自动执行射频前端的频率切换。

- 处理精确的包时序、CRC校验等对时间极度敏感的任务。

- 软件负责“决策”:运行在应用处理器上的C语言程序(蓝牙协议栈)负责:

- 初始化和管理:在连接建立时,将计算好的跳频序列参数、定时器配置等写入硬件寄存器和RAM中。

- 高层逻辑:处理连接、断开、加密、配对等复杂的状态管理。

- 智能决策:实现自适应跳频。软件可以通过监听信道质量,判断哪些信道被Wi-Fi或其他设备占用,然后通过修改硬件寄存器中的信道映射表,告诉硬件“避开”这些坏信道。硬件在执行跳频时,会自动跳过这些被标记的信道。

举个例子:

蓝牙耳机和手机连接后,手机的蓝牙协议栈(软件)会计算出初始的跳频序列,并配置给双方的蓝牙芯片硬件。之后,在正常音乐传输中,每一次1250微秒的跳频动作都是由芯片内部的硬件基带控制器自动完成的,完全不需要CPU参与。如果耳机检测到2.4GHz频段干扰严重,其软件可以决策并更新硬件的信道映射表,实现自适应跳频。

4. 结论与总结

特性 | 纯软件方案 | 纯硬件方案 | 主流混合方案 |

实时性 | 差 | 极佳 | 佳 (硬件保证关键时序) |

灵活性 | 极佳 | 差 | 佳 (软件负责策略) |

CPU占用 | 高 | 无 | 低 |

开发成本 | 低 | 高 | 中 |

适用场景 | 对时序要求不高的实验性项目 | 对成本和功耗不敏感的特殊定制芯片 | 几乎所有商用蓝牙芯片 |

所以,回到你的问题:一般的蓝牙芯片,跳频是放在FPGA端还是C语言端?

答案是:关键的、对时序要求极高的跳频“动作”本身,是由硬件数字逻辑(ASIC)完成的,而不是FPGA(在量产芯片中)。而跳频的“策略”、“序列计算”和“自适应”等高级功能,则由C语言编写的软件协议栈来控制。 这种分工协作的模式,完美地平衡了性能、功耗和灵活性,是经过市场验证的最佳实践。

5. CEVA IP中的跳频实现

频率选择模块可由RW-BLE软件用于跳频序列预处理。其运行机制如下:

- RW-BLE软件通过交换存储器中的FREQSELPTR地址指示计算出的跳频序列保存位置。根据要使用的目标跳频序列,RW-BLE软件通过设置FREQSEL_CS<1/2>_SEED值来定义种子输入,同时通过FREQSEL_LLCHMAP<0/1>寄存器设置用于重映射操作的信道映射表。

- 完成设置后,RW-BLE软件通过配置FREQSELCNTL寄存器的FREQSEL_MODE模式位,并向FREQSELCNTL寄存器的FREQSEL_START位写入1来启动跳频序列计算。

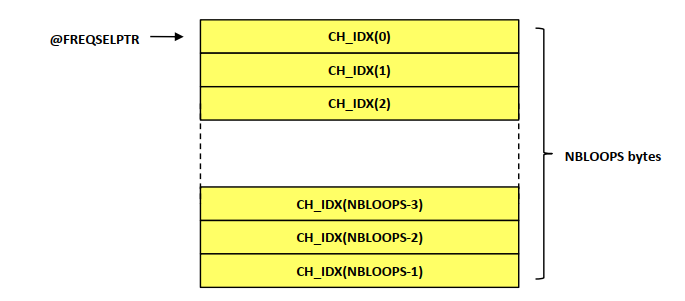

- 在正常终止情况下,RW-BLE软件将收到ble_hop_irq中断。完成后,RW-BLE软件可在FREQSELPTR地址处获取跳频序列信道索引(考虑字节寻址存储器)。

当需要处理任何事件时,可能出现事件控制器要求频率选择模块在软件请求正在进行的同时运行的情况。此时,由于实时跳频处理具有更高优先级,当前频率选择过程将被中止。当实时跳频处理结束后,状态机将重新启动其软件驱动的初始过程直至正常终止,随后FREQSELCNTL寄存器的FREQSEL_START位被复位。

若相关寄存器内容存在错误信息(例如空循环次数),则将设置ERRORTYPESTAT寄存器的FREQSEL_ERROR错误位,并生成ble_error_irq错误中断。