【芯片设计中的时序约束:Multicycle Path与False Path深度解析】

在数字芯片设计中,时序约束是确保电路正确工作的关键。其中,multicycle path(多周期路径)和false path(伪路径)是两种常见的时序例外约束。正确设置它们可以提高时序收敛效率,但设置错误可能导致芯片功能故障。本文将深入解析这两种约束的概念、设置原因、风险及检测难点。

一、什么是Multicycle Path?为什么需要设置?

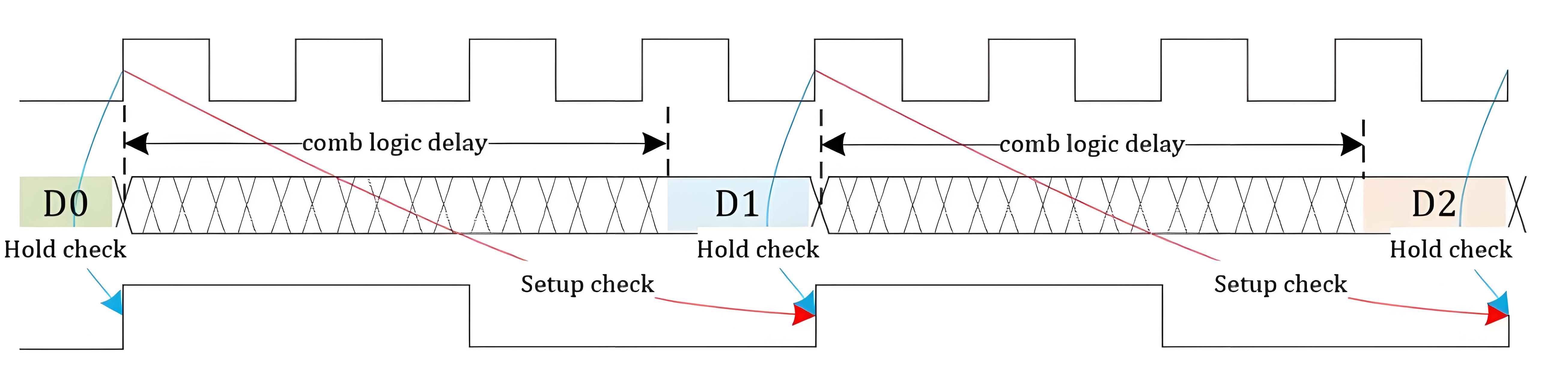

Multicycle path是指数据从源寄存器到目标寄存器需要多个时钟周期才能稳定传输的路径。在默认情况下,静态时序分析工具(如PT、DC)假设所有路径都是单周期的,即数据在一个时钟周期内必须被捕获。但对于某些设计,数据允许在多个周期内变化,这时设置multicycle约束可以正确反映时序要求。

设置原因

1.放松时序约束:当路径延迟较大时,设置multicycle避免工具过度优化,减少面积和功耗。

2.匹配设计意图:例如,慢时钟域到快时钟域的数据传输,可能每N个快时钟周期才采样一次有效数据。不设置multicycle会导致工具检查每个时钟沿,造成虚假违规。

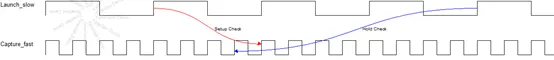

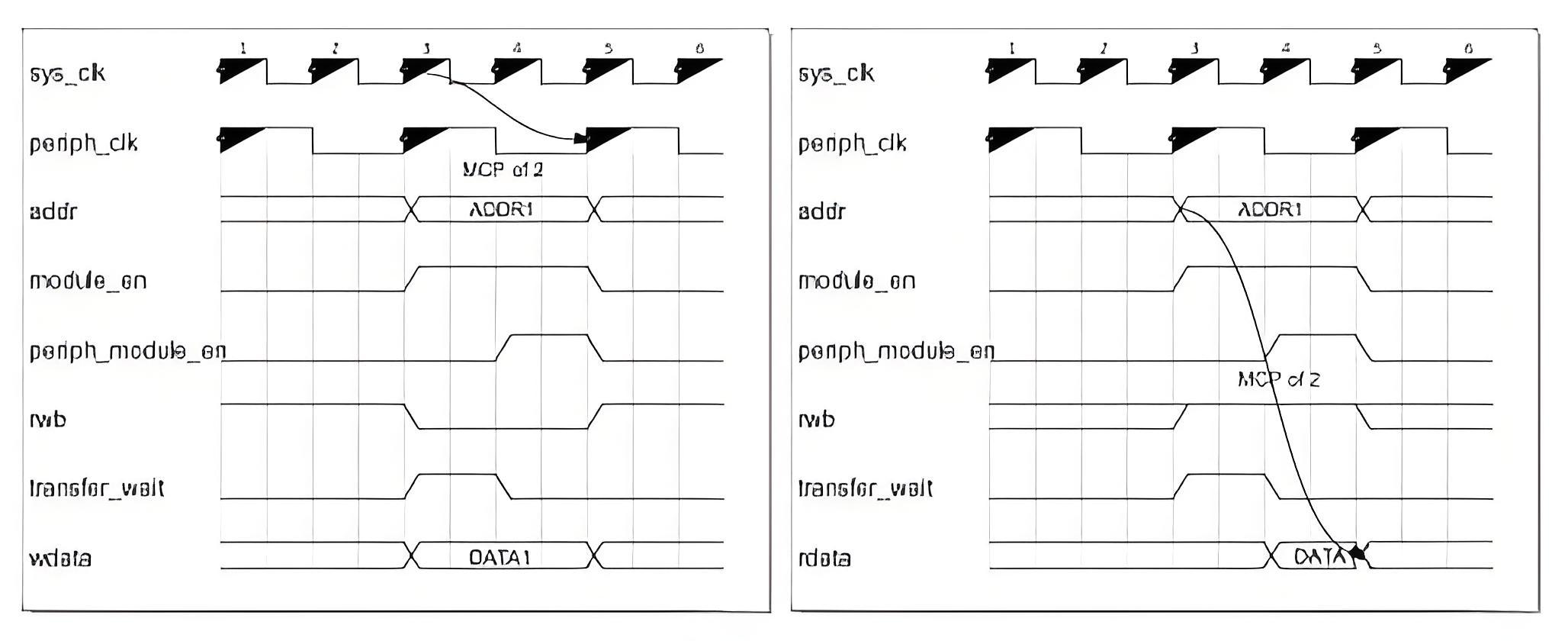

3.在慢时钟(CLKS)到快时钟(CLKD)的案例中,默认检查每个捕获时钟沿,但设计意图是多个周期采样一次。设置multicycle后,时序检查更合理:

风险与设置错误后果

hold检查错误:如果hold multicycle设置不当,检查点可能过于严格或宽松。例如,若hold使用默认值,检查点会前移,导致hold时间不足,引发亚稳态。

功能故障:设置过松可能掩盖真实时序违规;设置过严则导致不必要的优化,影响性能。

multicycle设置错误会使hold检查点偏移,数据在亚稳态窗口被采样:

二、什么是False Path?为什么需要设置?

False path是设计中那些功能上不会发生或不需要时序分析的路径。例如,测试逻辑、异步时钟域路径或静态配置寄存器。设置false path可以避免工具浪费资源优化这些路径。

设置原因

减少优化负担:工具不会对false path进行时序分析和优化,节省计算资源。

避免虚假违规:对于异步路径,由于时钟域不同,时序分析无意义,设置false path防止误报。

false path分为多种类型:

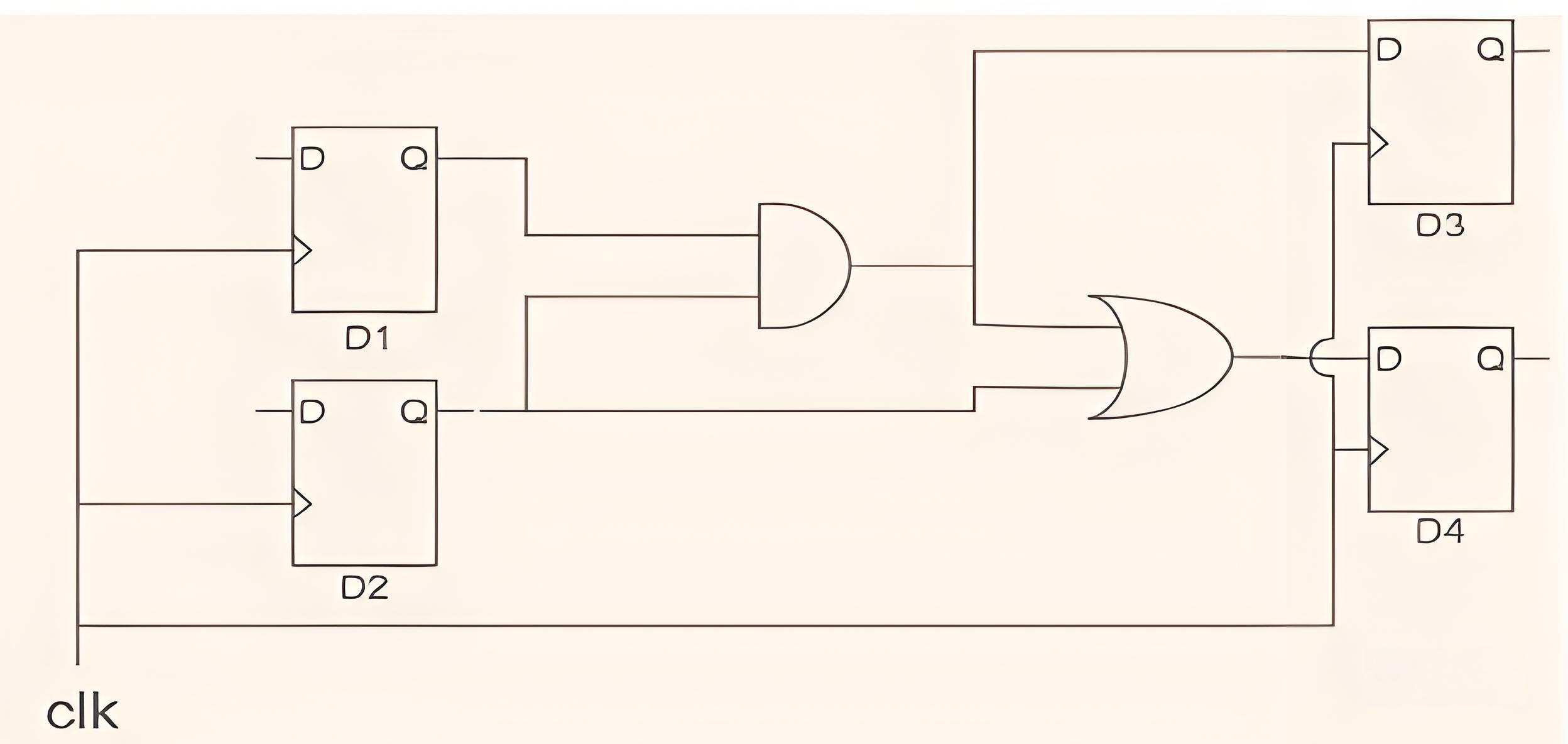

1.Static False Path:源寄存器变化不影响目标寄存器,如配置寄存器到输出路径。

下图描述了Static False Path的示例。这里 D1.Q 的变化永远不会导致 D4.D 的任何变化。D4 flop 的值将始终由 D2 的值决定。因此,对于这个特定的电路,D1->D4 可以被视为False Path。

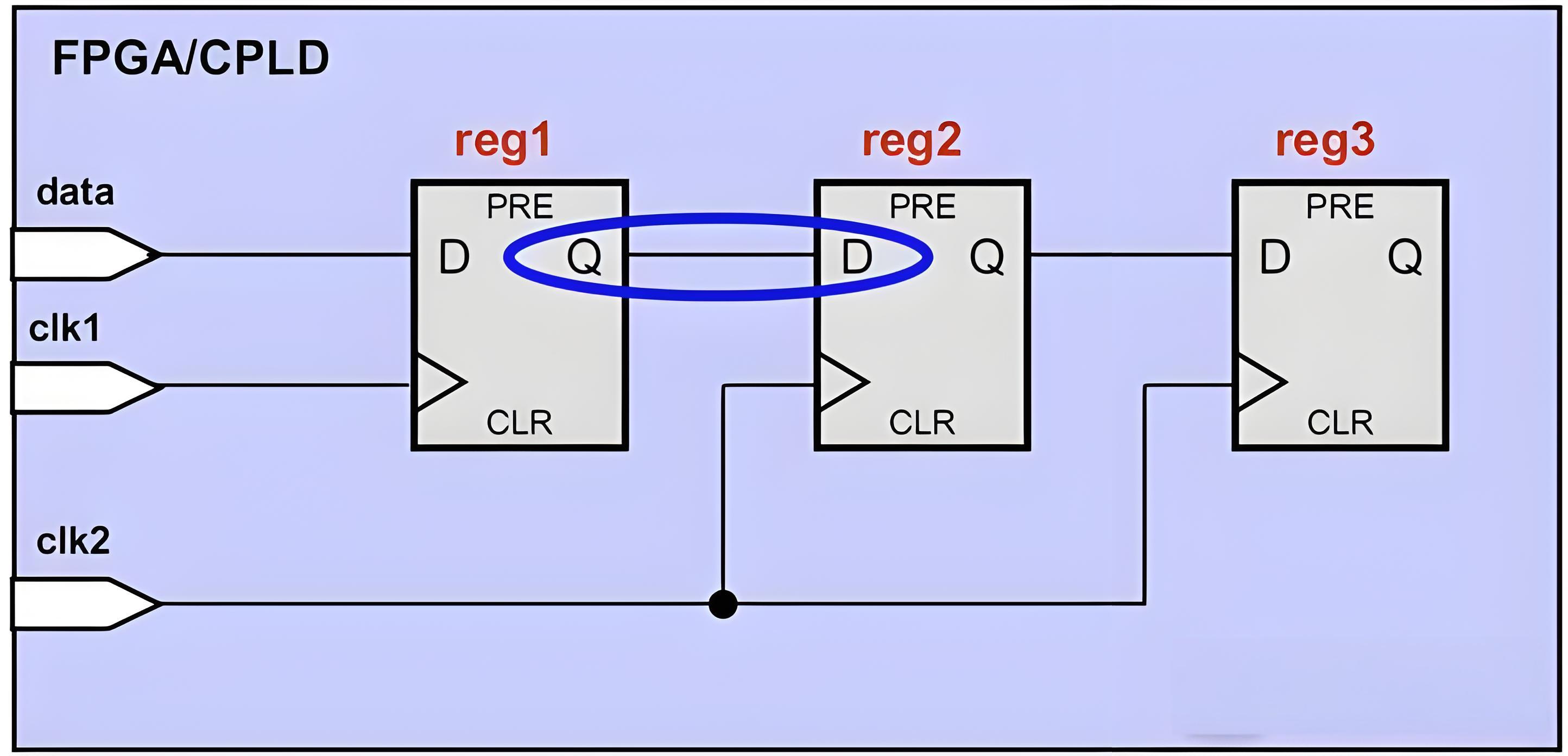

2.Asynchronous False Path:跨异步时钟域的路径,如CDC(时钟域交叉)路径,应使用同步器处理。

风险与设置错误后果

忽略关键路径:如果错误地将真实路径设置为false path,工具不会检查其时序,可能导致芯片失效。例如,半双工接口的数据方向寄存器路径不能设为false path,否则方向变化时可能采样错误。

crosstalk分析错误:异步时钟域应使用set_clock_groups -asynchronous而非set_false_path,因为后者在crosstalk分析中会错误地处理时序窗口,导致延迟计算不准确。

设置错误会使aggressor和victim的timing window重叠忽略,影响信号完整性:

#错误做法

set_false_path -from [get_clock clka] -to [get_clock clkb]

#正确做法

set_clock_groups -asynchronous -group {clka} -group {clkb}

三、设置错误的后果与检测困难

后果

1.功能故障: Multicycle设置错误可能导致数据在亚稳态窗口被采样,引发系统崩溃;false path设置错误则可能使关键路径未被优化,时序违规。

2.性能下降:过度设置multicycle或false path可能使工具忽略真实瓶颈,降低芯片频率。

检测困难点

工具不报告:一旦路径被设置为false path或multicycle,时序分析工具会跳过检查,错误只能在后期验证中暴露。

依赖设计验证:需要全面后仿(覆盖对应path)和硬件测试,但亚稳态等问题可能间歇性出现,难以复现。

跨时钟域复杂性:异步路径错误可能仅在特定时钟相位下触发,增加调试难度。

multicycle设置需严格匹配设计协议,否则读写周期可能错位:

四、最佳实践与结论

谨慎验证:设置multicycle和false path前,必须从设计功能确认路径是否真正多周期或无关。

使用正确命令:异步时钟域用set_clock_groups,避免crosstalk问题。

早期约束:在综合阶段提供准确约束,减少后期迭代。

multicycle和false path是芯片设计的双刃剑。正确设置可提高效率,错误设置则隐藏风险。设计师需深入理解设计意图,结合时序分析工具,确保约束准确无误。