PYNZ搭建高性能CNN部署的快速 FPGA 原型验证框架

本项目旨在为 PYNQ 平台构建一套面向高性能 CNN 部署的快速 FPGA 原型验证框架。

我将设计的这套框架,不仅能最大限度降低工程师在 FPGA 平台上进行 CNN 原型开发的工作量,还能优化 ARM 内核与 FPGA 硬件的协同利用效率,实现业界领先的 CNN 部署速度、准确率和功耗表现。

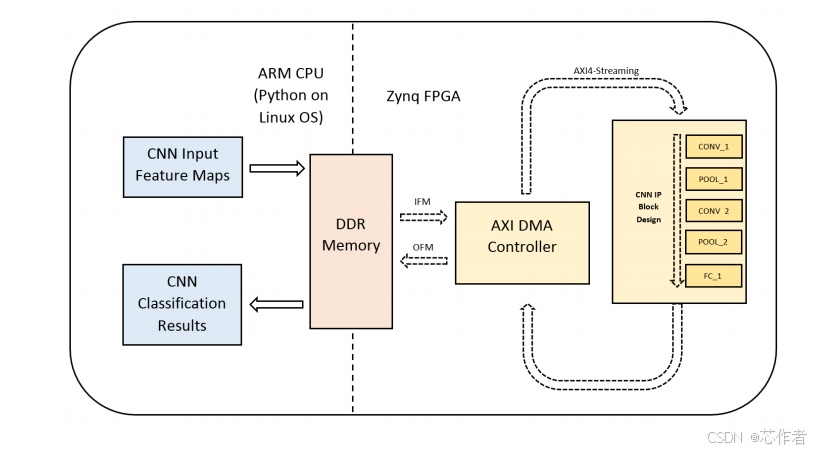

我的目标平台是赛灵思(Xilinx™)PYNQ 开发板。该开发板搭载高性能 Zynq FPGA 芯片,以及运行 Linux 操作系统的双核 ARM-Cortex A9 处理器,是构建本框架的理想选择 —— 框架既需要 FPGA 提供高性能计算(HPC)能力以处理核心任务,也需要 Linux 操作系统支持高级语言设计接口。

作为项目的最终交付物,该框架将包含以下核心组件:

FPGA IP 核库:以块设计(block designs)格式封装,工程师可将其作为 CNN 模型开发的基础构建模块;

Vivado 工程:能将工程师设计的 CNN 模型综合生成为 FPGA 比特流文件;

PYNQ ARM Linux 端 Python 函数:用于在 FPGA 上部署 CNN 模型。

在嵌入式 CNN 部署场景中,系统需要长时间执行大量运算,这类任务属于高吞吐量计算(HTC)任务。因此,速度性能的衡量指标将采用吞吐量,单位为每秒运算次数(OP/s)。

整体架构: