AMBA 总线及AXI协议介绍

目录

一、AMBA 总线概览

1、什么是AMBA总线

2、AMBA 的使用场景

3、AMBA 发展历程

(1)AMBA-APB 协议

(2)AMBA2-AHB 协议

(3)AMBA3-ATB & AHB-lite

(4)AMBA4-AXI4

(5)AMBA5

二、AXI 协议

1、概述

(1)多manager系统

(2)AXI 通道

写操作:

读取作:

3、AXI 的主要功能

三、通道传输

1、通道握手

2、Transfer 和 Transaction之间的区别

3、通道传输示例

4、写传输

(1)写单个数据

(2)写多个数据

5、读传输

(1)读单个数据

(2)读多个数据项

6、Active 传输

四、通道信号

(1)写通道信号

(2)读通道信号

(3)数据大小、长度和突发类型

(4)访问权限信号

(5)缓存支持

(6)响应信号

(7)写数据选通

(8)原子访问

(9)服务质量

(10)区域信令

(11)AXI 通道依赖关系

五、原子访问

1、锁定访问

2、独占访问权限

3、专属交易:均通

4、独占交易对:1 次通过,1 次失败

六、传输行为和时序

1、简单传输示例

2、传输ID 信号

(1)写传输顺序

(2)读传输顺序

(3)读写通道排序

3、非对齐传输起始地址

4、支持字节序

一、AMBA 总线概览

1、什么是AMBA总线

高级微控制器总线架构 (AMBA) 是一种开放标准的片上互连规范,用于连接和管理片上系统 (SoC) 设计中的功能块。 从本质上讲,AMBA 协议定义了功能块如何相互通信。

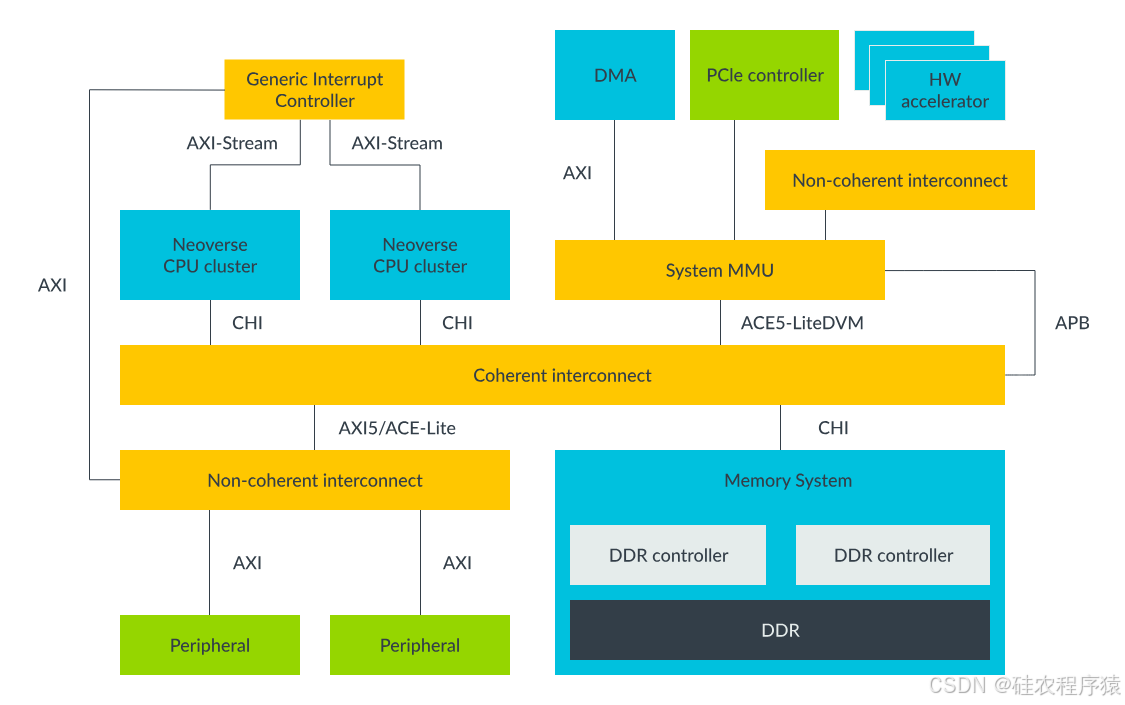

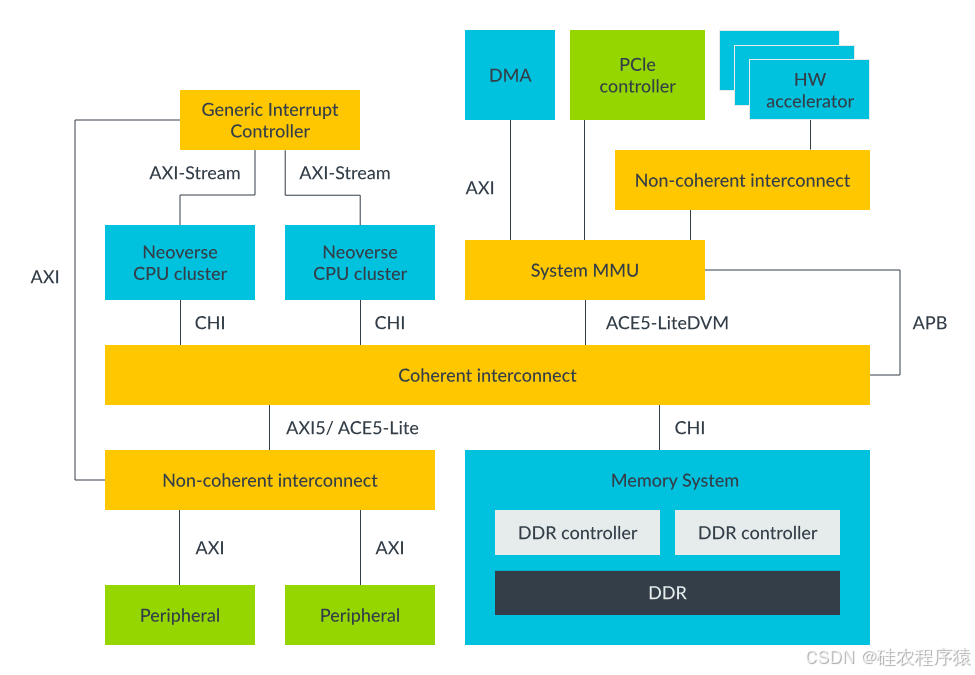

下图显示了 SoC 设计的示例:

此 SoC 具有多个功能块,这些功能块使用 AMBA 协议:APB、ACE-lite、 AXI和CHI 总线进行通信和互联。

2、AMBA 的使用场景

AMBA 简化了具有多个处理器和大量控制器和外设的设计开发,广泛用于ASIC 和 SoC 部件。这些部件包括用于 IoT 子系统、智能手机和网络 SoC 等设备的应用处理器。

使用 AMBA 具有以下几个好处:

- 高效的 IP 重用:IP 重用是降低 SoC 开发成本和时间的重要组成部分。

- 灵活性:AMBA 提供了与一系列 SoC 配合使用的灵活性。IP 重用需要一个通用标准,同时支持具有不同功耗、性能和面积要求的各种 SoC。

- 兼容性:标准接口规范(如 AMBA)允许来自不同设计团队或供应商的 IP 组件之间兼容。

- 支持: AMBA 得到了很好的支持,它在整个半导体行业得到广泛实施和支持,包括来自第三方 IP 产品和工具的支持。

总线接口标准通过它们支持的性能而有所不同,总线接口性能的两个主要特征是:

- 带宽:通过接口驱动数据的速率。在 synchronous system 中,最大带宽受 clock speed 和 data bus宽度的乘积限制。

- 延迟:事务启动和完成之间的延迟。在基于突发的系统中,延迟数字通常是指第一次传输的完成,而不是整个突发。 接口的效率取决于它以零延迟实现最大带宽的程度。

3、AMBA 发展历程

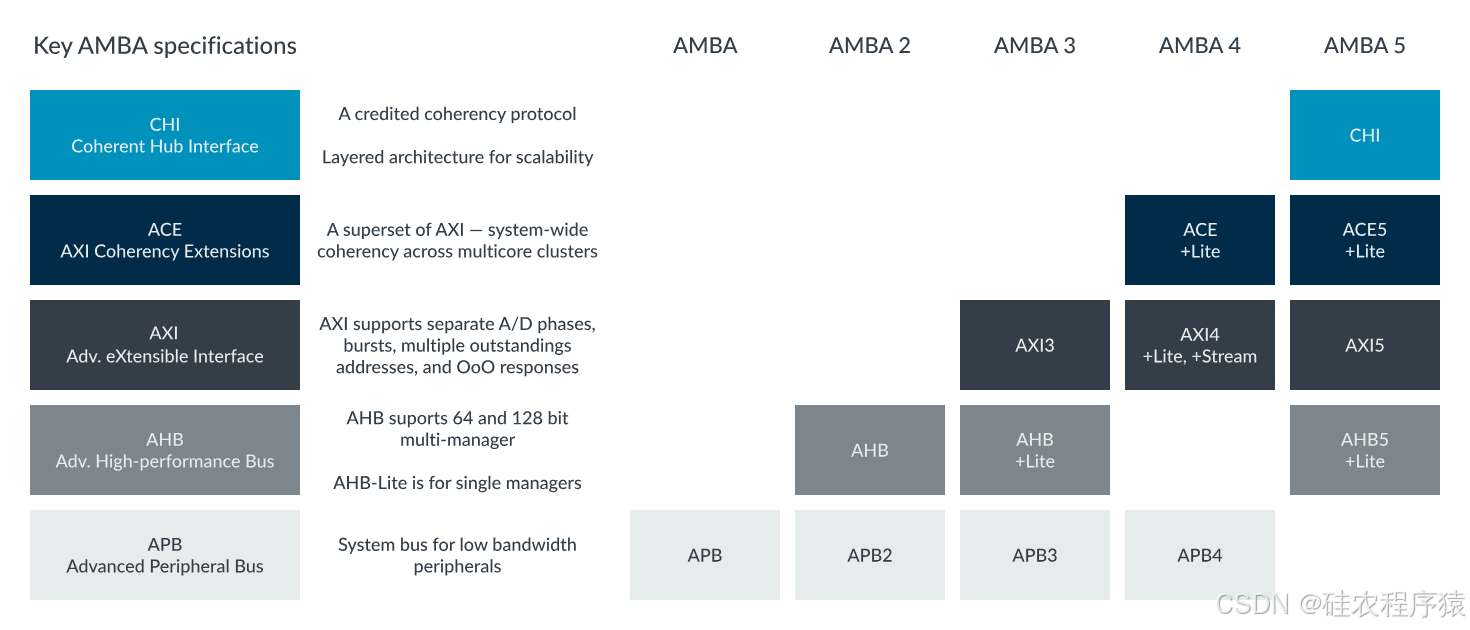

AMBA 多年来不断发展,以满足处理器和新技术的需求。

(1)AMBA

ARM 在1990 年代后期推出了 AMBA。第一代 AMBA 总线是 Advanced System Bus (ASB) 和 Advanced Peripheral Bus (APB)。

ASB 已被更新的协议所取代,而 APB 至今仍被广泛使用。

APB 专为低带宽控制访问而设计,例如系统外设上的寄存器接口。该总线具有简单的地址和数据相位以及低复杂度的信号列表。

(2)AMBA2

1999 年,AMBA 2 增加了 AMBA 高性能总线 (AHB),这是一种单时钟边缘协议。

AHB 上的简单传输由地址阶段和后续数据阶段组成。对目标设备的访问通过 MUX 进行控制,一次允许一个主机访问。

AHB 是为了实现性能而流水线化的,而 APB 不是为了设计简单性而流水线化的。

(3)AMBA3

2003 年,Arm 推出了第三代 AMBA 3,其中包括 ATB 和 AHB-Lite。

高级跟踪总线 (ATB) 是 CoreSight 片上调试和跟踪解决方案的一部分。 AHB-Lite 是 AHB 的一个子集。此子集简化了具有单个 manager 的总线的设计。

高级可扩展接口 (AXI) 是 AMBA 3 规范中定义的第三代 AMBA 接口,面向高性能、高时钟频率系统设计。AXI 包含适用于高速亚微米互连的功能。

(4)AMBA4

2010 年,AMBA 4 规范问世,从 AMBA 4 AXI4 开始,然后是 2011 年的 AMBA 4 AXI 一致性扩展 (ACE)。 ACE 通过额外的信号传输扩展了 AXI,引入了系统范围的一致性。这种系统范围的一致性允许多个处理器共享内存,并支持像 big.LITTLE 处理。

同时,ACE-Lite 协议实现了单向一致性。单向一致性使网络接口能够从完全一致的 ACE 处理器的高速缓存中读取数据。 AXI4-Stream 协议设计用于从主机到从属设备的单向数据传输,减少了信号路由,非常适合在 FPGA 中实现。

(5)AMBA5

AMBA5 2014 年,推出了 AMBA 5 相干集线器接口 (CHI) 规范,该规范重新设计了高速传输层和旨在减少拥塞的功能。CHI 协议已经有多个版本,每个新版本都增加了新功能。

2016 年,AHB-Lite 协议更新为 AHB5,以补充 Armv8-M 架构,并将 TrustZone 安全基础从处理器扩展到系统。

2019 年,推出了 AMBA 自适应流量配置文件 (ATP)。ATP 补充了现有的 AMBA 协议,用于以简洁、简单和可移植的方式对高级内存访问行为进行建模。

AXI5、ACE5 和 ACE5-Lite 扩展了前几代产品,包括许多性能和可扩展性功能,以与 AMBA CHI 保持一致和补充。一些新功能和选项包括:

- 支持多个处理器之间的高频、非阻塞一致数据传输。

- 分层模型允许分离通信和传输协议,以实现灵活的拓扑结构,例如交叉杆、环形、网状或临时拓扑。

- 缓存存储,允许加速器或 IO 设备将关键数据存储在 CPU 缓存中,以实现低延迟访问。

- 远原子作使互连能够对共享数据执行高频更新。

- 端到端数据保护和poisoning信号。

二、AXI 协议

1、概述

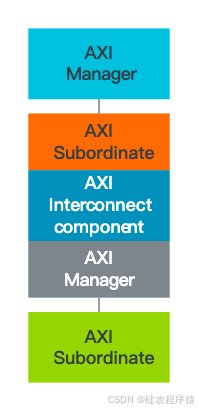

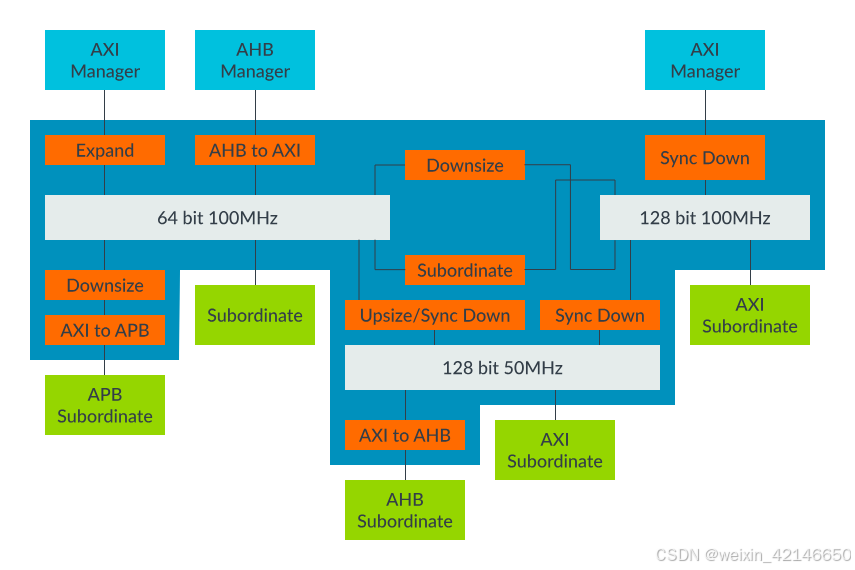

AXI 是一种接口规范,用于定义 IP 模块的接口,而不是互连本身。 下图显示了如何使用 AXI 连接互连组件:

AXI 接口类型只有两种 :manager 和 subordinate,这些接口类型是对称的,所有 AXI 连接都位于主机接口和从属接口之间,上图显示了 AXI 连接如何联接manager 和slave接口。直接连接在 manager和slave组件之间提供最大带宽,无需额外logic。

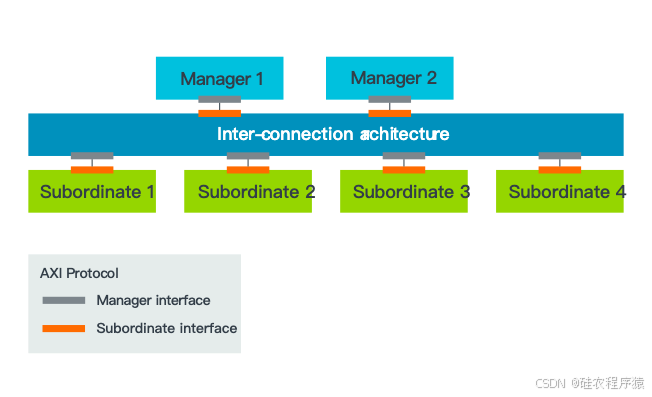

(1)多manager系统

下图显示了 SoC 系统的简化示例,该系统由主机、从机和将它们全部链接的互连组成:

Arm 处理器是主机的一个例子,从属处理器的一个简单例子是内存控制器。 AXI 协议定义了主机和从属设备之间点对点连接的信号和时序。

注意

AXI 协议是点对点规范,而不是总线规范。因此,它仅描述接口之间的信号和时序。

上图显示每个 AXI 主机接口都连接到一个 AXI 从属接口。当有多个主机和从机时,需要一个互连结构。

下图显示互连是一个复杂的元件,需要AXI 主机和从机接口才能与外部功能块通信:

下图显示了具有各种处理器和功能块的 SoC 示例:

上图显示了使用 AXI 的所有连接, AXI3 和 AXI4 在同一个 SoC 中使用,这种情况下,互连在不同 AXI 接口之间执行协议转换。

(2)AXI 通道

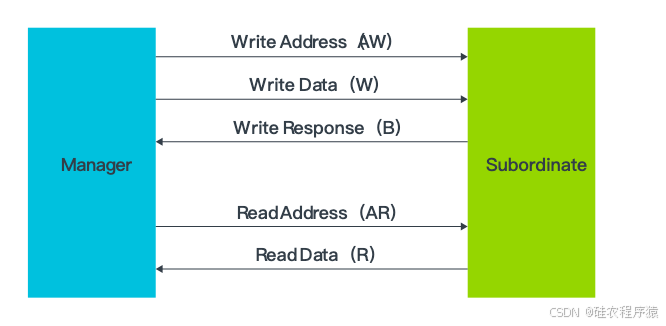

AXI 规范描述了两个接口之间的点对点协议,下图显示了每个 AXI 接口用于通信的五个主要通道:

写操作:

主机在 Write Address (AW) 通道上发送地址,并将 Write Data (W) 通道上的数据传输给从从机。

从机将收到的数据写入指定的地址。一旦从机完成写操作,它就会在 Write Response (B) 通道上向主机发送消息。

读取作:

master发送它想要在 Read Address (AR) 通道上读取的地址。

从机将数据从请求的地址发送到 Read Data (R) 通道上的 master。从机还可以在 Read Data (R) 通道上返回错误消息。如果地址无效、数据损坏或访问权限没有正确的安全权限,则会发生错误。

注意

每个通道都是单向的,因此需要一个单独的 Write Response 通道来将响应传递回 master。但是,不需要 Read Response 通道,因为 Read Response 是作为 Read Data 通道的一部分传递的。

使用单独的地址和数据通道进行读写传输有助于最大化接口的带宽。读和写 通道之间没有 timing relationship,可以同时发生。

3、AXI 的主要功能

AXI 协议旨在提高数据传输和事务的带宽和延迟,如下所示:

- 独立的读取和写入通道:AXI 支持两组不同的通道,一组用于写操作,另一组用于读操作。有助于提高接口的带宽性能,支持读写同时发生。

- 多个未完成的地址(oustanding):AXI 允许多个未完成的地址。这意味着manager可以发布请求,而无需等待前面的交易完成。这可以提高系统性能,因为它支持并行处理事务。

- 地址和数据之间没有严格的时序关系:使用 AXI 时,地址和数据作之间没有严格的时序关系。这意味着,例如,master 可以在 Write Address 通道上发出一个写地址,但是没有时间要求主机何时必须提供相应的数据以写入 Write Data 通道。

- 支持未对齐的数据传输:对于由宽度超过一个字节的数据传输组成的任何突发,访问的第一个字节可以与自然地址边界不对齐。例如,从字节地址 0x1002 开始的 32 位数据包与自然 32 位地址边界不对齐。

- 无序事务完成(out of order):AXI 可以完成无序事务。AXI 协议包含事务标识符,并且对不同 ID 值的事务的完成没有限制。这意味着单个物理端口可以通过充当多个逻辑端口来支持无序事务,每个逻辑端口都按顺序处理其事务。

- 基于起始地址的突发传输:AXI 主机仅发出第一次传输的起始地址。对于任何后续传输,从属将根据突发类型计算下一个传输地址。 渠道转账和交易 本节解释了 AXI 通道的握手原则,并展示了握手如何成为所有读写事务的基础机制。

三、通道传输

1、通道握手

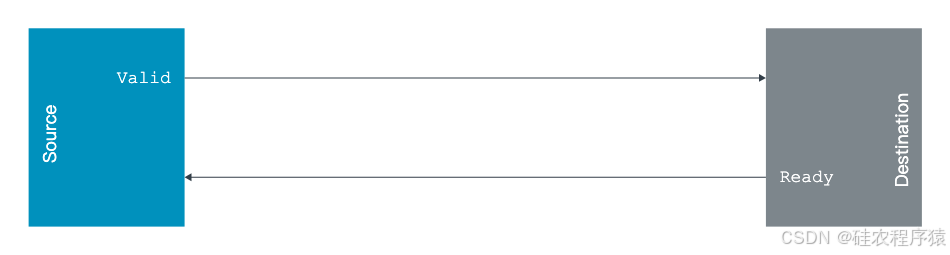

AXI4 协议定义了五个不同的通道,如AXI 通道.所有这些通道共享基于 VALID 和 READY 信号的相同握手机制,如下图所示:

VALID 信号从源到目标,而 READY 信号从目标到源。 源或目标是 master还是 subordinate 取决于所使用的通道。 源使用 VALID 信号来指示何时有有效信息可用。VALID 信号必须保持置位状态,即设置为高电平,直到目标接受信息。以这种方式保持置位状态的信号称为粘性信号。 目标指示何时可以使用 READY 信号接受信息。READY 信号从通道目标传递到通道源。 这种机制不是异步握手,需要 clock 的 rising edge 才能完成握手。

2、Transfer 和 Transaction之间的区别

AXI 对Transfer 和 Transaction进行了区分:

Transfer是一次信息交换,具有一次 VALID 和 READY 握手。

Transaction是整个突发传输,包含一个地址传输、一个或多个数据传输,以及一个响应传输(对于写入序列)。

⚠️也就是一个transaction可以包括多个transfer!

3、通道传输示例

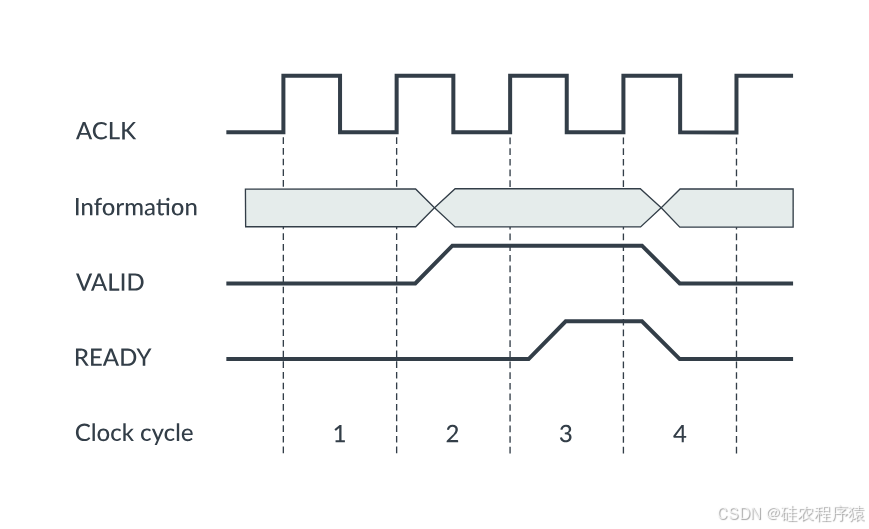

如下图所示,有一个 clock 信号,然后是一个信息总线, VALID先于READY 信号拉起

传输时序如下:

- 在 T2 中,VALID 信号被置位,表示 information 通道上的数据有效。

- 在 T3 中,下一个 clock cycle,READY 信号被置位。

- 握手在T4 的上升沿完成,因为 READY 和 VALID 信号都被置位。

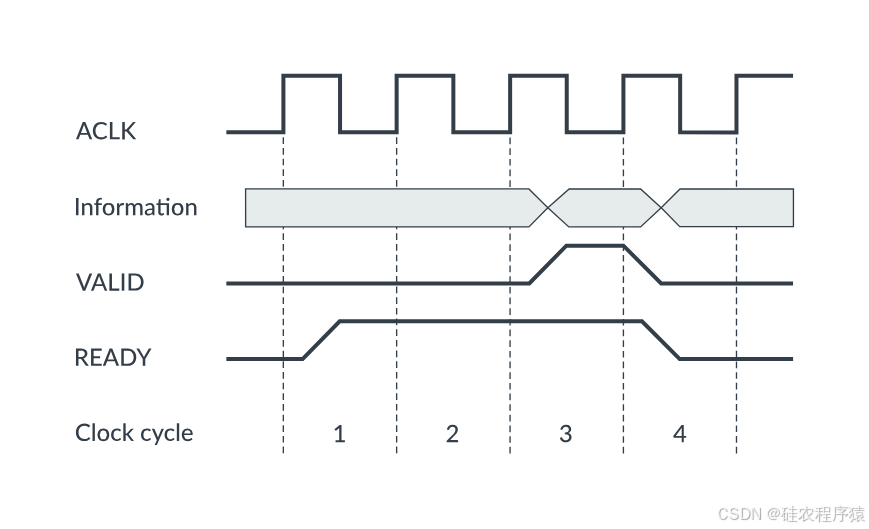

下图显示了另一个示例,ready 先于valid 信号拉起

传输时序如下:

- 在T1 中,READY 信号被置位。

- VALID 信号在 T3 时被置位。

- 握手在T4 的上升沿完成,此时 VALID 和 READY 都被置位。

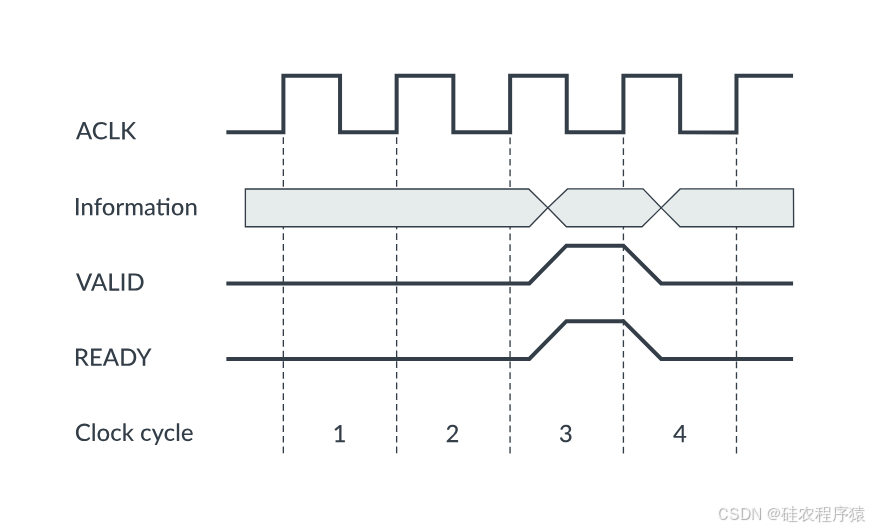

最后一个示例显示了在 T3 期间被置位的 VALID 和 READY 信号,如下图所示:

同样,握手在T4 的上升沿完成,此时 VALID 和 READY 都被置位。 在所有3个示例中,当 READY 和 VALID 在 clock 上升沿置位时,握手成功。

读取和写入握手必须遵守以下规则:

- 源端不能等待 READY 被断言后再断言 VALID

- 目地端可以等待 VALID 被断言,然后再断言 READY

这些规则意味着 READY 可以在 VALID 之前或之后断言,甚至可以同时断言。

4、写传输

(1)写单个数据

写传输涉及以下通道: 写入地址 (AW)、 写数据 (W)和 写响应 (B)

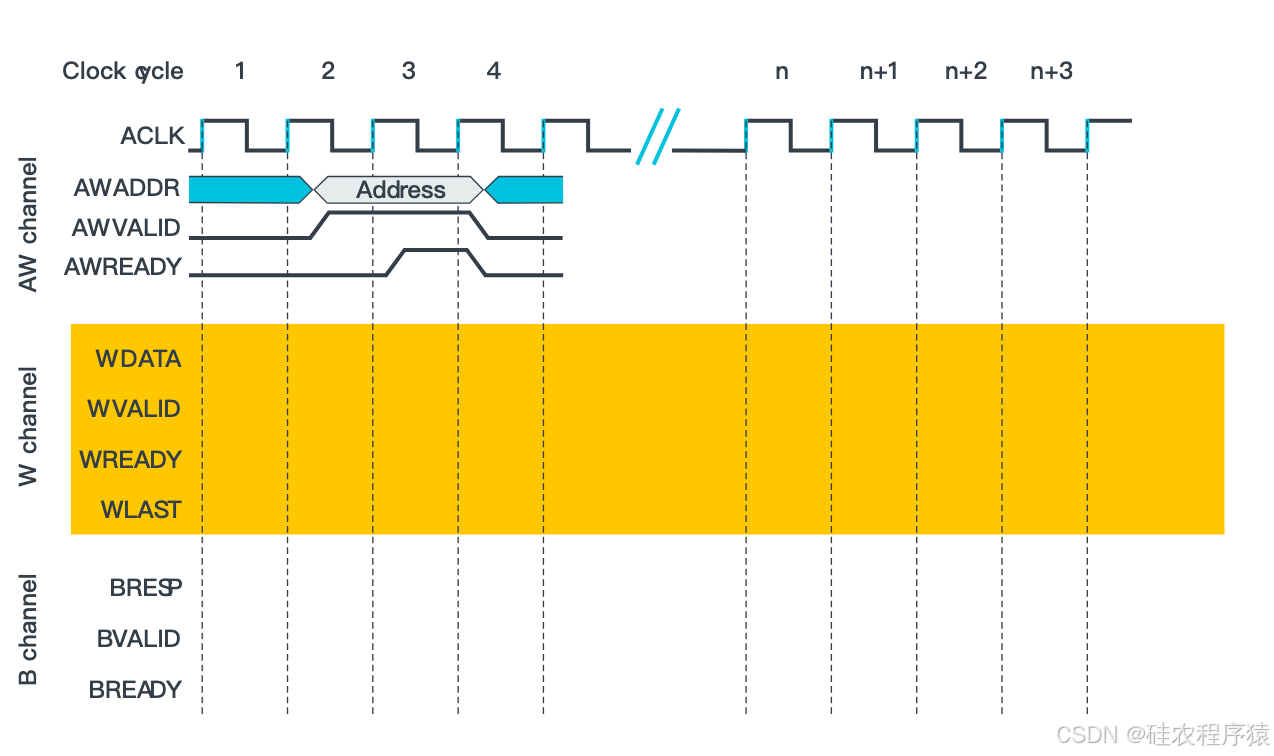

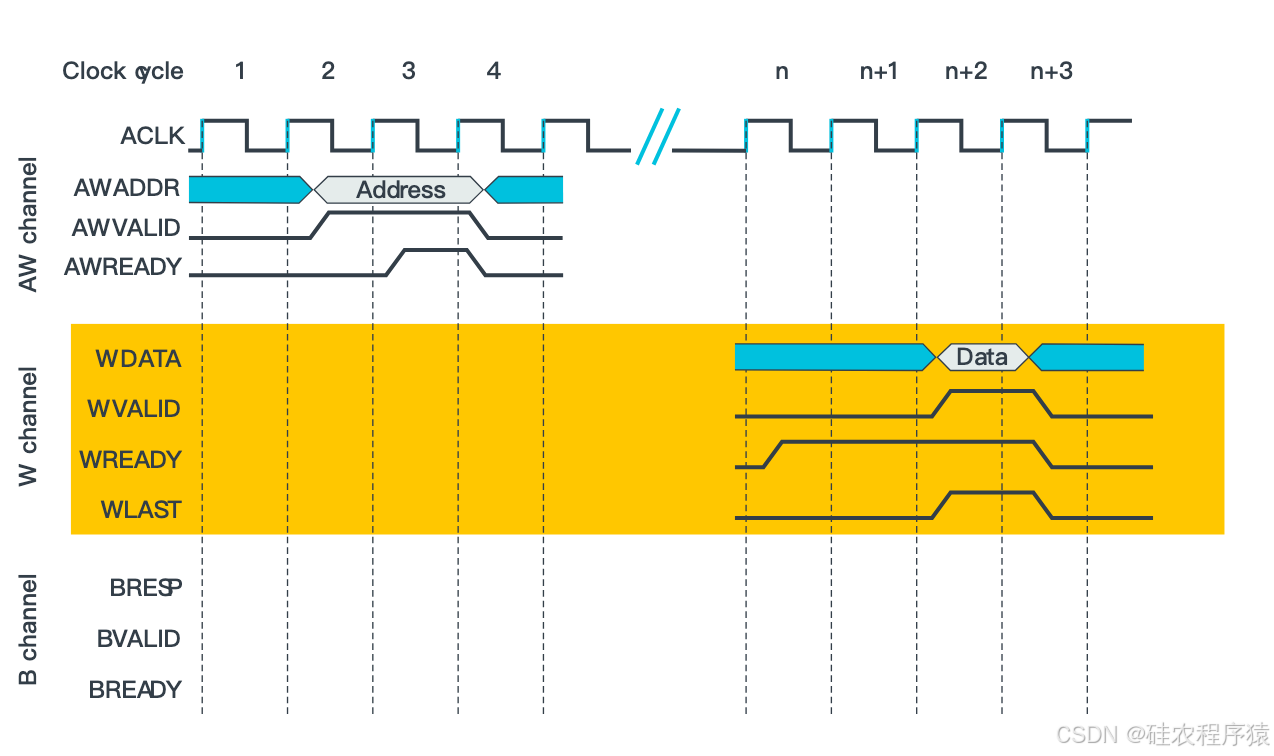

首先,在 Write Address (AW) 通道上进行握手,如下图所示:

握手过程为:

1、manager 将地址放在 AWADDR 上,并在 T2 时刻置位 AWVALID

2、slave在 T3 中置位 AWREADY 以指示其接收地址值的能力

3、握手在 T4 的上升沿完成

在第一次握手之后,manager 将数据传输到 Write (W) 通道上的从属通道,如下图所示

握手过程为:

1、slave正在等待数据,WREADY 在 Tn 时拉高

2、manager将数据放在 WDATA 总线上,并在 Tn+2 中置位 WVALID

3、握手在 Tn+3 的上升沿完成

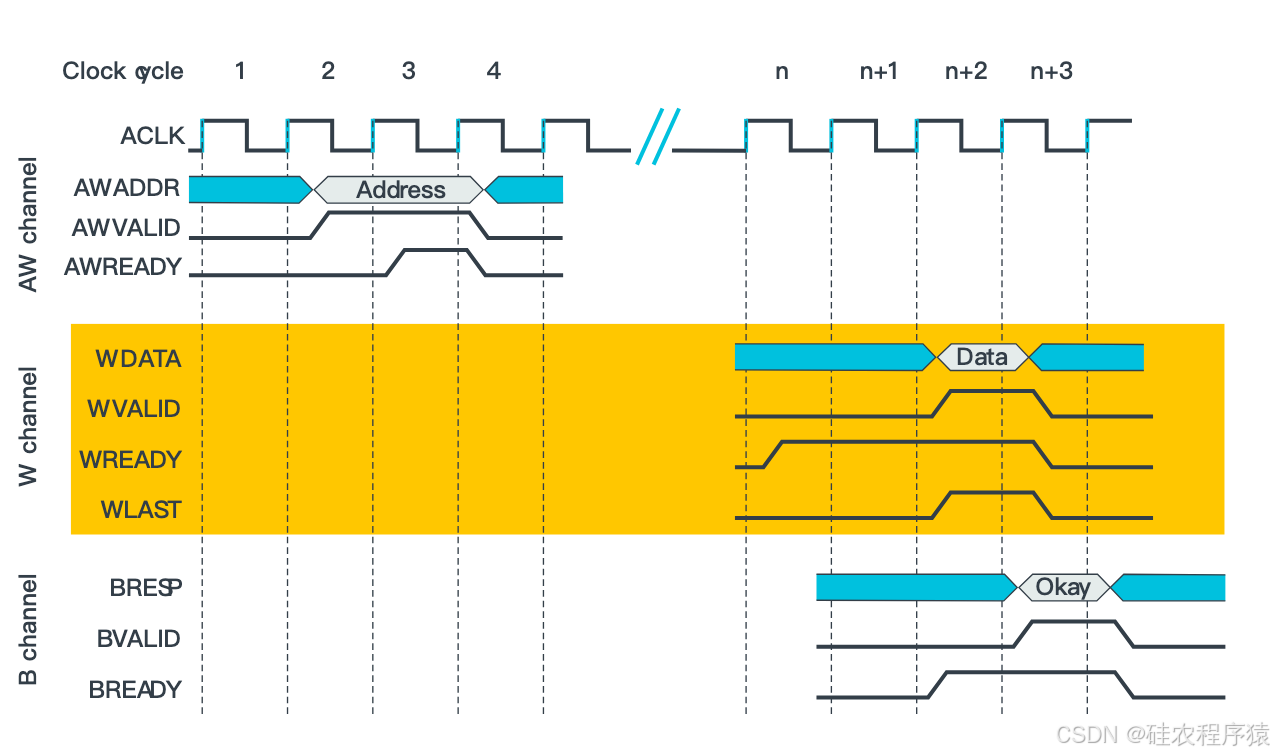

最后,slave使用 Write Response (B) 通道,确认在收到所有 WDATA 后写传输已完成。

响应如下图所示:

写响通道顺序如下:

1、manager断言 BREADY

2、slave驱动 BRESP 以指示写传输成功或失败,并断言 BVALID

3、握手在Tn+4 的上升沿完成

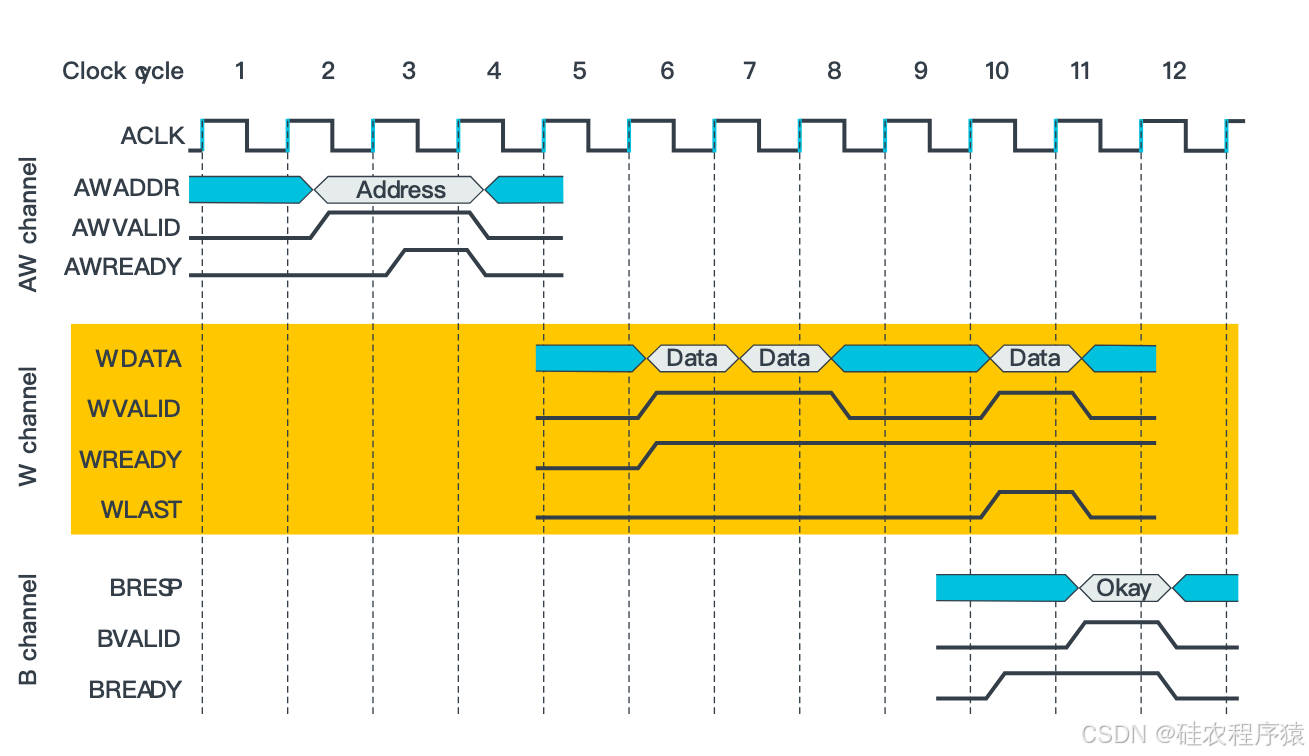

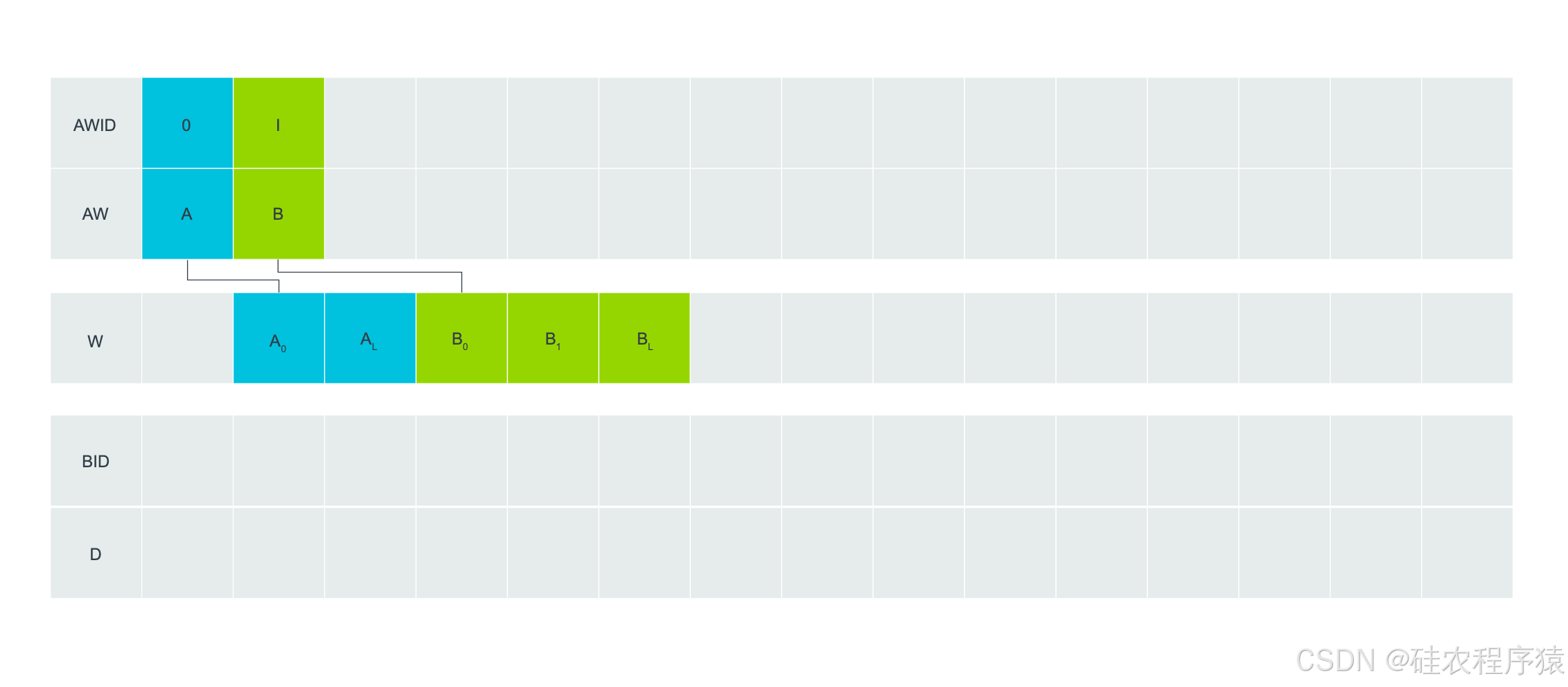

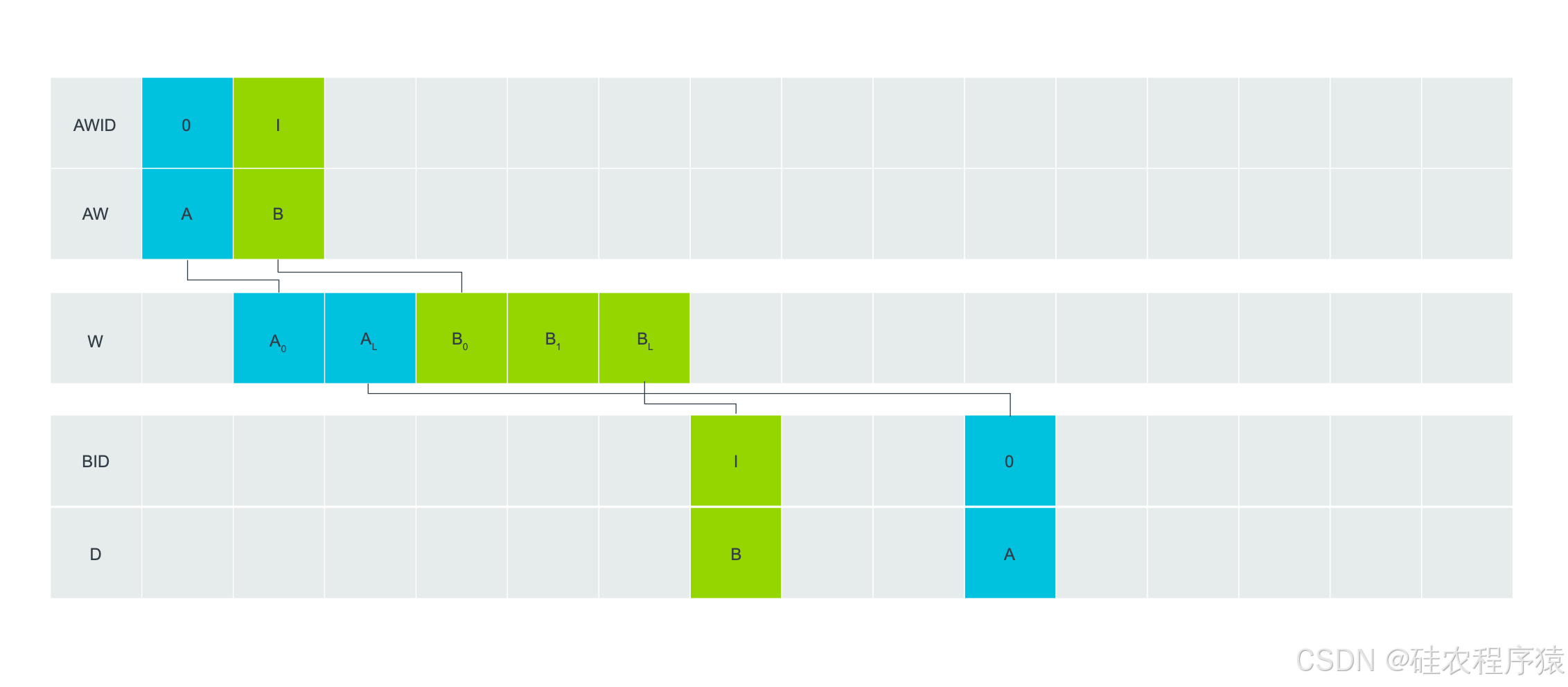

(2)写多个数据

AXI 是基于突发的协议,可以在单个transaction 中传输多个数据。通过在AW 通道上传输单个地址,以传输多个数据,以及相关的突发宽度和长度信息。

下图显示了多个数据传输的示例:

在本例中,AW 通道指示三个传输的序列,而在 W 通道上,有三个数据传输。 主机将 WLAST 驱动为高电平以指示最终的 WDATA。这意味着slave可以计算数据传输量,也可以只监视 WLAST。 收到所有 WDATA 传输后,slave在 B 通道上给出一个 BRESP 值。

如果slave发现传输存在错误,必须等到整个transaction完成,才能通知 manager 发生了错误。

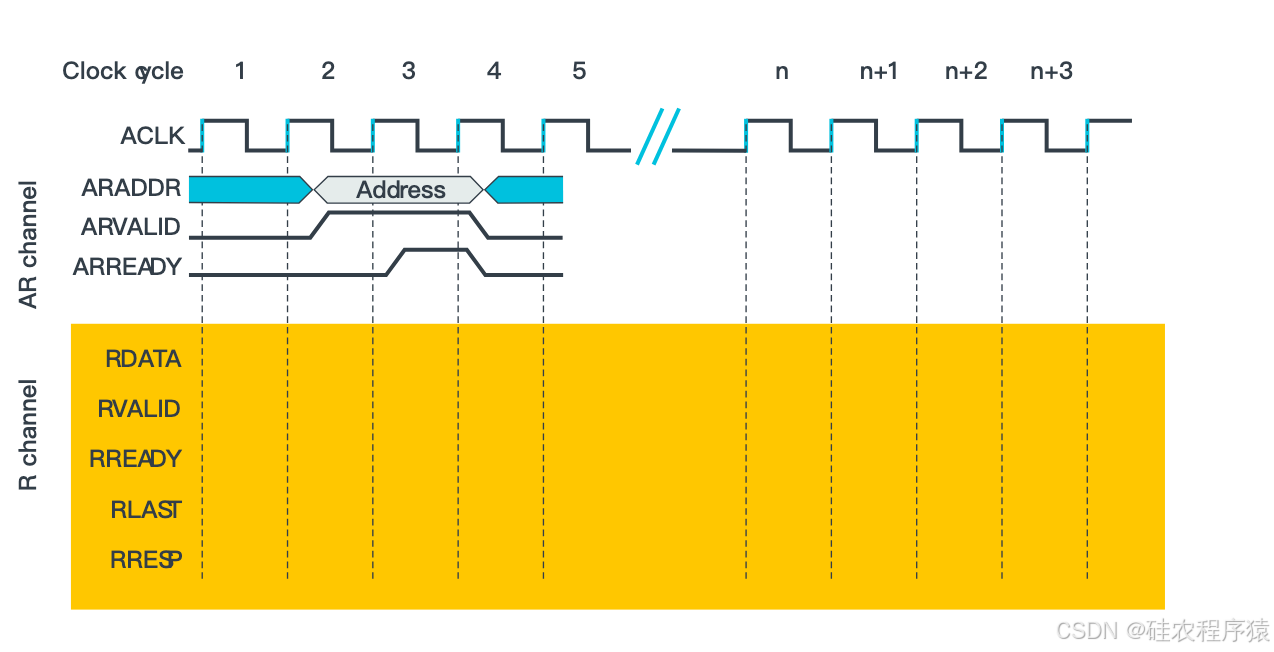

5、读传输

(1)读单个数据

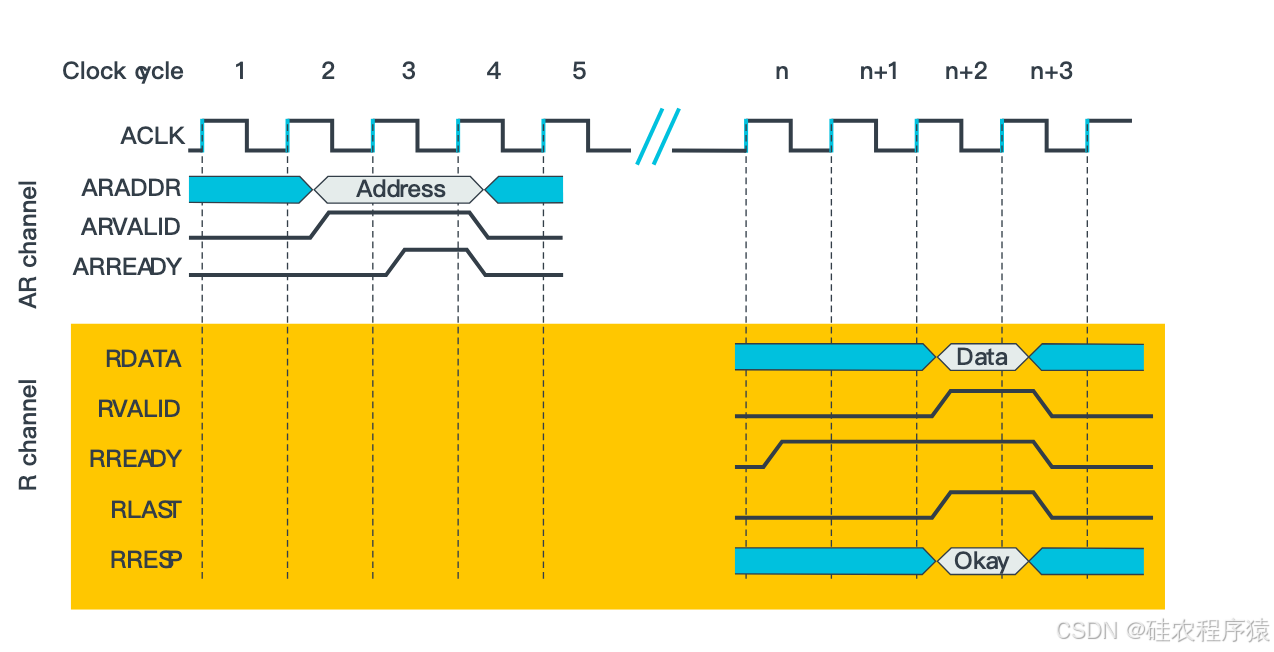

读传输涉及以下通道: 读取地址 (AR) 和读数据(R) 。首先,在 Read Address (AR) 通道上进行握手,如下图所示:

握手时序如下:

1、在T2 时刻,manager 将读取的地址传达给 ARADDR 上的slave并置位 ARVALID。

2、在T3 时刻,slave置位 ARREADY 以指示它已准备好接收地址值。 握手在T4 的上升沿完成。

接下来,在 Read (R) 通道上,从属设备将数据传输到主机。下图显示了数据传输过程:

数据传输握手时序如下:

1、在Tn 中,manager 通过置位 RREADY 来指示它正在等待接收数据。

2、slave检索数据并将其在Tn+2 中放置在 RDATA 上。

在这种情况下,因为这是一个 single data transaction,所以从机还将 RLAST 信号设置为高电平。同时,使用 RRESP 向 manager 指示读事务的成功或失败,并断言 RVALID。 因为 RREADY 已经由 manager 断言,所以握手在Tn+3 的上升沿完成。

(2)读多个数据项

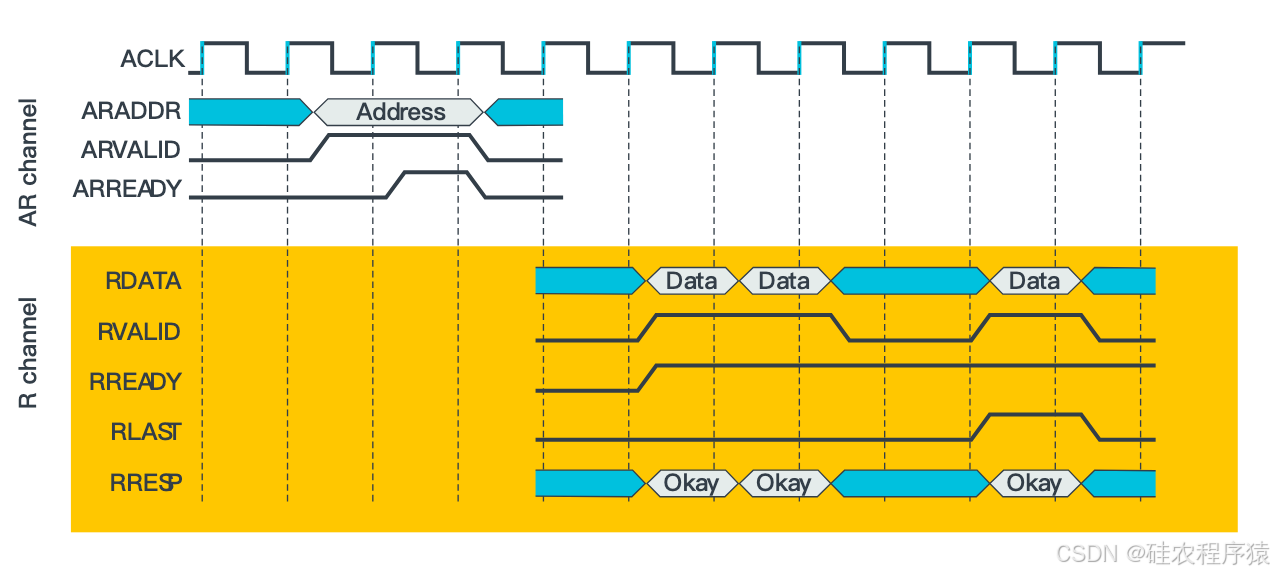

AXI 协议还允许在同一transaction中进行多个数据的burst读取。

下图显示了突发读取传输的示例:

在 AR 通道上传输单个地址,以传输多个数据项以及相关的burst宽度和长度信息。AR 通道表示 3 次传输的序列,因此在 R 通道上,我们看到从salve到 manager 的 3 次数据传输。 在 R 通道上,从属机构将数据传输到 manager。在此示例中,主机正在等待 RREADY 设置为 high 所显示的数据。从属设备驱动有效的 RDATA 并为每个传输断言 RVALID。

读取事务和写入事务之间的一个区别是,对于读取事务,事务中的每次传输都有一个 RRESP 响应。这是因为,在 write transaction 中,subordinate 必须在 B channel 上将响应作为单独的 transfer 发送。在读取事务中,从属设备使用相同的通道将数据发送回主机并指示读取作的状态。 如果事务中的任何转账指示错误,则仍必须完成事务的完整指示长度。没有早期突发终止这样的东西。

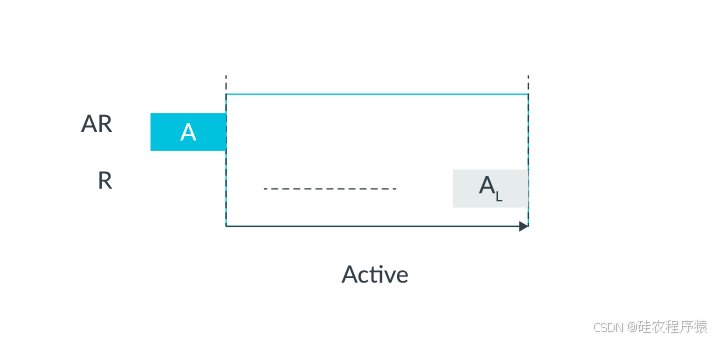

6、Active 传输

Active 传输也称为未完成事务。 Active Read Transaction 是指已传输 Read address,但该没有收到最后一笔读数据的 Transaction。 对于读操作,数据必须位于地址之后,因此transaction何时开始有一个简单的参考点。

如下图所示:

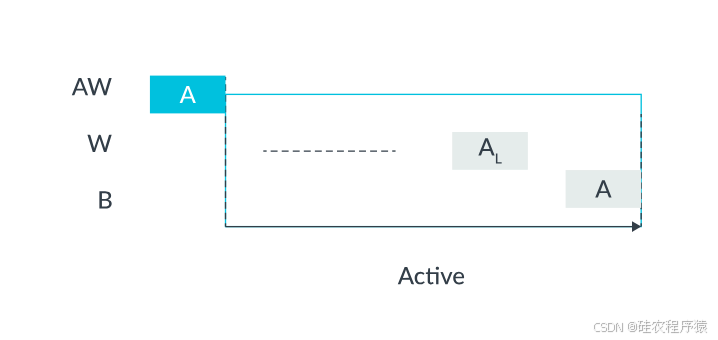

对于写传输,数据可以在地址之后,但也允许在地址前写入数据。因此,active 写传输是已传输写地址或写入数据但尚未收到写响应的transaction。

下图显示了active 写传输,其中写地址已传输,但没有收到写响应:

下图显示了已经有写数据,但没有收到写响应:

四、通道信号

本节介绍主要的 AXI 信号和属性,并说明如何使用它们来提高系统性能。

AXI 协议定义了五个通道:3个用于写传输,2个用于读传输。

(1)写通道信号

用于写传输的通道:写地址、写数据、写响应

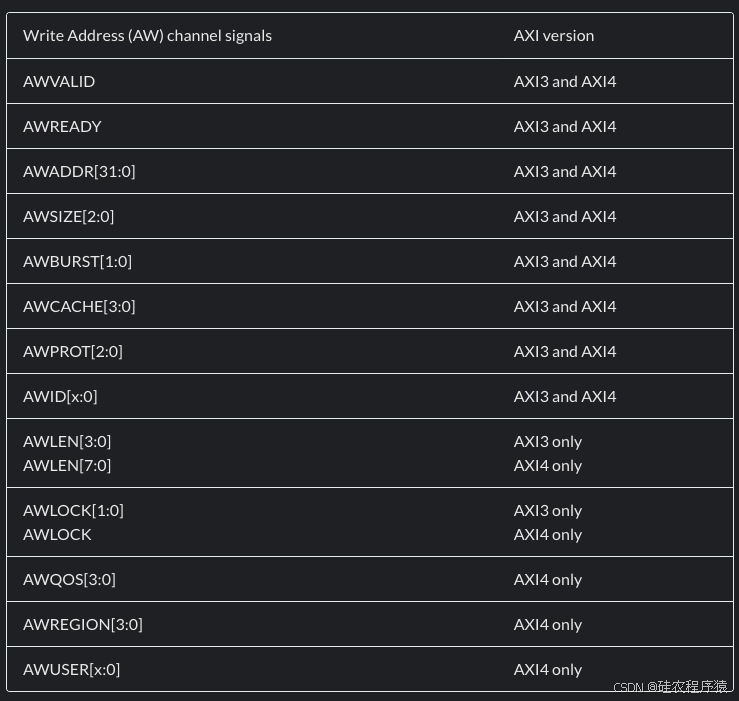

下表显示了 Write Address 通道信号:

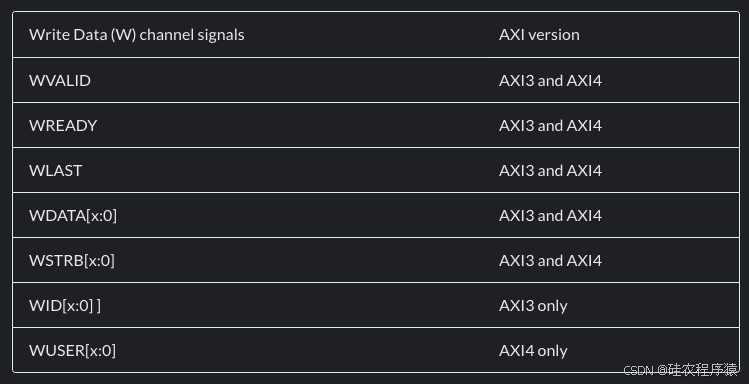

下表显示了 Write Data 通道信号:

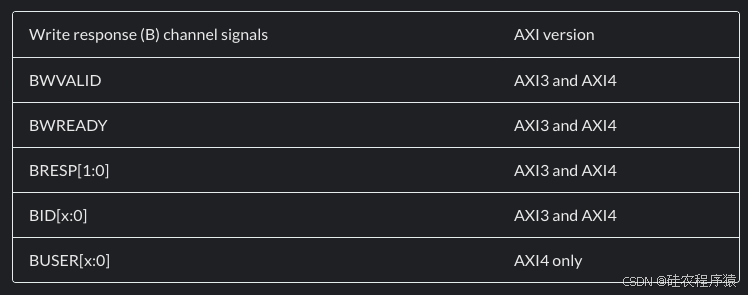

下表显示了 Write Response 通道信号:

每个通道中的所有信号都有相同的前缀:

AW 用于 Write Address 通道、W 代表 Write Data 通道、B 代表 Write Response 通道

AXI3 协议和 AXI4 协议在写通道的差异

- 对于写入地址通道,AXI4 协议的 AWLEN 信号更宽。因此,AXI4 能够产生比 AXI3 更长的突发

- AXI4 将 AWLOCK 信号减少到单个位,以仅容纳独占传输,因为不支持锁定传输

- AXI4 将 AWQOS 信号添加到 AW 通道。此信号支持 AXI4 协议中的服务质量 (QoS) 概念

- AXI4 将 AWREGION 信号添加到 AW 通道。该 signal 允许来自单个物理slave接口的多个逻辑接口

- AXI4 从 W 通道中删除 WID 信号,因此不支持写交织

- AXI4 将新增用户定义的信号XUSER

(2)读通道信号

用于 read transaction 的通道是:读取地址、读取数据

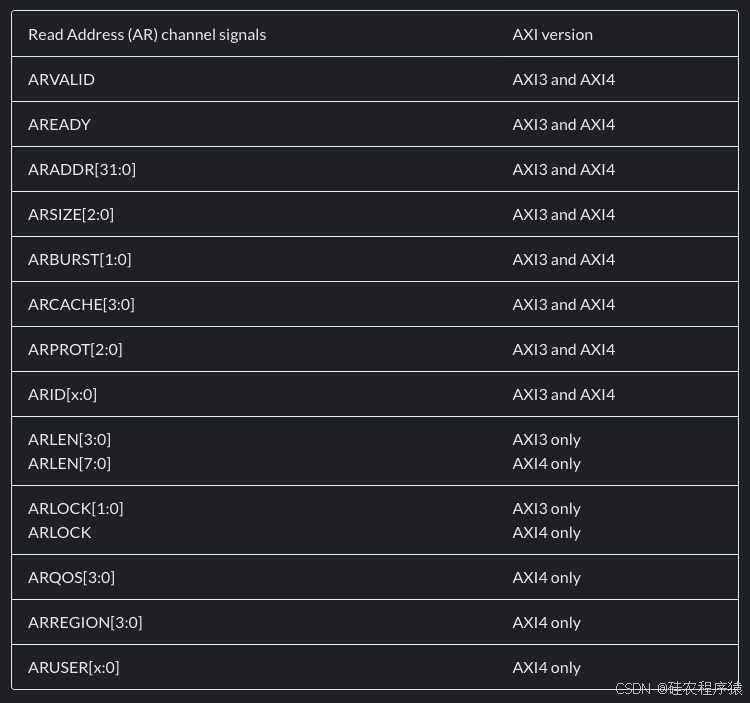

下表显示了 Read Address 通道信号:

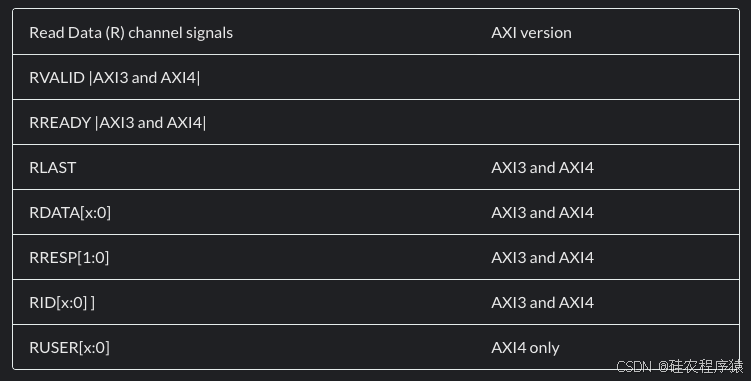

下表显示了 Read Data 通道信号

每个通道中的所有信号都有相同的前缀:

Read Address 通道的 AR、R 代表 Read Data 通道

AXI3 协议和 AXI4 协议在读通道的差异

- 对于 AXI4 协议,读取地址长度信号 ARLEN 更宽。因此,AXI4 能够生成比 AXI3 更长的读取突发

- AXI4 将 ARLOCK 信号减少到单个位,以仅容纳独占传输,因为不支持锁定传输

- 与写入通道信号一样,服务质量和从属区域的概念也适用于读取事务。这些信号使用 AR 通道中的 ARQOS 和 ARREGION 信号

- AXI4 新增用户定义的信号XUSER

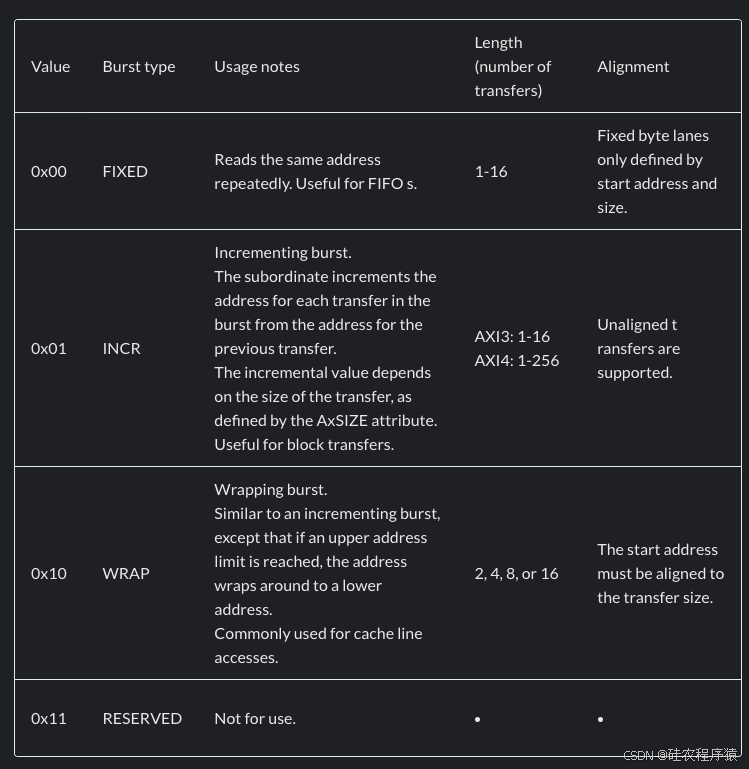

(3)数据大小、长度和突发类型

每个读操作和写操作都有指定该传输的数据长度、大小和突增信号属性的属性。 在下面的属性列表中, x 代表 write 和 read,因此它们同时适用于 Write Address 通道和 Read Address 通道:

AxLEN 描述突发传输的长度。 对于 AXI3,AxLEN[3:0] 有 4 位,最多支持16 次burst传输; 对于 AXI4,AxLEN[7:0] 有 8 位,最多支持256 次burst传输。

AxSize[2:0] 描述每次数据传输中要传输的最大字节数。三位编码表示每次传输 1、2、4、8、16、32、64 或 128 字节。

AxBURST[1:0] 描述事务的突发类型:固定、递增或卷绕传输。

下表显示了这些突发类型的不同属性:

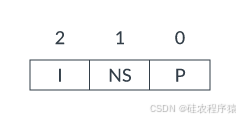

(4)访问权限信号

AWPROT 和 ARPROT支持保护级别,可以防止系统下游的非法传输。例如,如果事务没有正确的保护级别,则内存控制器可以使用这些信号拒绝读取或写入访问。 这对于 Arm TrustZone 等安全解决方案非常有用,处理器有两种不同的状态:Secure 和 Non-secure。

AxPROT 定义了三个级别的访问保护,如下图所示:

AxPROT 位分配指定以下属性:

AxPROT[0] (P) 将访问标识为无特权或特权: 1 表示特权访问。 0 表示无特权访问。 尽管某些处理器支持多级权限,但 AXI 可以提供的唯一区别是特权和非特权访问。

AxPROT[1] (NS) 将访问标识为安全或不安全: 1 表示 Non-secure transaction。 0 表示安全事务。

AxPROT[2] (I) 指示交易是指令访问还是数据访问: 1 表示指令访问。 0 表示数据访问。

AXI 协议将此指示定义为提示。它并非在所有情况下都准确,例如,当事务包含指令项和数据项的混合时。AXI 3 和 AXI4 都建议主机将bit 2 设为0以指示数据访问,除非该访问被明确知道为指令访问。

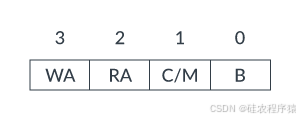

(5)缓存支持

访问权限信号

现代 SoC 系统通常包含放置在系统多个点的缓存。例如,2 级缓存可能位于处理器外部,或者 3 级缓存可能位于内存控制器前面。 为了支持使用不同缓存策略的系统,AWCACHE 和 ARCACHE 信号指示事务在系统中如何进行。

下图显示了 AxCACHE 位分配:

AxCACHE 位分配指定以下属性:

AxCACHE [0] (B) 是可缓冲位。当该位设置为 1 时,互连或任何组件可以将事务延迟任意数量的周期到达其最终目的地。可缓冲位指示响应是否可以来自中间点,或者响应是否必须来自目标从属设备。

AxCACHE [1] 是 AXI3 中的可高速缓存位,或 AXI4 中的可修改位。此位表示最终目的地的事务属性不必与原始事务的属性匹配。对于写入,设置可修改位意味着可以合并多个不同的写入,或者可以将单个写入分解为多个事务。对于读取,设置可修改位意味着可以预取位置的内容,或者单个获取的值可用于多个读取事务。

AxCACHE [2] 是 RA 位。RA 位表示在读取时,建议分配事务,但不是必需的。

AxCACHE [3] 是 WA 位。WA 位表示在写入时,建议分配事务,但不是必需的。

如果断言了 AxCACHE [2] 或 AxCACHE [3],则必须在缓存中查找事务,因为它可能已由另一个主机在此缓存中分配。

注意

如果未断言可缓存位 AxCACHE [1],则无法断言 AxCACHE [2] 和 AxCACHE [3]。

在读取和写入地址总线上都包含 read 和 write allocation 的原因是它允许系统级缓存优化其性能。 例如,假设一个缓存看到定义为“write-allocate, but not read-allocate”的读取访问权限。在这种情况下,缓存知道地址可能存储在缓存中,因为它可能已在上一次写入时分配,因此它必须执行缓存查找。 但是,现在考虑一下缓存看到定义为“no write-allocate and no read-allocate”的读取访问。在这种情况下,缓存知道地址尚未在缓存中分配。

缓存可以避免查找并立即将事务传递给另一端。只有当缓存知道每个事务的读取和写入分配时,它才能执行此作。 缓存以这种方式运行并不是必需的,但 AXI 协议是使用 RA 和 WA 定义的,用于读取和写入,如果您或您的缓存设计人员想要实现这种作模式,则允许这种作模式。

(6)响应信号

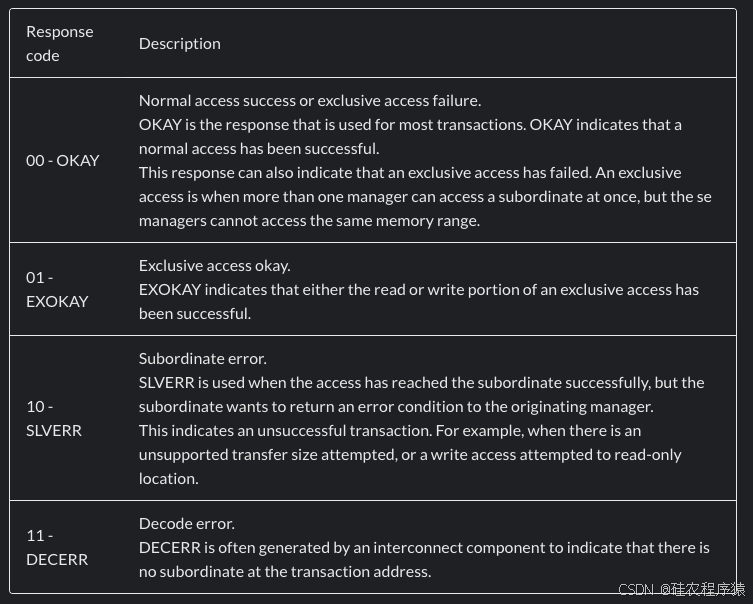

AXI 为读取和写传输提供响应信号。 对于读传输,来自 subordinate 的响应信息使用 RRESP 在读取数据通道上发出信号。 对于写传输,响应信息使用 BRESP 在写入响应通道上发出信号。 RRESP 和 BRESP 都由两个 bit 组成,这些信号的编码可以传输四个响应,如下表所示:

(7)写数据选通

主机使用写入数据选通信号来告诉下属需要数据总线的哪些字节。写入数据选通对于缓存访问非常有用,以便有效地移动稀疏数据数组。除了使用写入数据选通之外,还可以使用未对齐的起始地址优化数据传输。

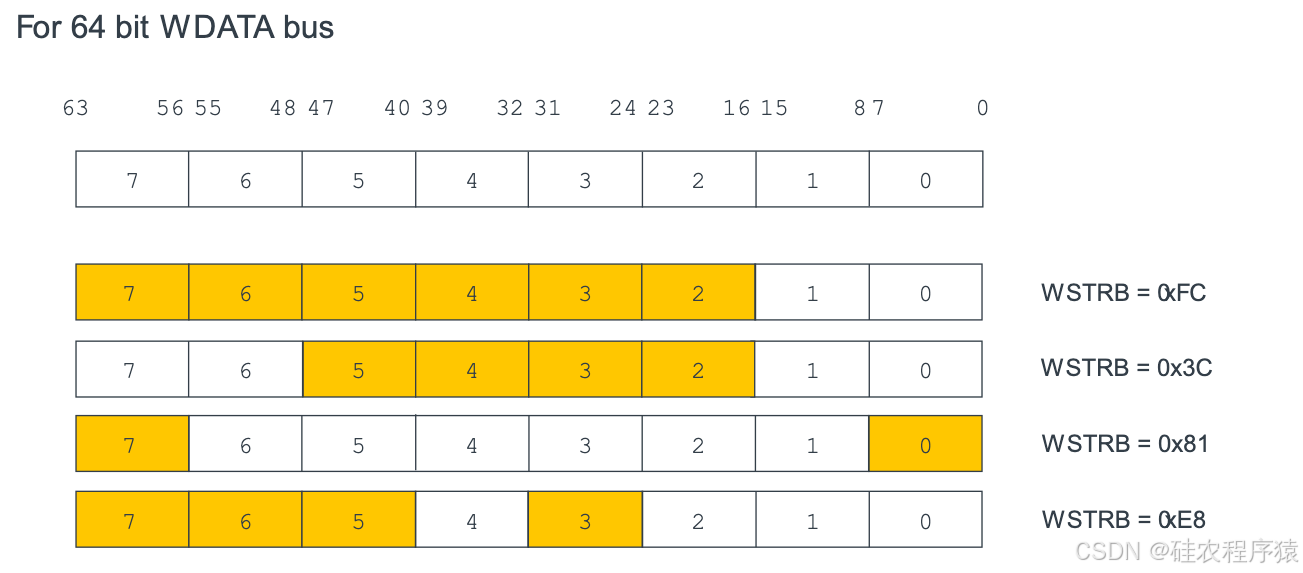

写通道在数据总线上每个字节有一个选通位。这些位发出 WSTRB 信号。 主机必须确保仅对于包含有效数据的字节通道,write strobes 设置为 1。 例如,考虑 64 位写入数据总线。WSTRB 信号有 8 位,每个字节 1 位。

下图显示了示例 WSTRB 值如何指定哪些字节通道有效:

看第一个示例,假设有效数据仅在数据总线的前 6 个有效字节中,从字节 7 到字节 2。这意味着 Manager 必须使用十六进制值 0xFC 来控制 WSTRB 信号。 同样,其余示例指定有效的数据总线字节通道,如下所示:

- 仅在数据总线的字节 2、3、4 和 5 中有效数据需要 WSTRB 信号值 0x3C。

- 仅在数据总线的字节 0 和 7 中有效数据要求 WSTRB 信号值为 0x81。

- 仅在数据总线的字节 3、5、6 和 7 中的有效数据需要 0xE8 的 WSTRB 信号值。

字节通道选通提供稀疏数据阵列的高效移动。使用此方法,可以通过将剩余的传输字节通道选通设置为 0 来提前终止写入事务,尽管剩余的传输仍必须完成。WSTRB 信号还可以在transfer之间发生变化。

读通道没有等效信号。这是因为 manager 指示所需的传输,并且可以屏蔽从从属设备接收的任何不需要的字节。

(8)原子访问

AxLOCK 信号用于指示何时执行原子访问。

AXI 协议提供两种机制来支持原子性:

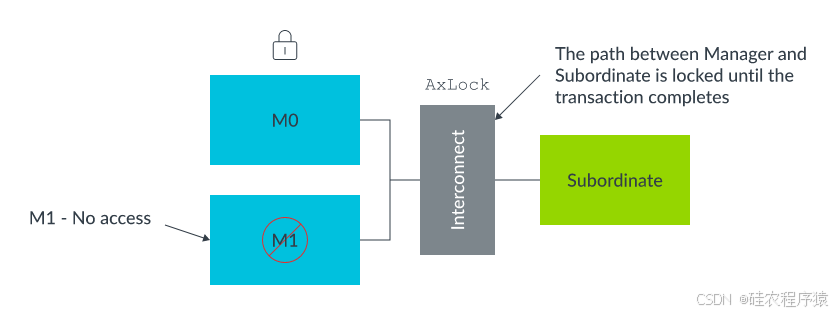

1、锁定访问: 锁定的传输将锁定通道,该通道将保持锁定状态,直到生成解锁的传输。锁定访问类似于 AHB 协议支持的机制。当 manager 使用事务的 AxLOCK 信号来显示它是锁定的事务时,互连必须确保只有该 manager 才能访问目标从属区域,直到来自同一 manager 的解锁事务完成。互连模块中的仲裁程序必须强制实施此限制。由于锁定访问需要互连来防止在锁定序列进行时发生任何其他事务,因此它们可能会对互连性能产生重要影响。锁定的事务只应用于旧设备。只有 AXI3 支持锁定访问,AXI4 不支持锁定访问。

2、独占访问:独占访问比锁定事务更有效,并且它们允许多个主机同时访问一个slave。独占访问机制允许实现 semaphore-type作,而无需 bus 在作期间保持对特定 manager 的锁定。由于锁定访问的效率不如独占访问,并且大多数组件不需要锁定事务,因此它们已从 AXI4 协议中删除。

在 AXI3 中,AxLOCK 信号由两个位组成,其值如下:

0b00 - 正常

0b01 - 独占

0b10 - 已锁定

0b11 - 保留

在 AXI4 中,AxLOCK 信号由一位组成,其值如下:

0b0 - 正常

0b1 - 独占

(9)服务质量

AXI4 协议引入了额外的信号来支持服务质量 (QoS)。 Quality of service 允许您对事务进行优先级排序,从而通过确保以更高的优先级处理更重要的事务来提高系统性能。

服务质量信号有两种:

AWQOS 在每个写入事务的 Write Address 通道上发送。

ARQOS 在每个读取事务的 Read Address 通道上发送。

两个信号都是 4 位宽,其中值 0x0 表示最低优先级,值 0xF 表示最高优先级。 服务质量的默认系统级实现是,任何选择多个事务的组件首先处理具有较高 QoS 值的事务。

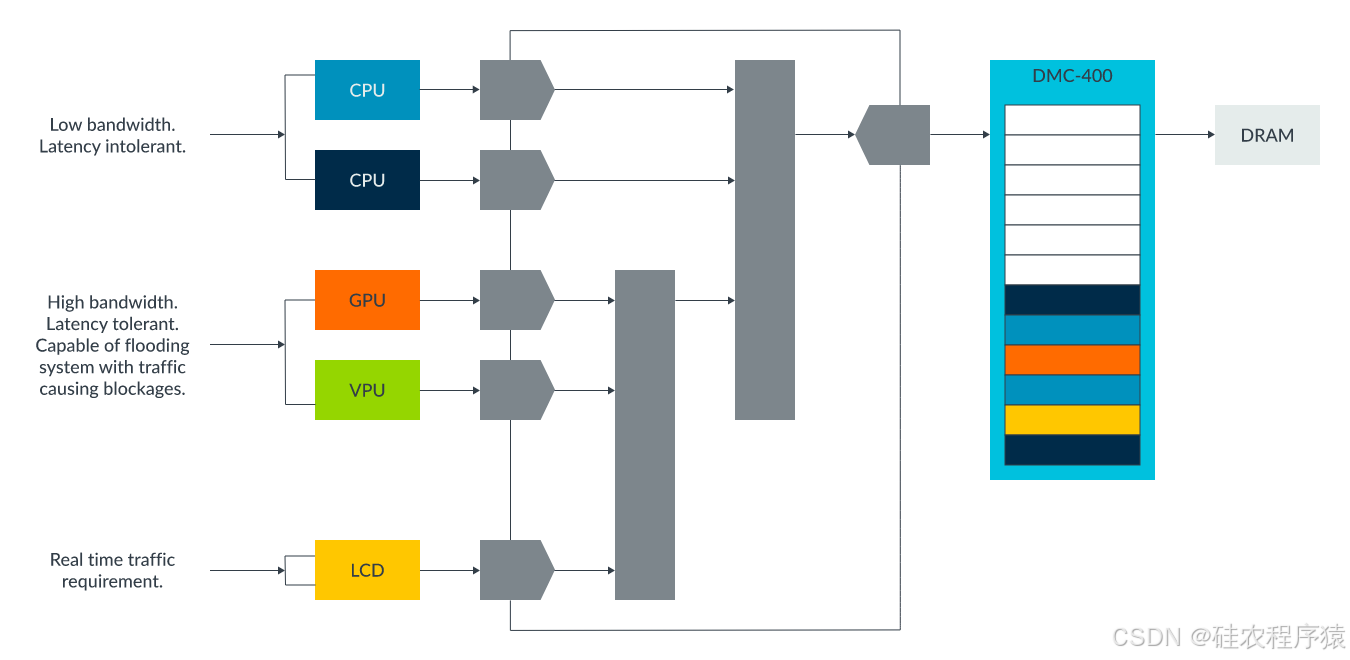

下图显示了一个带有直接内存控制器 (DMC) 的示例系统,特别是 DMC-400。此控制器管理到 DRAM 的事务:

在实践中,某些元素(如 CPU)需要的内存访问比其他组件(如 GPU 或 VPU)的内存访问重要得多。 当为事务分配适当的 QoS 值时,互连可以在较低优先级的事务之前仲裁较高优先级的事务,并且 DMC 会重新排序事务以确保提供正确的优先级。

(10)区域信令

区域信号是 AXI4 中的可选功能。 使用区域标识符时,这意味着从属设备上的单个物理接口可以提供多个逻辑接口。每个逻辑接口在系统地址映射中可以具有不同的位置。 从属设备不必支持不同逻辑接口之间的地址解码。

区域信号使用两个 4 位区域标识符,即 AWREGION 和 ARREGION。这些区域标识符可以标识多达 16 个不同的区域。

(11)用户信号

AXI4 接口信号集可以选择包含一组用户定义的信号,称为 User 信号。 每个通道都可以使用用户信号,在主机和从属组件之间传输额外的自定义控制信息。这些信号是可选的,不必在所有通道上都受支持。如果使用它们,则 User 信号的宽度由实施定义,并且每个通道上的宽度可能不同。 注意 由于 AXI 协议未定义这些用户信号的功能,因此如果两个组件以不兼容的方式使用相同的用户信号,则可能会出现互作性问题。

(12)AXI 通道依赖关系

AXI 协议定义不同通道之间的依赖关系。 三个主要依赖项如下所示:

WLAST 传输必须在断言 BVALID 之前完成。 Manager 必须先发送所有写入数据,然后 Manager 才能看到写入响应。此依赖关系在 AXI3 中不存在,但针对 AXI4 引入: 在 AXI3 中,在发送写入响应之前不必看到地址。 在 AXI4 中,在主机可以看到写入响应之前,必须传输所有数据和地址。

在传输 ARADDR 之前,无法断言 RVALID。 如果 subslave 不先看到地址,则无法传输任何读取数据。这是因为如果下属不知道将从中读取数据的地址,则无法将数据发送回主机。

WVALID 可以在 AWVALID 之前断言。 在传达下属应写入这些数据的地址之前,主机可以使用 Write Data 通道将数据发送给下属。

五、原子访问

原子访问是对内存区域的一系列访问。当 manager 想要对特定内存区域执行一系列访问时,他们会使用原子访问,同时确保该区域中的原始数据不会被其他 manager 的写入破坏。此序列通常是 read、modify 和 write 序列。

原子访问有两种类型:

锁定 当 manager 执行具有 locked access 的事务序列时,任何其他 manager 对同一下属的访问都将被拒绝。

独占 当一个主机成功地执行具有独占访问的事务序列时,其他主机可以访问从属节点,但不能访问正在访问的内存区域。

1、锁定访问

AXI4 不支持锁定的事务,但 AXI3 实现支持锁定的事务。 在主机可以启动锁定传输之前,必须确保没有其他事务等待完成。 锁定的传输序列会强制互连拒绝任何其他主机对从机的访问。

由于锁定访问需要互连来防止在锁定序列进行时发生任何其他事务,因此它们对互连性能有重要影响。

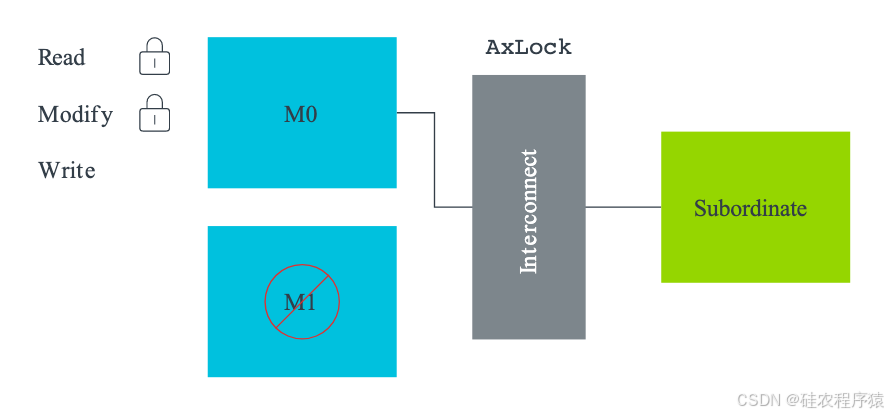

下图显示了 AXI 锁定访问作,并带有一个使用两个主机M0 和 M1 的示例:

当 M0 对事务使用锁定信号来指示它是锁定事务时,互连使用仲裁程序来确保只有 M0 可以访问从机。互连会阻止M1 对从机的访问,直到M0 完成的解锁。

下图显示了锁定访问如何与一系列事务配合使用:

此示例中的步骤如下:

1、主机 M0 启动 READ、MODIFY 和 WRITE 访问序列

2、第一个事务 READ 断言 LOCK 信号,指示它启动了一个锁定的事务

3、互连模块会锁定其他访问。这时,M1 无权访问下属

序列中的最后一个传输 WRITE 拉低 LOCK 信号,指示锁定序列的结束。互连将删除锁定,其他主机现在可以访问从机。

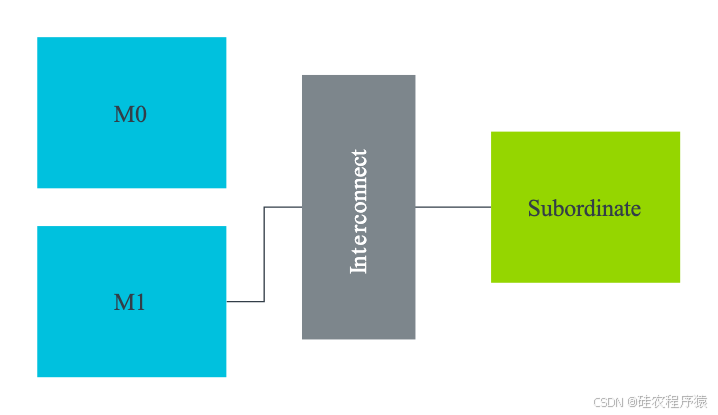

2、独占访问权限

使用独占访问比锁定访问更有效地执行原子操作。这是因为独占访问更有效地使用互连带宽。 在独占访问序列中,其他 manager 可以同时访问从属 manager,但只有一个 manager 被授予对同一内存范围的访问权限。

独占访问可以由多个数据传输组成,但所有传输必须具有相同的地址通道属性。

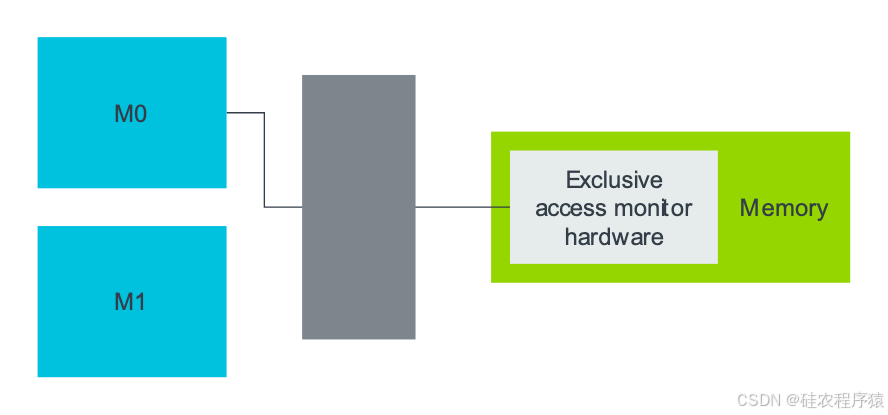

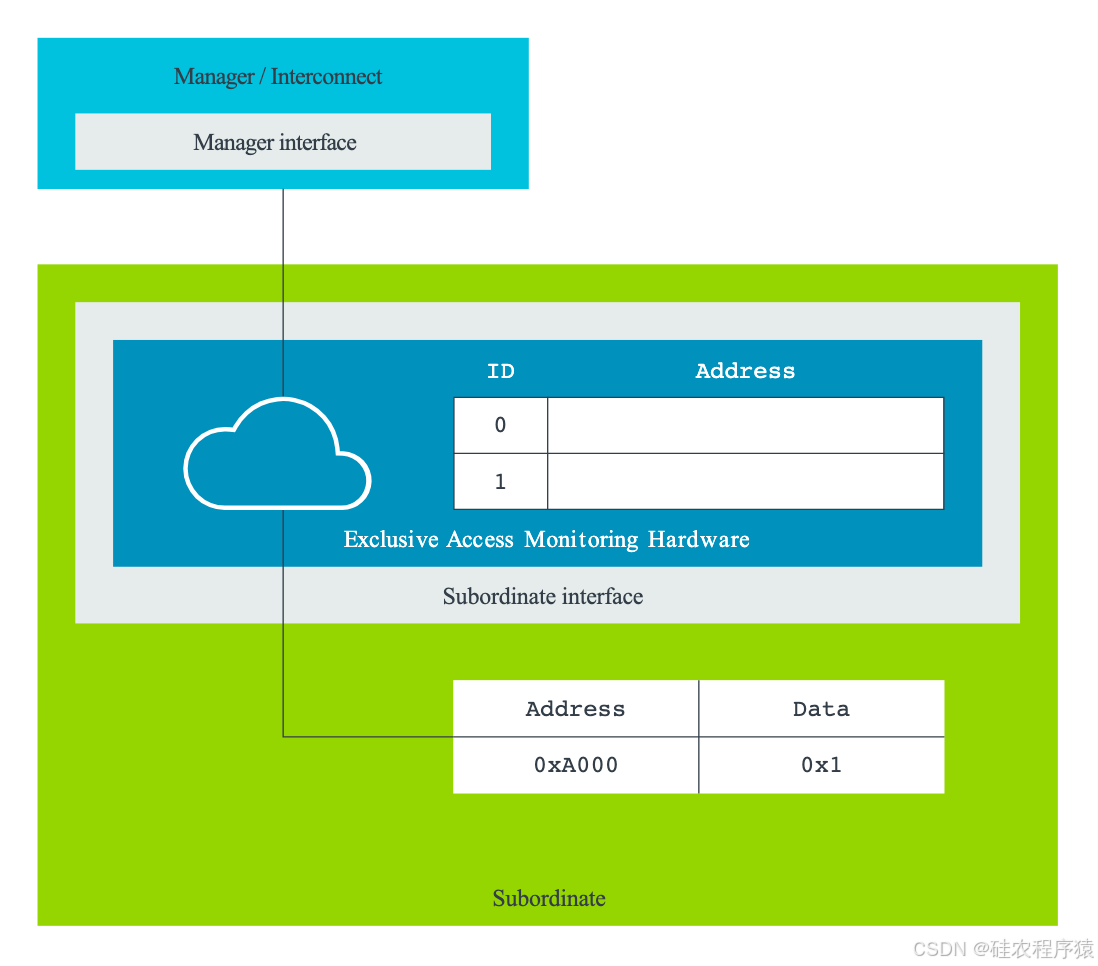

从机需要硬件独占访问监视器来记录独占序列的传输信息,以便它知道正在访问的内存范围和执行访问的主机的身份。 如果在独占序列完成之前没有其他 manager 访问监控范围,则该访问是原子的。 从属设备对其他主机的访问开放,提高了系统带宽利用率的整体公平性。

独占访问的基本机制由独占访问监视器控制实现的,下图显示了主机 M0 从地址执行独占读取的示例:

来自独占访问监控器硬件的响应是以下之一:

EXOKAY:该值被读取,事务的 ID 存储在独占访问监视器硬件中。

OKAY:该值已读取,但不支持独占访问,主机应将此响应视为独占作的错误。 在稍后的某个时间,如果在独占读取期间收到 EXOKAY,则 M0 会尝试通过对同一地址执行独占写入来完成独占序列。

独占写访问与独占读访问使用相同的事务 ID。 来自独占访问监控器硬件的响应是以下之一:

EXOKAY: 自独占读取访问权限以来,没有其他 Manager 写入该位置,因此写入成功。在这种情况下,独占写入会更新内存。

OKAY: 另一个主机(例如 M1)在独占读取访问权限后已写入该位置,因此写入失败。在这种情况下,内存位置不会更新。 一些 subordies 需要额外的 logic 来支持独占访问。独占访问监控硬件仅监控每个交易 ID 的一个地址,以便可以监控每个可能的独占 ID。

3、专属交易:均通

本节介绍两个成功的独占访问序列的示例,这两个序列都通过了。

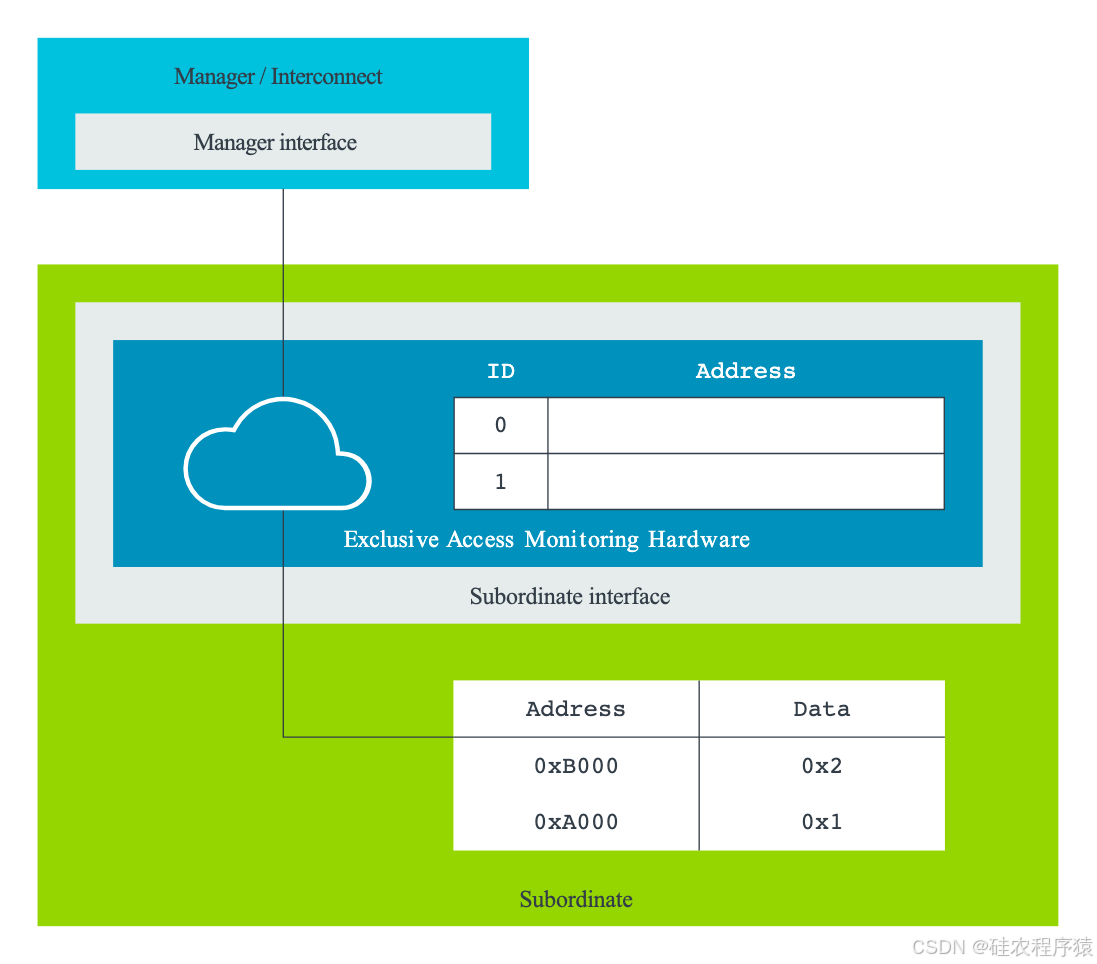

下图显示了一个系统,其中包含一个主机及其 AXI 主机界面和一个从属设备:

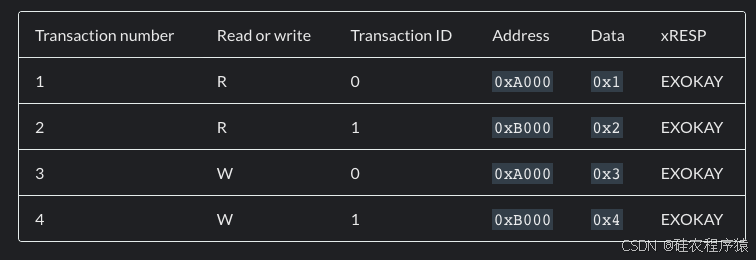

从属接口包括独占访问监控硬件,可以保存每个交易访问的 ID 和地址。 下表描述了示例序列中的不同交易。

表中的所有传输都是独占访问: 上表所示的事务序列按如下方式进行:

首先, manager从地址 0xA000 执行 ID 为 0 的 read exclusive 事务。独占访问监控硬件将此事务的 ID 和地址保存在其表中,从属设备使用读取的数据 0x1 进行响应。由于此从属设备正确支持独占访问,因此独占访问监视硬件以 EXOKAY 响应进行响应。

接下来,主机从地址 0xB000 执行 ID 为 1 的读独占交易。同样,独占访问监控硬件将这个新事务的详细信息保存在表中,而从属设备使用读取的数据 0x2 进行响应。

由于此从属设备正确支持独占访问,因此独占访问监视硬件再次以 EXOKAY 响应进行响应。此时,有两个单独的独占序列正在进行中。 主机完成其作后,它会执行 ID 为 0 的 write exclusive 事务,以地址 0xA000。

独占访问监控硬件检查表中此事务的详细信息,并且由于 ID 为 0 且地址为 0xA000 的现有记录,因此使用 EXOKAY 响应响应主机。这意味着没有其他 manager 访问过这个内存位置,并且从属使用它接收的新值更新它,在本例中为 0x3。独占访问监控硬件从其表中删除此事务的 ID 和地址,因为该地址位置的独占访问序列现已完成。

最后,主机执行一个 ID 为 1 的新 write exclusive 事务来寻址 0xB000。独占访问监控硬件在其表中检查此事务的详细信息。看到 ID 为 1 且地址为 0xB000 的现有记录,它会再次以 EXOKAY 响应响应经理。这意味着没有其他 manager 访问过这个内存位置,并且 subordinate 使用收到的新值更新它,在我们的示例中为 0x4。同样,独占访问监控硬件从其表中删除此事务的 ID 和地址,因为该地址位置的独占访问序列现已完成。

4、独占交易对:1 次通过,1 次失败

本节介绍两个独占访问序列的示例,其中第一个成功,第二个失败。

下图显示了一个系统,其中包含一个主机及其 AXI 主机界面和一个从属设备:

从属接口包括独占访问监控硬件,可以保存每个交易访问的 ID 和地址。 下表描述了示例序列中的不同交易。

表中的所有事务都是独占访问: 上表所示的事务序列按如下方式进行:

第一个事务是 manager 从地址 0xA000 执行 ID 为 0 的 read exclusive 事务。独占访问监控硬件将此事务的 ID 和地址保存在其表中,从属设备使用读取的数据 0x1 进行响应。由于此从属设备正确支持独占访问,因此独占访问监视硬件以 EXOKAY 响应进行响应。

稍后,主机从与第一个事务 0xA000 相同的地址执行 ID 为 1 的新独占事务。独占访问监控硬件将此新事务的详细信息保存在表中,从属数据库使用读取数据 0x1 进行响应。同样,由于此从属设备正确支持独占访问,因此独占访问监视硬件以 EXOKAY 响应进行响应。此时,有两个不同的正在进行的 exclusive sequence 到同一个内存位置。

主机完成其作后,它会执行 ID 为 0 的独占写入事务以寻址 0xA000。独占访问监控硬件在其表中检查此事务的详细信息,并看到 ID 为 0 且地址为 0xA000 的记录,并使用 EXOKAY 响应响应主机。这意味着没有其他 manager 更新了这个内存位置,并且从属可以使用收到的新值来更新它,在我们的示例中为 0x3。由于地址位置0xA000的内容已被修改,因此独占访问监控硬件会从其表中删除与该位置地址匹配的所有条目。

最后,主机再次执行 ID 为 1 的新 write exclusive 事务以寻址 0xA000。独占访问监控硬件在其表中检查此事务的详细信息。找不到地址0xA000的任何记录,它会以 OKAY 响应响应。OKAY 响应表示已在此内存位置执行了先前的写入作,该作更新了数据。

在这种情况下,从设备无法使用新值 0x4 更新内存位置。这种情况是独占访问失败。在这种情况下,主机必须重新启动完全独占访问序列,从独占读取开始,然后再次重启独占写入。 此示例演示了独占访问如何实现非阻塞行为。与 LOCK 访问相比,正是这种行为提供了更大的系统吞吐量。

六、传输行为和时序

介绍了一些传输的控制规则, 未对齐的传输,以及如何优化带宽利用率、 big-endian 和 little-endian 编码之间的区别,以及一些简单的示例 与 AXI 接口相关的主要参数。

1、简单传输示例

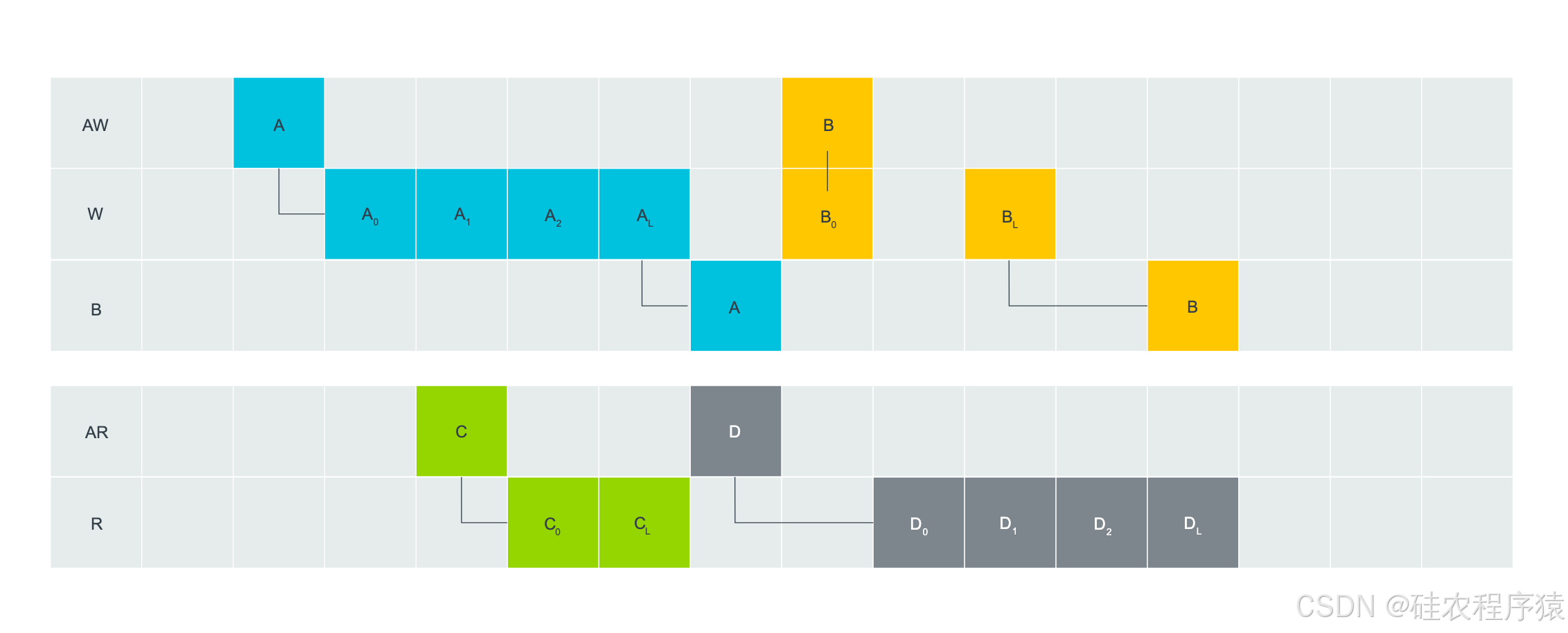

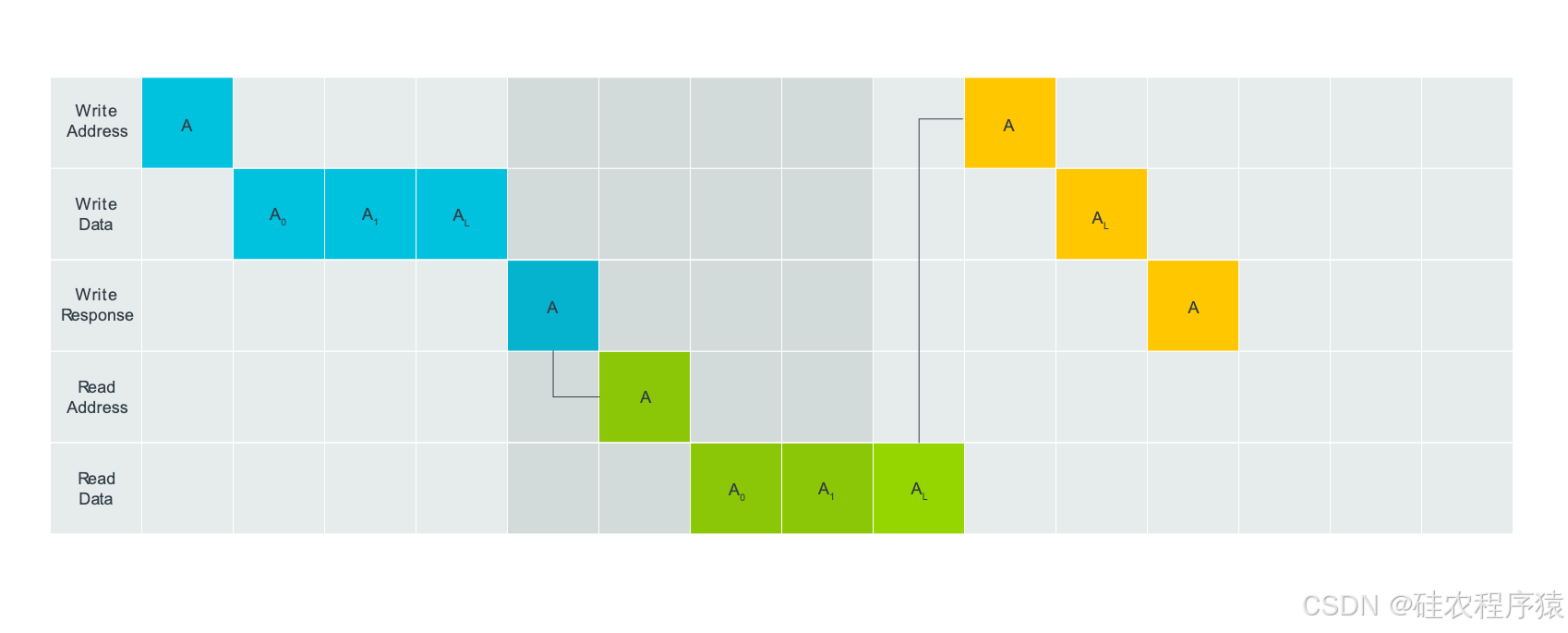

下图显示了 AXI3 或 AXI4 接口的 5 个通道上多个有效transaction的时间表示:

传输过程如下: 事务 A,这是一个包含四次传输的写操作。

主机首先将地址 A 放在 AW 通道上,然后将四次数据传输序列放在 W 通道上,以 AL 结尾,其中 L 代表最后一个。当4次数据传输都完成,从机在B通道上做出响应。

当传输A发生时,主机还使用读通道执行读事务 C,包含两个传输。

来自从机的响应与数据同时包含在 R 通道中。 一旦传输C完成,主机使用 Read Address 通道 AR 将新的读地址 D 发送给从机。这种情况下,从机的响应不是立即的,由 D 和 D0 之间的延迟表示。

最终,从机在 R 通道上以 D0 到 DL 的四次顺序传输作为响应。 最后,当读传输D正在进行时,主机使用 Write Address 通道将新地址 B 发送到从机进行写操作。主机将数据B0放在W通道上,同时将相应的地址B放在 AW 通道上。在此示例中,数据传输B0 和 BL之间存在延迟,响应 B 之前存在另一个延迟。当从机将响应发送给 manager 时,传输才会完成,这些示例都是有效的传输。

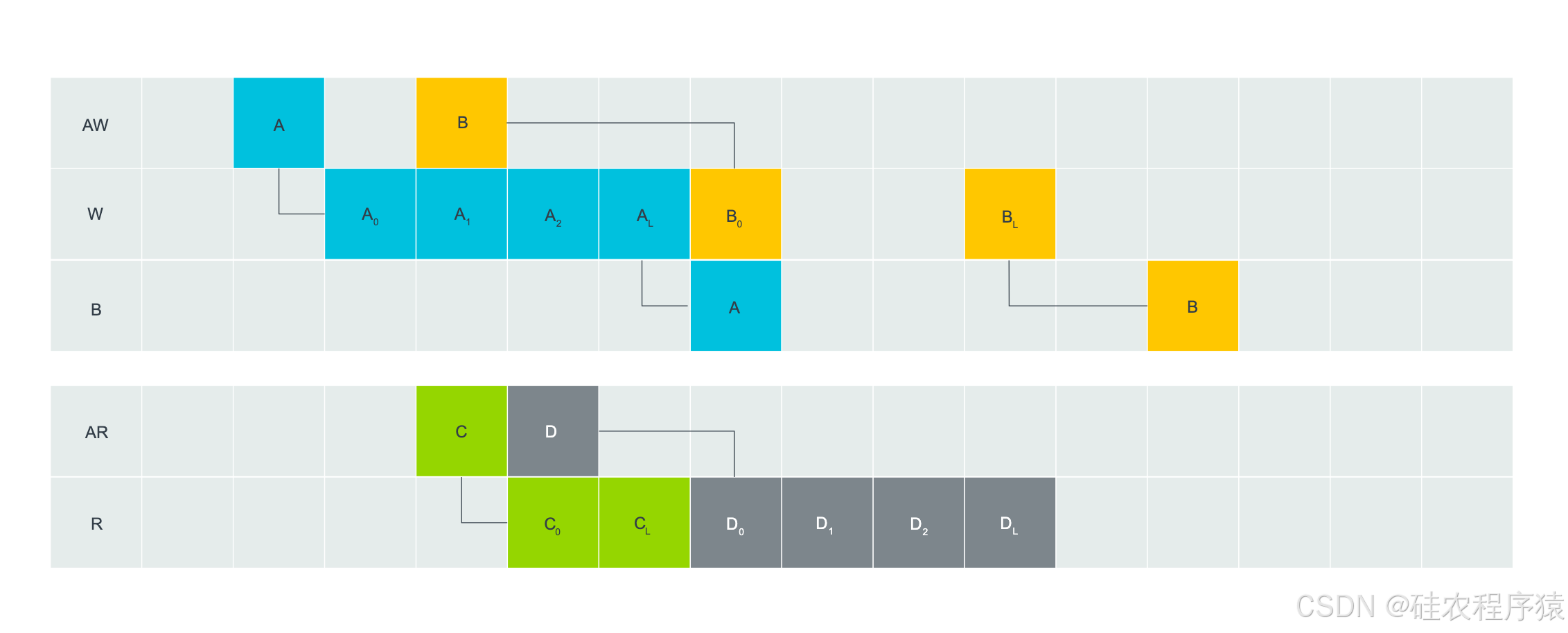

下图显示了在不同但仍然有效的时间线中进行的相同读取和写操作序列:

主机在完成事务A之前启动事务B。主机使用 Write Address 通道 发送新请求,方法是在 W 通道上完成传输A 的数据传输之前将新地址B发送给从机。 当事务 A 的所有数据都完成后,事务 B 的数据将传输到下属。主机在开始传输事务 B 的数据之前,不会等待事务 A 的 B 通道响应。 同时,主机使用 Read Address 通道依次传输从机的读地址C和D,从设备按顺序响应两个读取请求。

这个例子显示在不同通道上发生的读取和写入操作的不同有效组合,表明了 AXI 协议的灵活性以及优化互连性能的可能性。

2、传输ID 信号

AXI 协议用 ID信号实现乱序传输,使用 transfer ID 可以实现高性能互连,从而最大限度地提高数据吞吐量和系统效率。

根据 AXI 协议规范,必须对具有给定 ID 的所有传输进行排序。但是,对具有不同 ID 的交易的排序没有限制, 主机可以支持多个线程的多个 ID。 从机通常需要可配置的 ID 宽度。

ID 信号的两个参数:

写ID 位宽,用于 AWID、WID 和 BID 总线的位数 ;读ID 宽度,用于 ARID 和 RID 总线的位数。

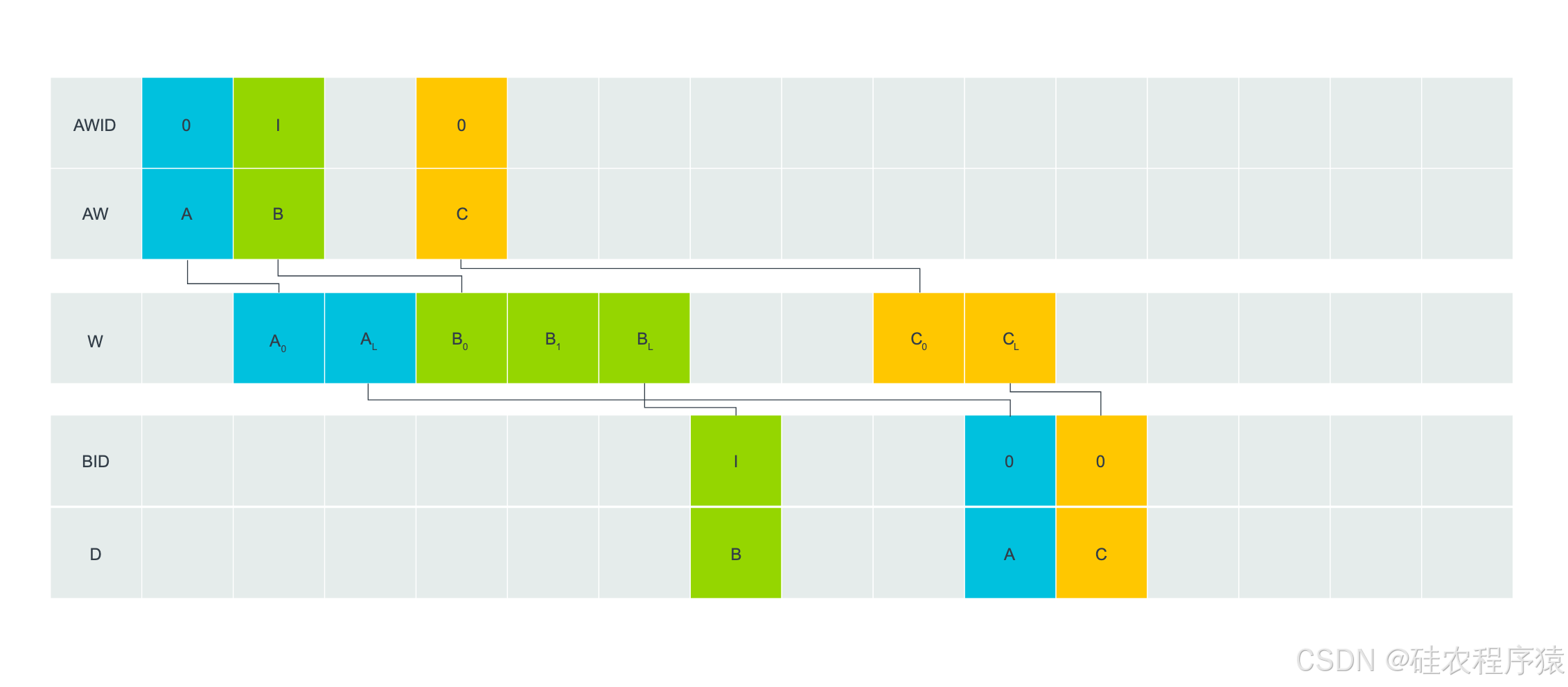

(1)写传输顺序

写传输有三个 AXI 排序规则, 规则如下: W 通道上的写数据必须与 AW 通道上的地址传输顺序相同,如下图所示:

在此例中,主机先发送地址 A,然后发布地址 B,因此数据必须以 A0 开头,然后再以 B0 开头。 注意 AXI3 允许在 W 通道上交错使用具有不同 ID 的写入数据(交织),但 AXI4 及更高版本不支持。如下图所示:

在此示例中,事务 B 在事务 A 之前完成,即使事务 A 先启动。 一个主机可以有多个具有相同 ID 的未完成事务,但必须按顺序完成。如下图所示:

在此例中,传输 B 的 ID 与其他不同,因此它可以随时完成。但是,A 和 C 具有相同的 ID,因此它们必须按照与发出的顺序相同的顺序完成。

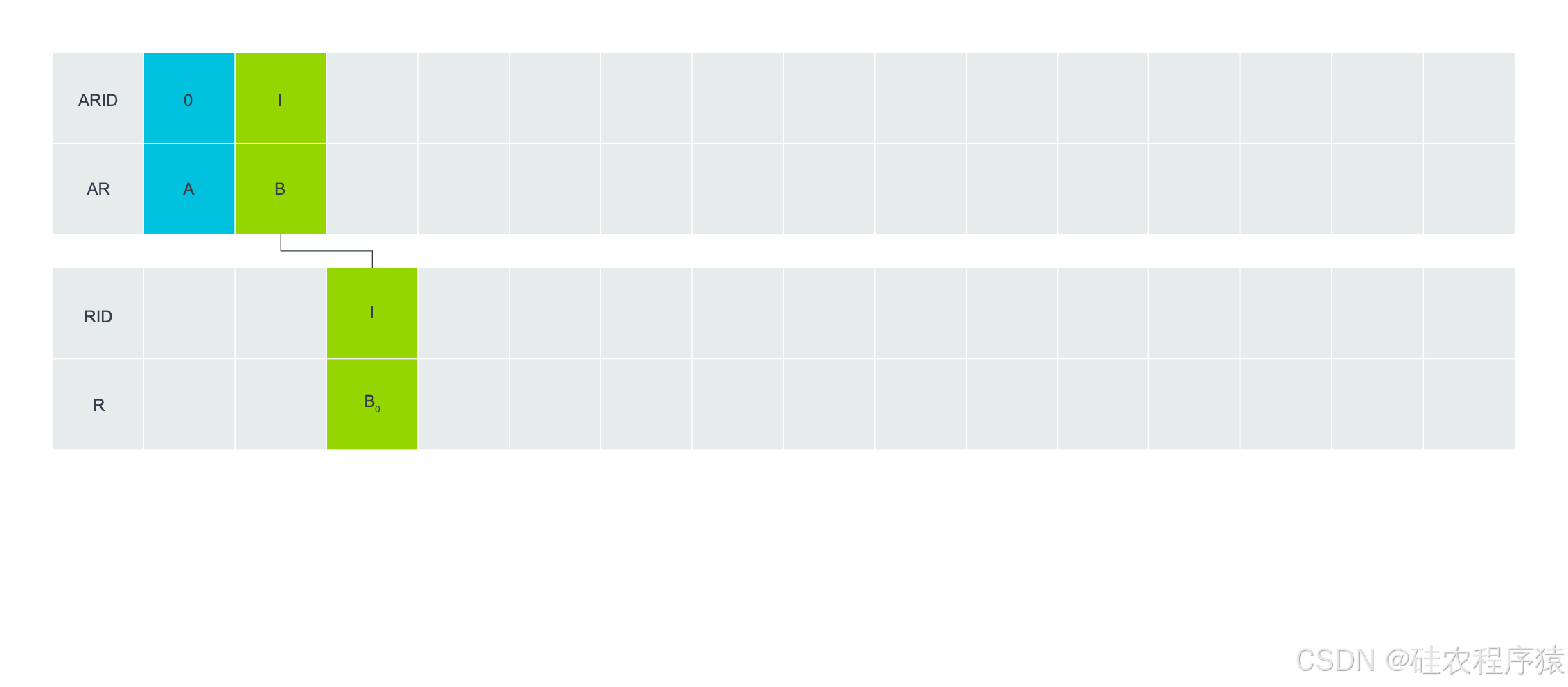

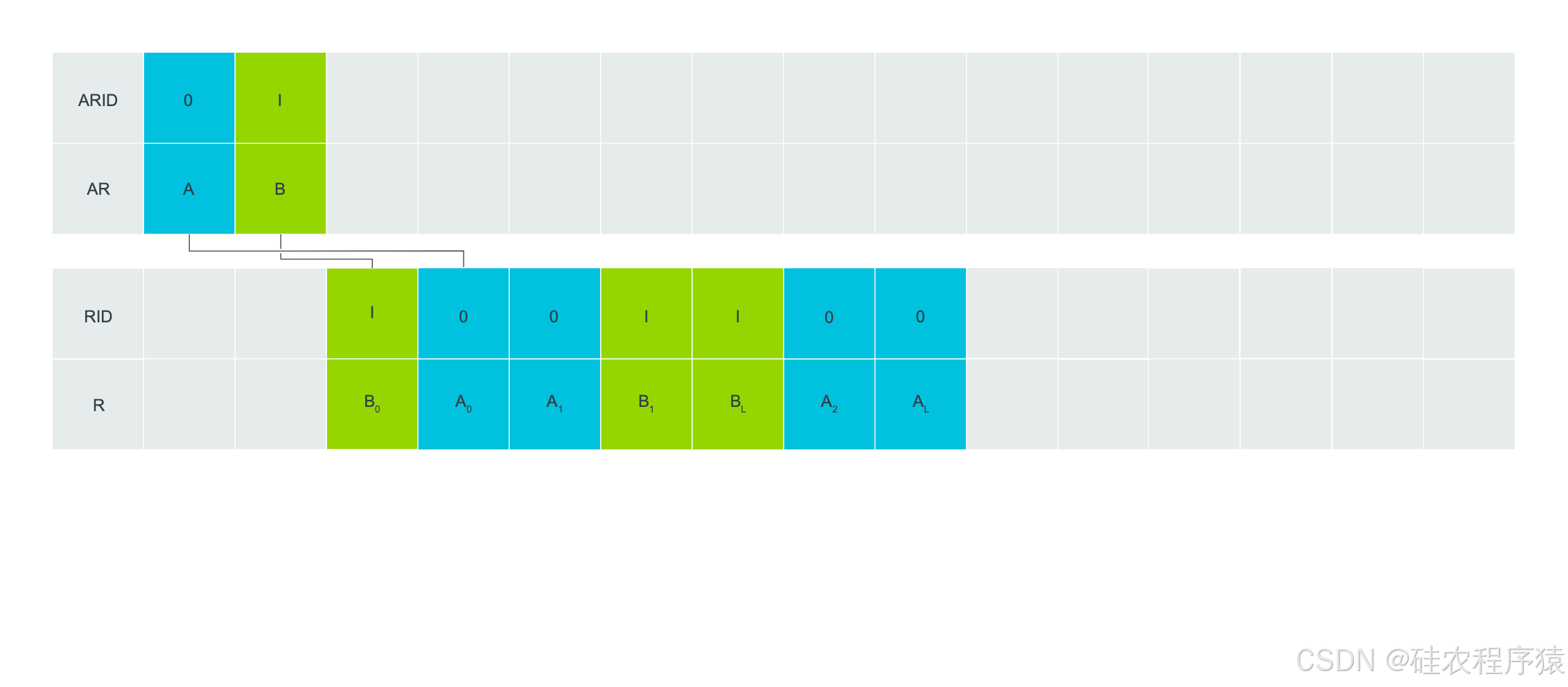

(2)读传输顺序

读事务有三种排序规则,在 R 通道上读取不同 ID 的数据没有排序限制。这意味着 subordinate 可以按任何顺序发送它。如下图所示,A 先于B 发送地址请求,但B 先于A返回读数据。

通道上不同 ID 的读数据可以交错,RID 值区分数据与哪个请求相关。如下图所示:

对于具有相同 ID 的事务,必须按照请求的顺序返回R通道上的读数据。

如下图所示,事务A和C具有相同的RID值0:

由于事务 A 是在事务 C 之前请求的,因此从机必须在 C 的数据值之前返回 A 的所有四个读数据。

(3)读写通道排序

读和写通道彼此之间没有ordering规则,可以按任何顺序完成。因此,如果主机需要对特定的读取和写入序列进行排序,则 Manager必须在发出新事务之前显式等待传输完成来确保遵守顺序。 下图显示了一个示例,其中 manager 要求对来自地址的 write-read-write序列进行特定排序:

操作顺序如下:

1、主机发送第一个写请求,等待 Write Response 通道上的信号来确保从机已完成写操作。

2、主机发送读请求,主机等待 Read Data 通道上的最终响应。

3、主机发送第二个请求。

总结

无论是AXI3还是AXI4及更高级协议,对于不同ID,都支持读、写乱序;对于相同ID,需要保序;

AXI3都支持读交织(对一个transaction);但AXI4不支持写交织。

3、非对齐传输起始地址

AXI 协议支持非对齐地址传输,该地址仅影响地址的第一次传输。在传输的第一笔之后,所有其他transfer都要地址对齐。

注意

AXI 协议支持使用选通信号的未对齐传输

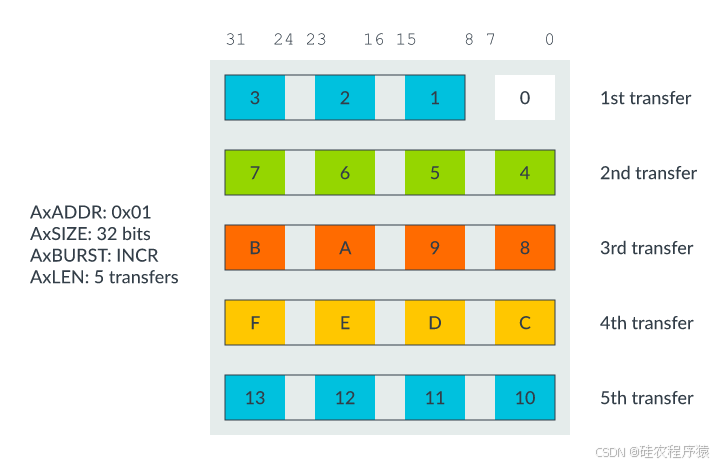

未对齐的传输是 AxADDR 值不必与事务的宽度对齐的地方。例如,从字节地址 0x1002 开始的 32 位数据包与自然 32 位地址边界不对齐0x1002因为它不能被 0x20 整除。 以下示例显示了从未对齐地址 0x01 开始的 5 拍 32 位传输:

如果传输与起始地址 0x00对齐,则结果将是一个宽度为 4 字节的 5 拍突发,最大数据传输量为 20 字节。但是,当有一个未对齐的起始地址 0x1,这会减少传输的总数据量,但这并不意味着最终的未对齐传输将完成突增并产生回卷。

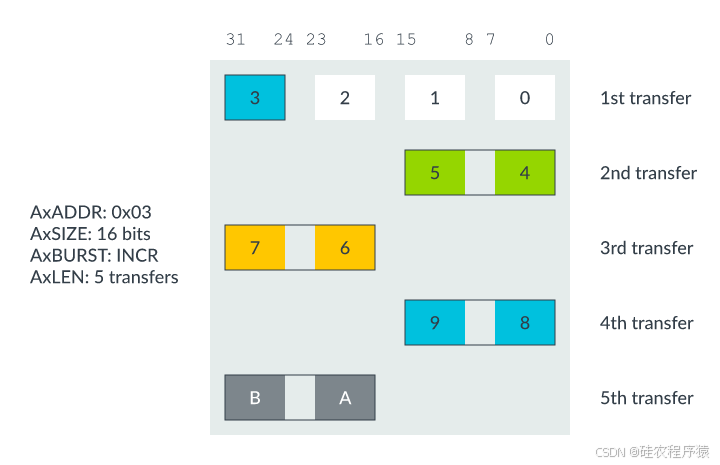

以下示例显示了从地址 0x03 开始的 5 拍 16 位大小的事务:

如果事务与起始地址 0x00对齐,则结果将是一个宽度为 2 字节的 5 拍突发,最大数据传输量为 10 字节。但此示例中,第一次传输从未对齐的地址 0x03 开始,最大数据传输量为9字节。

4、支持字节序

AXI 协议通过使用 Big Endian-8 (BE-8) 模式,支持同一内存空间中的混合字节序结构。与 little-endian 模式相比,BE-8 模式使用相同的字节通道,但字节的顺序是相反的。

注意

使用 BE-32 的混合端结构比使用 BE-8 的结构更复杂,因为字节通道与小端模式不同。

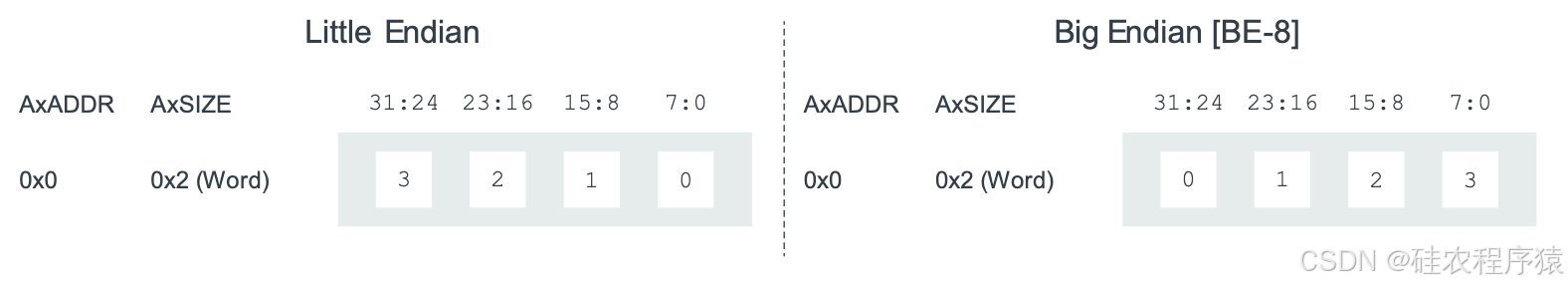

下图显示了同一四字节单词的 little-endian 和 big-endian 表示形式:

对于 little-endian 模式下的 4 字节字,最高有效字节使用最高有效字节通道。在 BE-8 模式下,最高有效字节使用最低有效字节通道。

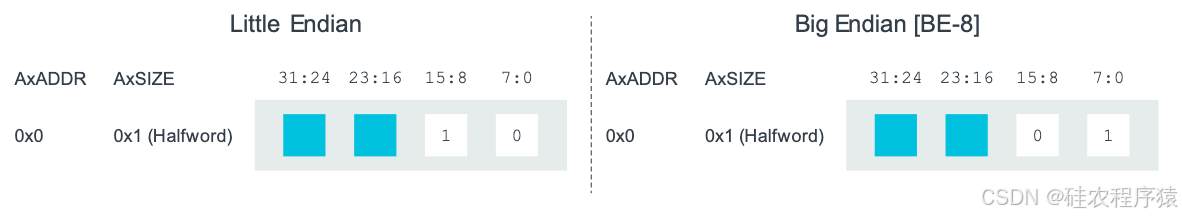

以下示例显示了同一双字节单词的 little-endian 和 big-endian 表示形式:

对于 little-endian 模式下两个字节的半字,最高有效字节使用字节通道 1,最低有效字节使用字节通道 0。在 big-endian BE-8 模式下,两个字节使用的通道被交换。

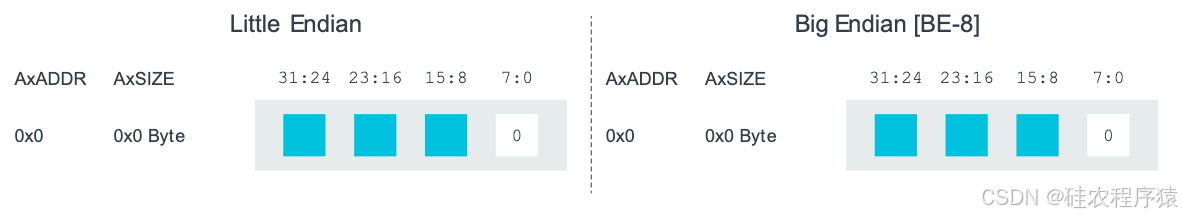

对于单字节,little-endian 和 big-endian 模式之间没有区别,如以下示例所示:

在支持 BE-8 的 Arm 内核等可配置字节序组件中,字节的重新排序应在内部执行,无需在互连级别执行。另一方面,连接到 AXI 互连(本质上是 BE-8)的自定义设备具有正确的字节顺序。AXI 协议中的 BE-8 简化了对动态字节序切换的支持。