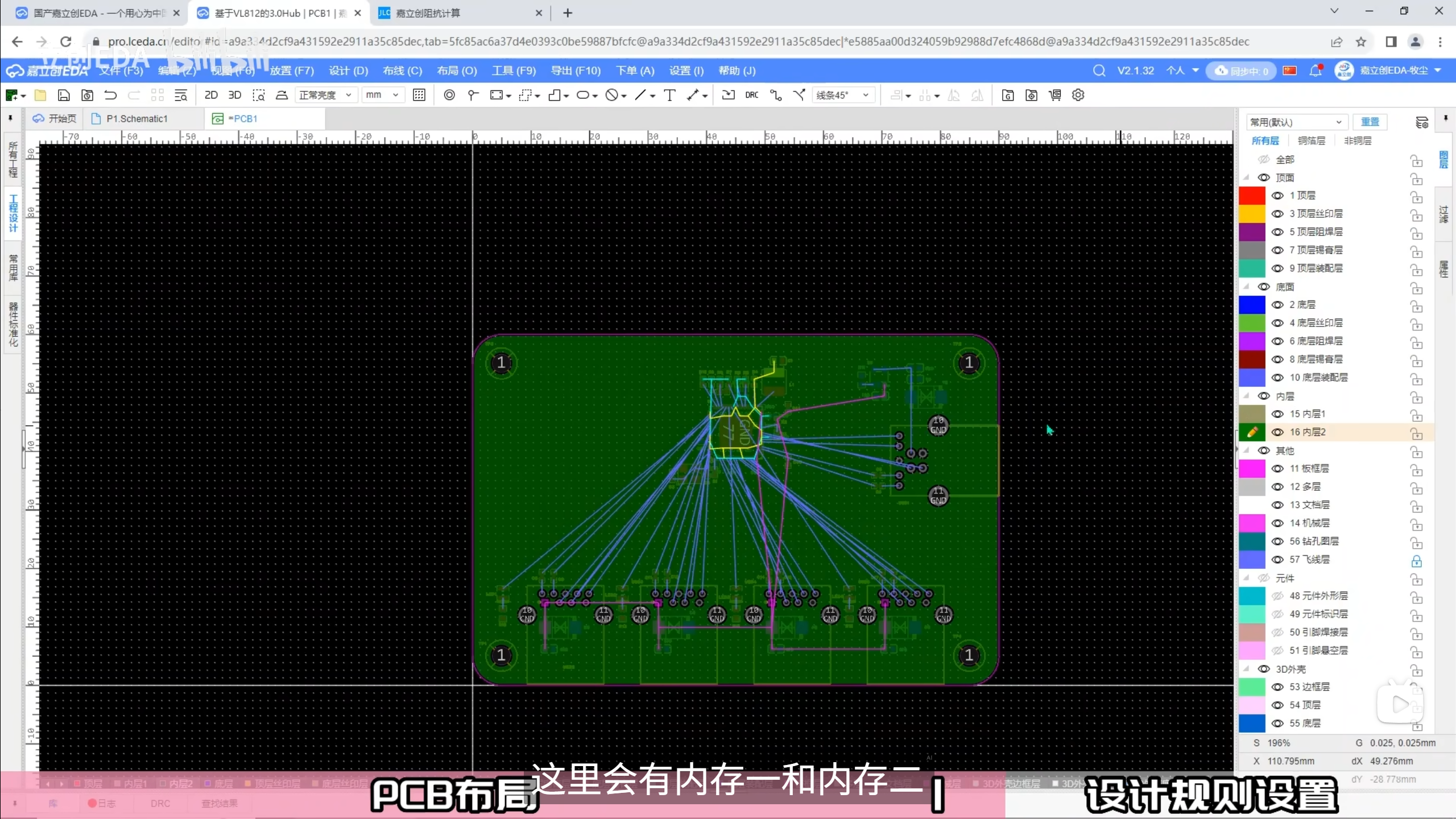

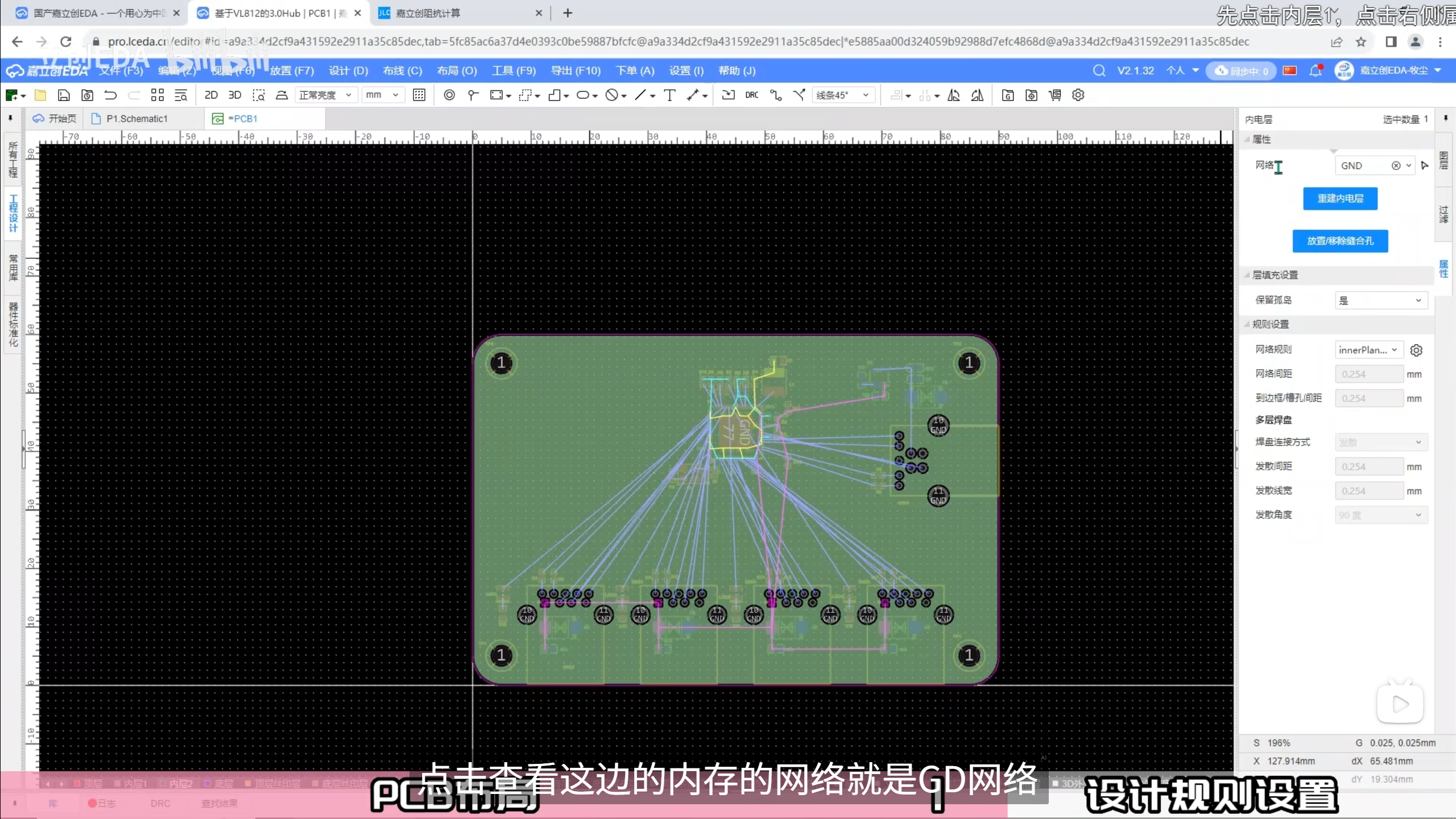

嘉立创EDA四层板PCB学习记录(44小点)

1.

2.

3.

4.

5.

6.

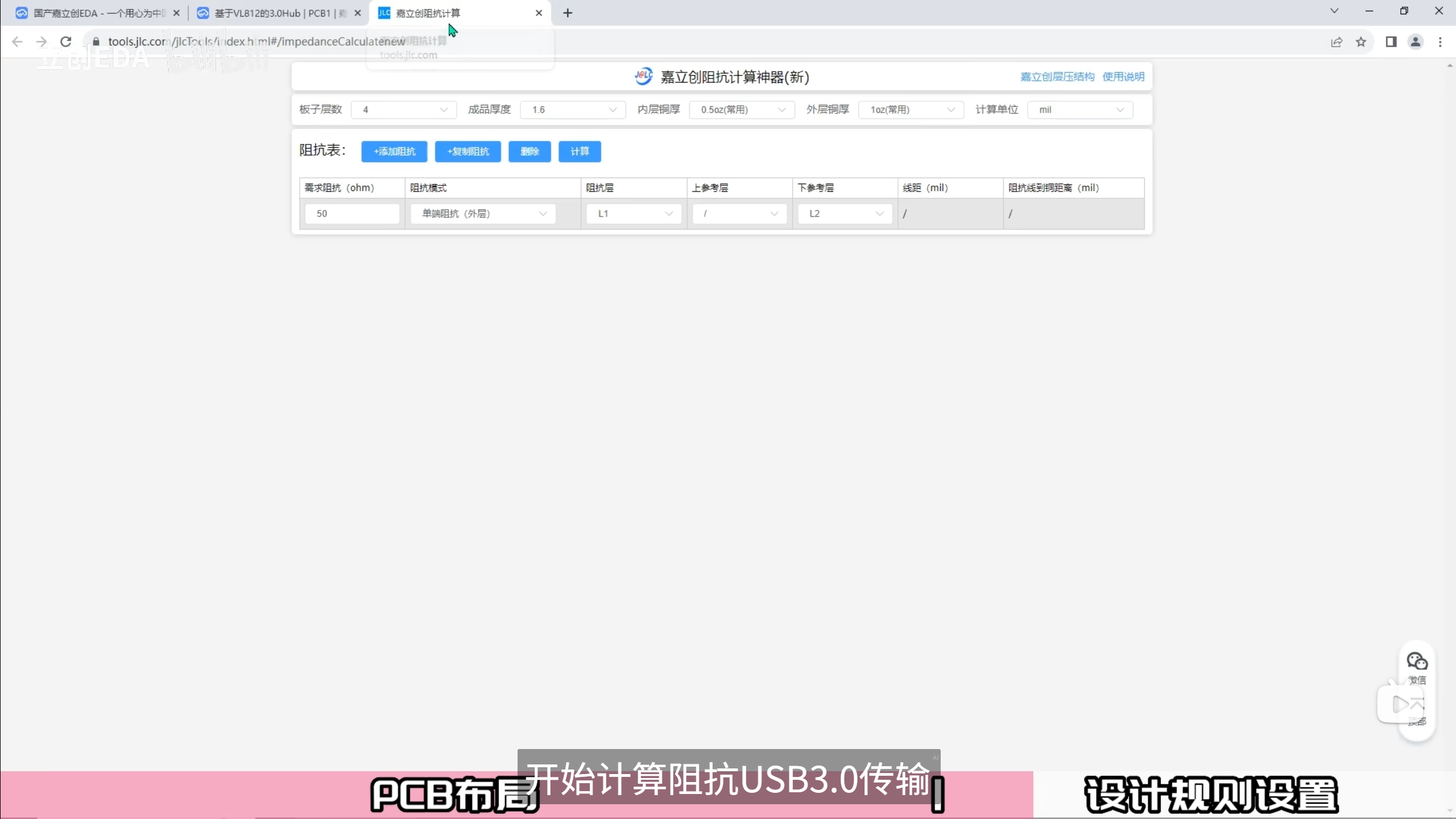

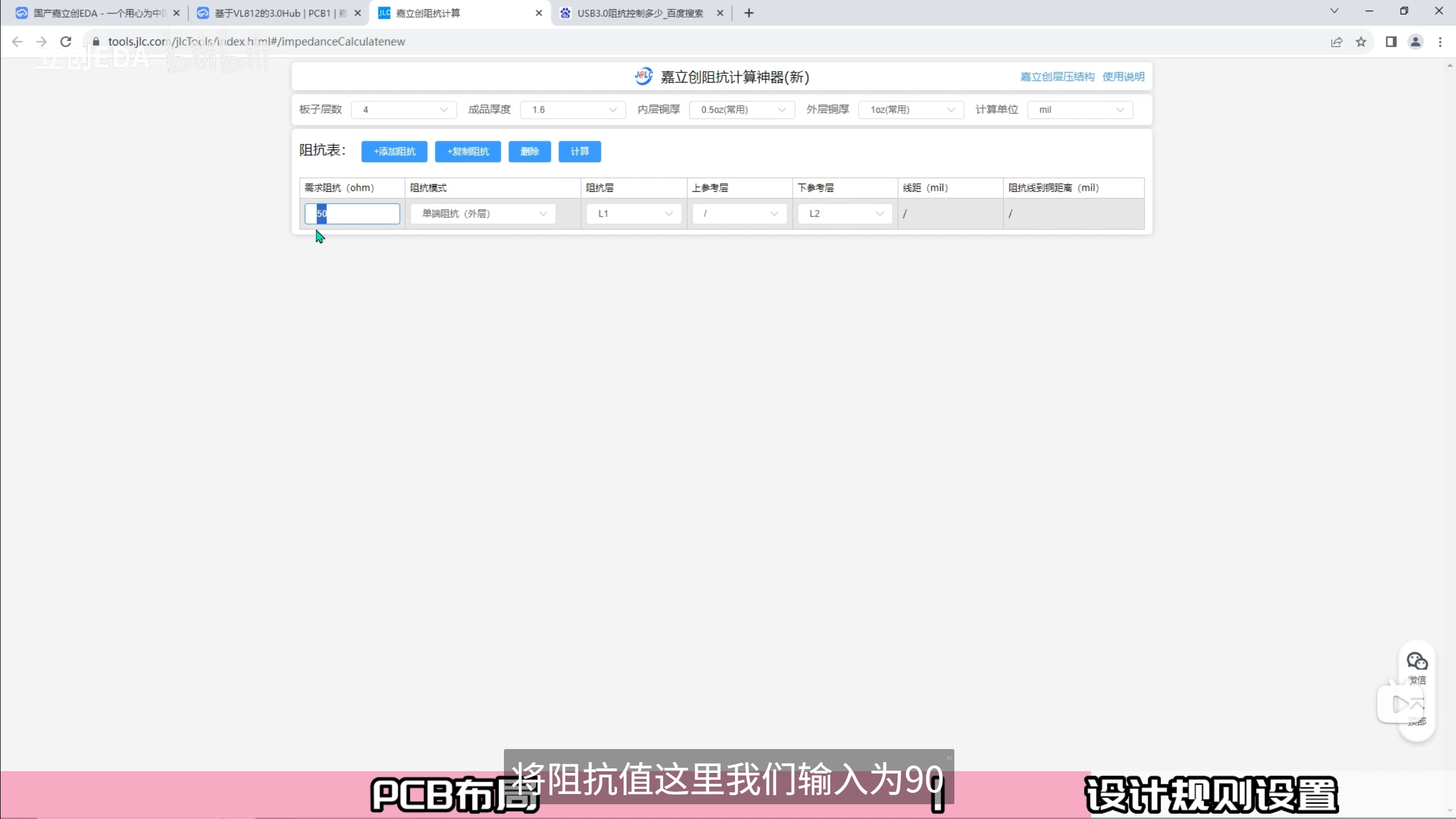

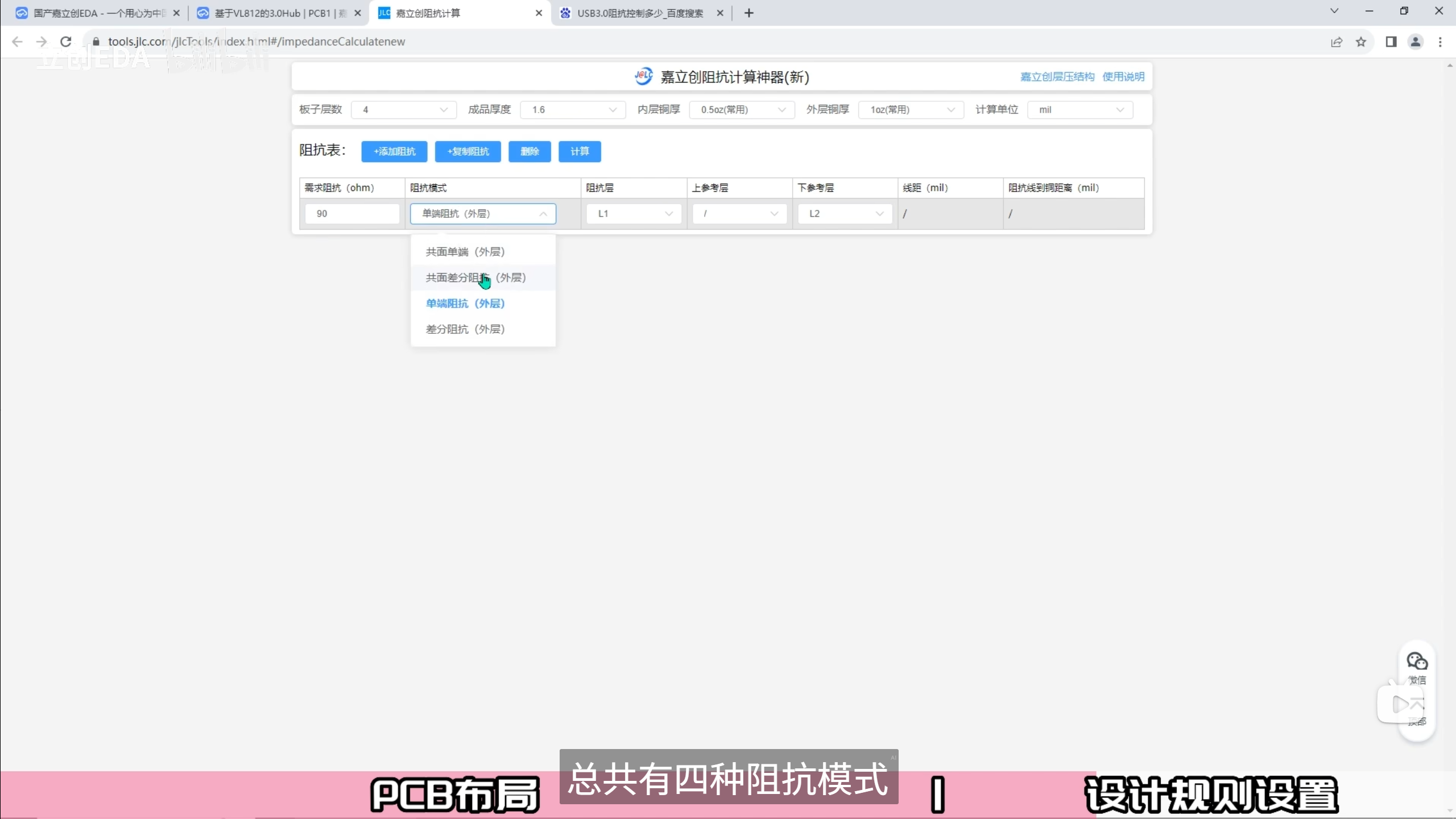

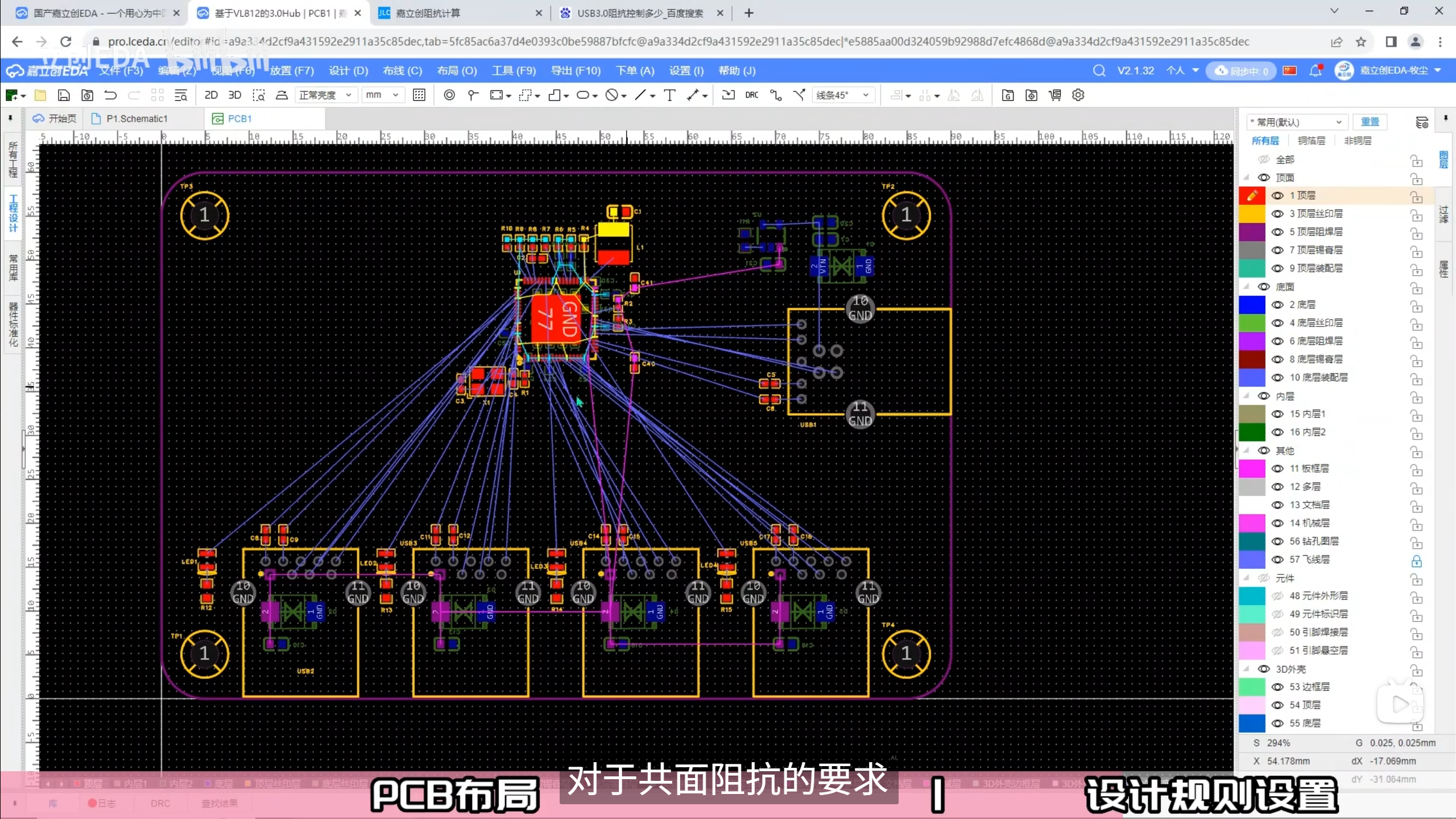

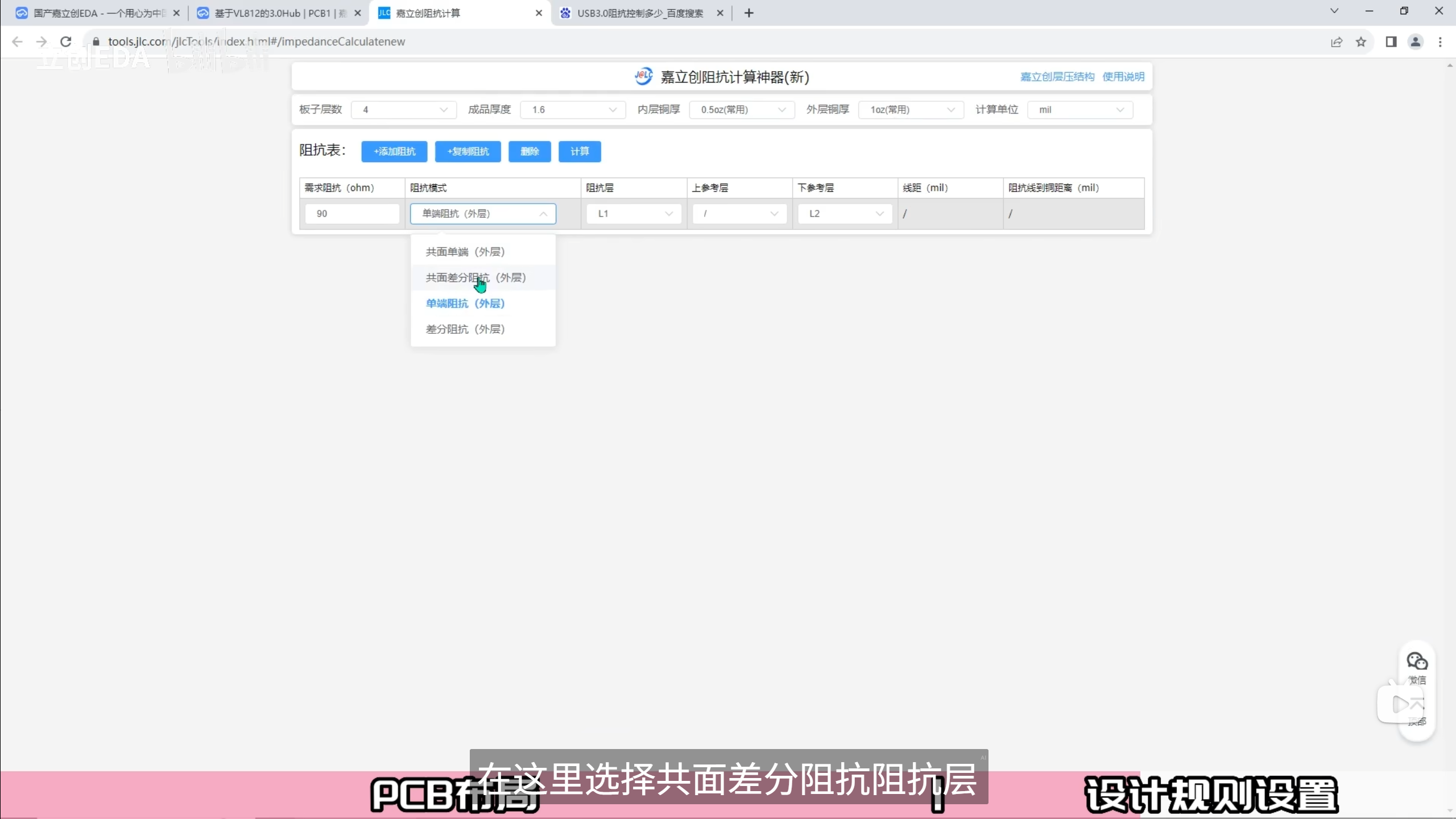

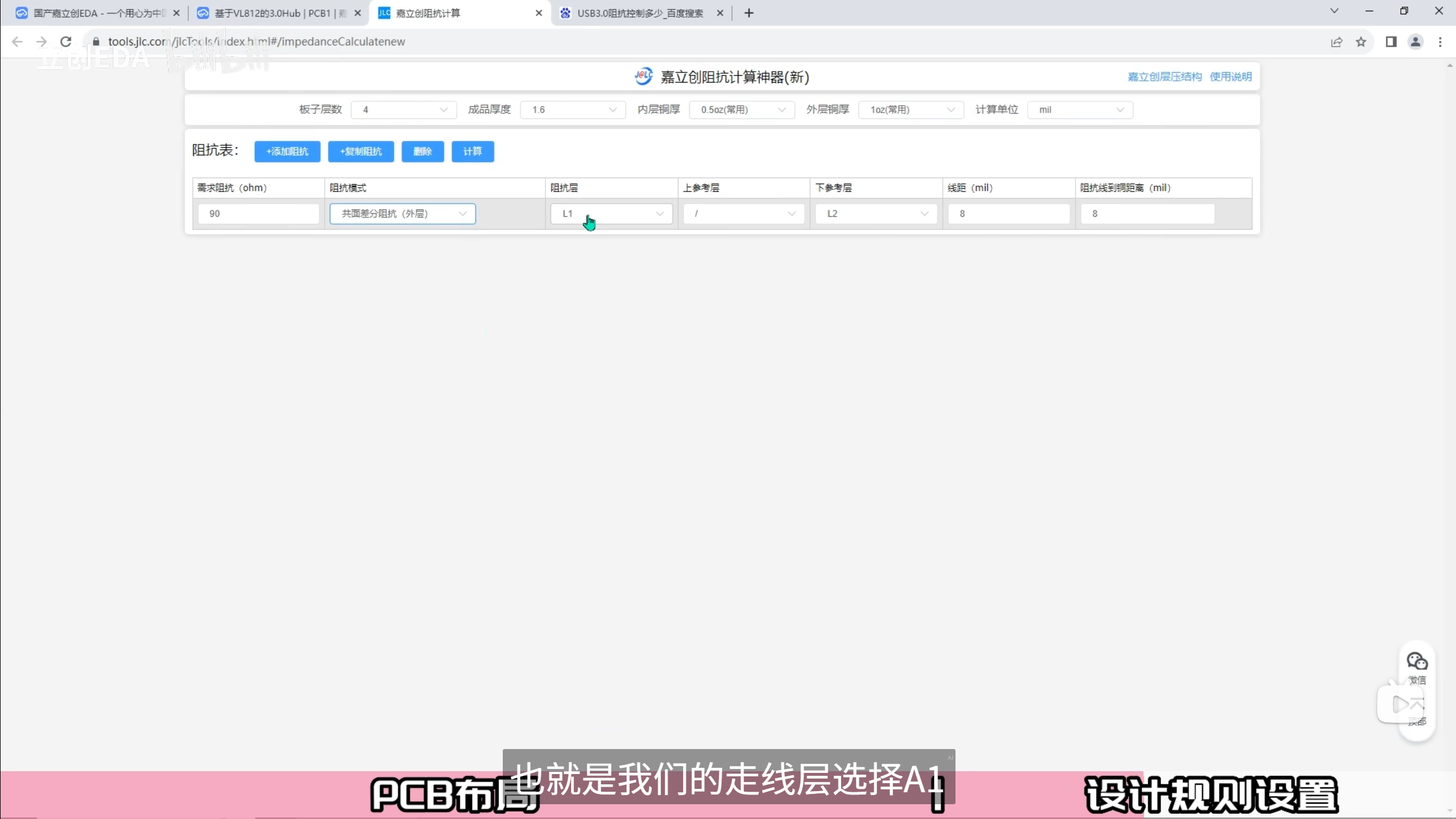

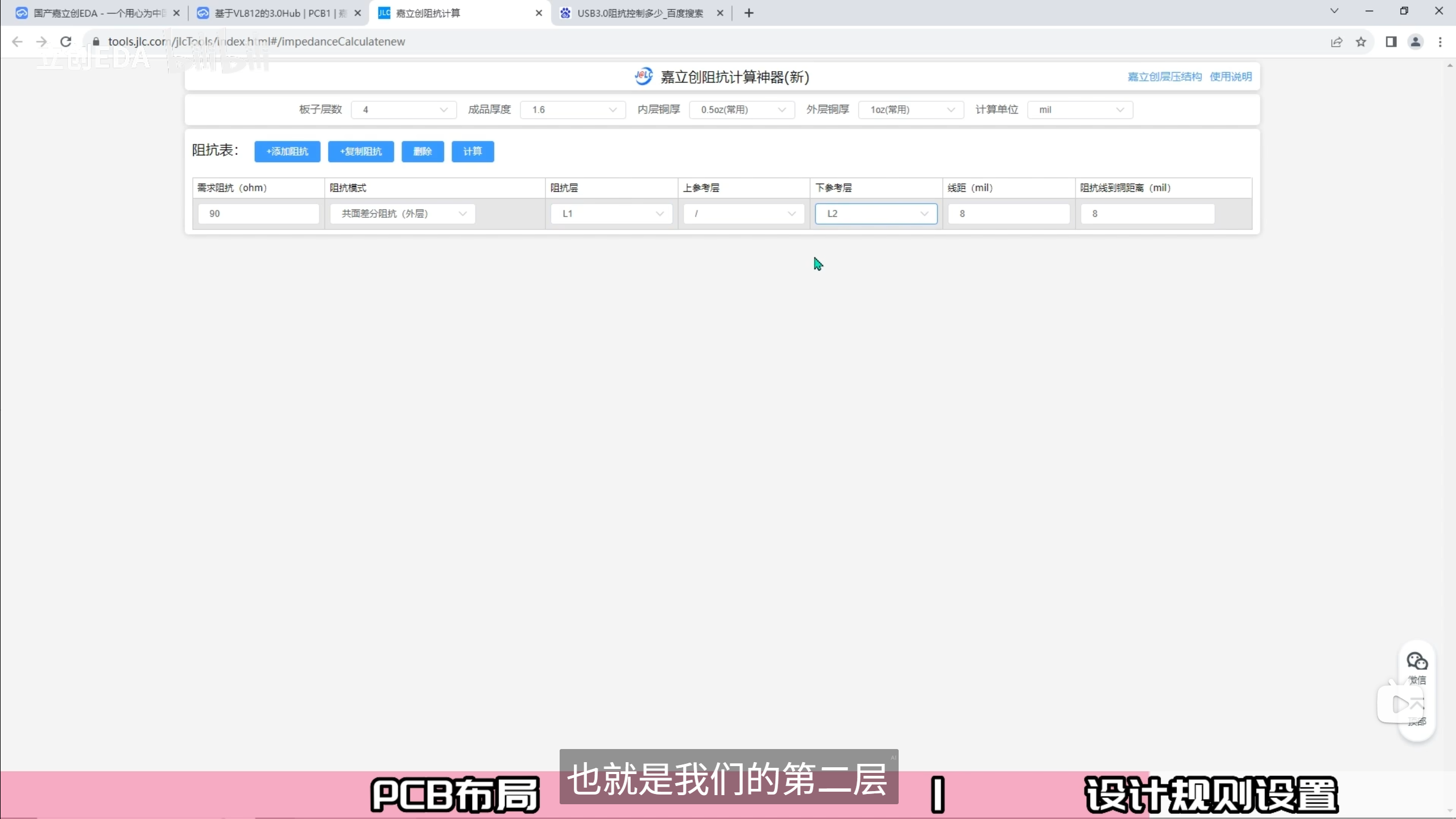

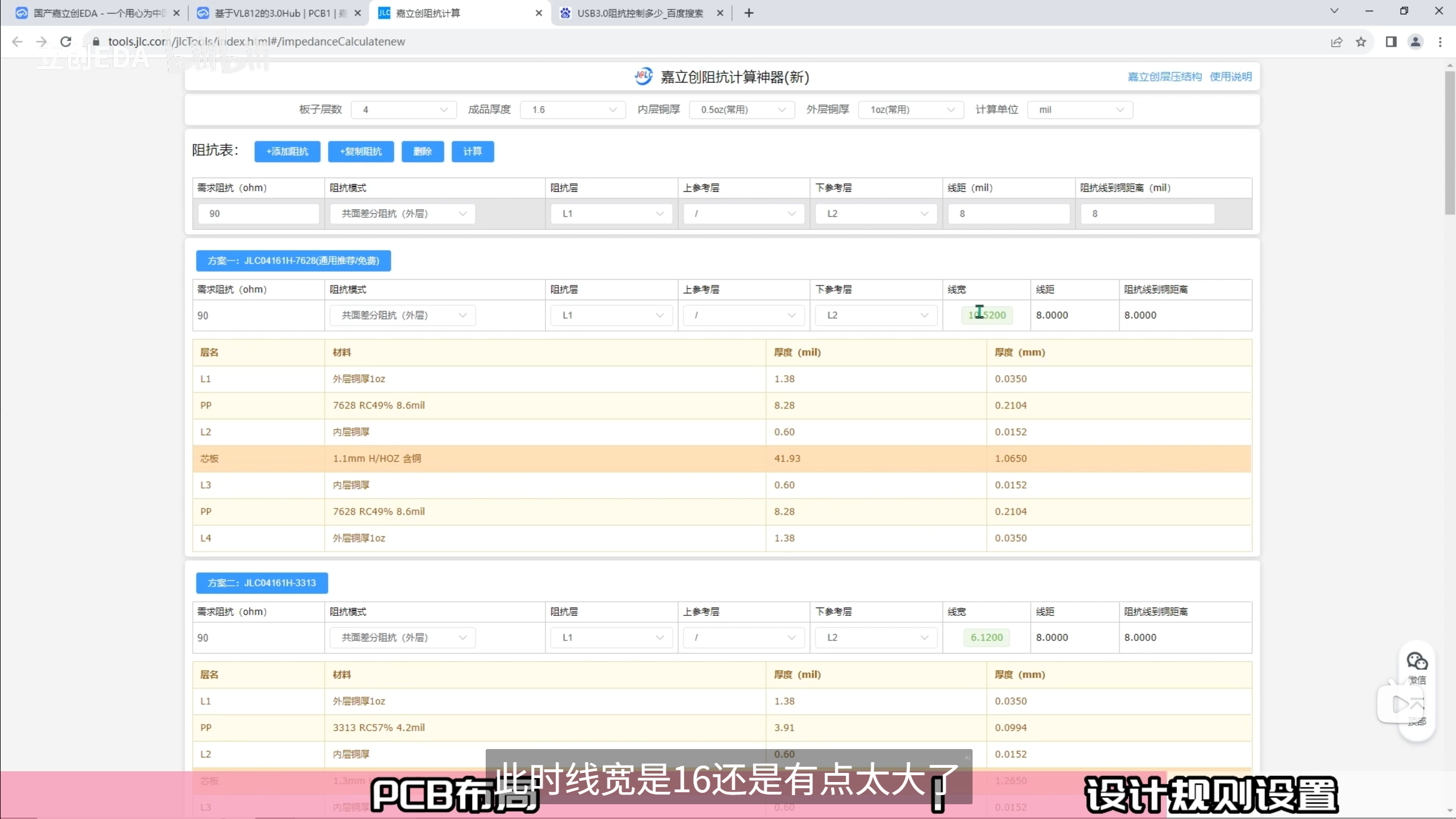

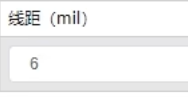

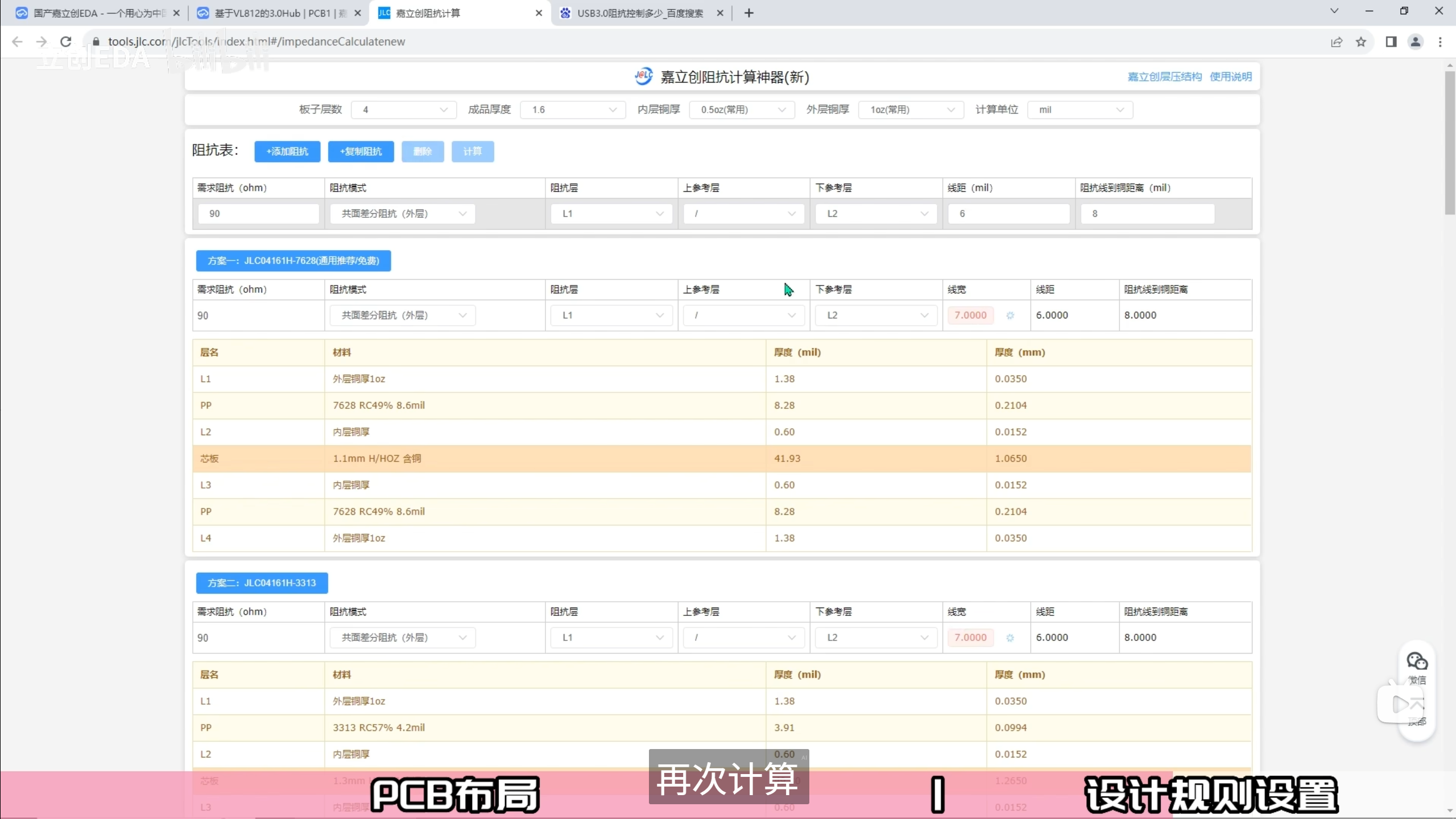

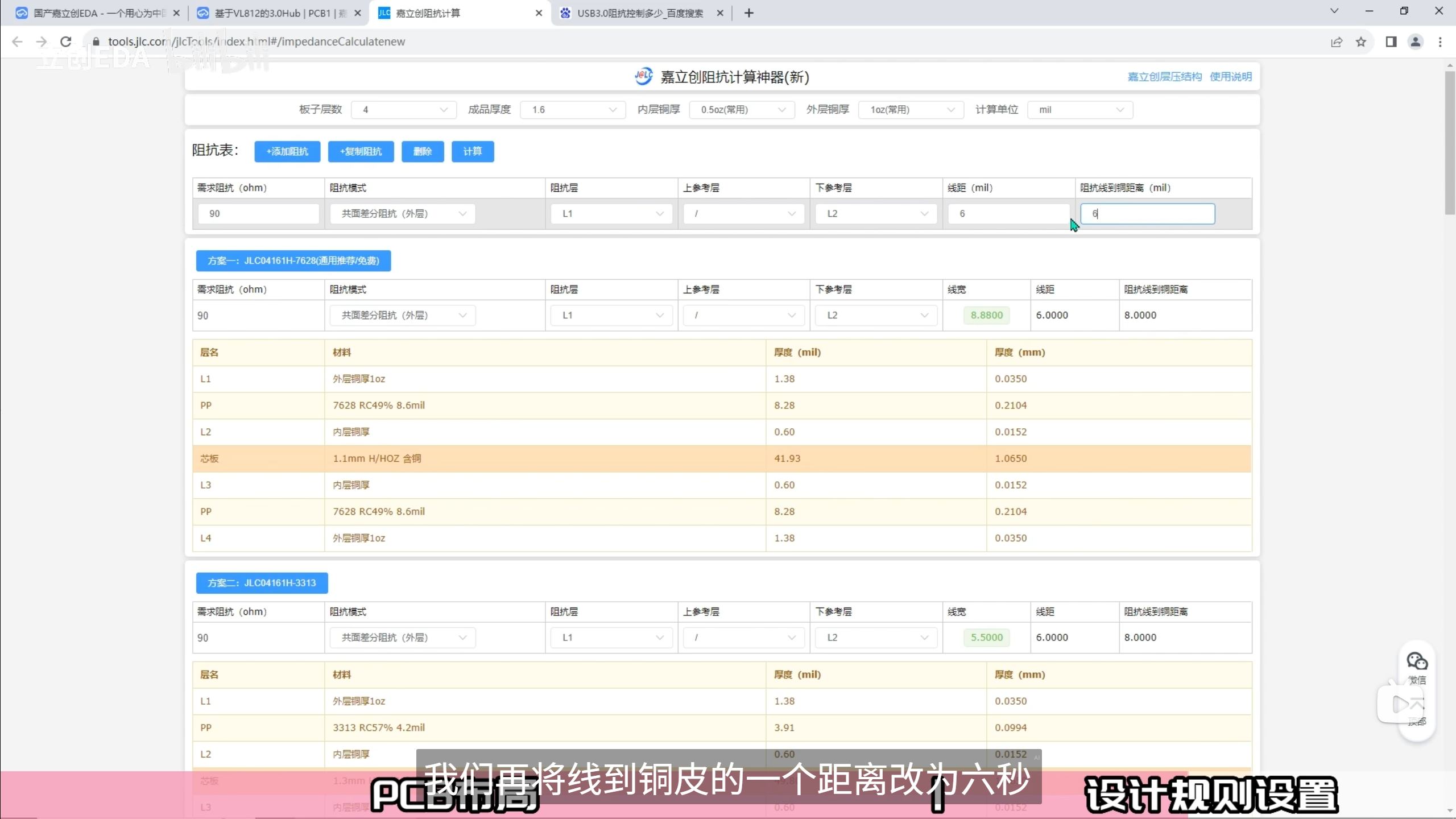

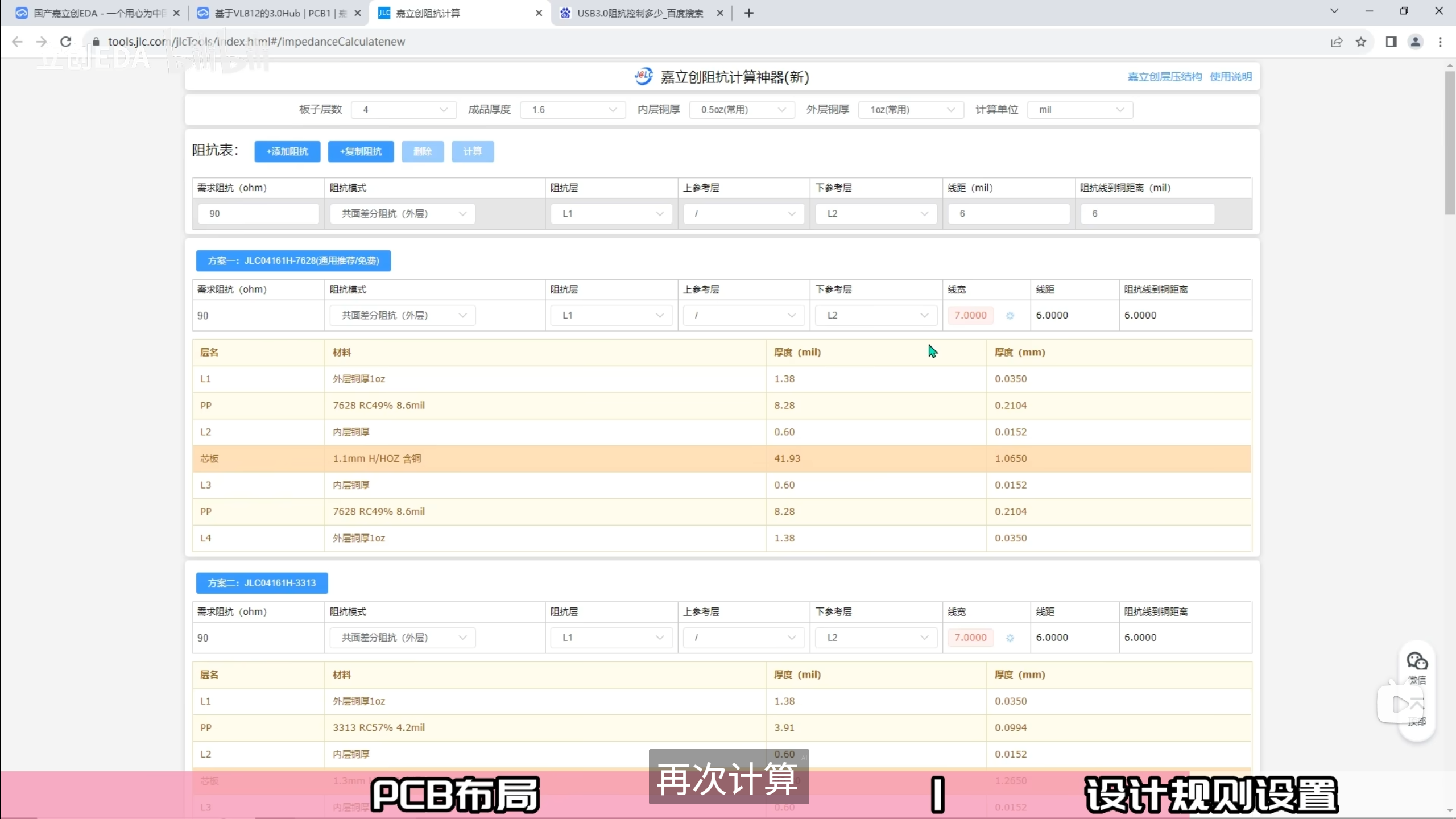

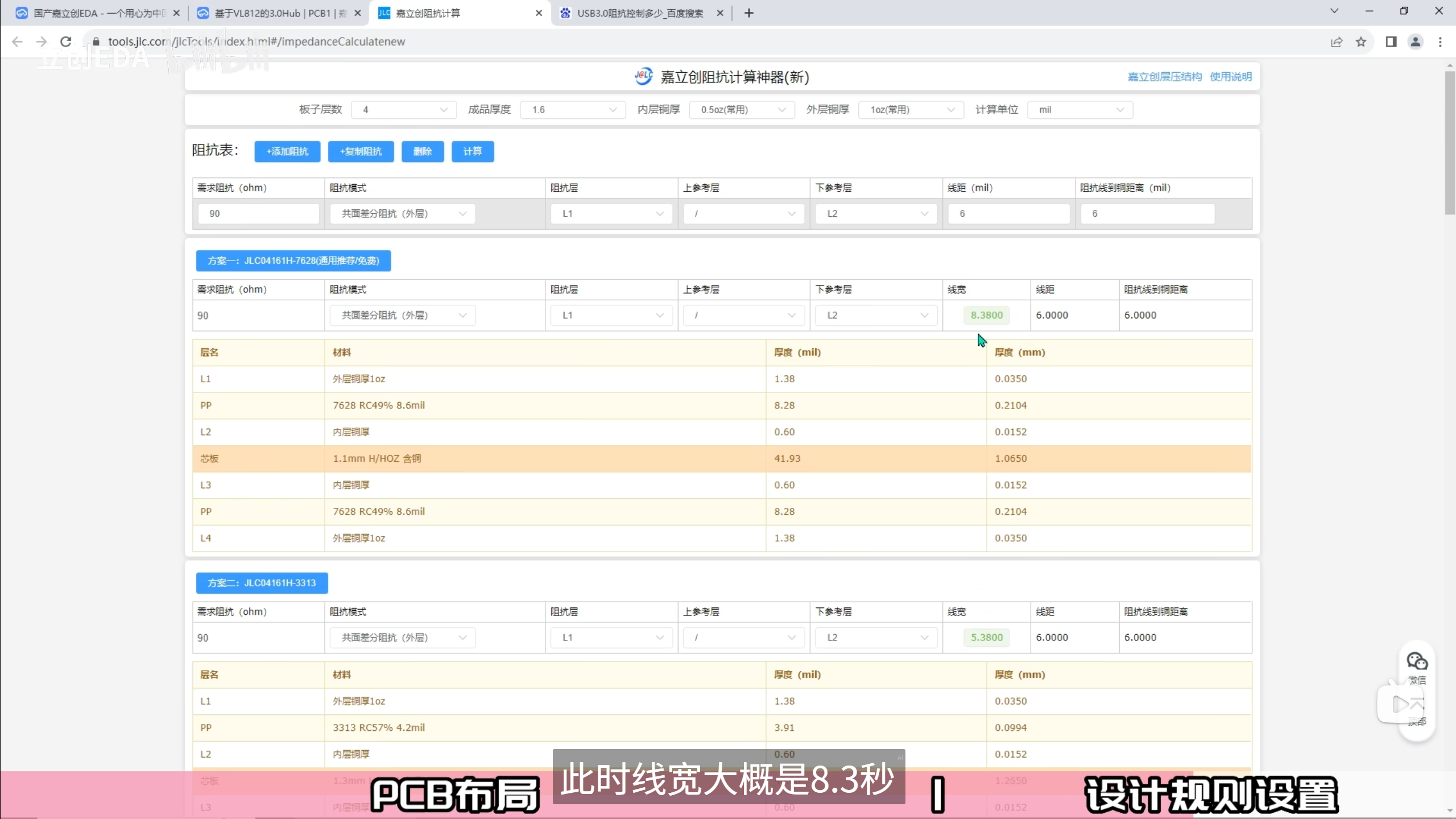

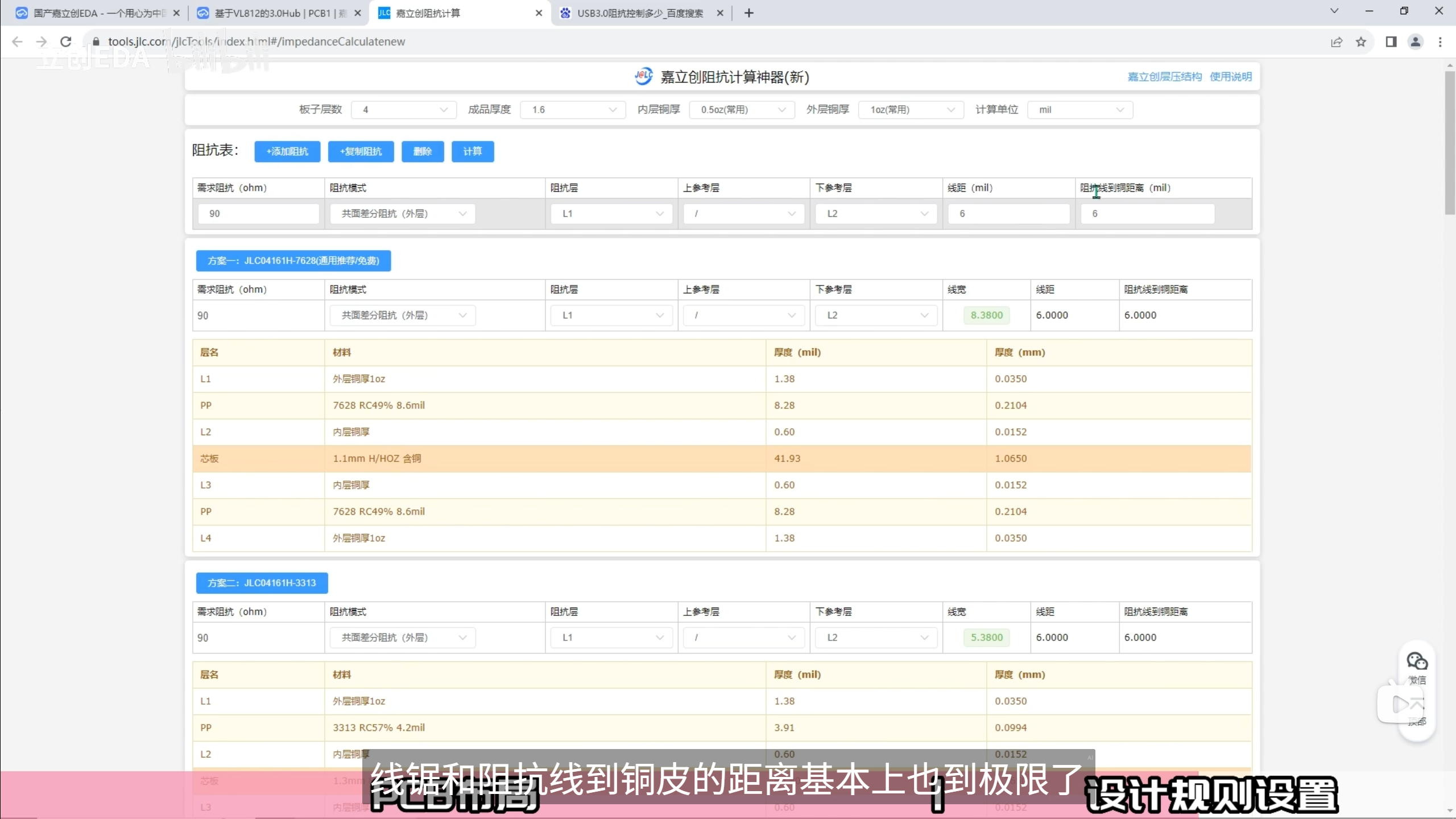

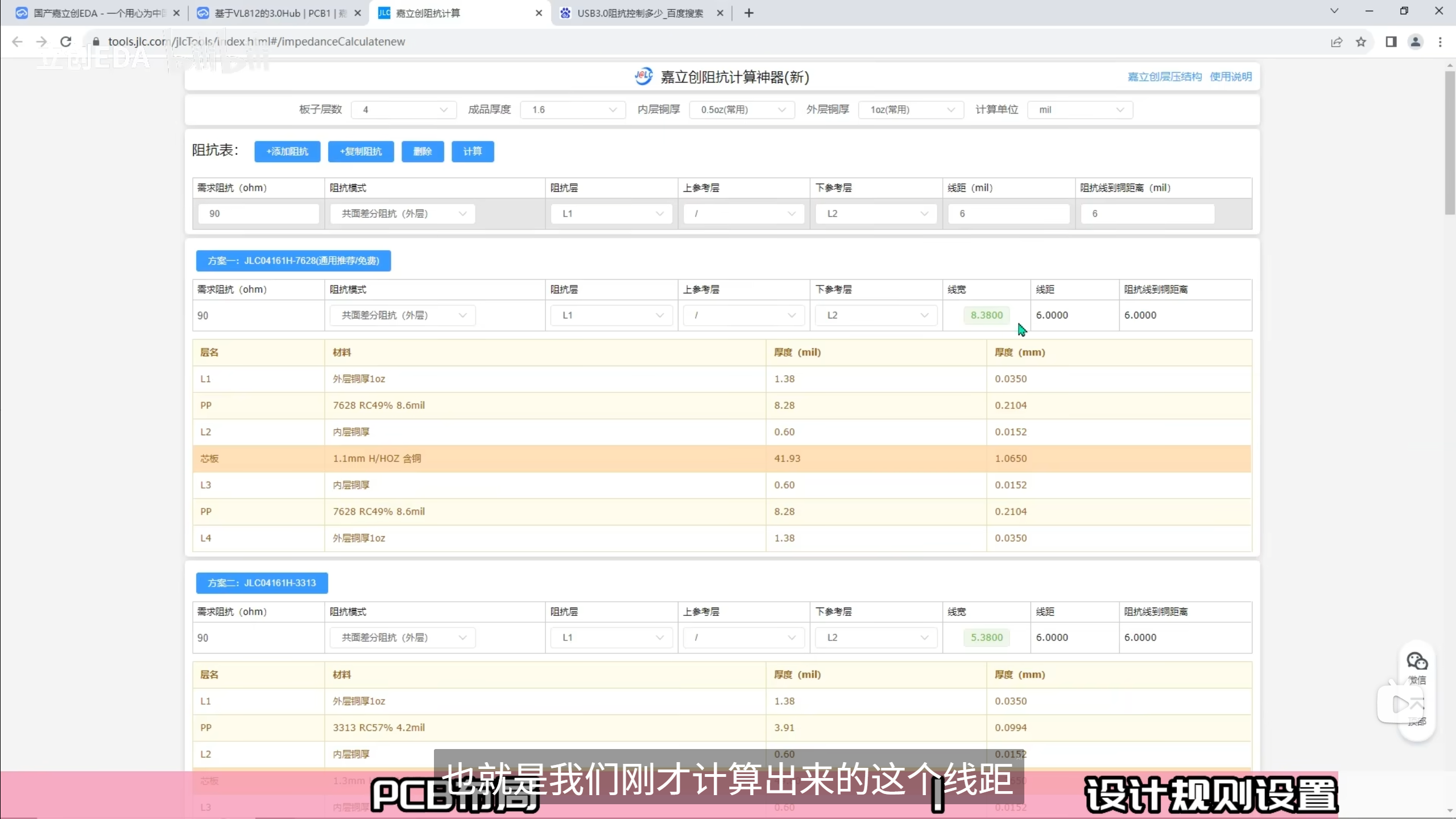

7.受控阻抗计算器 - JLCPCB

8.

9.

10.

11.

12.

13.

14.

15.

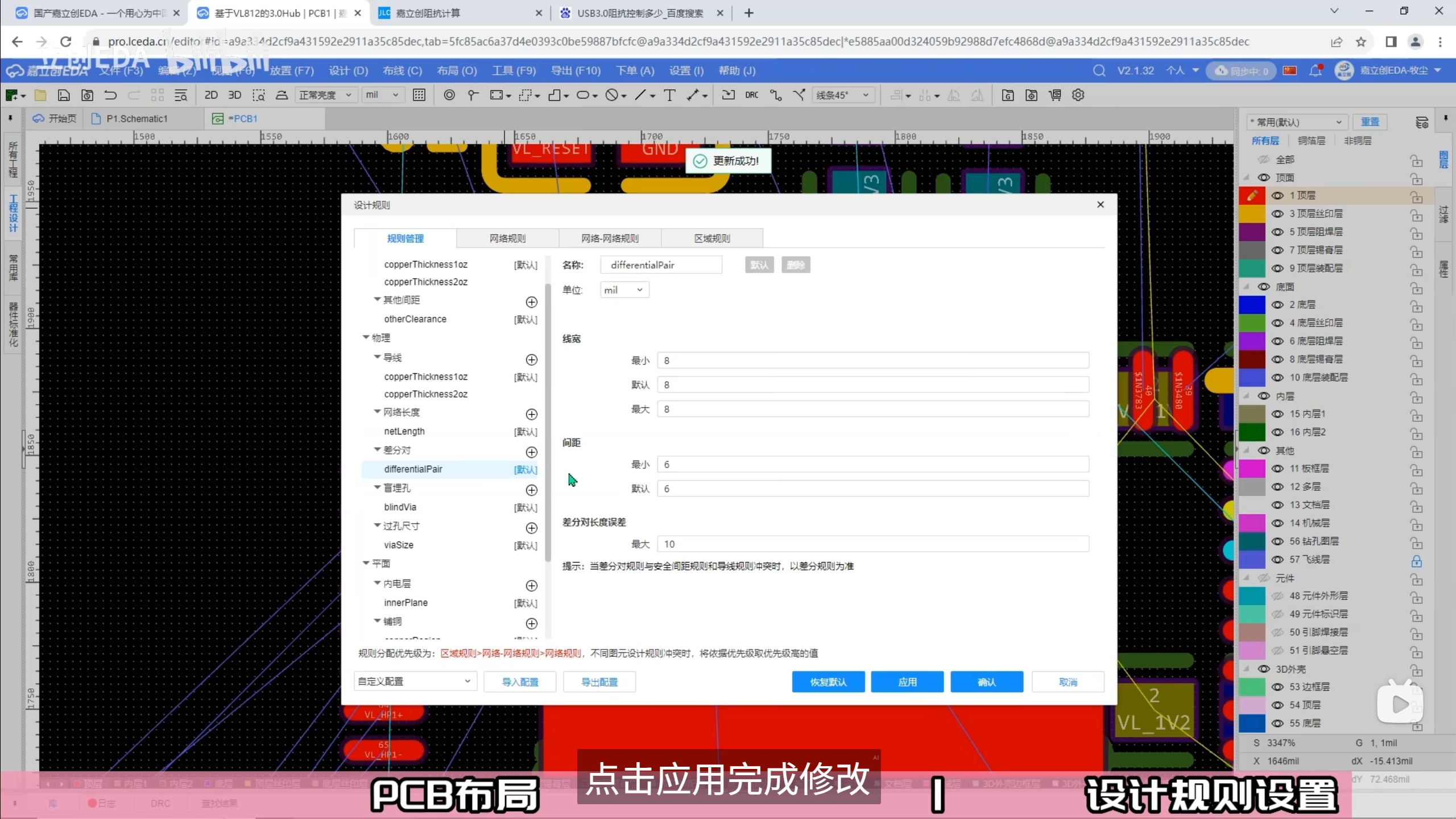

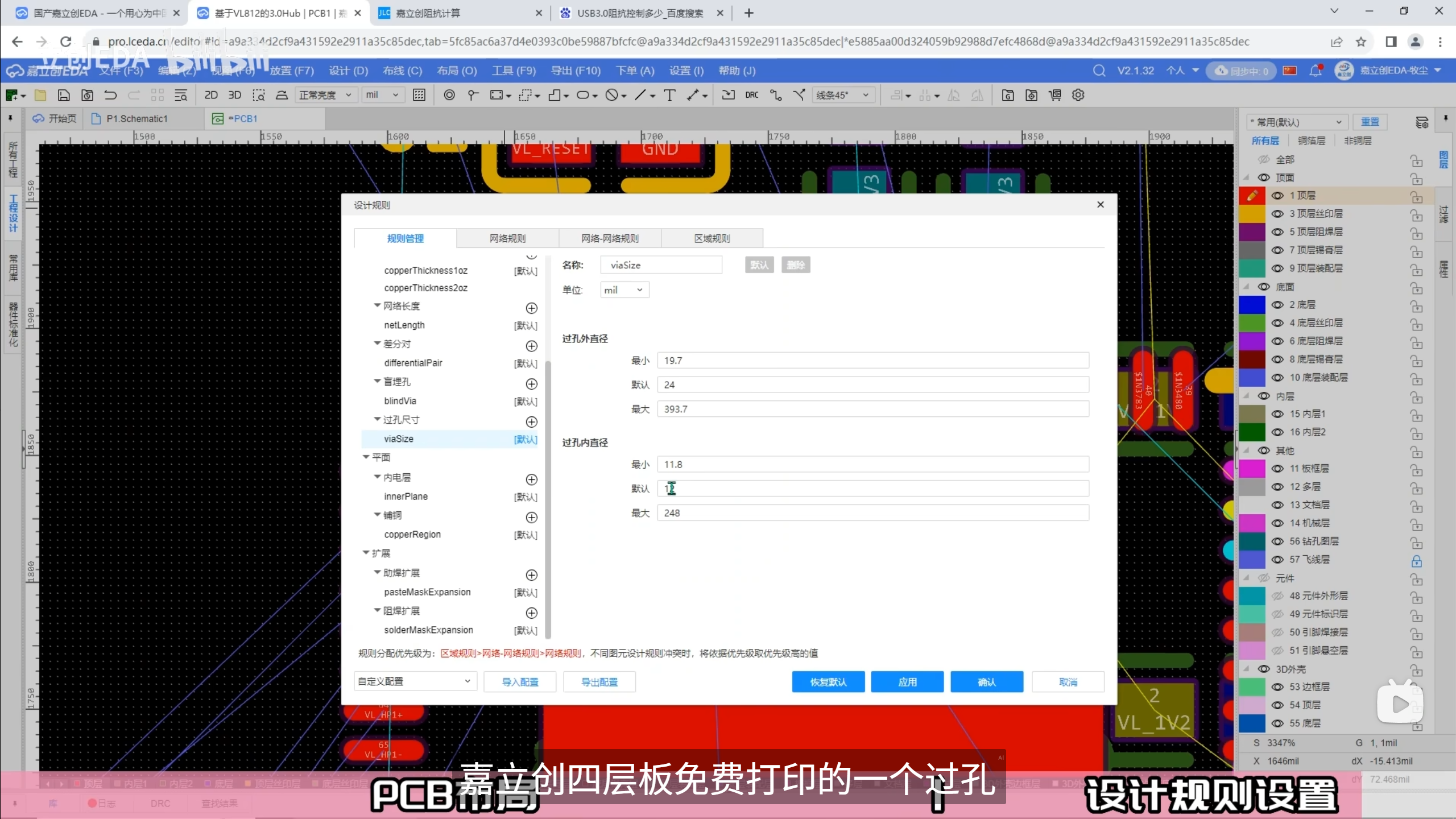

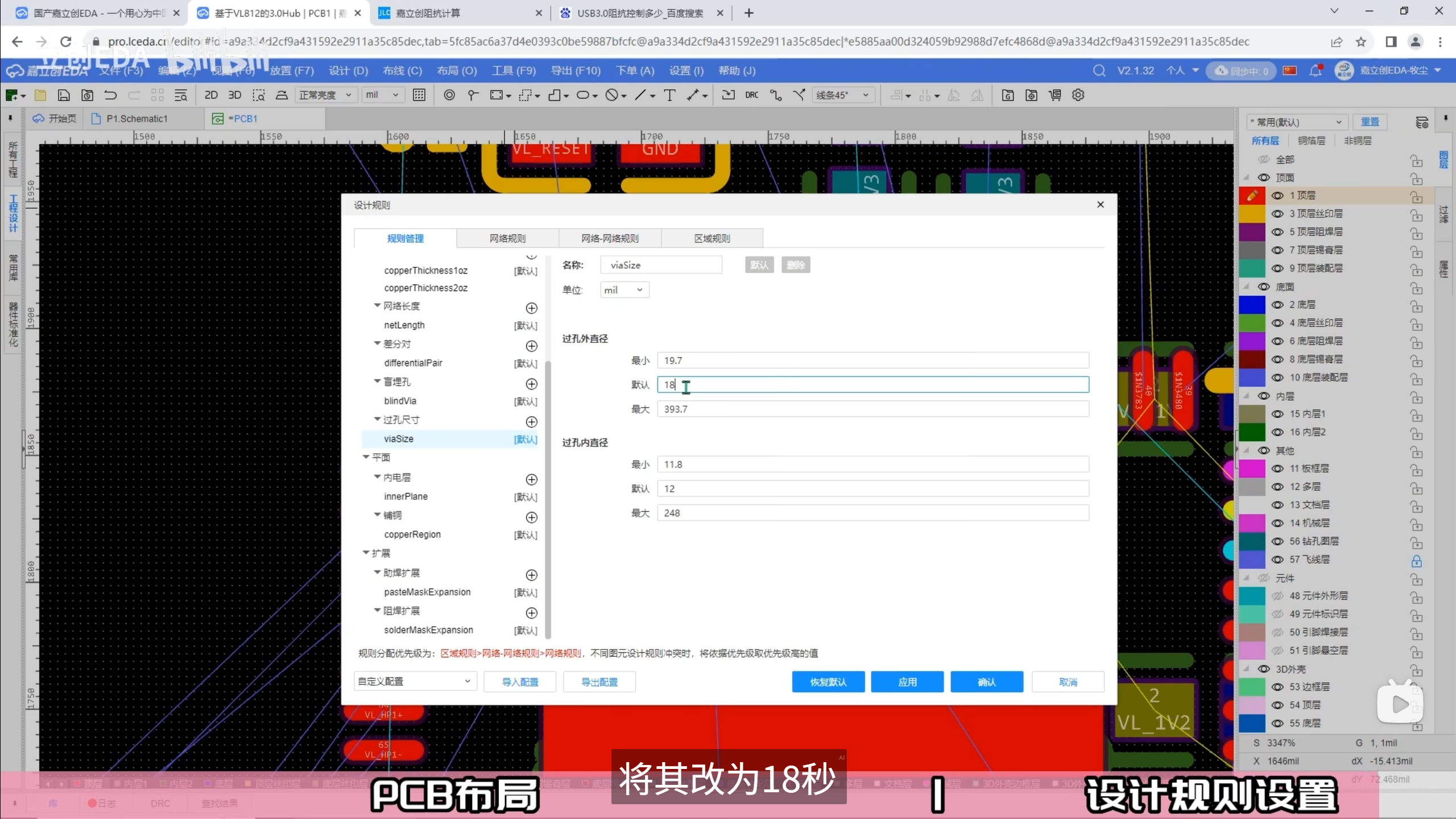

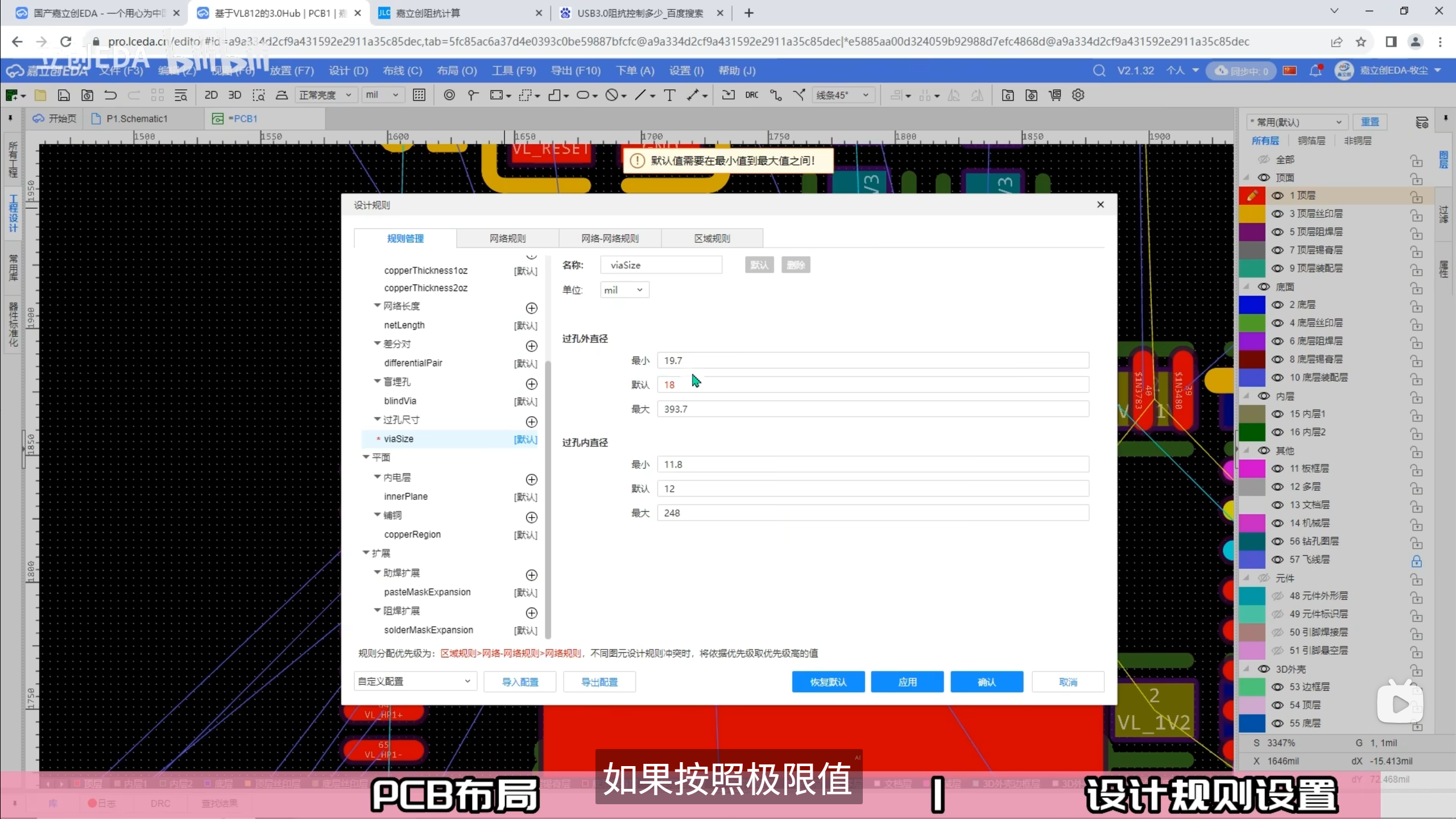

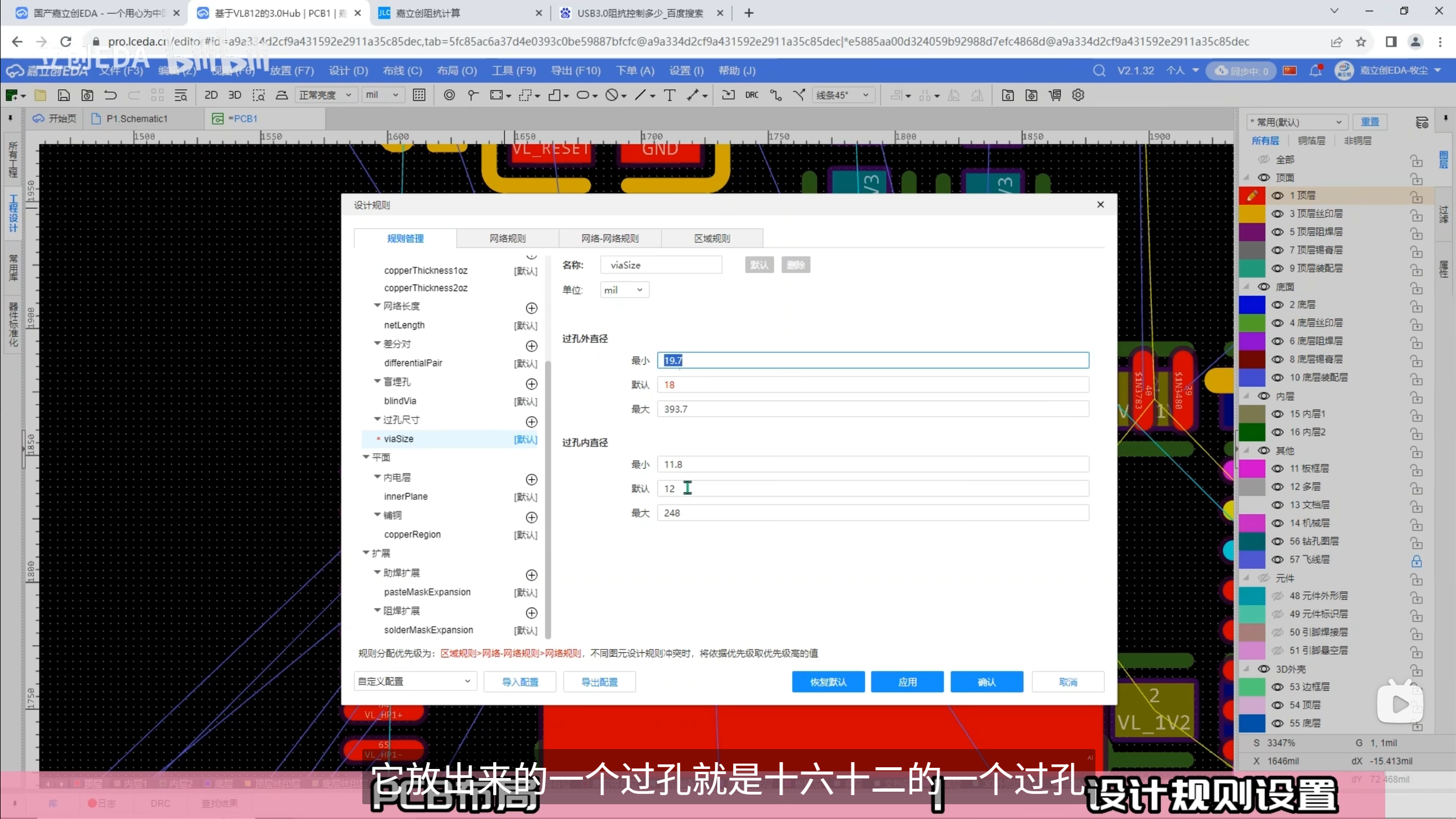

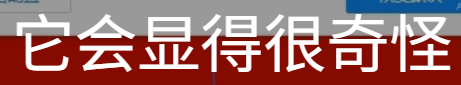

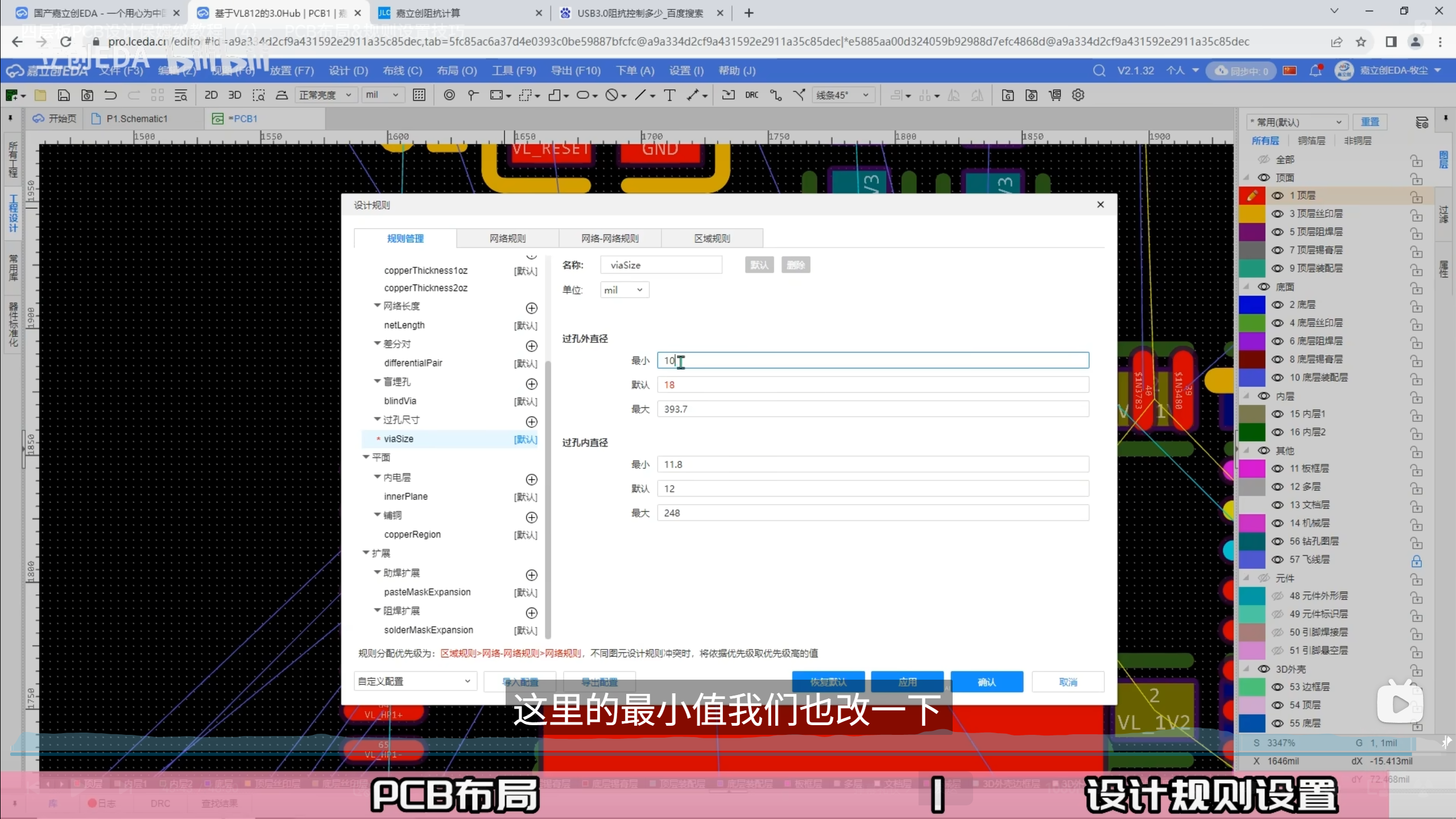

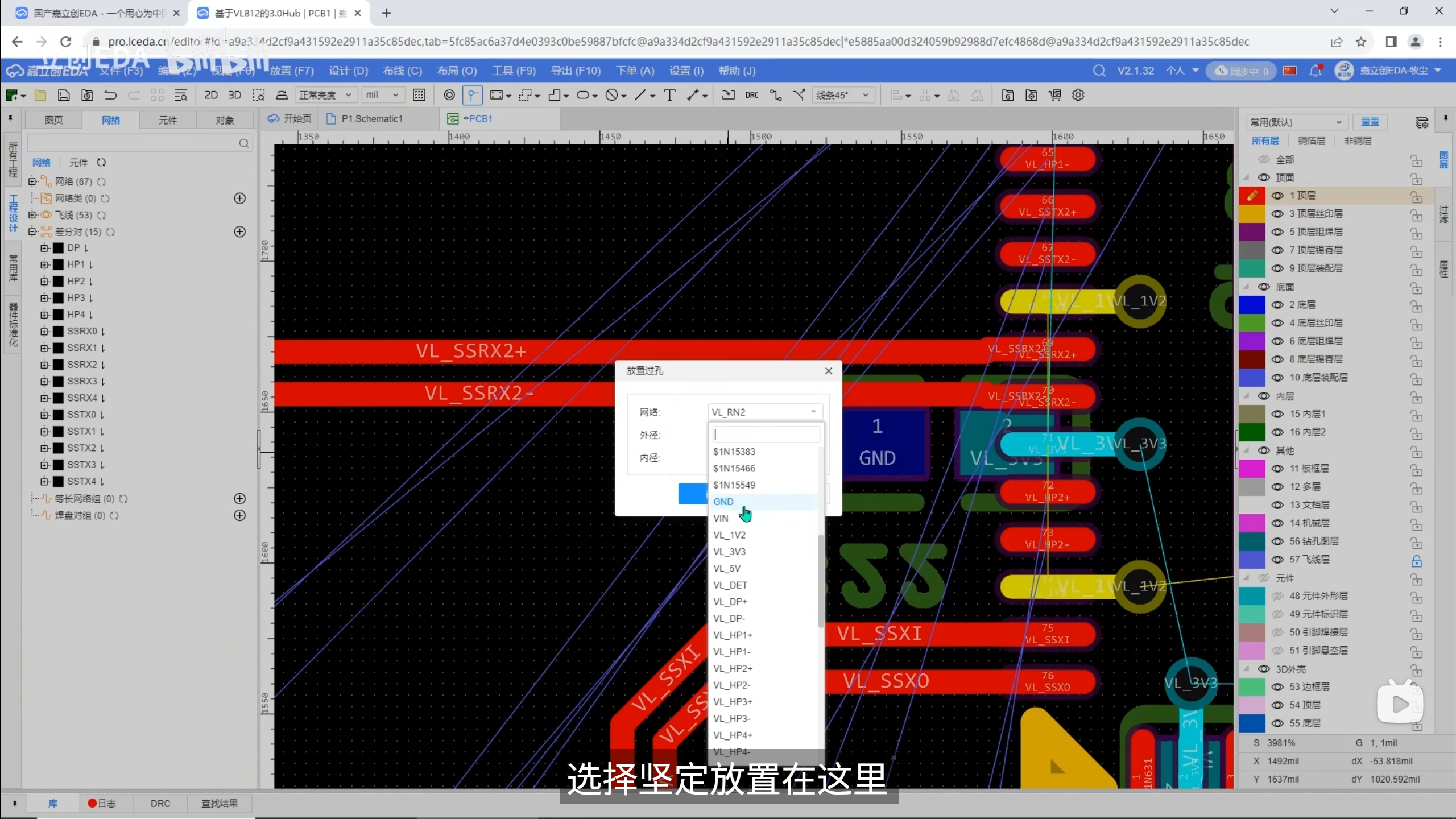

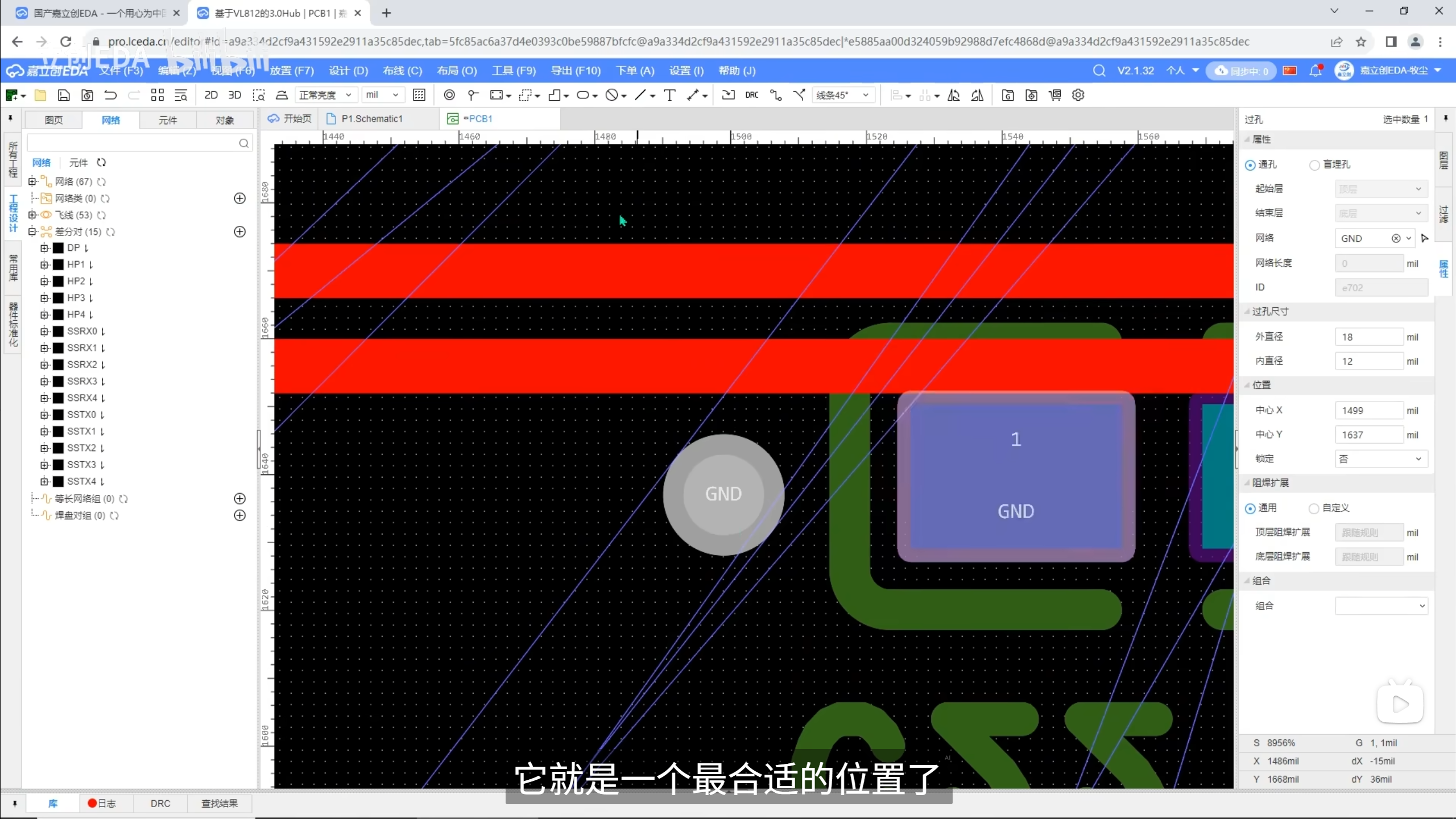

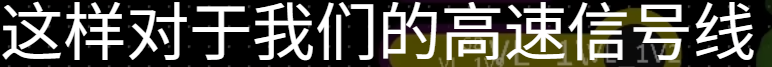

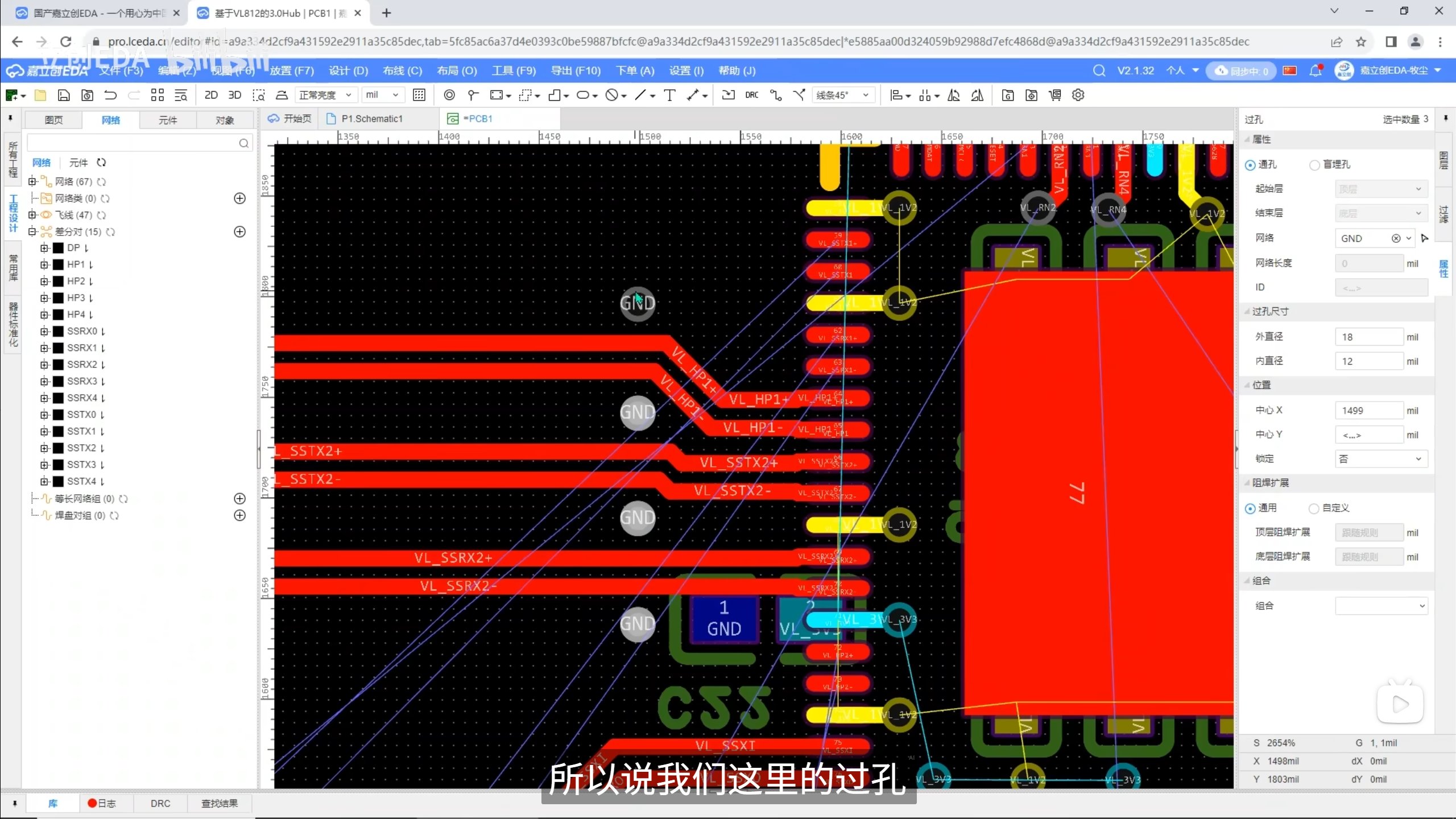

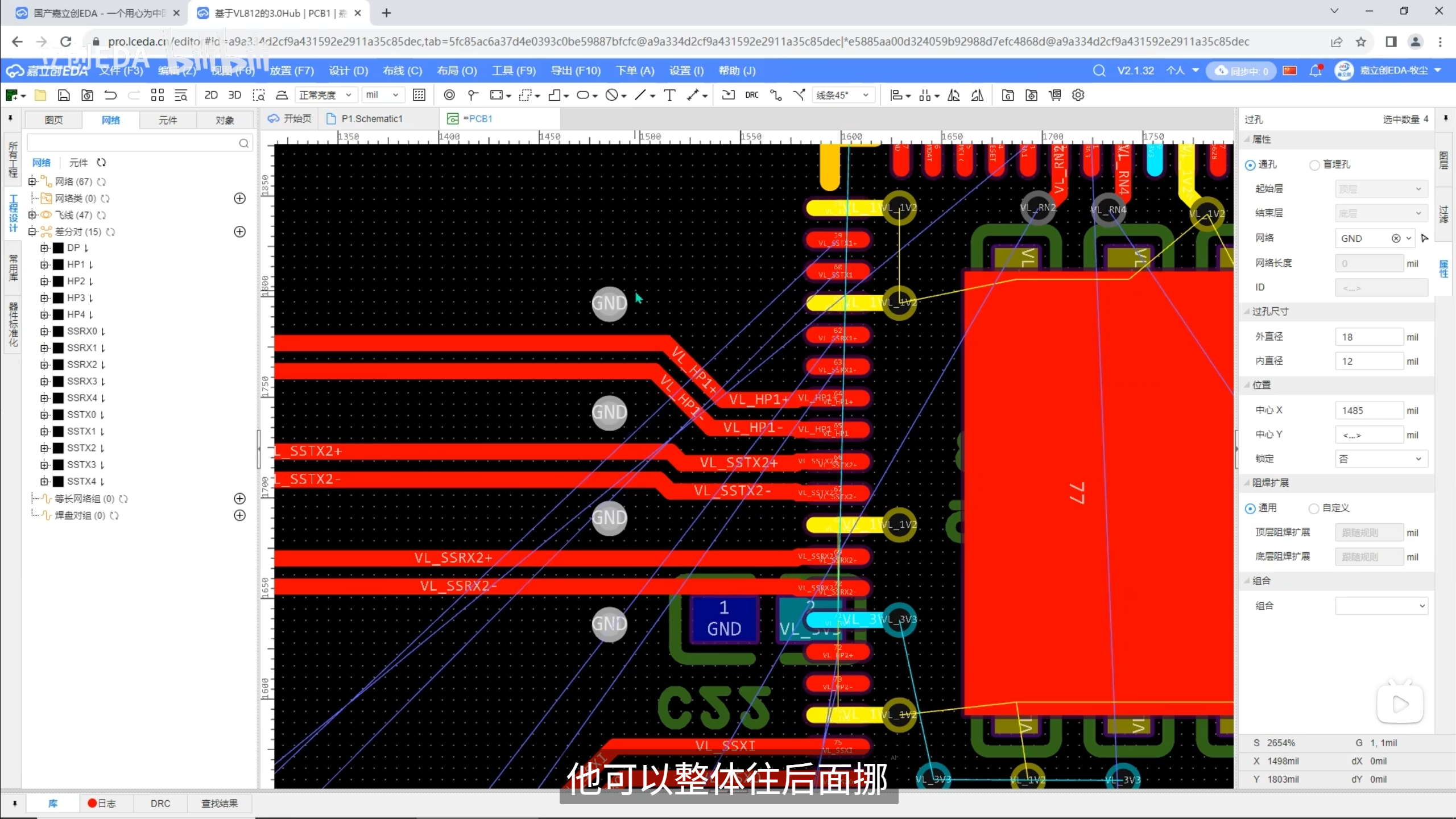

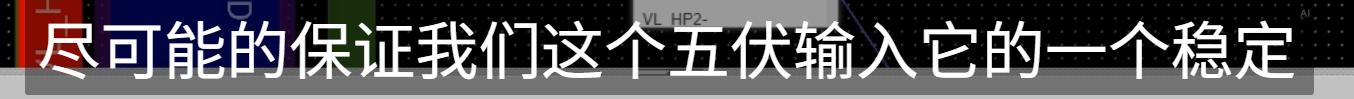

16. 内径12mil

内径12mil

外径大于16mil

17.

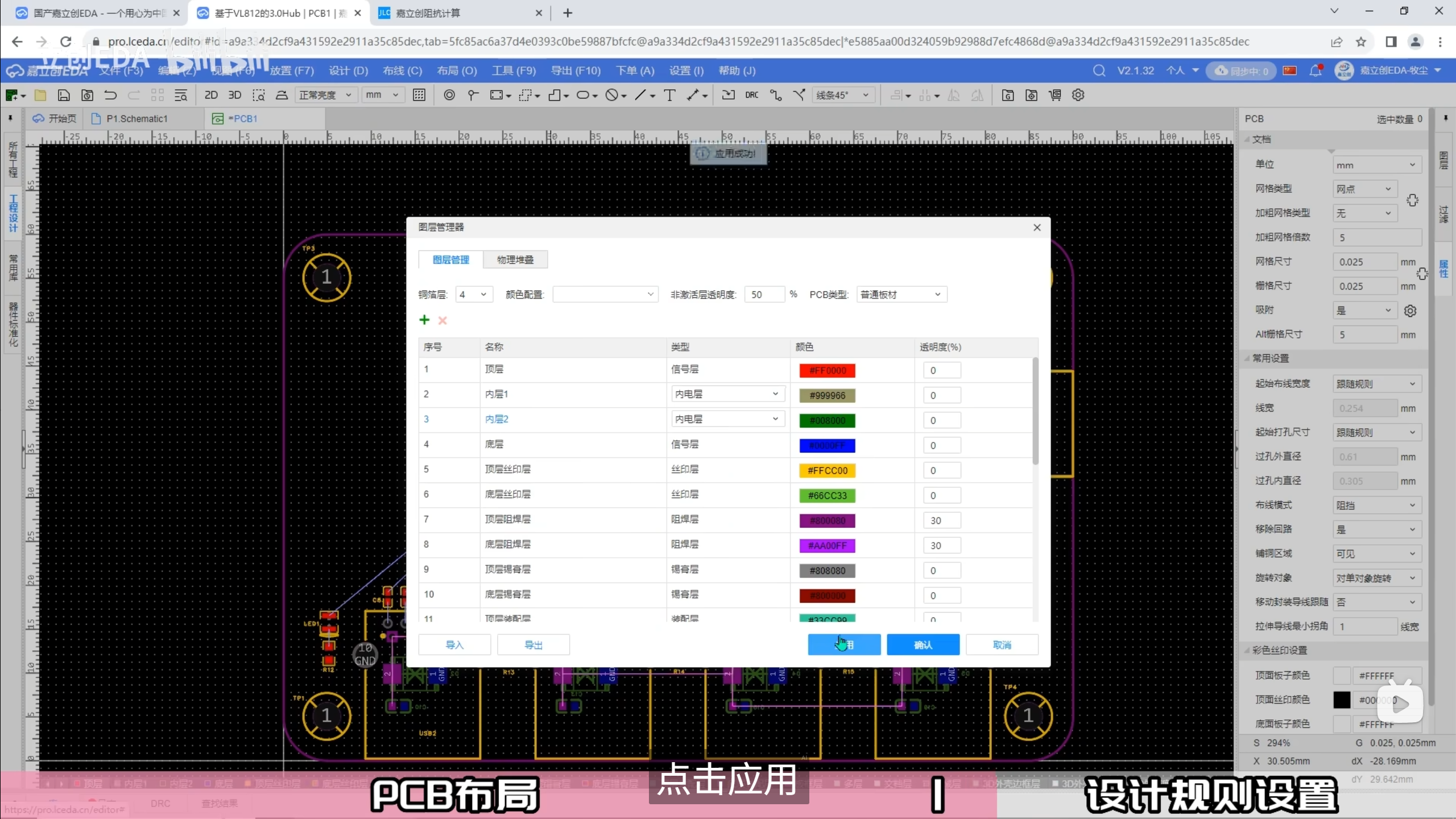

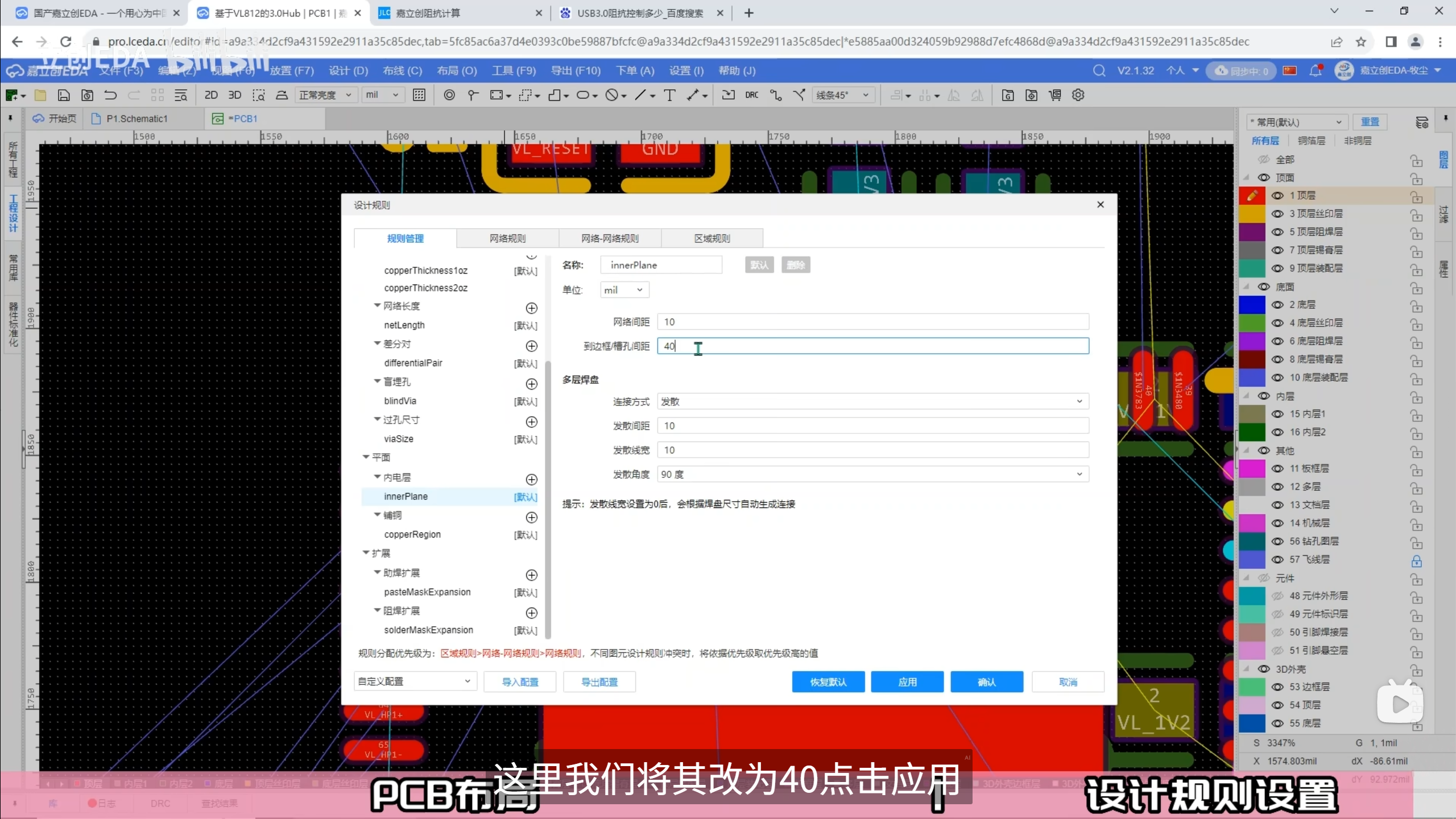

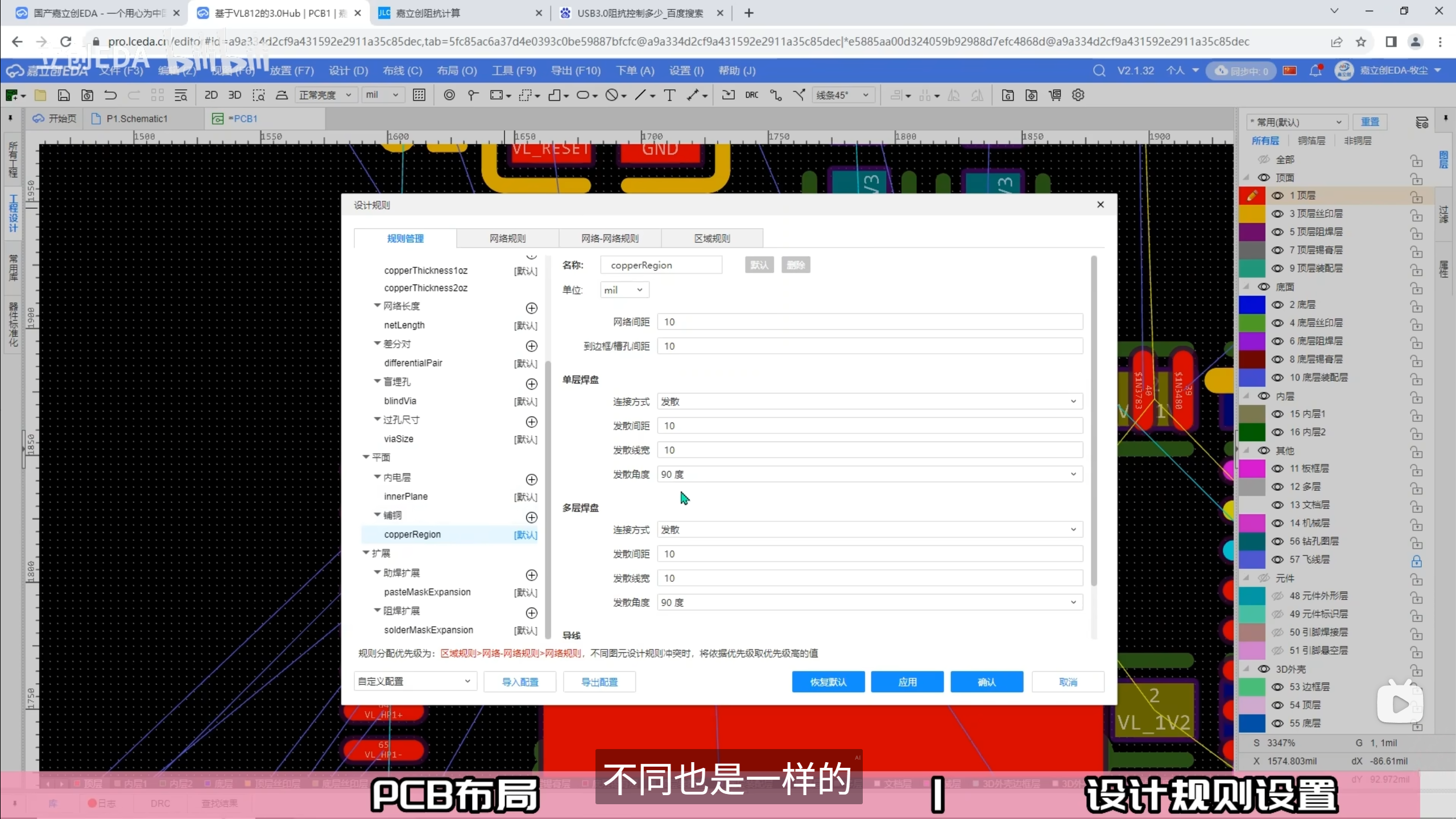

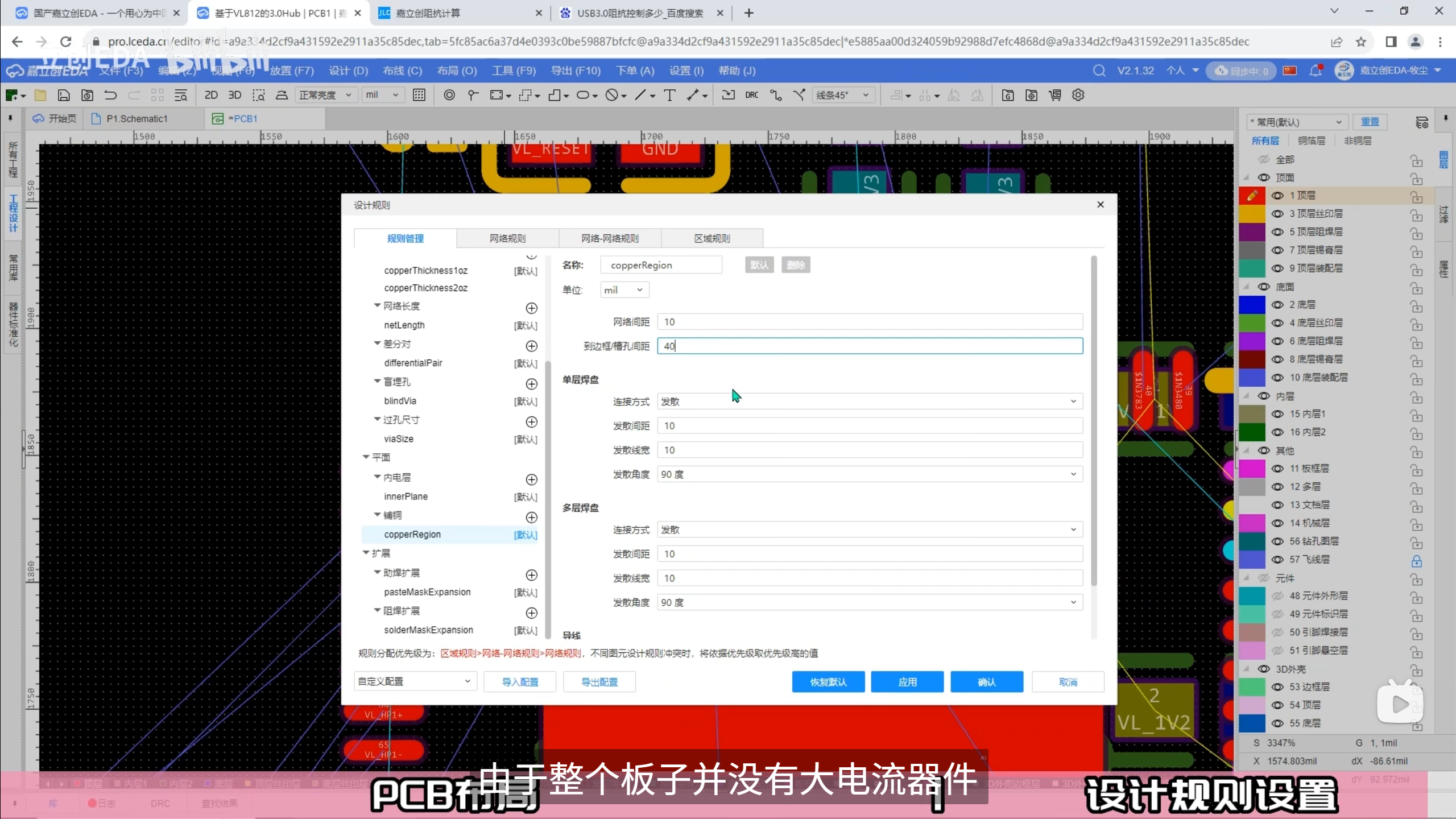

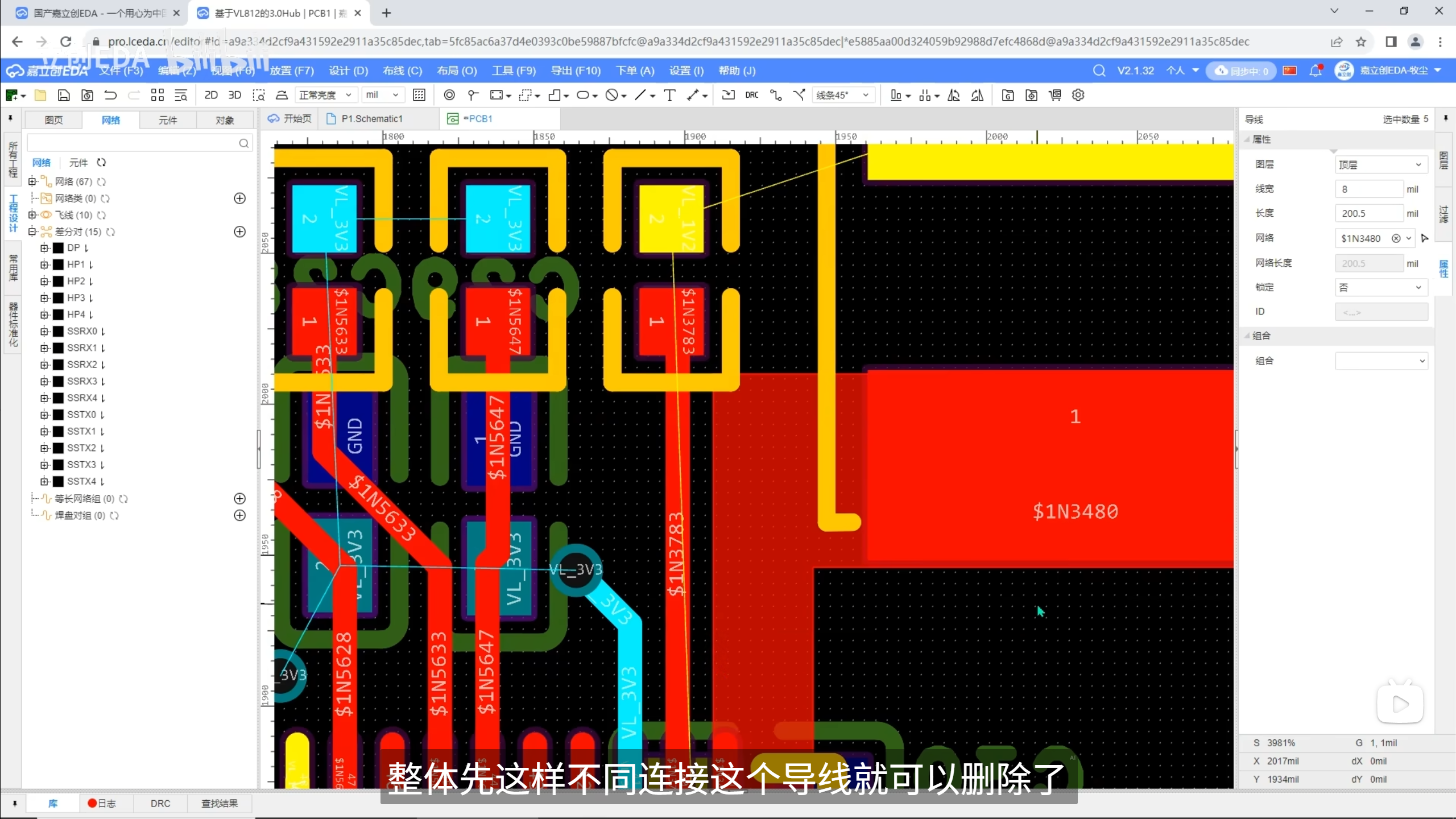

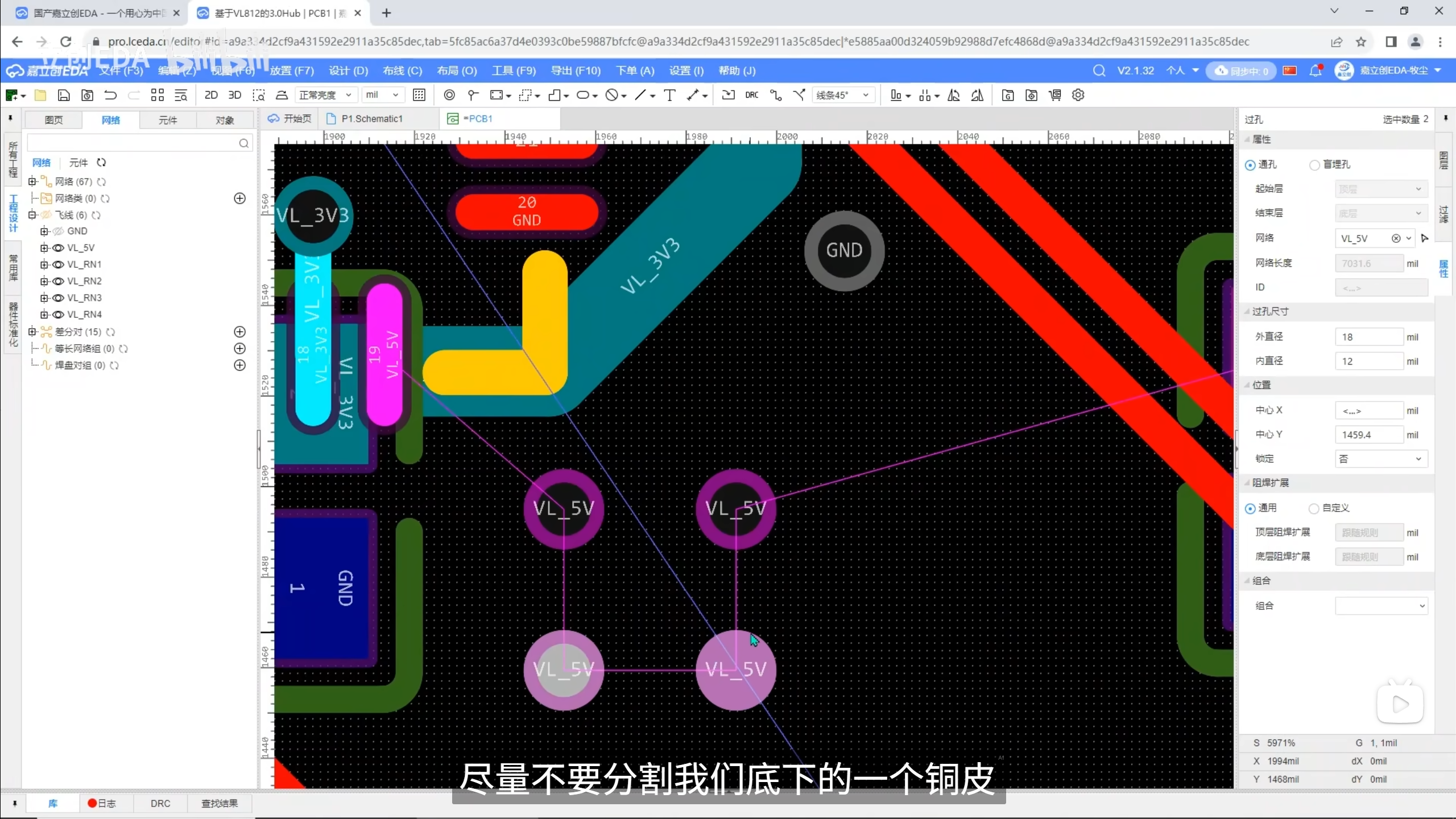

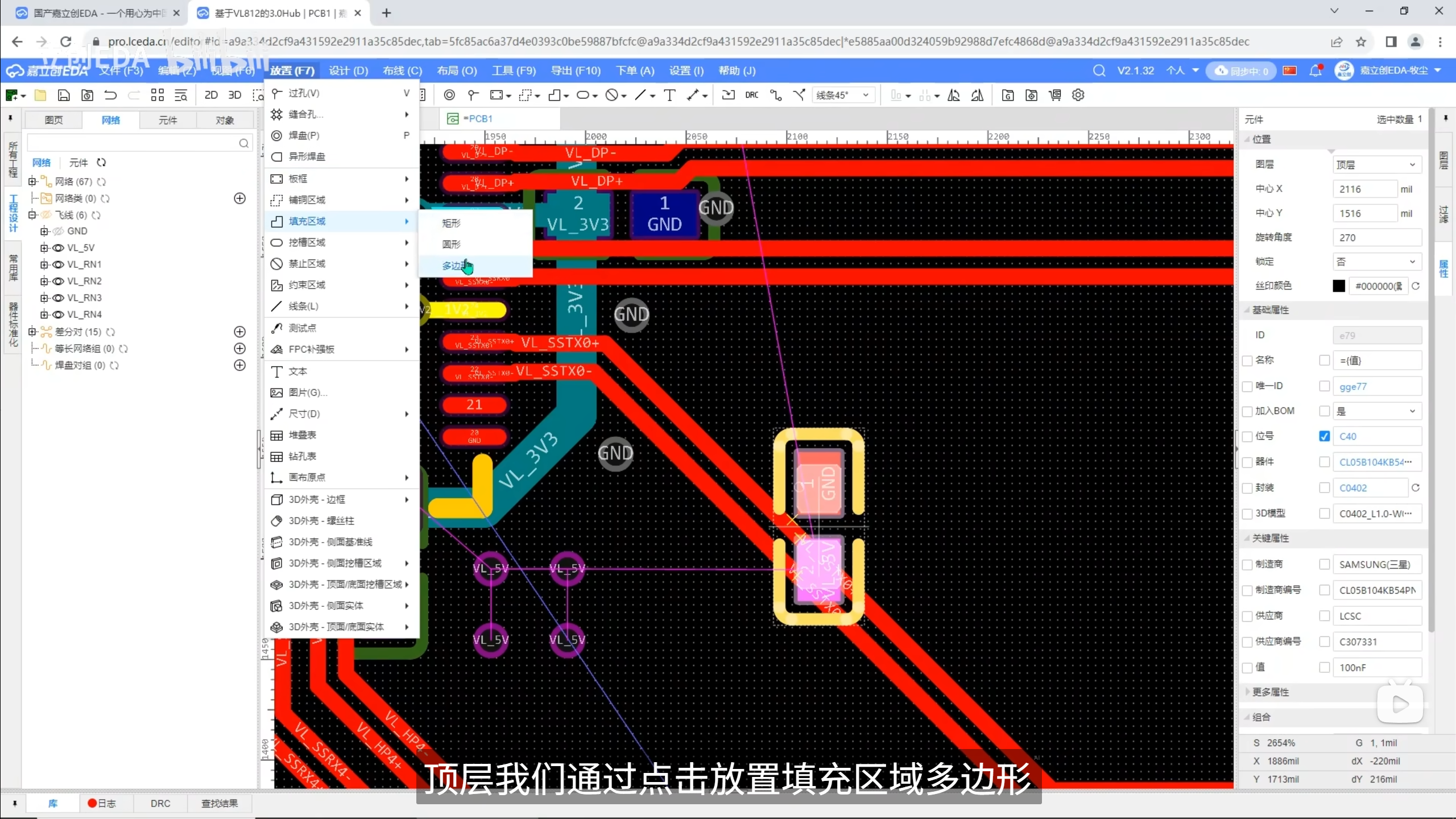

18.铺铜设置

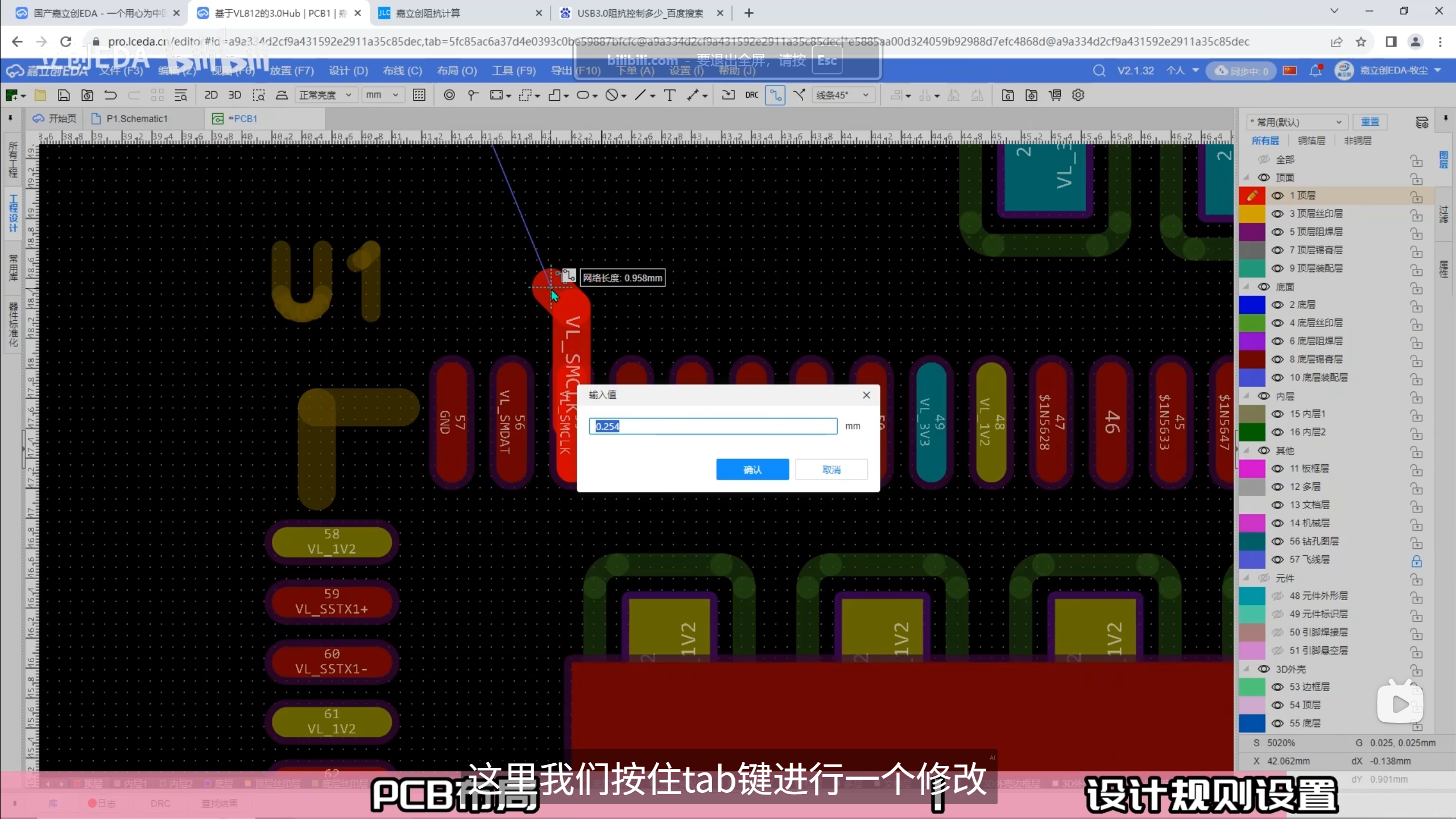

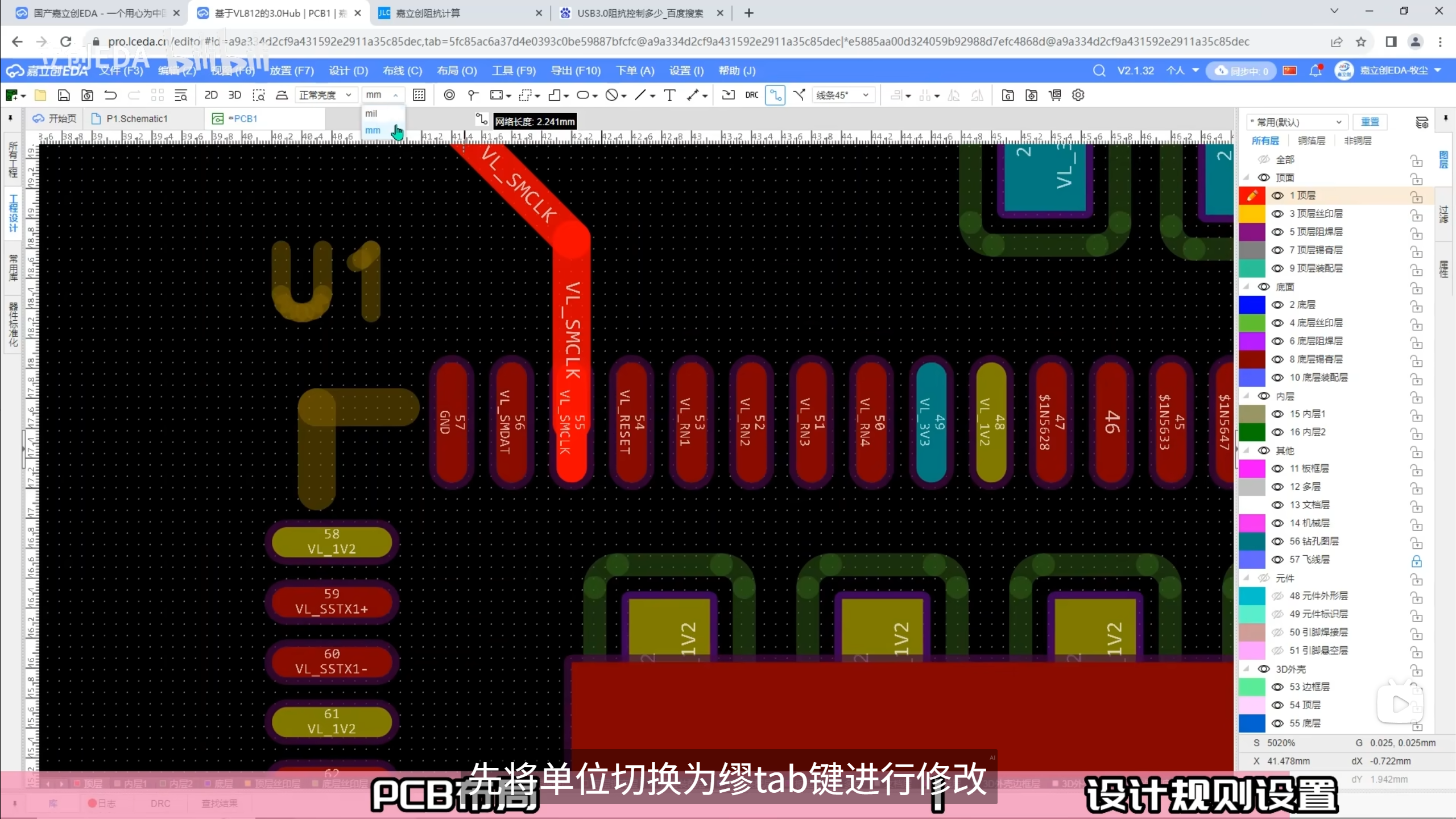

19.mil 和 mm 的进制关系为:

- 1 mil = 0.0254 mm

- 1 mm ≈ 39.37 mil

20.

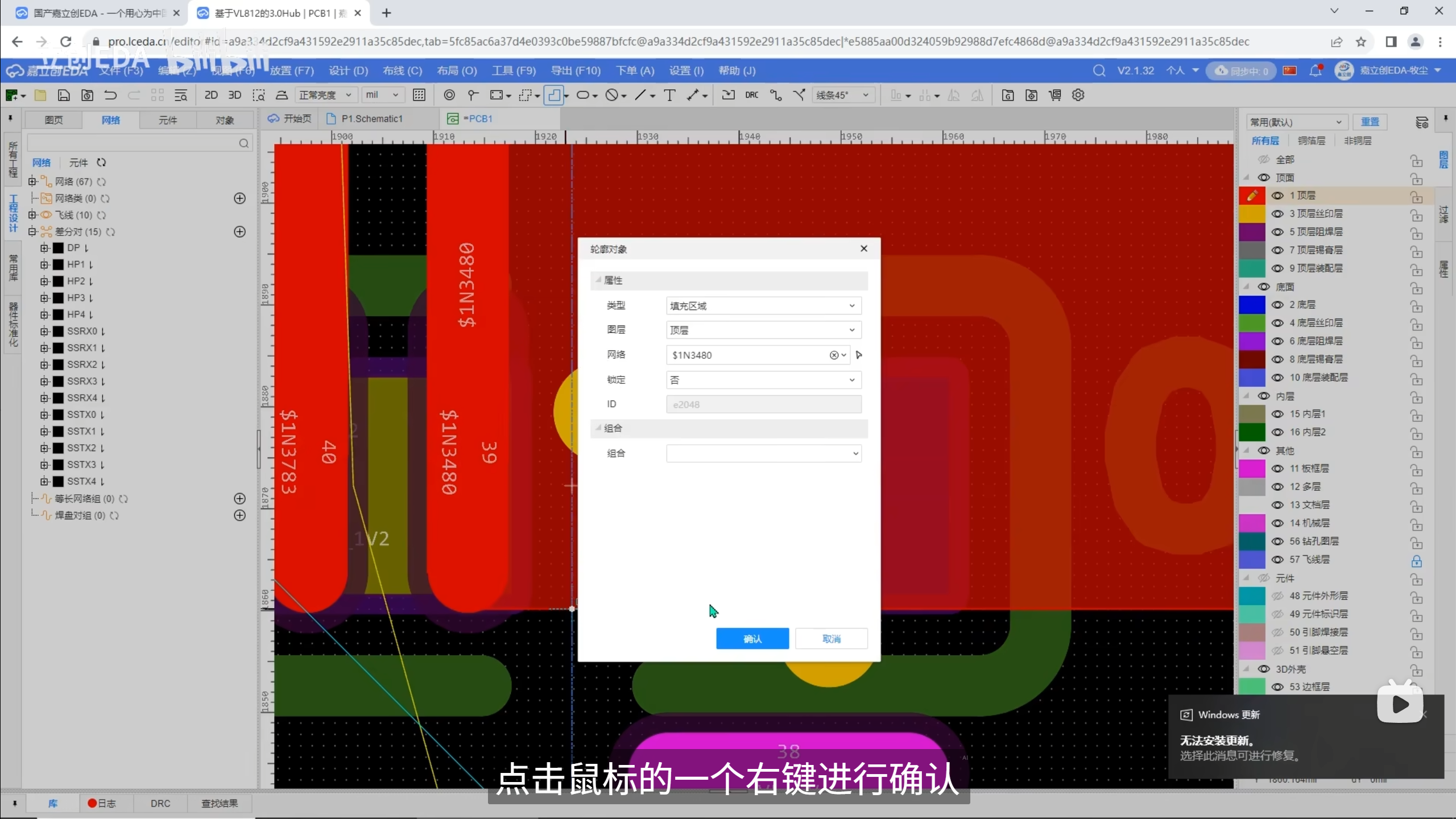

确认

21.

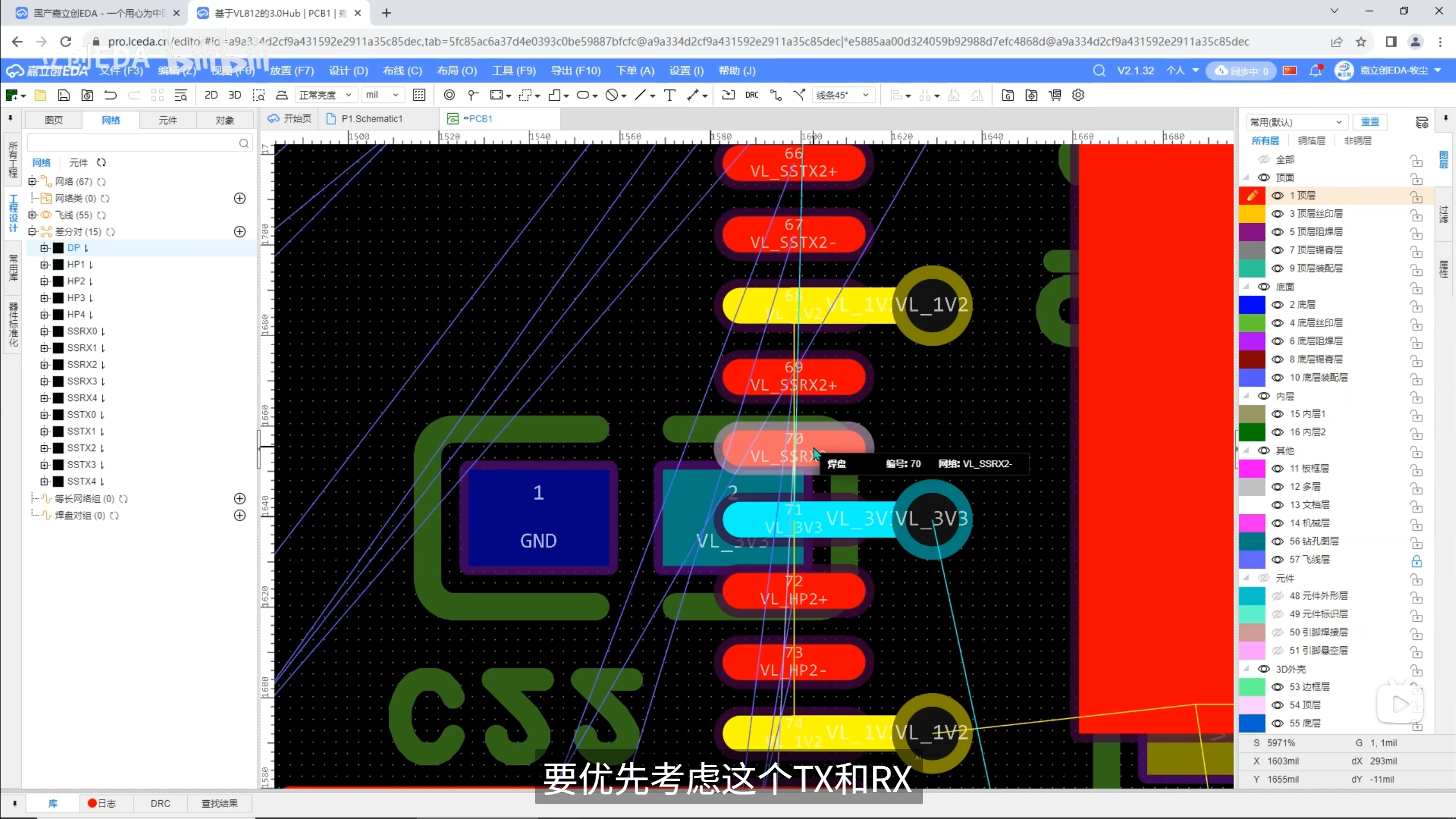

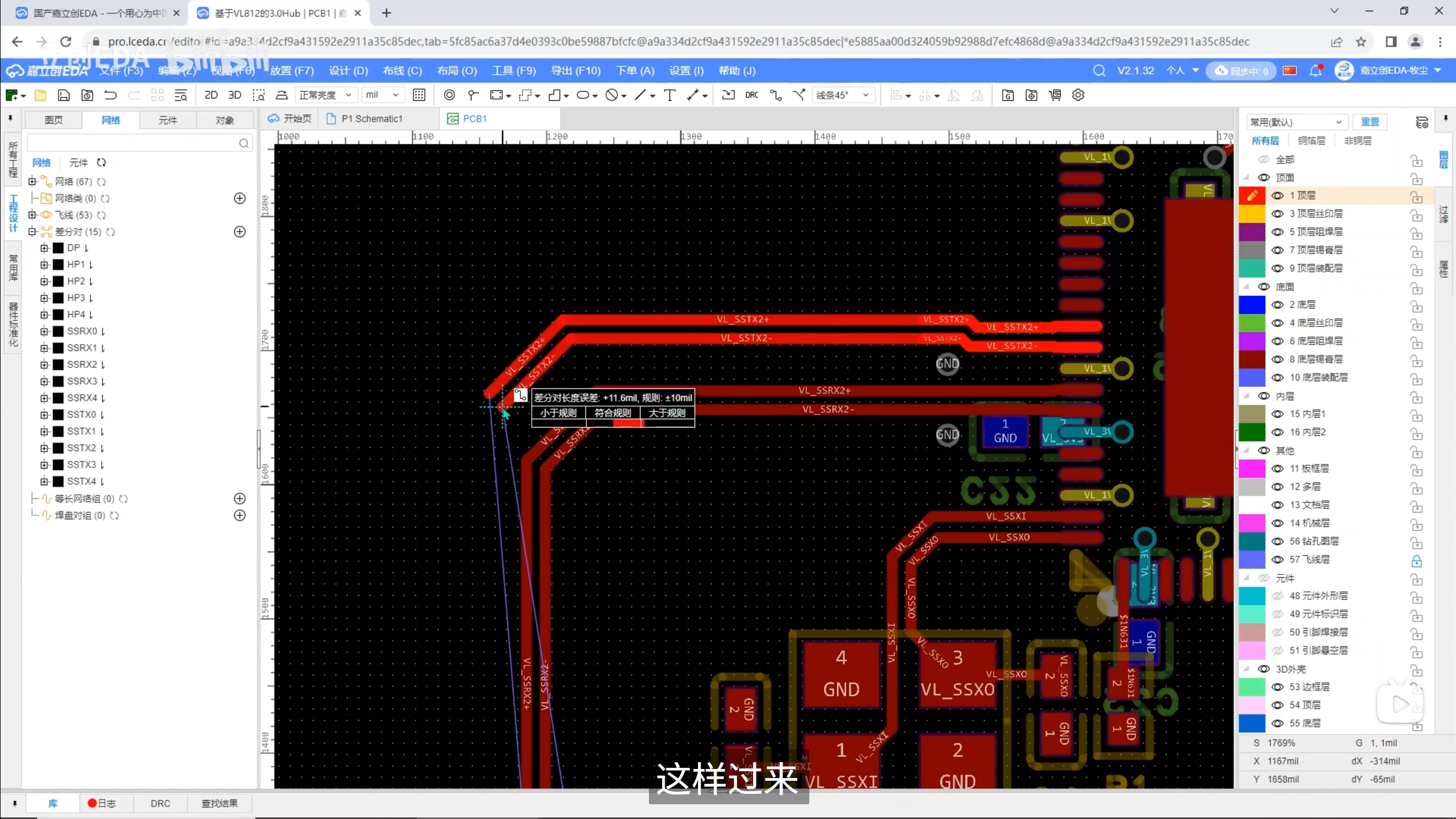

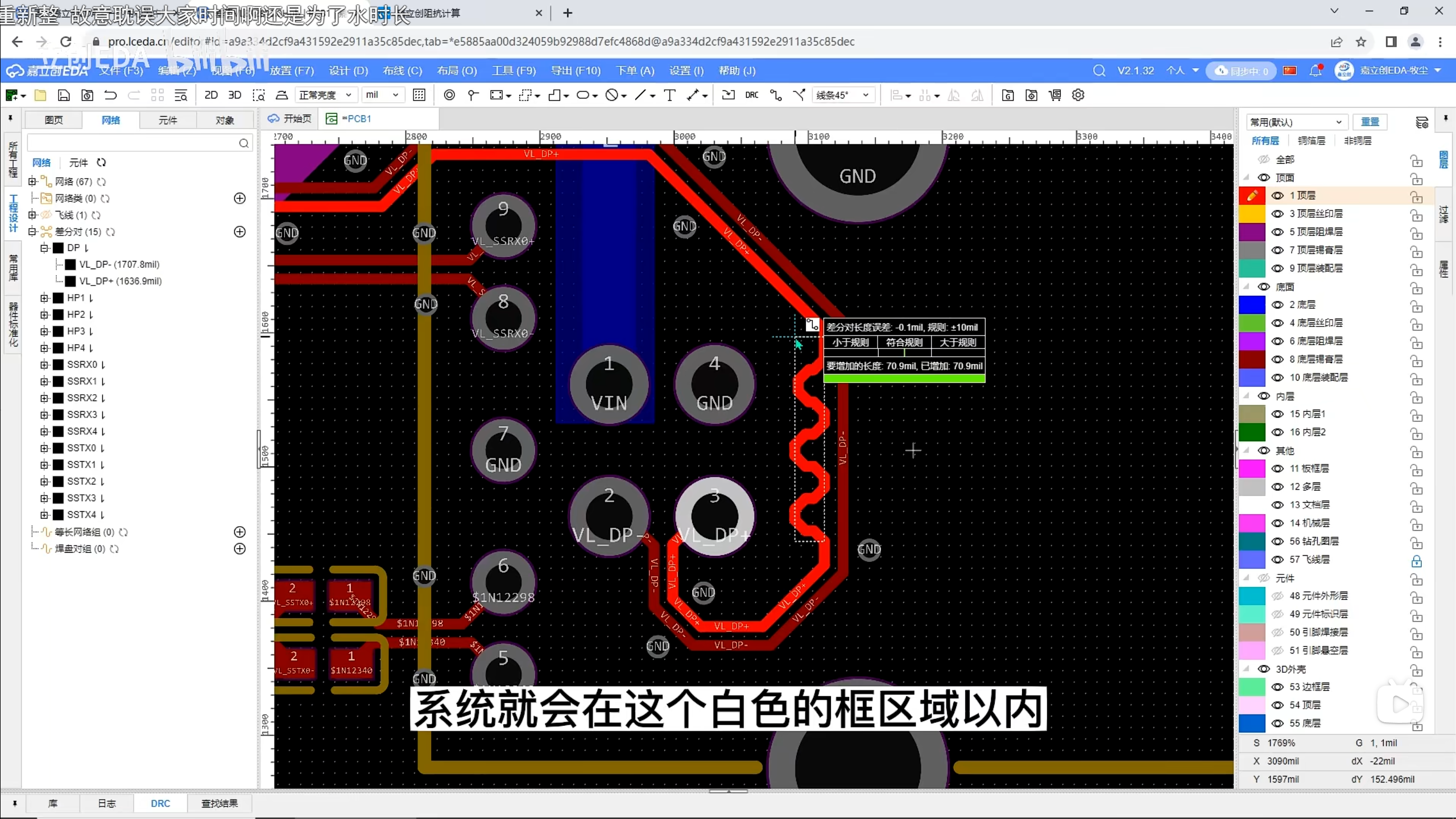

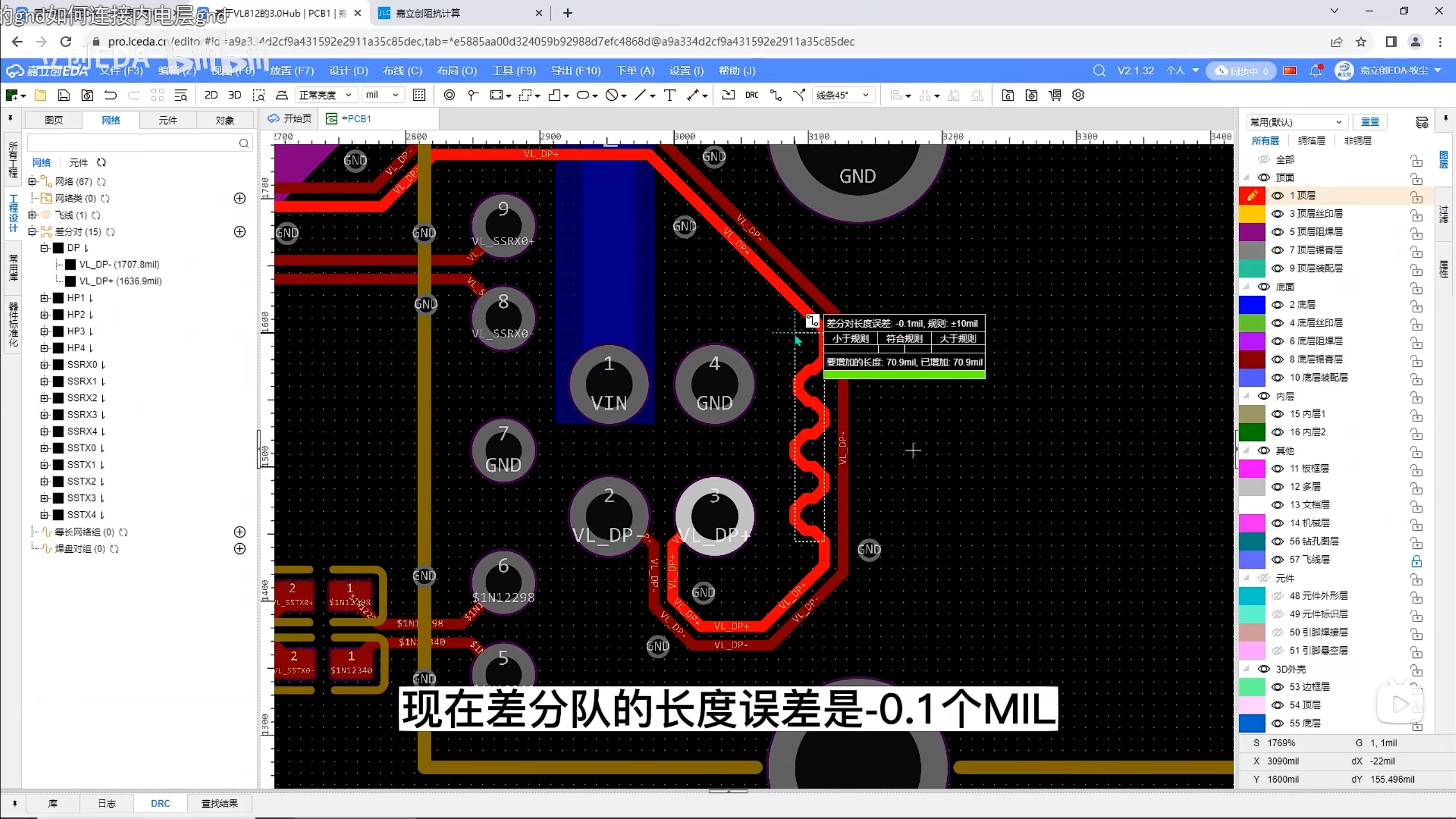

22.每隔150要有一个包地触点

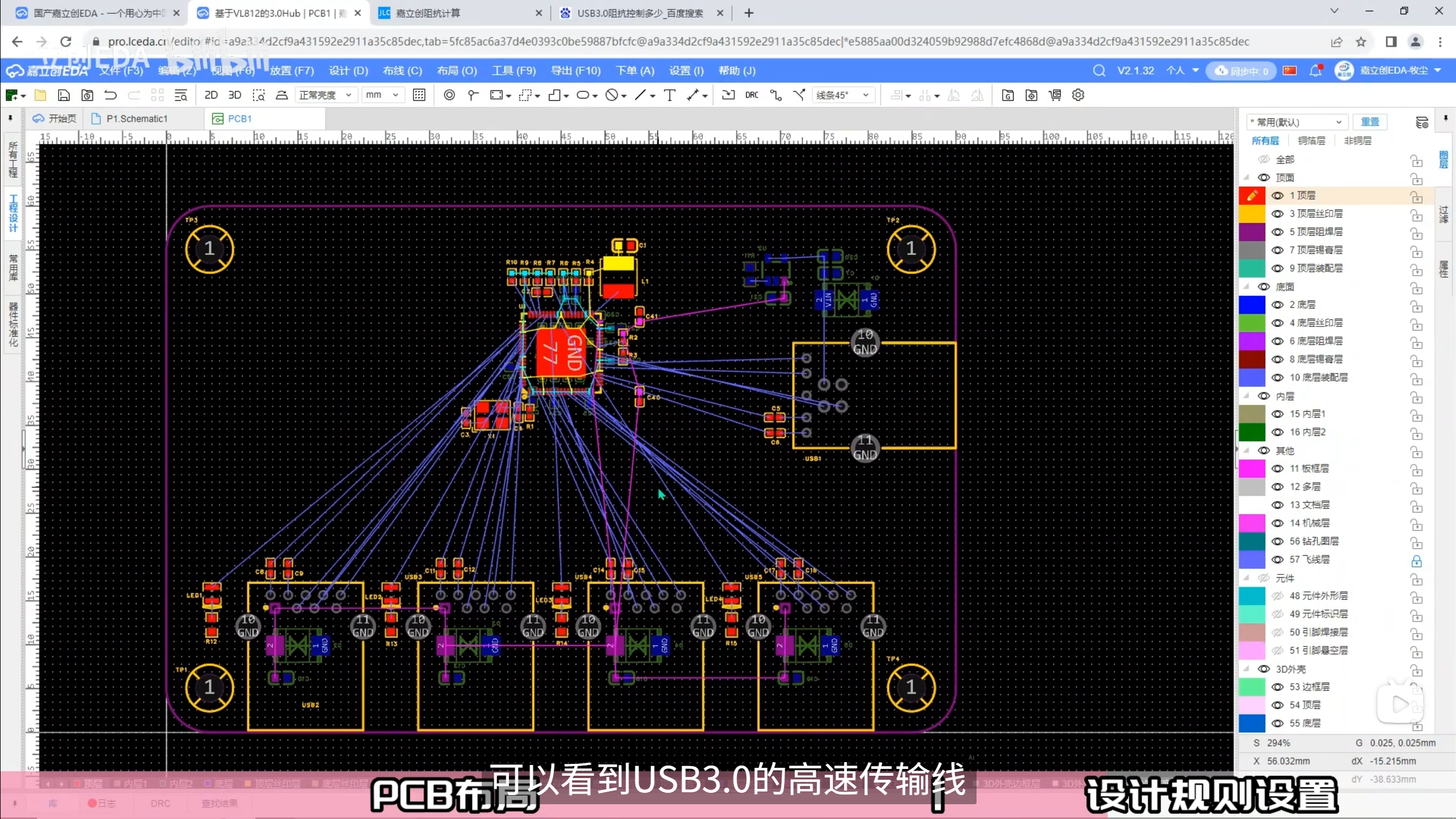

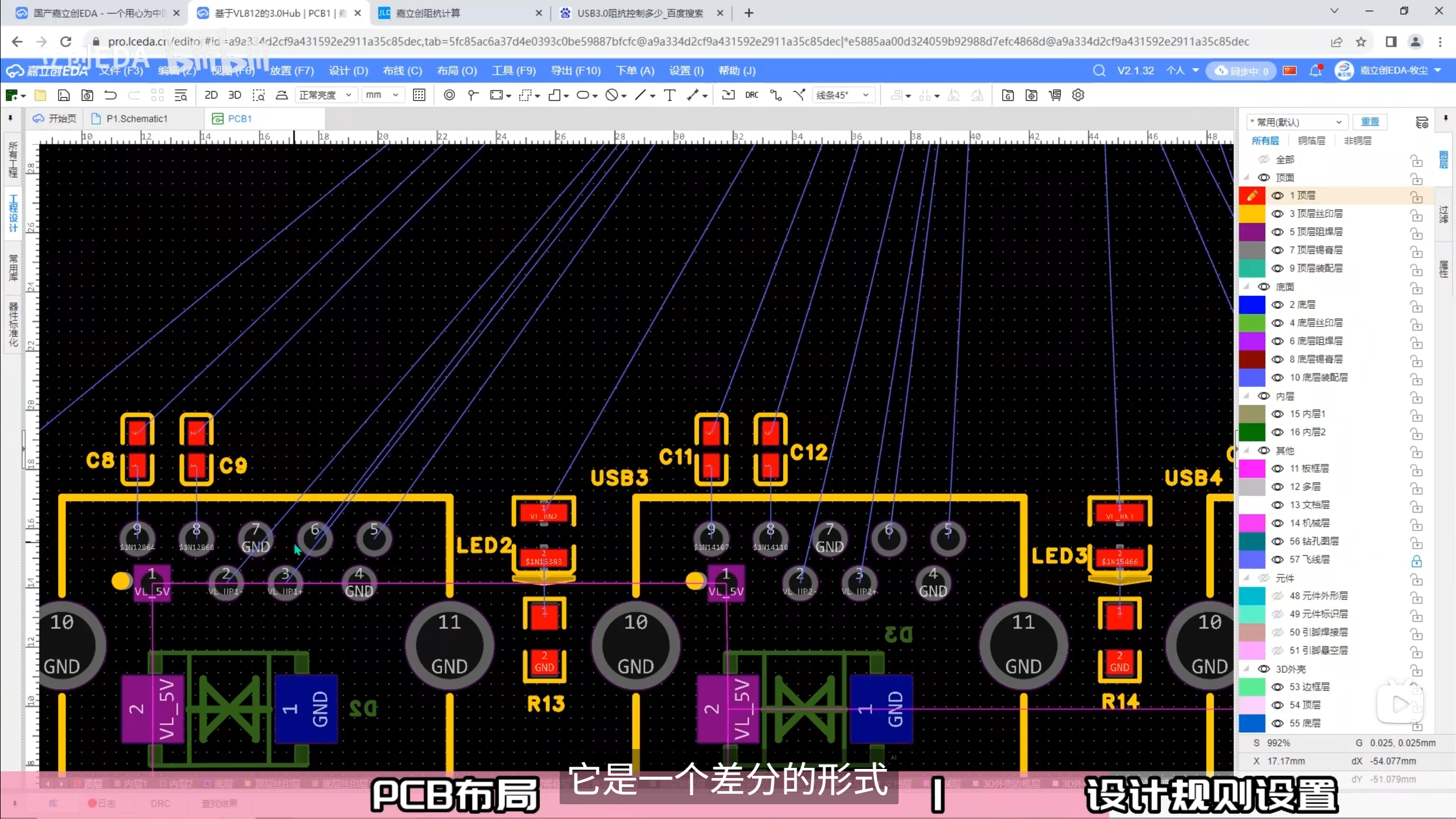

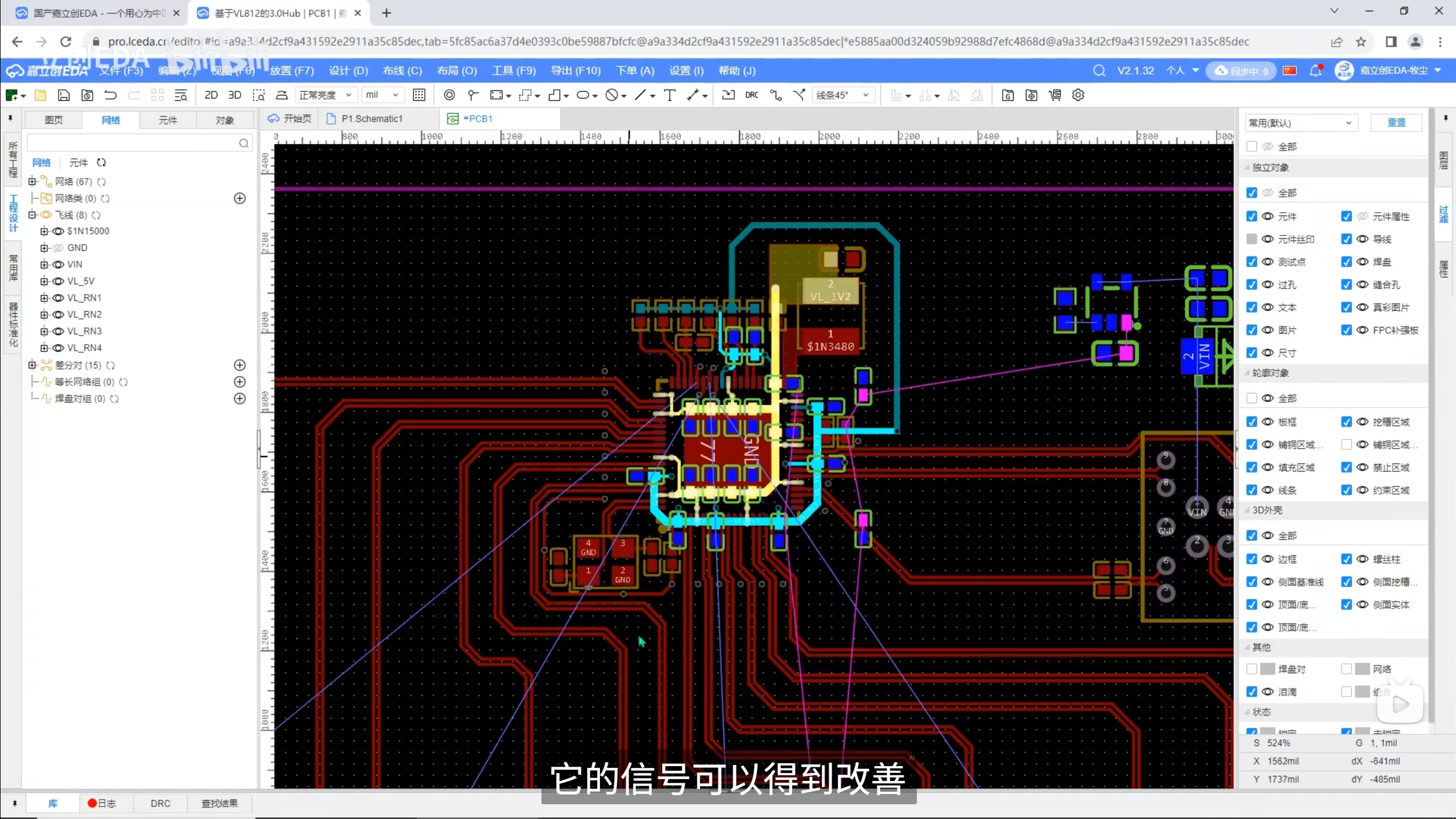

在差分线两侧并排放GND(接地),核心目的是屏蔽外部干扰和抑制自身信号辐射,同时保证差分信号的完整性。

差分线依靠两根线之间的信号差值传输信息,两侧的GND相当于“防护墙”:一是阻挡外部电磁干扰(EMI)侵入差分线,避免干扰信号叠加影响差值准确性;二是防止差分线自身的高频信号向外辐射,干扰其他电路。此外,GND还能为差分信号提供稳定的回流路径,减少信号延迟和串扰。

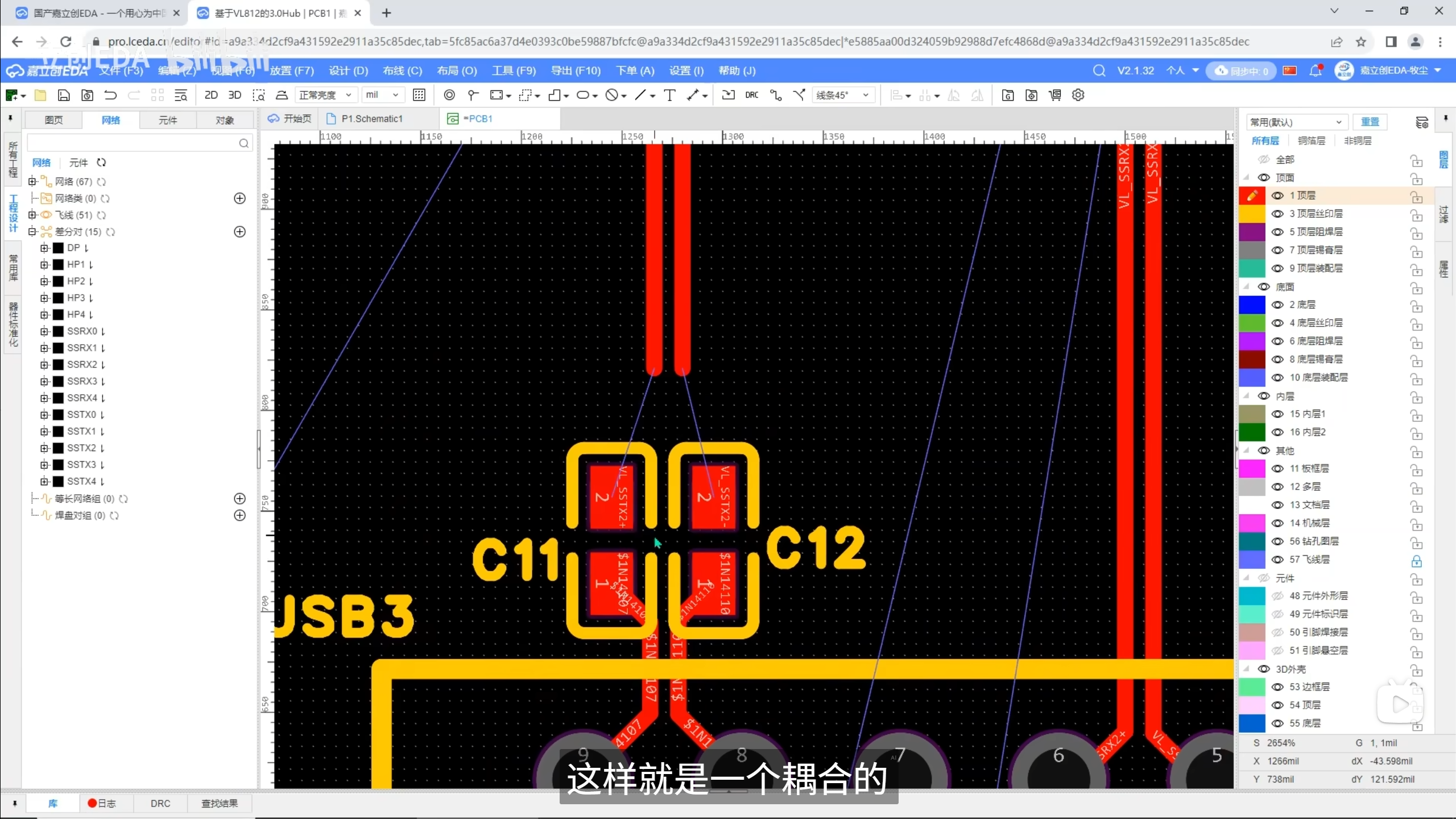

元器件靠近耦合间距和差分线差不多

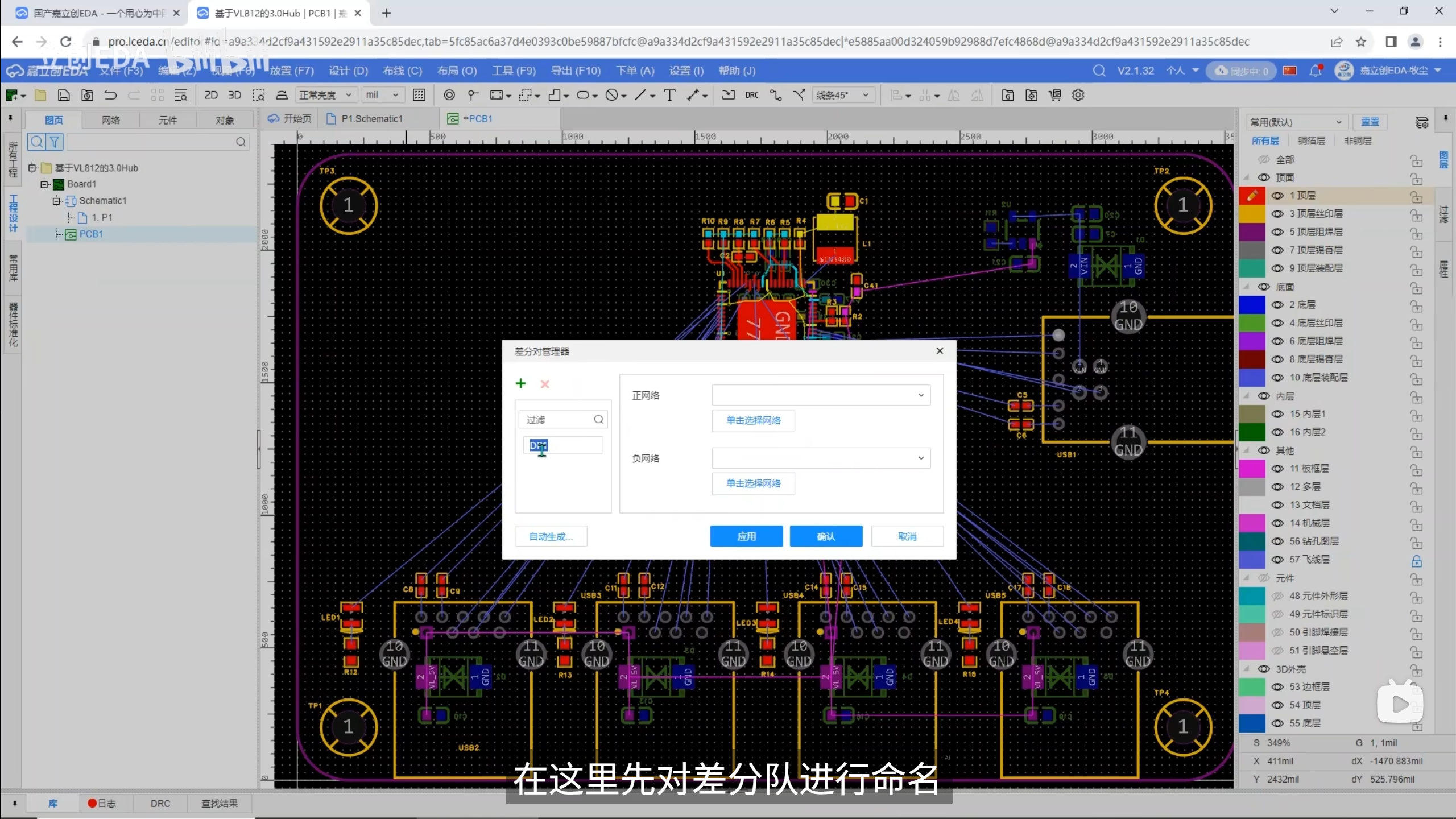

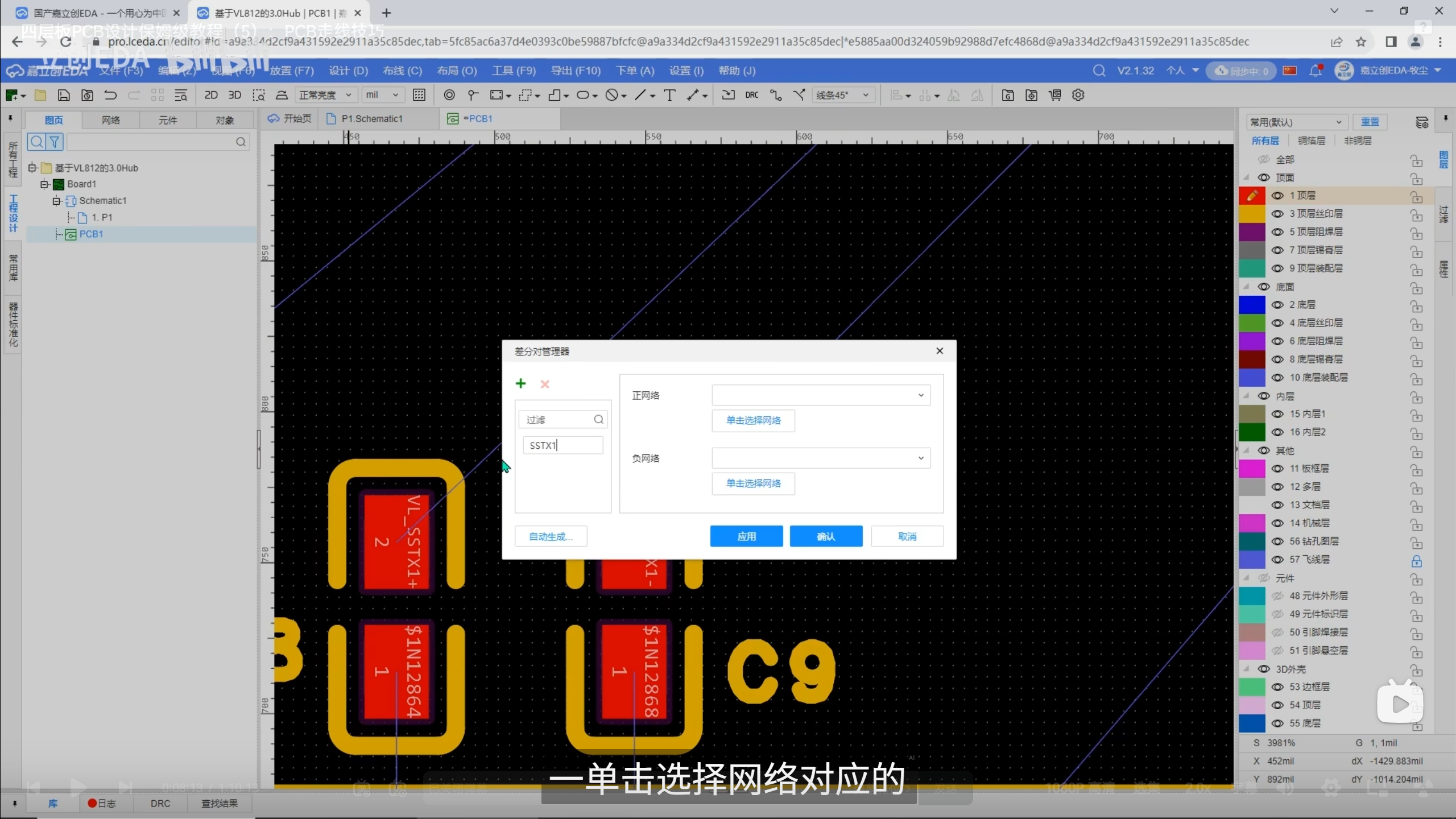

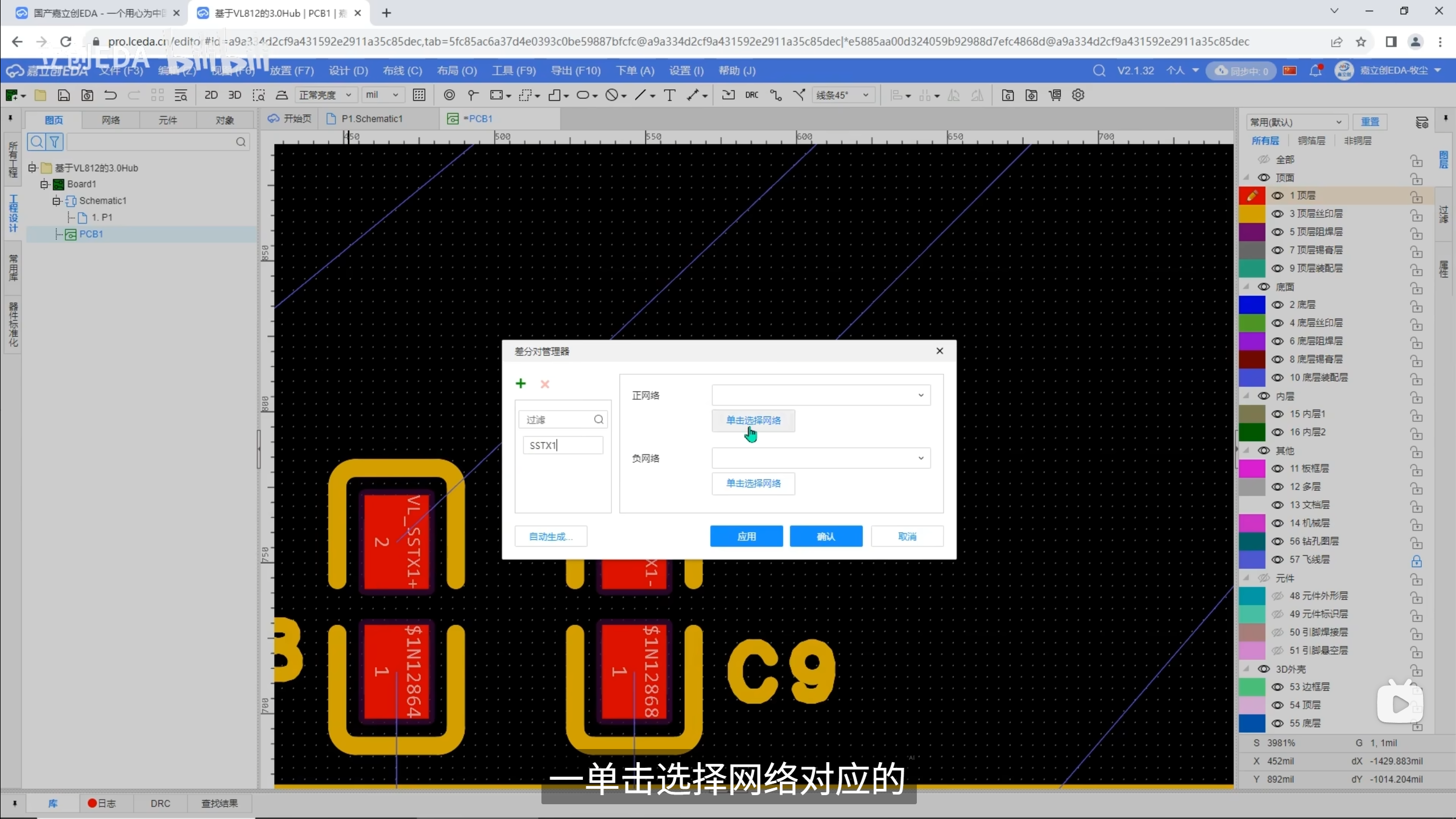

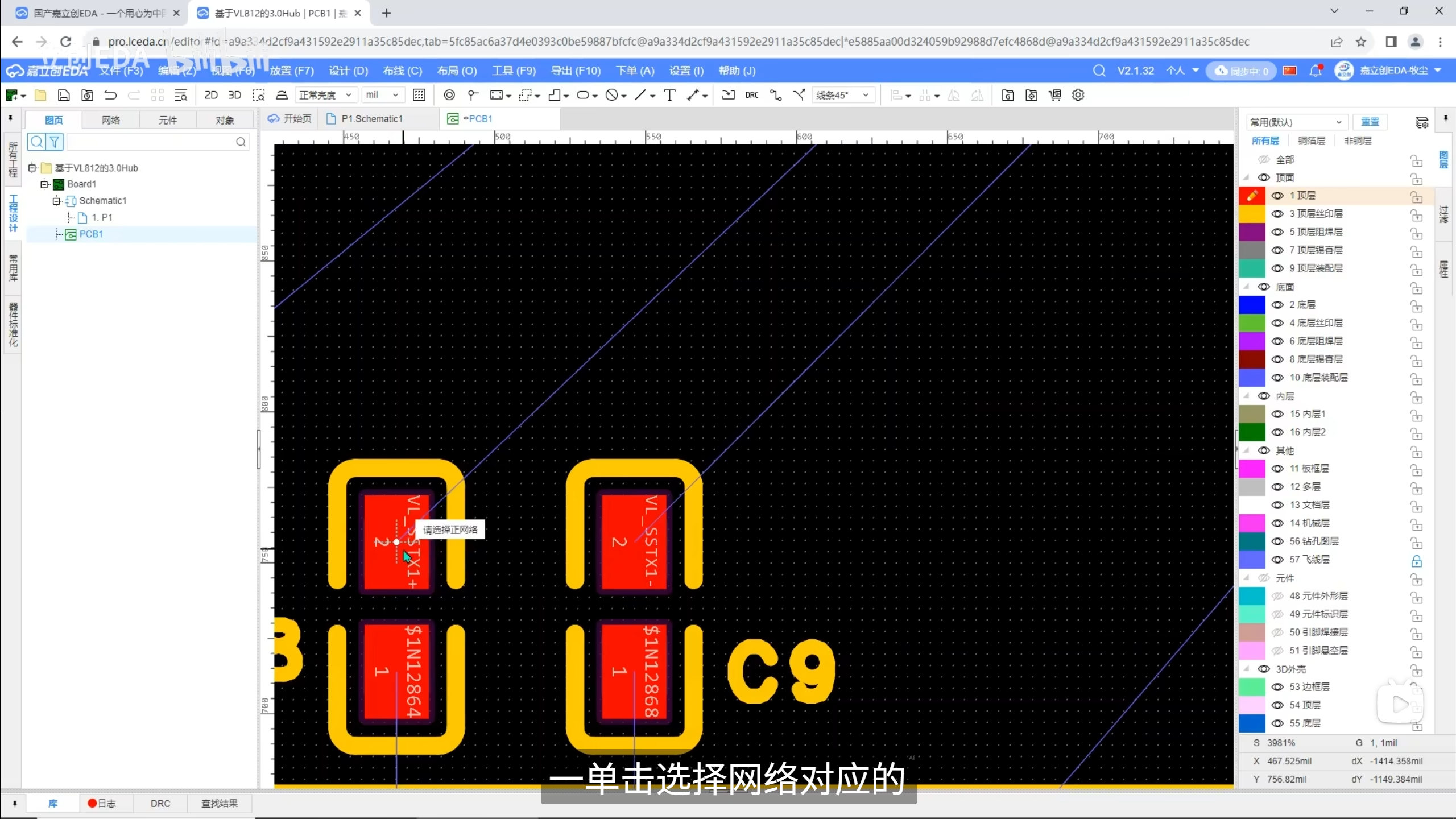

23.

24.

25.容易漏锡

26.

27.

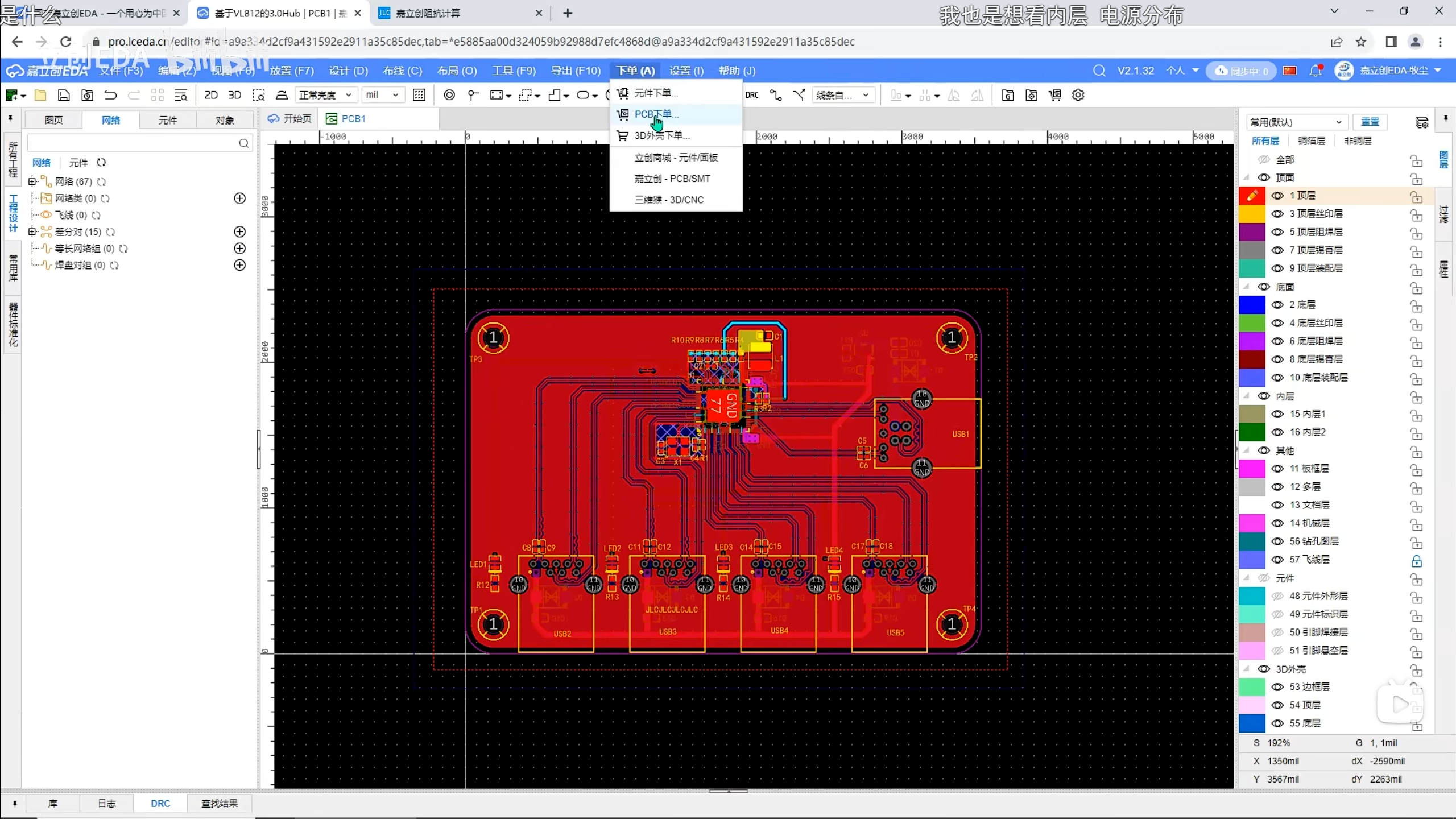

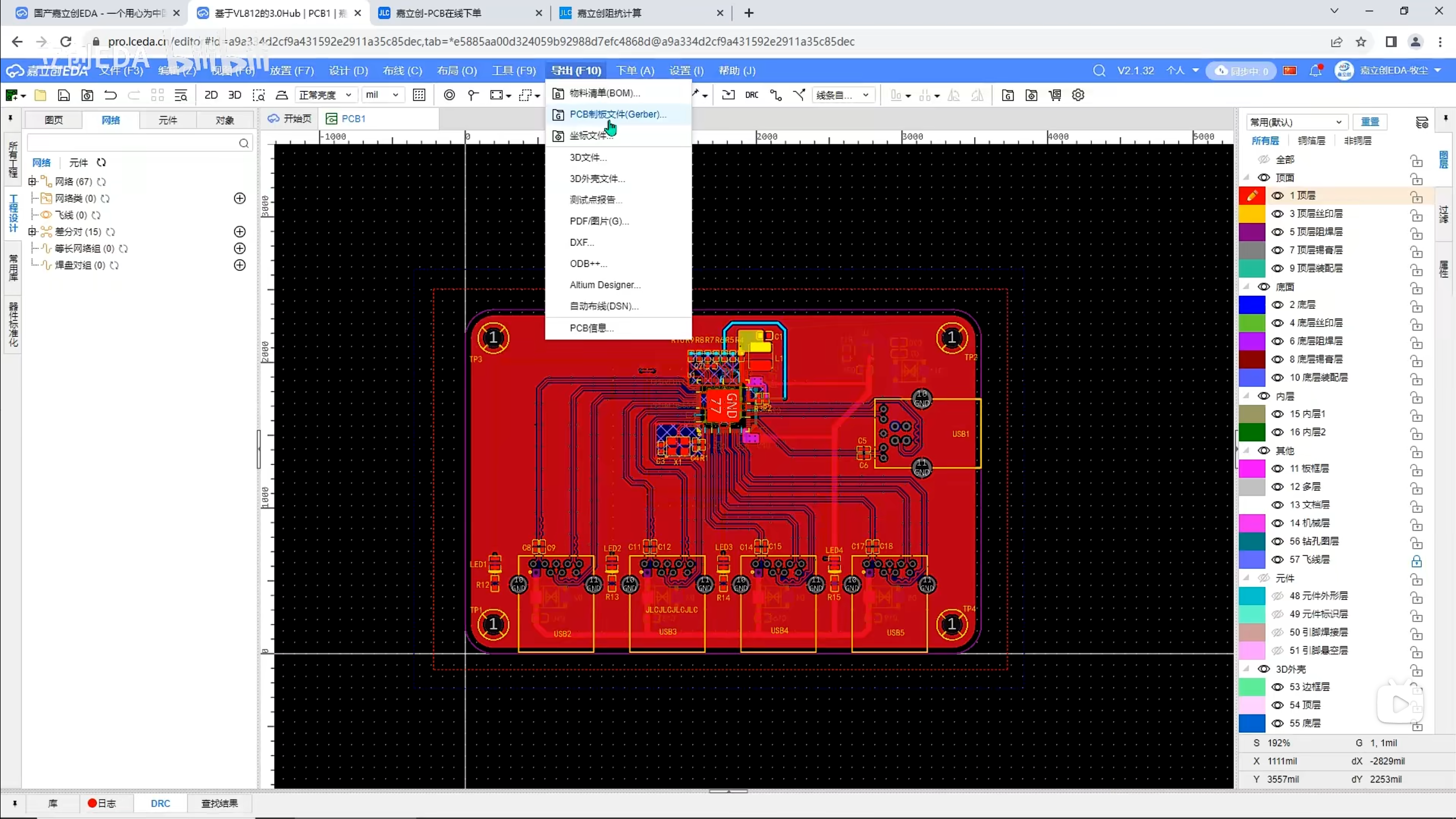

28.隐藏丝印

29.

30.

31.

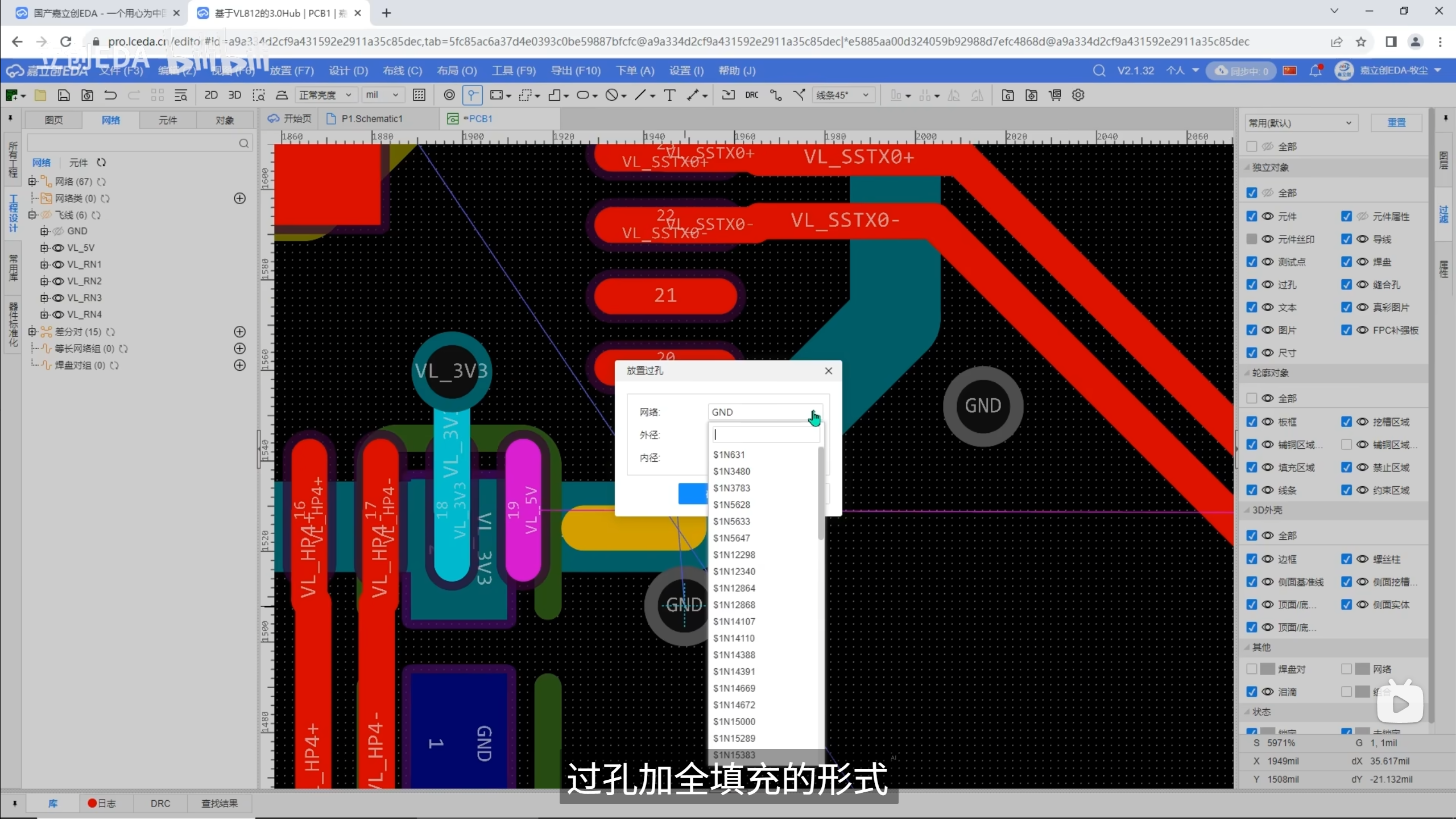

32.过孔

33.

34.

双层板并非完全不能阻抗或抵抗干扰,只是能力弱于多层板。

它通过顶层和底层的铜箔布线形成一定的信号回路,可实现基础的阻抗控制和干扰抵抗,但缺乏专门的接地层和电源层来高效屏蔽、滤波,面对高频信号或复杂电磁环境时,抗干扰能力明显不足。

35.

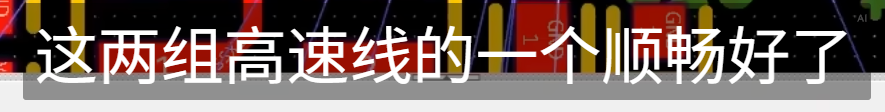

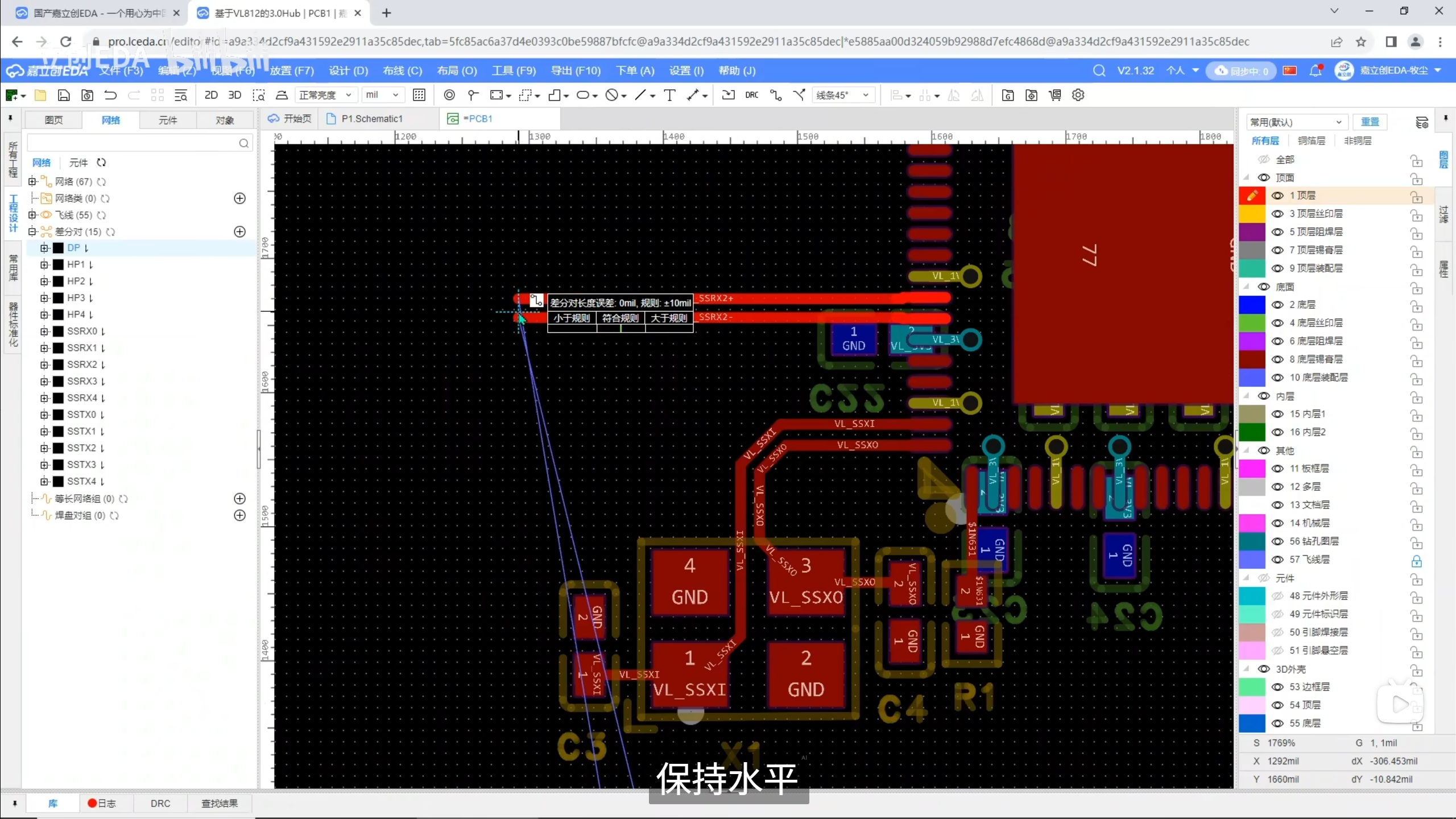

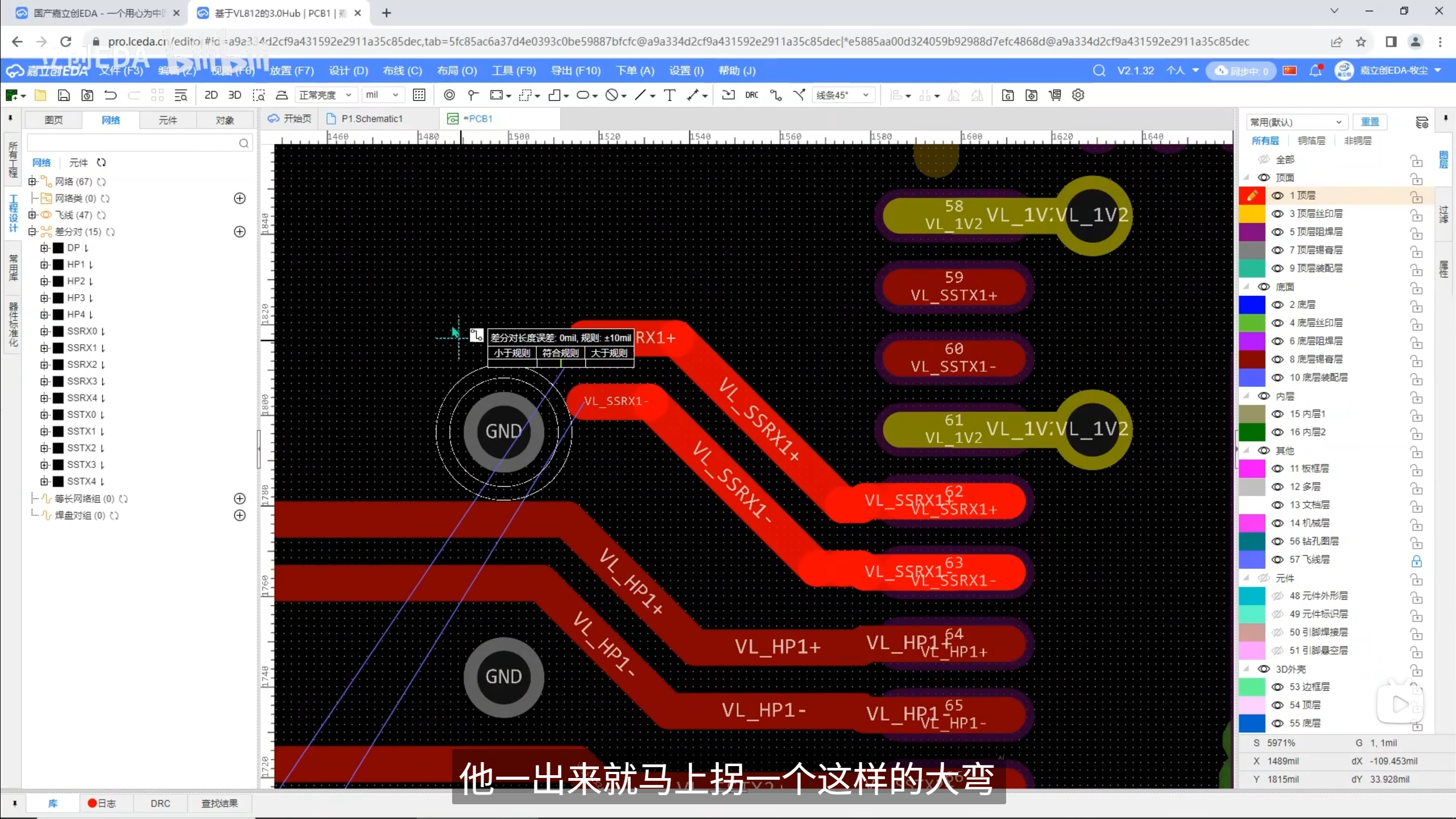

在 PCB(印刷电路板)设计中,走线最好不要采用锐角(通常指小于 90° 的角,尤其是锐角和直角的尖锐部分),主要有以下几方面原因:

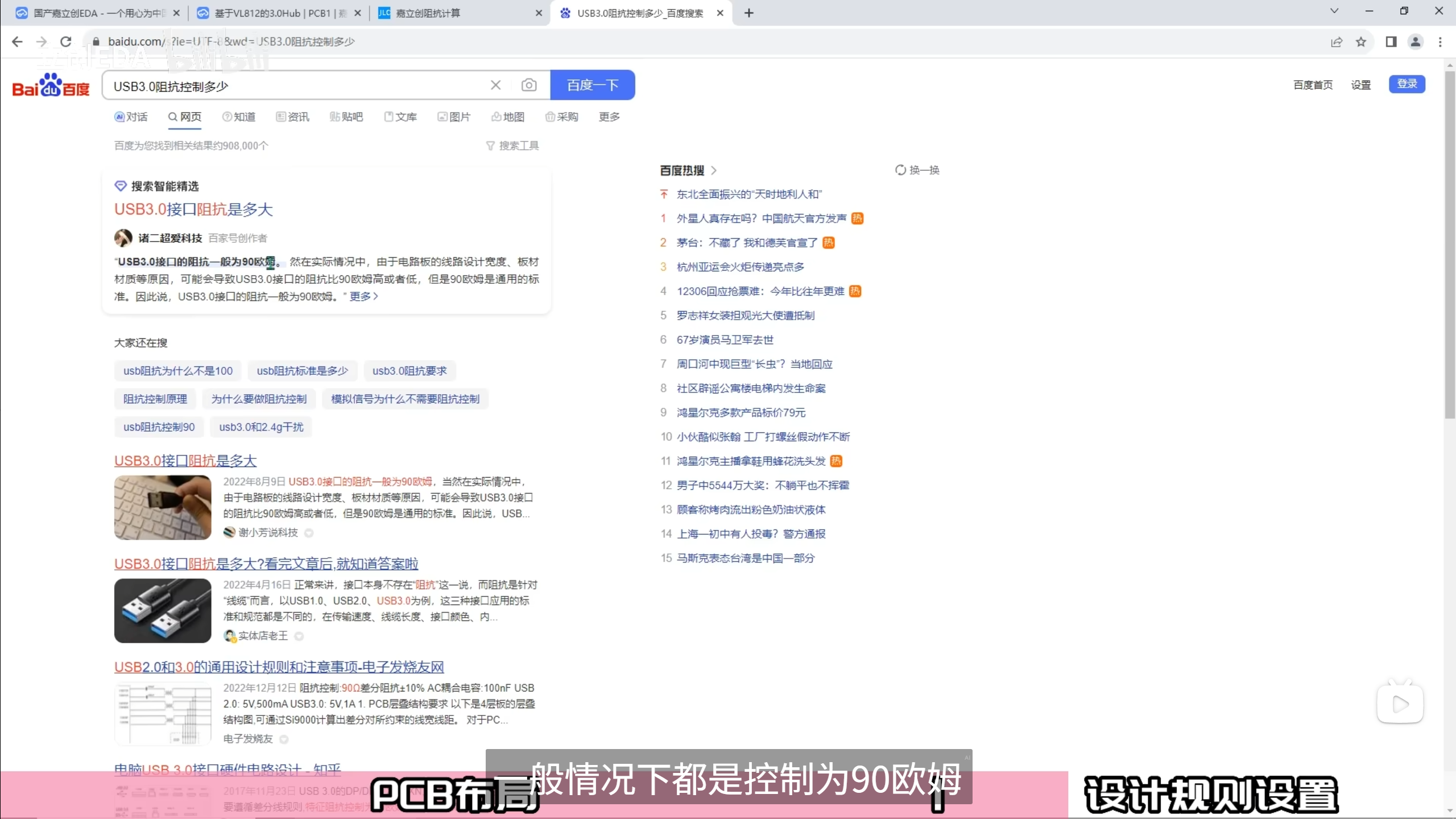

1. 信号完整性问题

高频信号在 PCB 走线上传输时,会存在阻抗不连续的问题。锐角走线的几何形状突变,会导致信号的反射、散射增加,从而影响信号的完整性,可能引发信号失真、时序错误等问题,尤其对于高速信号(如 USB 3.0、高速串行总线等)影响更为明显。

2. 制造工艺限制

- 蚀刻不均:在 PCB 的蚀刻工艺中,锐角处的铜箔容易出现过度蚀刻或蚀刻不足的情况。过度蚀刻会使走线变窄,阻抗增大;蚀刻不足则可能导致走线之间的间距变小,增加短路风险。

- 阻焊层覆盖问题:锐角处的阻焊层(绿油等)容易出现厚度不均或覆盖不完整的情况,影响 PCB 的绝缘性能和可靠性。

3. 电磁干扰(EMI)

锐角走线会产生额外的电磁辐射,同时也更容易接收外界的电磁干扰,从而增加 PCB 的电磁兼容性(EMC)问题,可能导致系统的稳定性下降。

4. 机械应力问题

在 PCB 的加工、组装和使用过程中,锐角处容易产生应力集中。例如,在焊接、热胀冷缩等情况下,锐角处的铜箔更容易出现断裂、翘起等故障,影响 PCB 的机械可靠性。

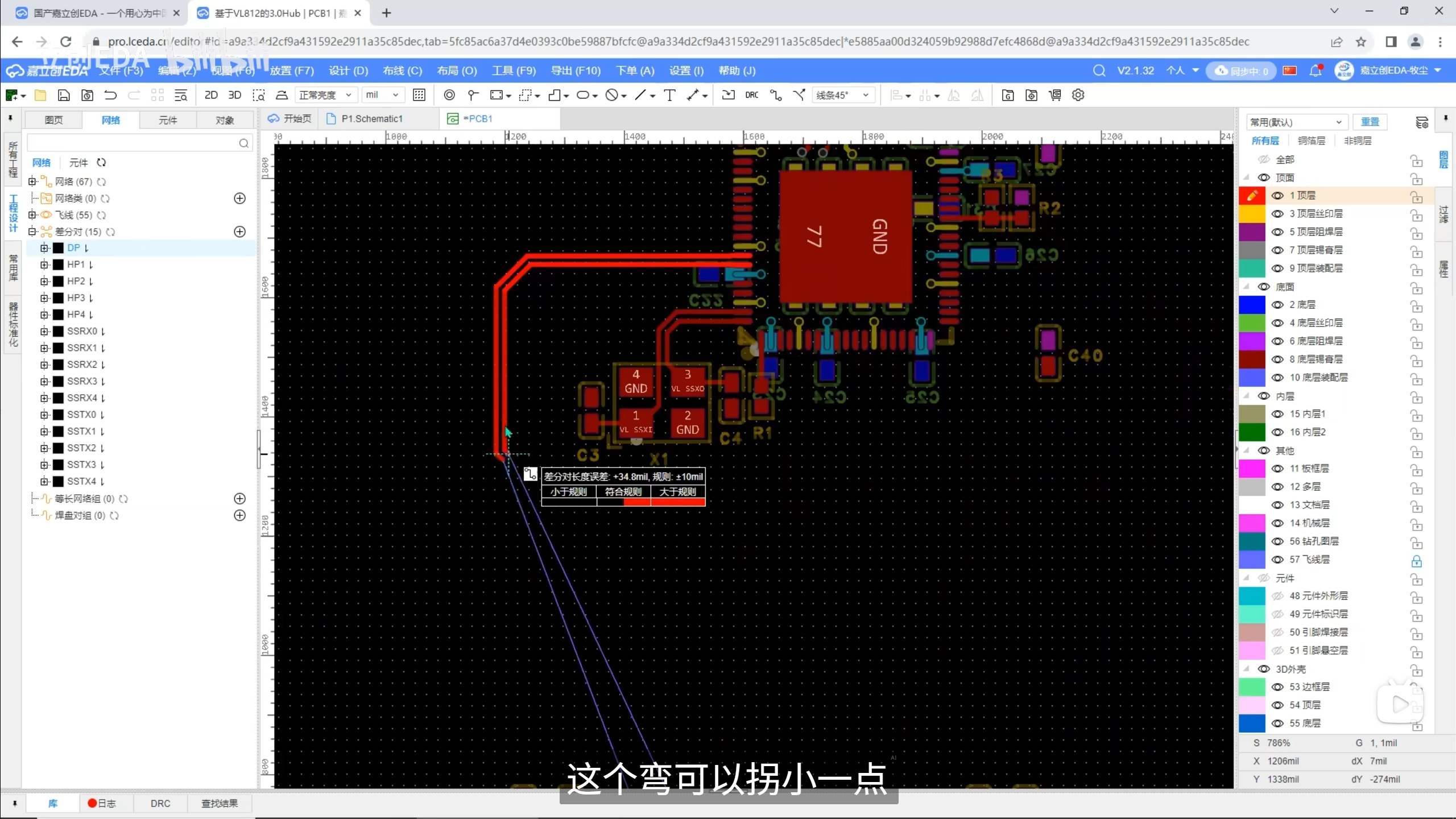

基于以上原因,PCB 设计中通常建议将走线的拐角设计为圆角(一般建议拐角半径不小于走线宽度)或45° 角,以避免锐角带来的各种问题,保证 PCB 的信号完整性、制造可行性、电磁兼容性和机械可靠性。

36.

37.

38.

通常建议在晶振附近局部挖掉铺铜区,但并非绝对,核心是避免干扰,保证晶振稳定起振。

晶振是高频信号源,若其下方或周围的铺铜(尤其是接地铜皮)不完整、有断裂,或与晶振引脚形成不合理的寄生电容/电感,反而会引入干扰,影响频率稳定性。挖掉局部铺铜能减少这种寄生效应,让晶振的振荡回路更纯净。

但需注意,挖空区域不宜过大,且晶振的接地引脚仍需可靠连接到主接地平面,确保接地良好。

39.

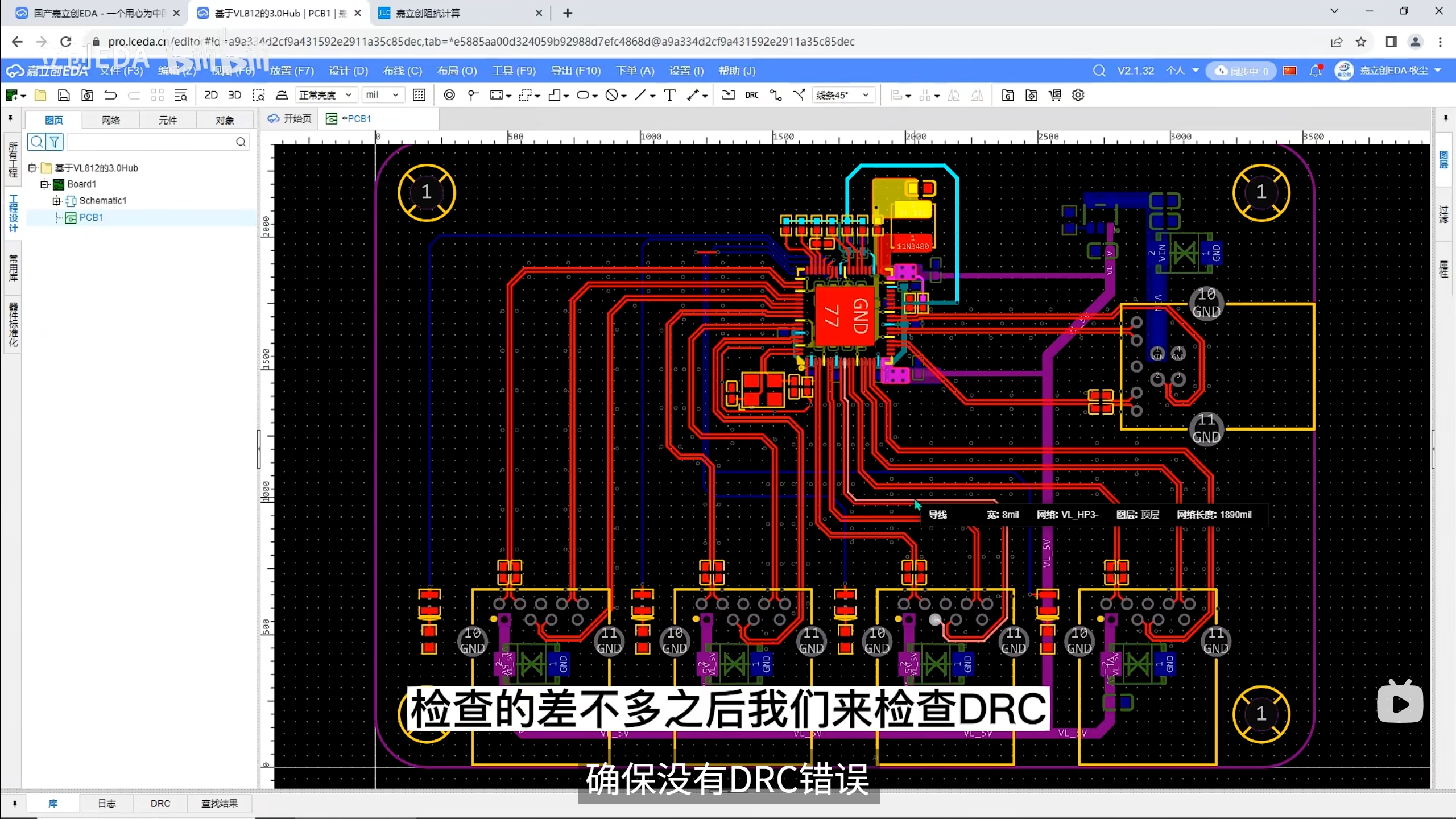

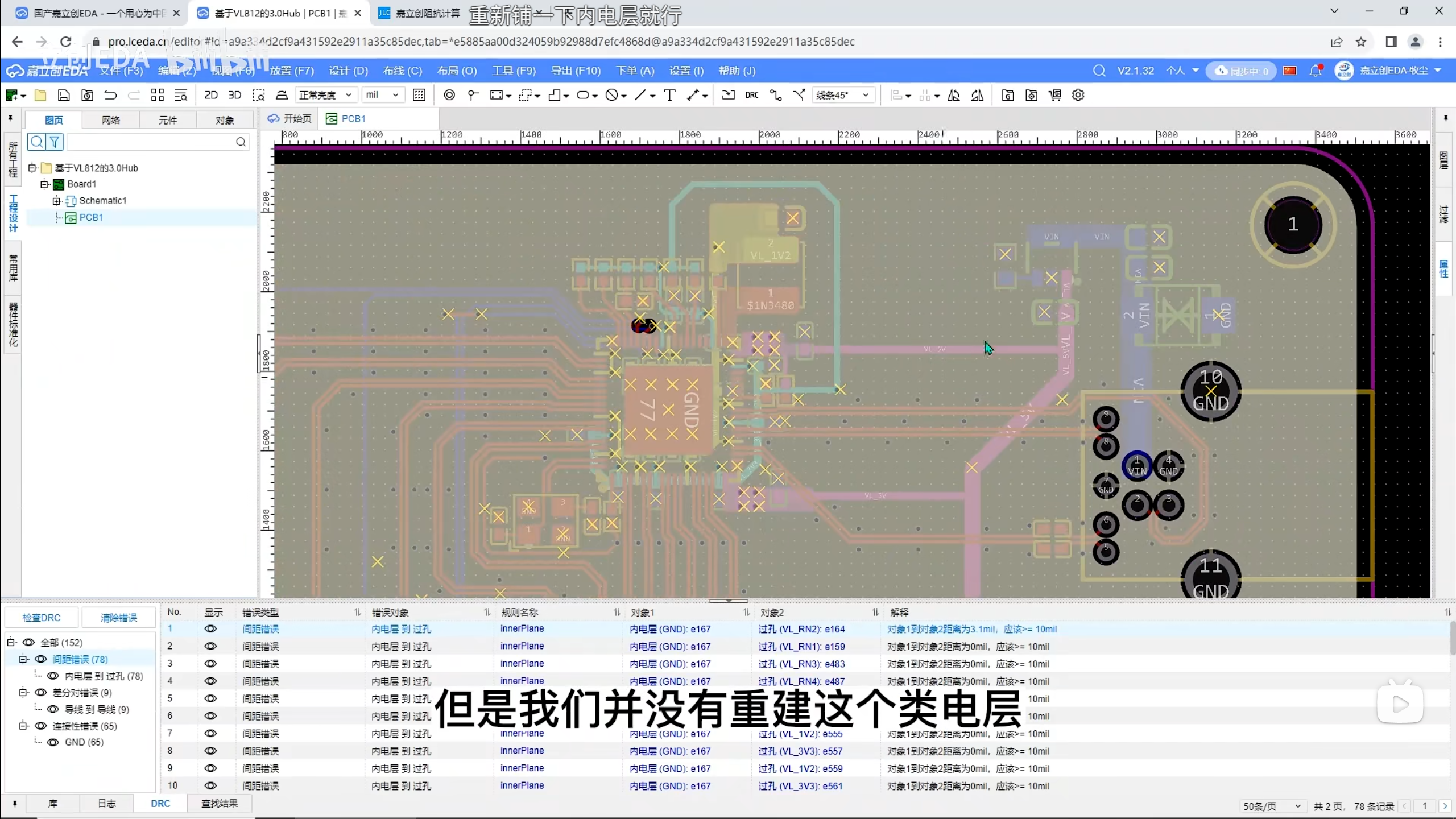

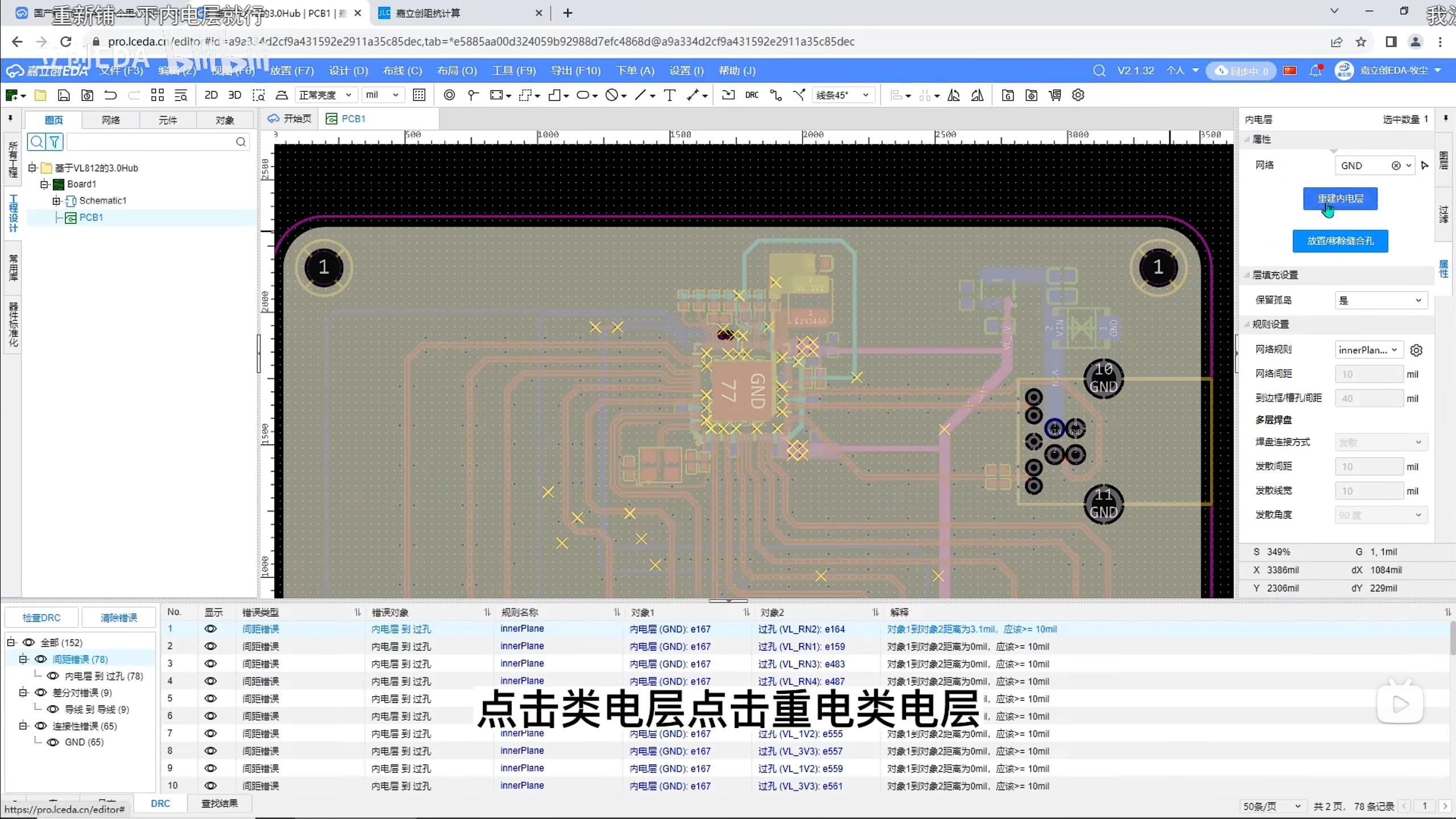

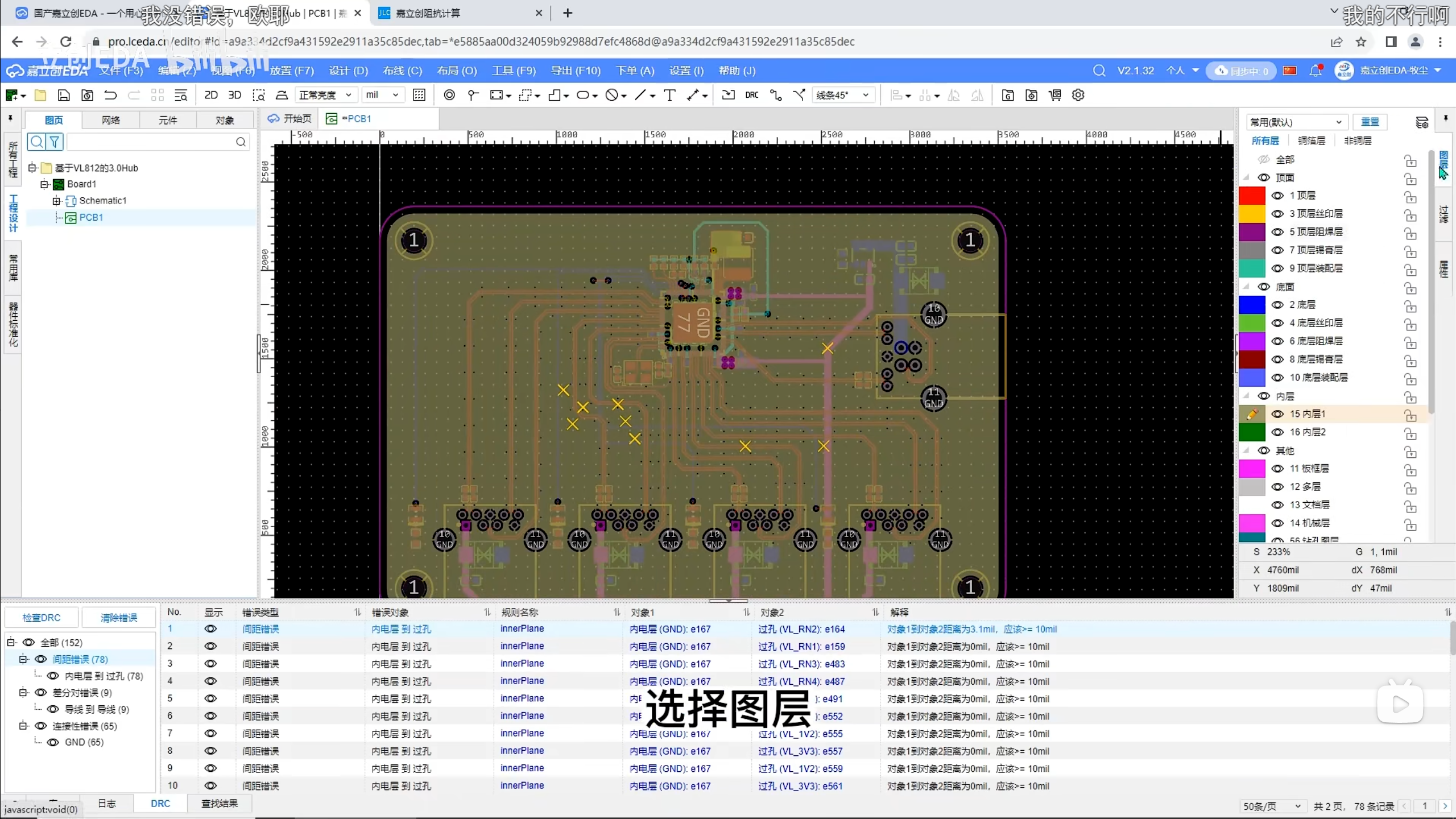

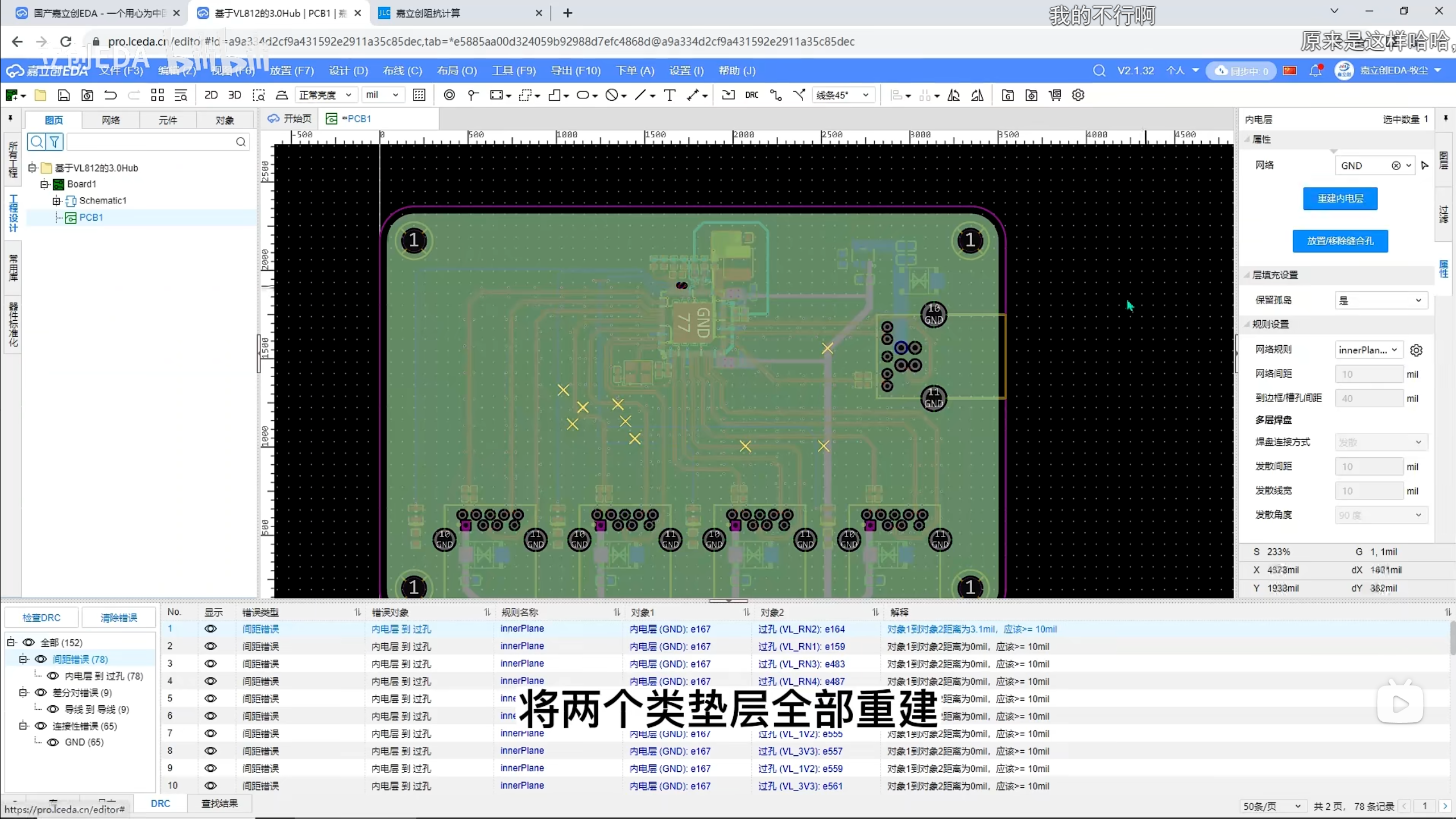

40.shift+b重建铺铜

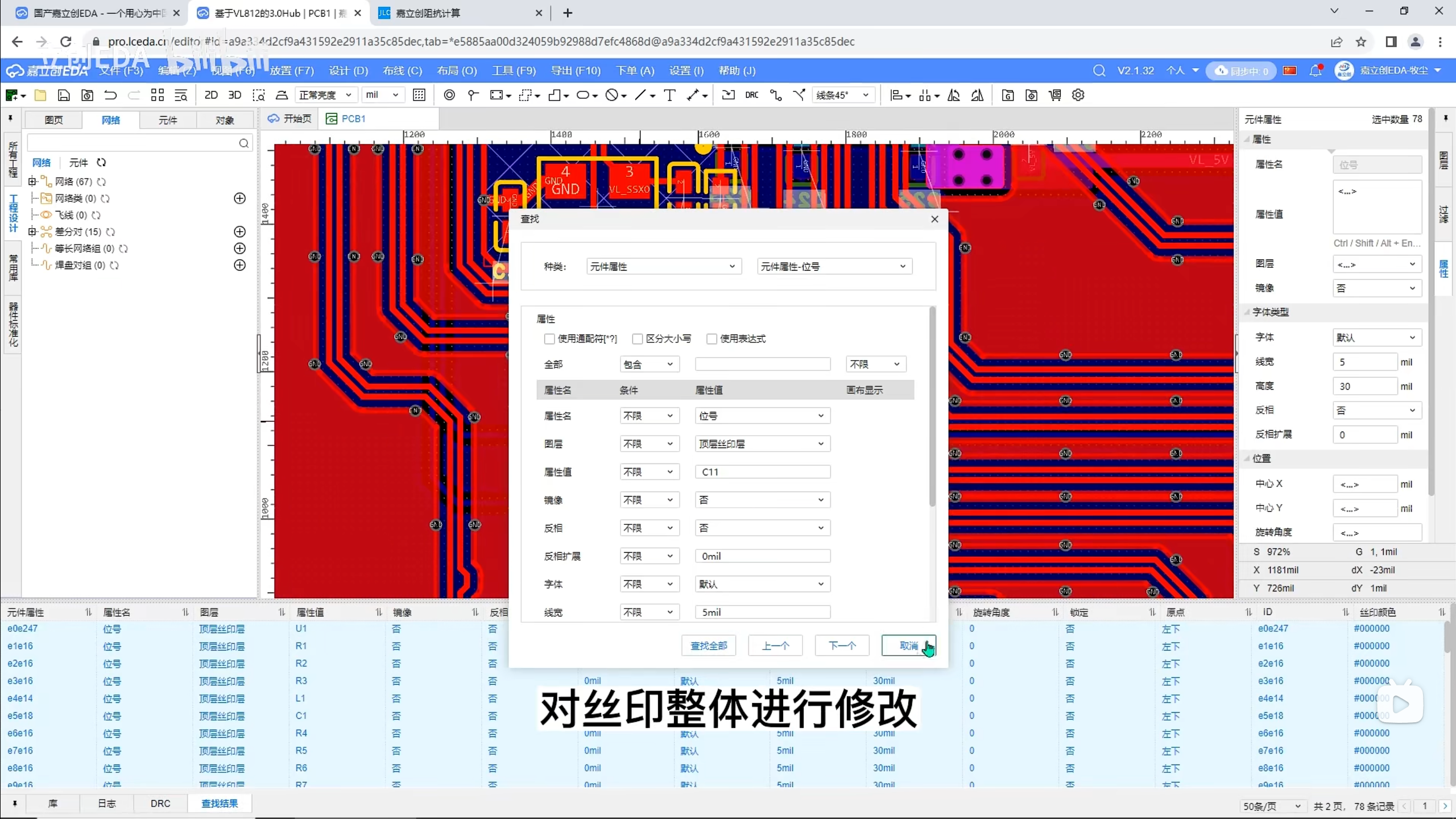

41.改丝印大小

42.

43.

44.

要对比四层板 “中间一层 GND + 一层 VCC” 和 “中间两层 GND” 这两种结构的优劣及成本,需从电气性能和制造成本两个维度分析:

一、电气性能对比

| 维度 | 中间 “GND+VCC” 结构 | 中间 “两层 GND” 结构 |

|---|---|---|

| 信号完整性 | 信号层(顶层 / 底层)有明确的参考平面(GND),高速信号回流路径短,阻抗控制精准,适合 USB 3.0 等高速传输。 | 仅单侧信号层有 GND 参考平面,另一侧信号层参考平面缺失,高速信号回流路径长,易出现阻抗不连续,信号失真风险高。 |

| 电源完整性 | 独立 VCC 层与 GND 层形成 “层间电容”,可抑制电源噪声,为芯片提供稳定供电,尤其适合多电源域、大电流场景。 | 无独立 VCC 层,电源需通过信号层走线传输,存在压降和噪声风险,电源稳定性差。 |

| 电磁干扰(EMI) | 完整的 GND 和 VCC 平面形成屏蔽层,可降低信号辐射和外界干扰,EMC 性能优异。 | 仅单层 GND 屏蔽,EMI 抑制能力弱,易受外界干扰或对外辐射。 |

| 布线密度 | 电源和地由专用层承载,信号层布线空间充足,可支持高密度 BGA、细间距元件。 | 电源需占用信号层走线,导致信号层布线拥挤,复杂电路易出现布线困难。 |

二、成本对比

| 维度 | 中间 “GND+VCC” 结构 | 中间 “两层 GND” 结构 |

|---|---|---|

| 材料成本 | 需为 VCC 层单独设计铜箔和介质层,材料用量略多。 | 无独立 VCC 层,材料用量少,成本略低。 |

| 加工成本 | 层压、蚀刻工艺复杂度与常规四层板一致,因电气性能优势,后期调试和整改成本低。 | 工艺复杂度虽低,但因电源稳定性差、EMI 问题可能导致后期多次改版,总体成本未必更低。 |

| 量产经济性 | 适合中高端、高速、高可靠性产品,批量生产时良率稳定(85%-90%),长期维护成本低。 | 仅适合低频、简单电路,批量生产时因性能缺陷导致的故障率高,隐性成本高。 |

结论

- 若涉及高速信号(如 USB 3.0)、多电源域或对 EMC 要求高,优先选择中间 “GND+VCC” 的结构,其在信号完整性、电源稳定性上的优势可避免后期大量调试成本,长期性价比更高。

- 若仅为低频、简单电路且极度追求低成本,可考虑中间 “两层 GND” 结构,但需接受性能上的明显妥协。

综上,从工程实用性和长期成本看,“中间 GND+VCC” 的四层板结构更具优势。