数字逻辑与FPGA实现基础

数字逻辑与FPGA实现基础

- 一. 复习组合逻辑电路的设计、化简和多种方式表达。按照课件内容完整推导电热水器水位报警系统。

- 1.组合逻辑电路的设计、化简和多种方式表达

- 2.例1.6.1 电热水器水位报警系统

- 3. 多种方式表达

- 总结

- 二. 复习大二上学期的“数字逻辑与组成原理”课程作业“Verilog编程基础练习”

- 1、对比Logsim设计的3-8译码器电路与Verilog编程实现的3-8译码器 RTL电路的区别。

- 2、用Verilog设计实现一个4位全加器。

- 三. 在DE2-115开发板上

- 1、完成4位全加器系统的设计、下载和功能演示。

- 2、完成3-8译码器的设计、下载和功能演示(利用板上的8段数码管)

一. 复习组合逻辑电路的设计、化简和多种方式表达。按照课件内容完整推导电热水器水位报警系统。

例1.6.1如图所示:

1.组合逻辑电路的设计、化简和多种方式表达

1.组合逻辑电路的设计步骤

-

逻辑抽象:

-

确定输入、输出变量:根据实际问题确定输入和输出变量,并定义其逻辑状态。

-

定义逻辑状态:确定每个变量的逻辑状态(通常用0和1表示)。

-

-

列出真值表:

- 根据逻辑描述:根据问题的逻辑描述,列出所有可能的输入组合及其对应的输出。

-

写出逻辑表达式:

-

从真值表中提取:根据真值表,写出每个输出的逻辑表达式。

-

简化逻辑表达式:使用代数法或卡诺图法化简逻辑表达式。

-

-

画出逻辑图:

- 根据逻辑表达式:根据化简后的逻辑表达式,画出对应的逻辑电路图。

2.例1.6.1 电热水器水位报警系统

- 逻辑抽象

- 输入变量:

- A:水位检测元件A的输出(逻辑1表示水位低于A,逻辑0表示水位高于A)。

- B:水位检测元件B的输出(逻辑1表示水位低于B,逻辑0表示水位高于B)。

- C:水位检测元件C的输出(逻辑1表示水位低于C,逻辑0表示水位高于C)。

- 输出变量:

- G:绿灯(逻辑1表示灯亮,逻辑0表示灯灭)。

- Y:黄灯(逻辑1表示灯亮,逻辑0表示灯灭)。

- R:红灯(逻辑1表示灯亮,逻辑0表示灯灭)。

- 列出真值表

根据题目要求,列出真值表如下:

- 写出逻辑表达式

根据真值表,写出每个输出的逻辑表达式:

-

绿灯 G:

-

黄灯 Y:

-

红灯 R:

- 化简逻辑表达式

使用卡诺图法化简逻辑表达式:

-

绿灯 G:

-

黄灯 Y:

-

红灯 R:

- 画出逻辑图

根据化简后的逻辑表达式,画出逻辑电路图:

- 绿灯 G:

- 使用与门和非门实现。

- 黄灯 Y:

- 使用与门、或门和非门实现。

- 红灯 R:

- 使用与门实现。

3. 多种方式表达

-

逻辑代数表达式:

-

真值表:如上所示。

-

逻辑图:如上所示。

-

卡诺图:用于化简逻辑表达式。

-

硬件描述语言(HDL):使用Verilog HDL描述逻辑电路。

总结

通过逻辑抽象、真值表、逻辑表达式、化简和逻辑图的步骤,我们完成了电热水器水位报警系统的设计。最终的逻辑表达式和逻辑图可以用于实际的电路设计和实现。

(以上内容由AI生成)

二. 复习大二上学期的“数字逻辑与组成原理”课程作业“Verilog编程基础练习”

1、对比Logsim设计的3-8译码器电路与Verilog编程实现的3-8译码器 RTL电路的区别。

设计过程

- Logsim设计:Logsim 是一款图形化的数字电路仿真工具。在 Logsim 中设计 3-8译码器,需要手动摆放与门、或门、非门等逻辑门元件,并通过连线将它们连接起来以实现译码逻辑。设计者需要对每个逻辑门的输入输出关系有清晰的理解,并且要逐一完成电路的构建,设计过程比较直观,但相对繁琐,尤其是对于大规模电路设计。

- Verilog设计:Verilog 是一种硬件描述语言(HDL),用户通过编写代码来定义电路的行为和结构。在 Verilog 中设计3-8 译码器,需要使用组合逻辑语句(如 case、assign 等)描述译码器的逻辑功能。设计者可以利用 Verilog的模块化、层次化设计方法,快速搭建电路模型。相比于 Logsim,Verilog 的设计过程更加抽象,但效率更高,尤其适合大规模电路设计。

电路表示

- Logsim设计:在 Logsim 中,3-8译码器的电路是通过图形化界面展示的,电路中的每个逻辑门和连线都以直观的方式呈现。例如,译码器的输入输出信号、逻辑门之间的连接关系等都能通过图形界面清晰地观察到。这种表示方式便于初学者理解电路的基本结构和工作原理。

- Verilog设计:Verilog 设计的 3-8 译码器以文本形式描述电路的逻辑关系。例如,使用 case语句可以根据输入选择对应的输出,代码的结构和逻辑关系清晰明了。然而,与图形化表示相比,Verilog 的代码表示可能不够直观,需要用户具备一定的代码阅读和理解能力。

电路实现

- Logsim设计:Logsim生成的电路是软件仿真环境中的虚拟电路,主要用于电路的可视化设计和功能验证。虽然它可以帮助用户理解电路的工作原理,但无法直接生成实际的硬件电路,也不能用于实际的硬件实现。

- Verilog设计:Verilog 设计的电路可以通过综合工具(如 Design Compiler等)转换为硬件描述语言的网表文件。这些网表文件可以被进一步用于 FPGA、ASIC等硬件平台的布局布线,最终生成实际的物理电路,完成电路的物理实现。

灵活性和可扩展性

- Logsim设计:在 Logsim 中,修改电路的逻辑功能需要重新调整逻辑门的连接和配置,灵活性相对较差。例如,如果想要将译码器扩展为4-16 译码器,需要手动添加更多的逻辑门和连线,工作量较大。

- Verilog设计:Verilog设计具有高度的灵活性和可扩展性。通过参数化设计和模块化设计,可以轻松地对译码器进行功能扩展。例如,通过修改参数或添加模块,可以快速将3-8 译码器扩展为更大的译码器,如 4-16 译码器或更高位数的译码器。

调试和验证

- Logsim设计:Logsim提供了直观的调试工具,如探针、示波器等,可以方便地观察电路中各个节点的信号状态和波形。此外,还可以通过仿真运行电路,观察译码器的输出是否符合预期,验证其功能的正确性。

- Verilog设计:Verilog 设计通常需要借助专业的仿真工具(如 ModelSim等)进行调试和验证。验证过程包括编写测试平台(Testbench),输入测试向量,观察输出结果,并通过分析仿真结果来验证电路的功能是否正确。Verilog的调试和验证过程相对复杂,但可以实现更全面、更系统的验证。

2、用Verilog设计实现一个4位全加器。

4位全加器是数字电路中的一个基本模块,用于对两个4位二进制数进行加法运算。以下是用Verilog实现的4位全加器的设计代码:

module FullAdder_4bit(

input [3:0] a, // 输入A,4位

input [3:0] b, // 输入B,4位

input cin, // 输入进位

output [3:0] sum, // 输出和,4位

output cout // 输出进位

);

// 内部信号

wire [3:0] c_out; // 每个位的进位

// 4位全加器的实现

assign {cout, sum} = a + b + cin;

endmodule

代码说明

- 模块端口定义:

- a 和 b 是两个4位的输入信号。

- cin 是初始的进位输入(第1位加法的进位输入)。

- sum 是4位的输出和。

- cout 是最高位的进位输出。

- 内部信号:

- c_out 是一个4位的中间进位信号。

- 加法器实现:

- 使用 Verilog 的位拼接操作符 { },将最高位的进位 cout 和4位和 sum 合并为一个5位的输出。

- 使用加法运算符 +,对 a、b 和 cin 进行加法运算,并自动处理进位逻辑。

使用方法

- 将上述代码保存为 FullAdder_4bit.v。

- 使用 Verilog 仿真工具(如 ModelSim)或 FPGA 开发工具(如 Quartus Prime)对代码进行编译和仿真。

- 通过测试平台(Testbench)输入不同的 a、b 和 cin 值,观察 sum 和 cout 的输出,验证4位全加器的功能。

示例输入输出

假设输入:

- a = 4’b0011(即十进制3)

- b = 4’b0010(即十进制2)

- cin = 1’b0

输出:

- sum = 4’b0101(即十进制5)

- cout = 1’b0

该设计的时间复杂度是O(1),因为所有的位运算都是并行处理的。 空间复杂度也是O(1),因为只涉及固定数量的寄存器和逻辑门。(以上内容由AI生成)

三. 在DE2-115开发板上

1、完成4位全加器系统的设计、下载和功能演示。

- FPGA上1位全加器的实现

首先,搭建一个半加器:需要1个and2,1个xor,2个输出,2个输入。(需要将其封装,以便搭建一位全加器)

RTL电路如下:

其次,搭建一位全加器:需要2个半加器,1个or2,2个输出,2个输入。

也可使用verilog生成一位全加器:

module verilog_full_adder(

//输入信号,ain表示被加数,bin表示加数,cin表示低位向高位的进位

input ain,bin,cin,

//输出信号,cout表示向高位的进位,sum表示本位的相加和

output reg cout,sum

);

reg s1,s2,s3;

always @(ain or bin or cin) begin

sum=(ain^bin)^cin;//本位和输出表达式

s1=ain&cin;

s2=bin&cin;

s3=ain&bin;

cout=(s1|s2)|s3;//高位进位输出表达式

end

endmodule

生成一位全加器,RTL电路如下图所示:

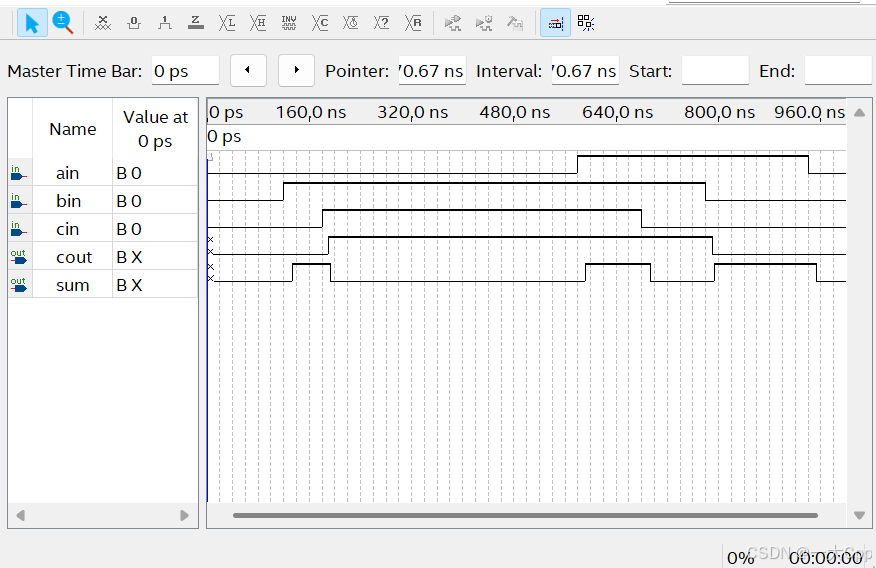

功能仿真如下:

时序仿真如下:

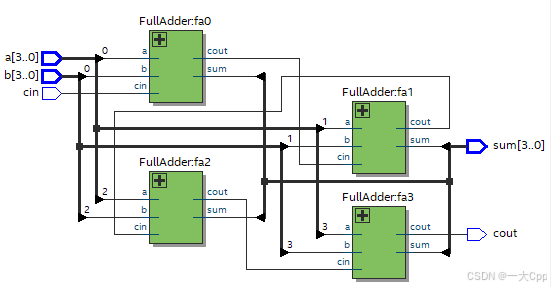

最后,用4个一位全加器搭建四位全加器:需要4个一位全加器,9个输入,4个输出。

RTL电路如下:

功能仿真如下:

时序仿真如下:

也可用verilog生成1个四位全加器:

module FullAdder_4bit(

input [3:0] a, // 输入A,4位

input [3:0] b, // 输入B,4位

input cin, // 输入进位

output [3:0] sum, // 输出和,4位

output cout // 输出进位

);

// 内部信号:每个位的进位输出

wire [3:0] c_out;

// 实例化4个一位全加器模块

FullAdder fa0 (a[0], b[0], cin, sum[0], c_out[0]);

FullAdder fa1 (a[1], b[1], c_out[0], sum[1], c_out[1]);

FullAdder fa2 (a[2], b[2], c_out[1], sum[2], c_out[2]);

FullAdder fa3 (a[3], b[3], c_out[2], sum[3], c_out[3]);

// 最终进位输出为第4位的进位输出

assign cout = c_out[3];

endmodule

// 一位全加器模块

module FullAdder(

input a, // 输入A,1位

input b, // 输入B,1位

input cin, // 输入进位

output sum, // 输出和,1位

output cout // 输出进位

);

// 逻辑表达式

assign sum = a ^ b ^ cin; // 和

assign cout = (a & b) | (b & cin) | (cin & a); // 进位

endmodule

生成四位全加器,如下图所示:

功能仿真如下:

时序仿真如下:

2、完成3-8译码器的设计、下载和功能演示(利用板上的8段数码管)

首先,可以用搭建电路图的方式来完成3-8译码器的设计步骤:

RTL电路如下:

功能仿真如下:

时序仿真如下:

也可用verilog语言生成3-8译码器

module Decoder3To8(

input [2:0] address, // 3位输入地址

input enable, // 使能信号

output reg [7:0] data // 8位输出数据

);

// 使用组合逻辑语句实现译码

always @(*) begin

// 初始化输出为低电平

data = 8'b00000000;

// 如果译码器被使能

if (enable) begin

case (address)

3'b000: data[0] = 1'b1; // 地址0选择data[0]

3'b001: data[1] = 1'b1; // 地址1选择data[1]

3'b010: data[2] = 1'b1; // 地址2选择data[2]

3'b011: data[3] = 1'b1; // 地址3选择data[3]

3'b100: data[4] = 1'b1; // 地址4选择data[4]

3'b101: data[5] = 1'b1; // 地址5选择data[5]

3'b110: data[6] = 1'b1; // 地址6选择data[6]

3'b111: data[7] = 1'b1; // 地址7选择data[7]

default: data = 8'b00000000; // 默认情况下输出全低

endcase

end

end

endmodule

生成3-8译码器,如下图所示:

功能仿真如下:

时序仿真如下: