数电基础:TTL构成的常见门电路

目录

一、TTL与非门

(1)与非门结构及原理

(2)输入输出特性

二、TTL或非门

(1)或非门的结构及原理

(2)输入输出特性

三、集电极开路输出的门电路(OC门)

(1)为什么需要OC门

(2)OC门的上拉电阻RL选取规则

四、三态输出门电路(TS门)

在上一篇文章,我们详细探讨了TTL反相器的工作原理及其输入输出特性。与CMOS门电路一致,反相器一直是所有门电路的基础组件,有了反相器之后才能构成更为复杂的门电路。本篇文章将在TTL反相器的基础上,延伸到常见的与非门、或非门等电路。

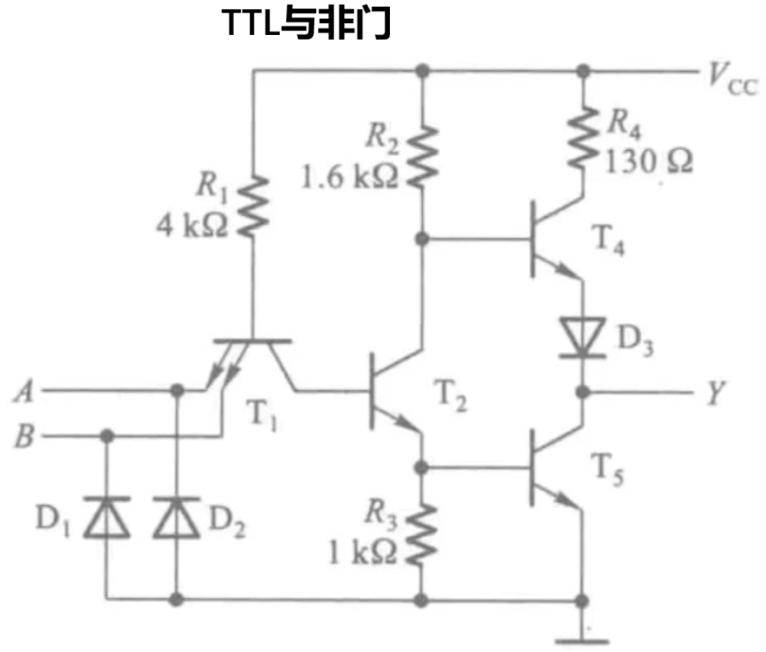

一、TTL与非门

(1)与非门结构及原理

所谓的TTL与非门其实就是在原本的反相器的T1管子引出两个输入端。

(1)当A、B两点都输入相同的电平信号时,直接等效于反相器输入高/低电平。

(2)当A、B两点一方输入高电平、一方输入低电平。看似在T1的发射极电位不相同了,与基尔霍夫定律都相违背了。但其实是和我们在二极管开关电路章节分析的类似,此时A、B两个输入端可以看做一个共阳二极管连接到T1的基极。由于电位低的通路会优先导通,所以电位会被钳位在较低的一方。而另一方则体现出PN结反向承担电压,如果这个反向电压过大,则会烧毁二极管,好在是TTL电路的高电平3.4V并不会轻易烧毁PN结,所以才能构造TTL与非门。

(3)分析上述两个结果,他们都在说明一个情况:有0则1,全1才0。完美的对应了与非的特性。

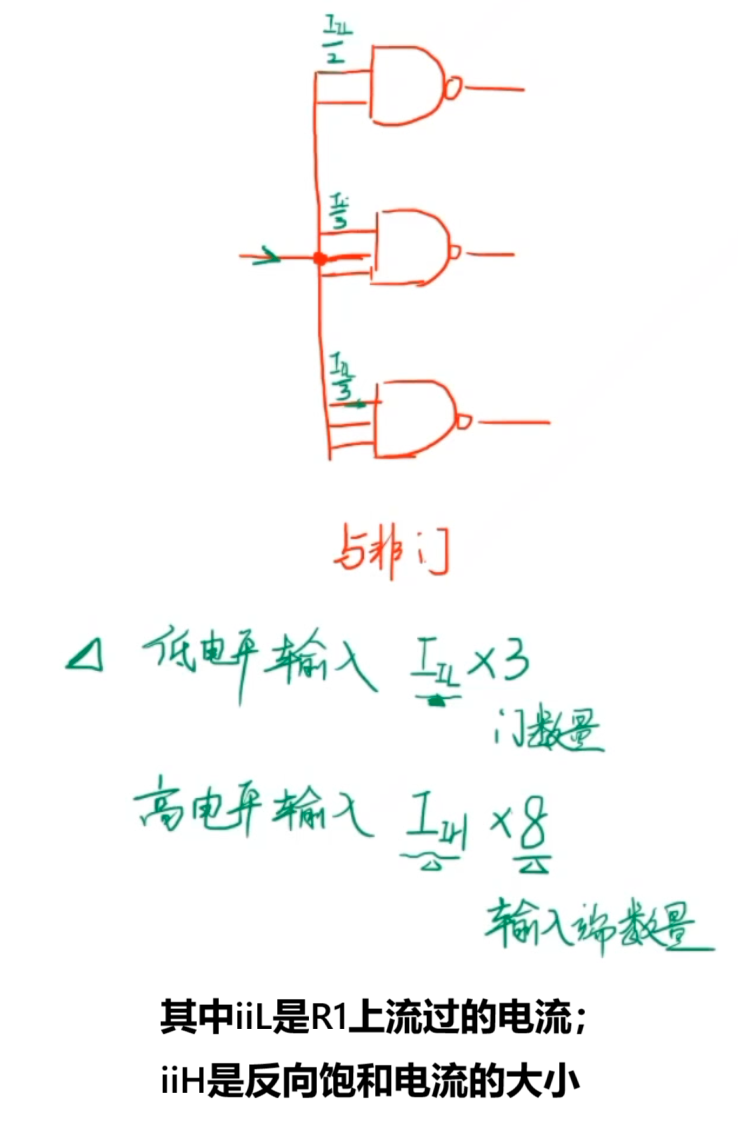

(2)输入输出特性

当输入低电平VIL时,根据TTL反相器的知识我们知道,T1管子的B点电位会被钳制在VIL+0.7V,于是在电阻R1身上的电压就是VCC-VIL-0.7,可以发现是一个固定值。那么从R1上面流过的电流即是固定的。然后因为在输入低电平时,T1管子是出于深度饱和的,所以电流是从内往外流出,即为负值。

换句话说,即使你在T1的发射极接N个出去,都与输出的电流无关。因为内部的R1及其压降已经决定了总输出电流的大小。

当输入高电平(大于1.4V)的时候,T1是工作在倒置状态的。即内部电流的流向是:VCC->R1

->T1的基极->T1的集电极->T2->T5->输出电流。而在输入端则相当于PN结加负压时候的反向饱和电流。

简单来说就是,此时输入电流的大小是取决于接入的数量的,具体的值是N*反向饱和电流。

至于输出端于纯粹的TTL无任何差异。不再赘述。

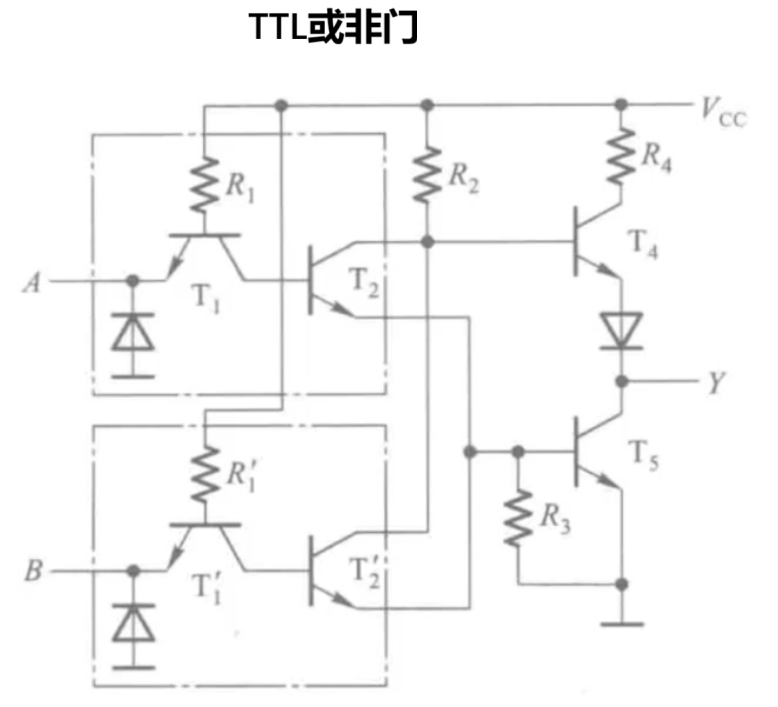

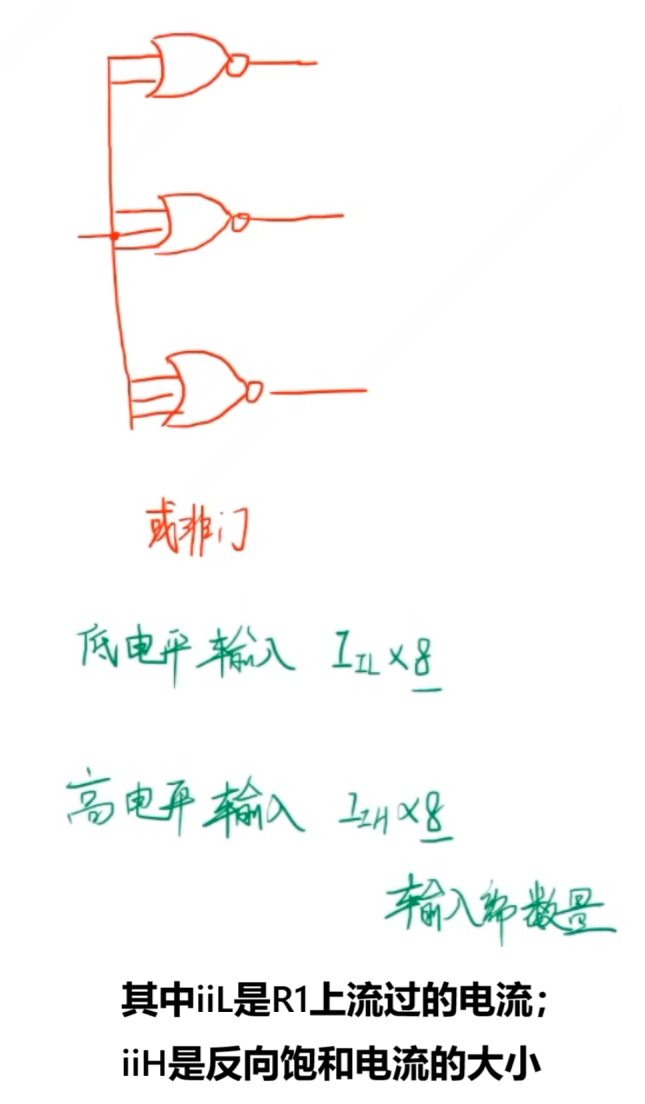

二、TTL或非门

(1)或非门的结构及原理

或在开关电路中是并联的意思,于是直接将TTL输入端改为两个并联输入。

(1)当A、B两端全部输入相同电平时候,可以直接等效成TTL反相器分析。

(2)当A、B两端一个输入高电平、另一个输入低电平时。假设A输入高电平,则T2导通、T5导通,输出低电平;B输入低电平,T2'截止,这里T5会被截止吗?并不会,因为T2'截止了,相当于和T5断开了联系,所以T5只受A部分的T2影响。即一方输入高,另一方输入低电平时候,T5只会看高电位的T2而呈现导通态。从而输出低电平。

(3)综上两条结论,发现他们在描述:有1则0;全0才1的特点。这个与或非的特性是完全一致的。

(2)输入输出特性

因为在或非门中,每一个输入端口都是独立的,所以计算电流的时候也是独立的。即电路内部总电流是所有输入端的总和,并不会出现与非门输入低电平时候总电流恒定的特点。

当输入低电平的时候,每一个门都会有R1上VCC-VIL-0.7产生的电流,于是总流出量为N*每条支路的电流。

当输入高电平的时候,和与非门一致,每一个端口都有一个R1流经电流。总流入的是N个反向饱和电流的值。

至于输出特性于TTL反相器并无任何差异。

综合与非门、或非门两种而言,其实只有与非门的低电平特殊一点,输入端流出的总电流是一致的,而其他三种情况的电流都是叠加计算。其实这个并不需要记忆,用的时候根据TTL反相器的原理很快就能理顺。

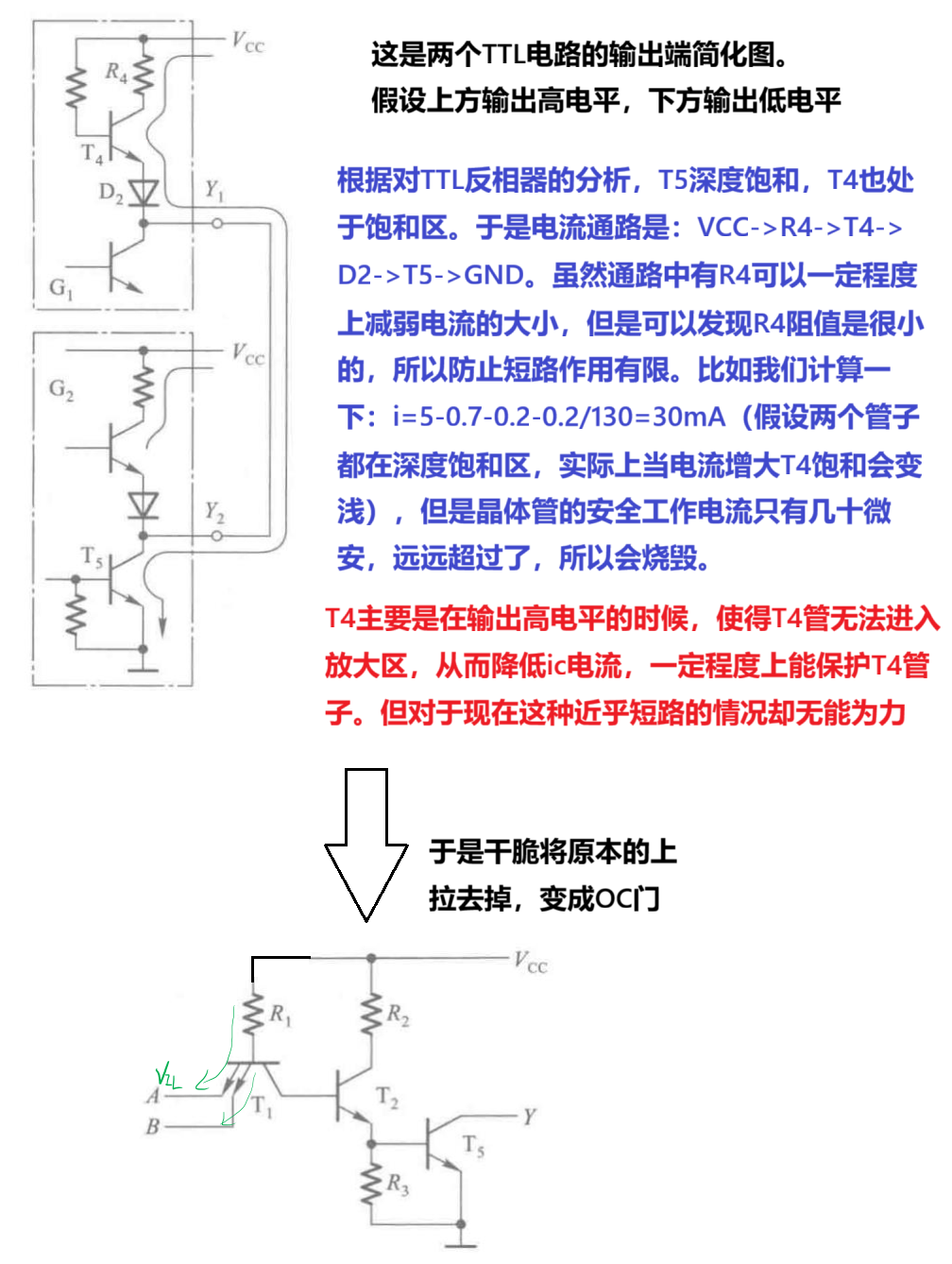

三、集电极开路输出的门电路(OC门)

(1)为什么需要OC门

在CMOS门电路中,我们通过分析发现各种一般CMOS不允许直连,因为会把电源接地,产生极大的电流烧毁电路中的元件,于是采取去掉原本的PMOS管,然后对于上拉部分替换成一个公共的上拉电阻,这样无论哪条支路导通都必定会经过该上拉电阻,从而保护电源。同时发现这样的OD门就能实现线与功能了,同时还附带了电平转换的能力。

于是在TTL门电路中,我们也希望它和OD门类似。我们把原本用于上拉输出的R4、T4管子、D2二极管这些全都去掉,然后在外面需要的时候再添加上拉电阻,从而达到与OD门一致的效果。

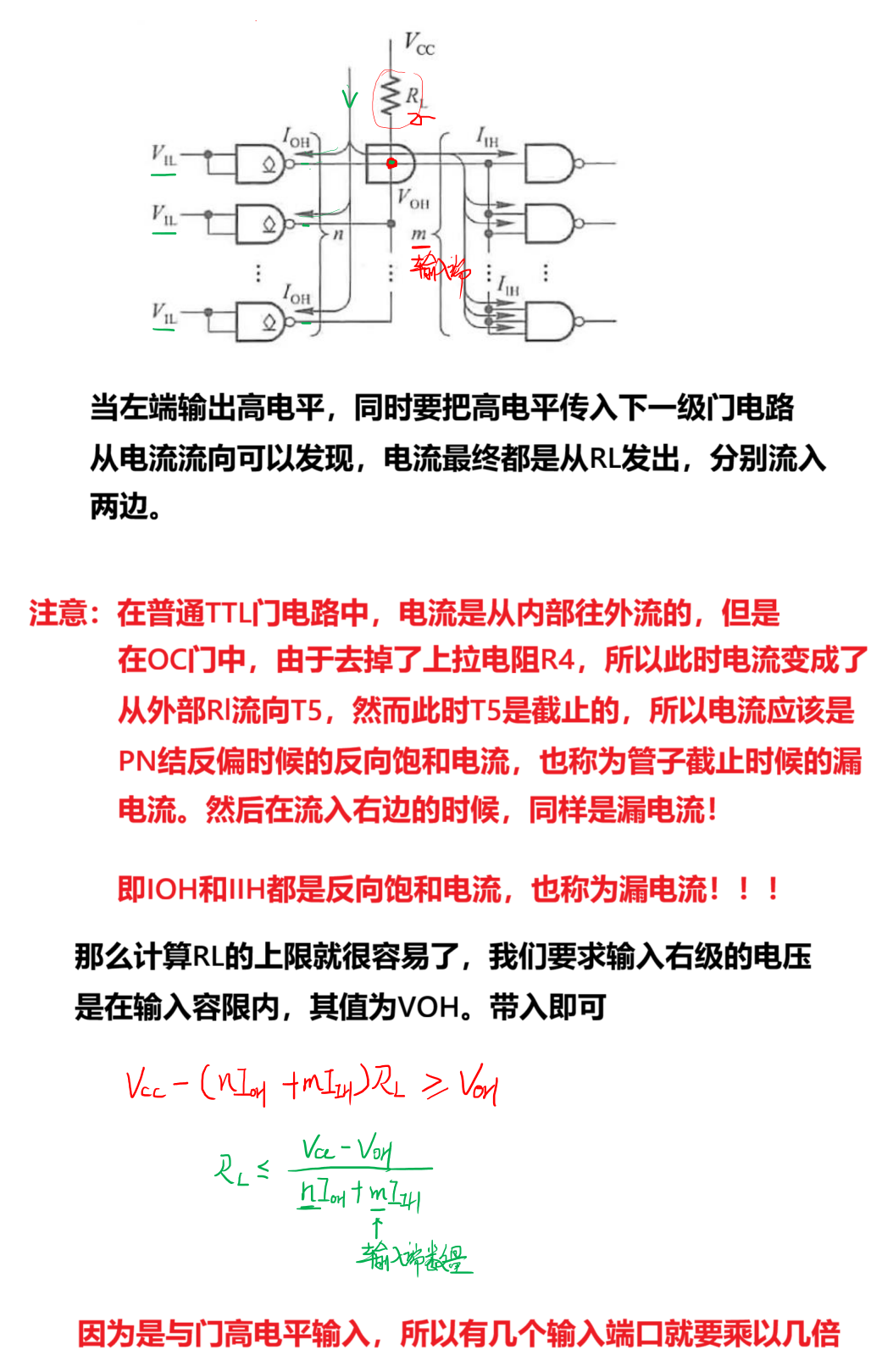

(2)OC门的上拉电阻RL选取规则

当输出高电平时:

考虑的关键点在于RL分压不能太大,至少不能低于高电平的噪声容限。

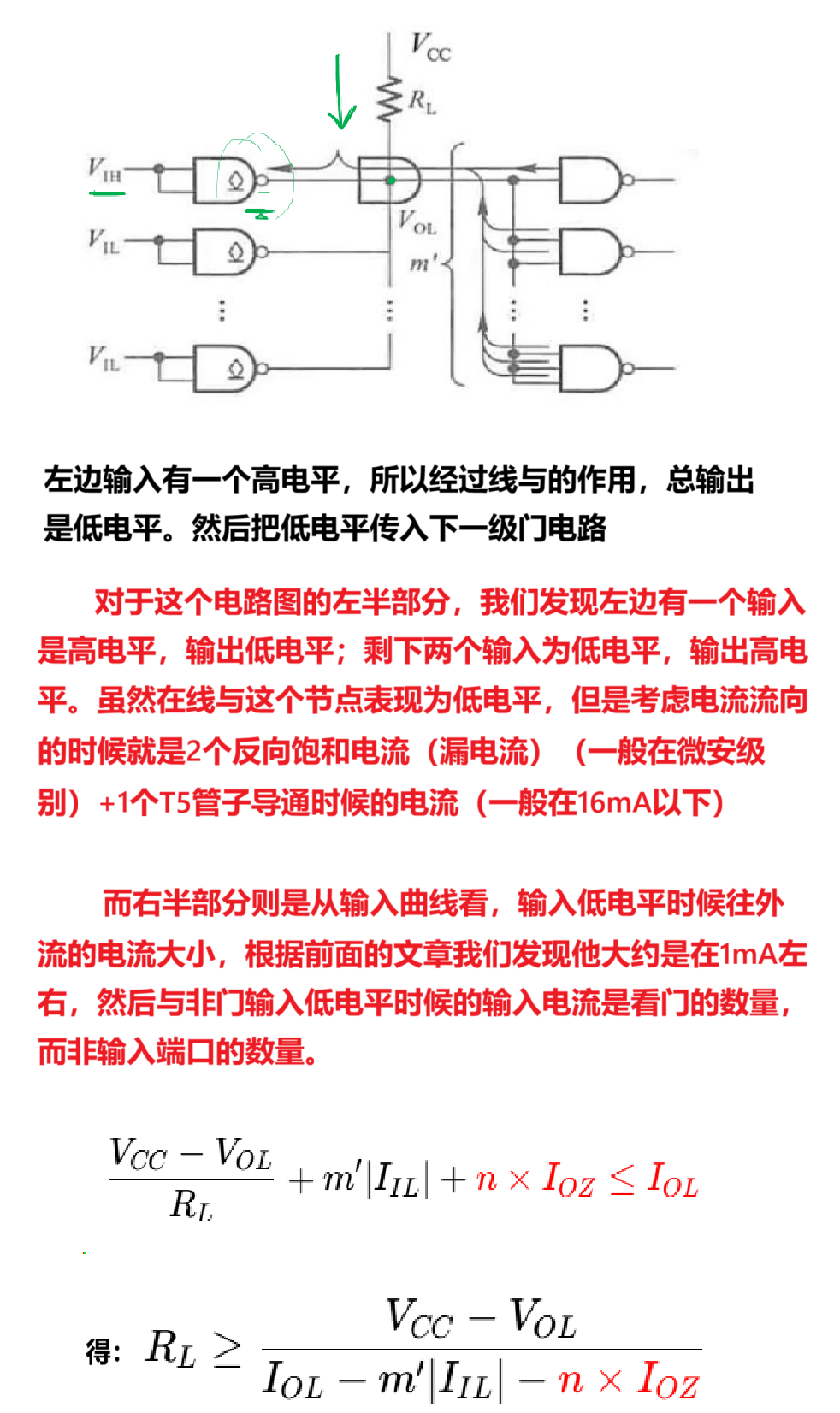

当输出低电平时:

考虑的关键点在于电流汇聚到某个T5下拉时候,不会超过其输出特性中的最大电流16mA左右。

结合两个方程,可以得到上拉电阻RL的选取范围。

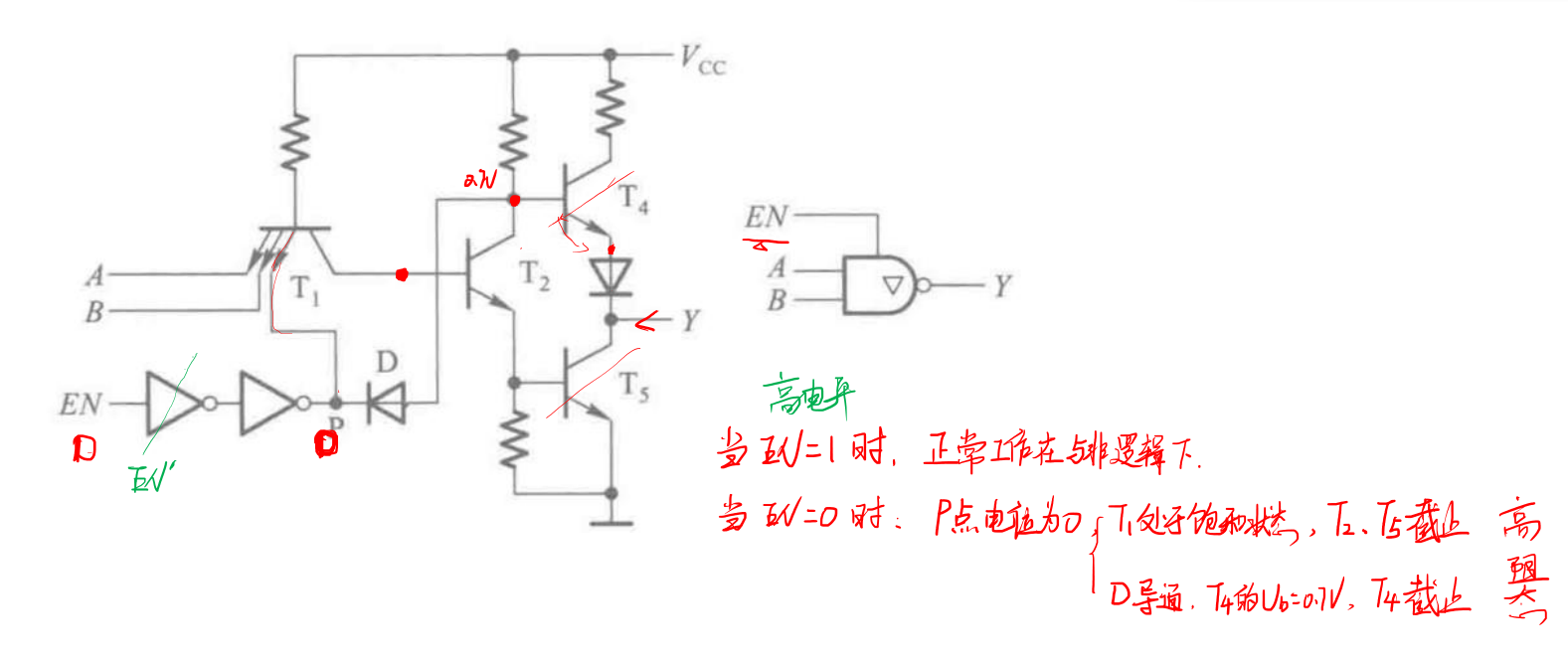

四、三态输出门电路(TS门)

类似CMOS的三态门的出现原因,我们制作了TS门。三态门的关键在于让两端都呈现截止状态,即体现高阻态断开,不会输出0或1。

TTL的三态门思考逻辑比CMOS的三态门简单,他的思考逻辑十分连贯。就是想让使能端可以控制输入端电平,从而先截止T5,让其工作在上拉作用下。然后再把上拉的T4左边、下方分别接一个二极管钳位,使得T4的b端电位不足以导通两个PN结而截止。