STM32H7 SPI通信的Underrun特性介绍 LAT1525

关键字: SPI , underrun,UDRDET,TxFIFO

1. 前言

在SPI通讯中,从器件借助主器件提供时钟信号进行发送和接收,收发的时刻由主器 件进行控制。在从器件发送模式下,如果主器件的时钟信号已经到来,但是从器件还没有 准备好要发送的数据(没有将数据放入TXFIFO中),就会发生下溢。若能够正确合理的 检测到下溢,并对其进行处理,可以提供数据传输的可靠性。

在STM32H7中可以配置下溢检测的位置,下面以STM32H723芯片为蓝本进行介绍。

2. 通信格式

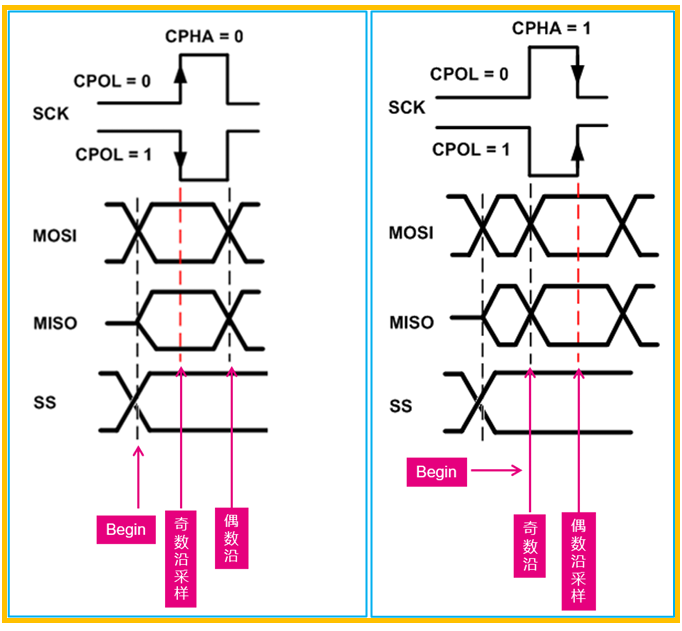

我们先理解下SPI的时钟相位和极性控制,时钟可以设置为四种基本配置之一。CPOL 和CPHA两个位的组合控制时钟信号的极性和相位。

• CPOL(时钟极性):SCK引脚空闲状态时的电平状态。

- CPOL=0 : SCK引脚空闲为低电平

- CPOL=1 : SCK引脚空闲为高电平

• CPHA(时钟相位):定义了哪个时钟边沿用于数据采样或移位(如下图所示)。

- CPHA=0 : 数据位在奇数时钟边沿采样,偶数时钟边沿或之后将下一个 数据位移到数据线上。

- CPHA=1 : 奇数时钟边沿或之后将当前数据位移到数据线上,数据位在 偶数时钟边沿采样。

图1. 时钟和相位控制示意图

3. 下溢检测

SPI(串行外设接口)从机下溢是一种在SPI通信中常见的错误情况,通常发生在从器 件(从机)未能及时提供数据给主器件(主机)时。

为了适应多种工作场景,STM32H7可以通过SPI_CFG1寄存器的UDRDET字段来配 置从机在发送模式下检测下溢的时刻。在从器件发送模式下,如果在 UDRDET 位指定的 时刻,从器件 TxFIFO 中没有数据可用于发送,则会由硬件在内部捕获下溢情况。

但是要注意,由于硬件传播延迟,UDR事件发生后会在几个SPI时钟周期后才能检测 到UDR事件发生(或者产生UDR事件中断)。

下面针对这几个检测的位置做一个简单介绍。

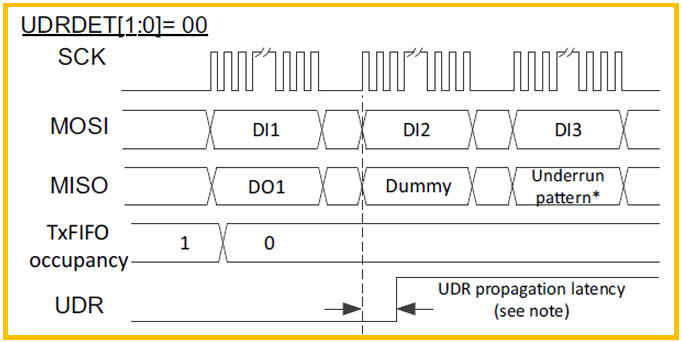

3.1. UDRDET = 0

当UDRDET=0的时候,在主器件发出新的数据帧时(开始为新的帧提供时钟信号 时),从器件会检测TXFIFO是否为空。当TXFIFO为空时,会产生下溢事件,slave会发 送一个dummy数据,如果不清除SR寄存器的UDR状态位,后续会发送underrun pattern 数据(由UDRCFG字段进行定义)

如下图所示,在第二帧开始的时候,TXFIFO已经为空了,此时会产生下溢 (underrun)事件,但是由于UDR(underrun)事件传播需要占用几个SPI时钟周期,所 以看到在实线位置处才能实际检测到UDR事件发生(或者产生UDR事件中断)。Slave 在第二帧发送的时dummy数据,第三帧及之后发送都是underrun pattern数据。

图2. UDRDET = 0

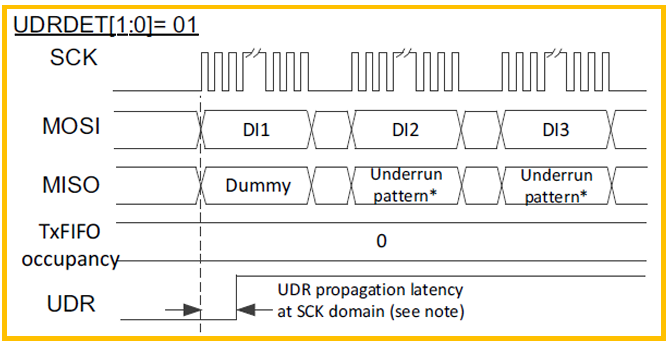

3.2. UDRDET = 1

当UDRDET=1的时候,在上一帧通讯结束的时候(TXFIFO变为空时),从器件会检 测TXFIFO是否为空。

这时候会有两种情况:

1. 在刚开始传输时TXFIFO就为空(第一帧)。由于TXFIFO为空,产生下溢事件。 没有可用数据可以发送,此时slave会先发送dummy数据,如果不清除SR寄存 器的UDR状态位,则后面会发送underrun pattern数据(由UDRCFG字段进行 定义)。

如下图所示,在第一帧时TXFIFO就为空,此时会产生UDR(underrun,下溢) 事件,由于UDR事件传播需要占用几个SPI时钟周期,所以看到在实线位置处才 能实际检测到UDR事件发生(或者产生UDR事件中断)。所以slave在第一帧会 发送dummy数据,第二帧及后续都发送underrun pattern数据(由UDRCFG 字段进行定义)。

图3. UDRDET=1并且在开始传输时TXFIFO为空

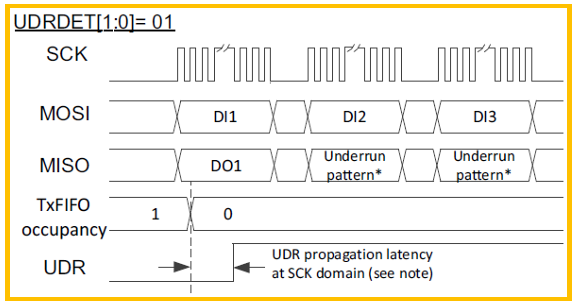

2. 在传输过程中TXFIFO变为空的情况。当TXFIFO变为空的时候,会产生下溢事 件,slave会发送underrun pattern 数据(由UDRCFG字段进行定义)。 如下图所示,在第一帧发送时TXFIFO变为空,由于UDR(underrun)事件传播需 要占用几个SPI时钟周期,所以看到在实线位置处才能实际检测到UDR事件发生 (或者产生UDR事件中断)。Slave会在检测到UDR事件后发送underrun pattern 数据(由UDRCFG字段进行定义)。

图4. UDRDET=1并且在传输过程中TXFIFO变为空

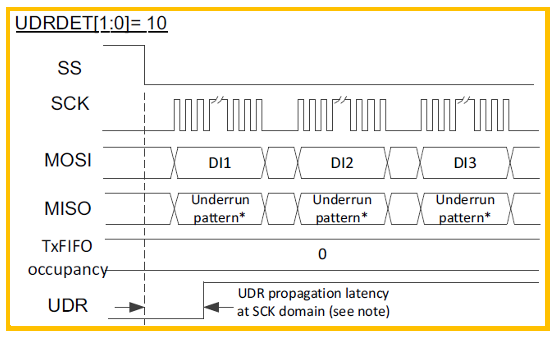

3.3. UDRDET = 2

当UDRDET=2的时候,在激活SS信号时就开始检测是否产生了下溢。当检测到下溢 事件之后,如果SS信号没有翻转过的话,在每帧之后都会产生下溢事件(即使在已经清 除了SR寄存器的UDR位和TXFIFO不为空的情况下)。

如下图所示,在SS为低(激活SS信号)时,TXFIFO为空,所以会产生下溢事件 (虚线位置),由于UDR事件传播需要占用几个SPI时钟周期,所以在实线位置处才能 实际检测到UDR事件发生(或者产生UDR事件中断)。所以slave在第一帧会及后续都 发送underrun pattern 数据(由UDRCFG字段进行定义)。

图5. UDRDET = 2

4. 小结

因为客户在使用过程中遇到过由于下溢检测位置的配置导致的问题,借此机会在此做 些分享,旨在帮助大家理解STM32H7的下溢检测特性及功能,供大家在实际应用中灵活 使用。

意法半导体公司及其子公司 (“ST”)保留随时对 ST 产品和 / 或本文档进行变更的权利,恕不另行通知。买方在订货之前应获取关于 ST 产 品的最新信息。 ST 产品的销售依照订单确认时的相关 ST 销售条款。 买方自行负责对 ST 产品的选择和使用, ST 概不承担与应用协助或买方产品设计相关的任何责任。 ST 不对任何知识产权进行任何明示或默示的授权或许可。 转售的 ST 产品如有不同于此处提供的信息的规定,将导致 ST 针对该产品授予的任何保证失效。 ST 和 ST 徽标是 ST 的商标。若需 ST 商标的更多信息,请参考 www.st.com/trademarks。所有其他产品或服务名称均为其 各自所有者的财 产。 本文档是ST中国本地团队的技术性文章,旨在交流与分享,并期望借此给予客户产品应用上足够的帮助或提醒。若文中内容存有局限或与ST 官网资料不一致,请以实际应用验证结果和ST官网最新发布的内容为准。您拥有完全自主权是否采纳本文档(包括代码,电路图等)信息, 我们也不承担因使用或采纳本文档内容而导致的任何风险。 本文档中的信息取代本文档所有早期版本中提供的信息。 © 2020 STMicroelectronics - 保留所有权利