PCIe 枚举设备 学习

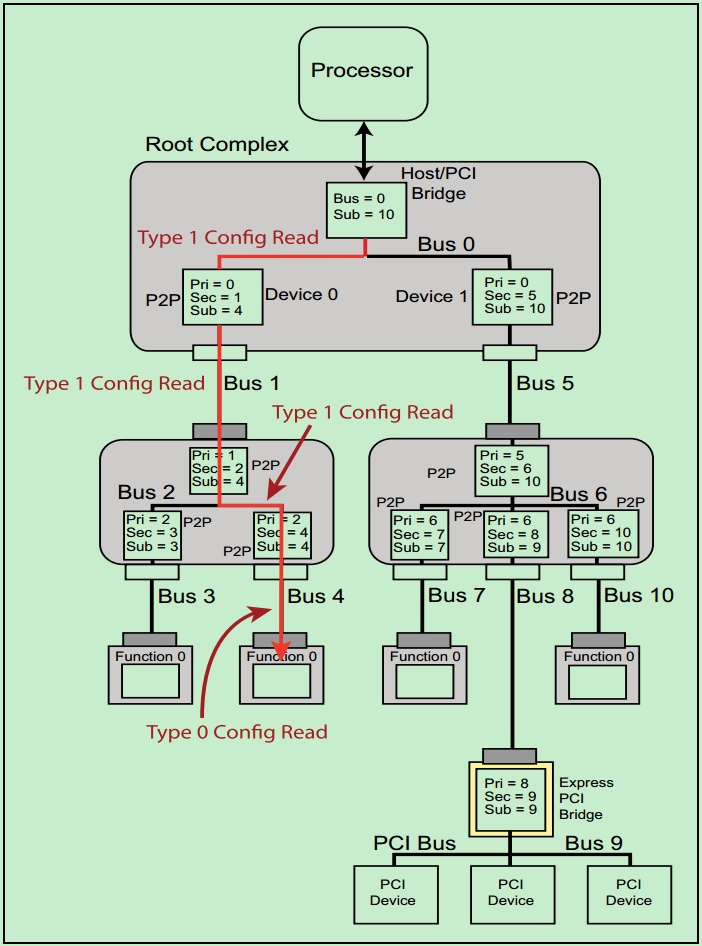

一 PCIe 拓扑结构

二 PCIe 配置空间

2.1 标准空间配置头 64bytes

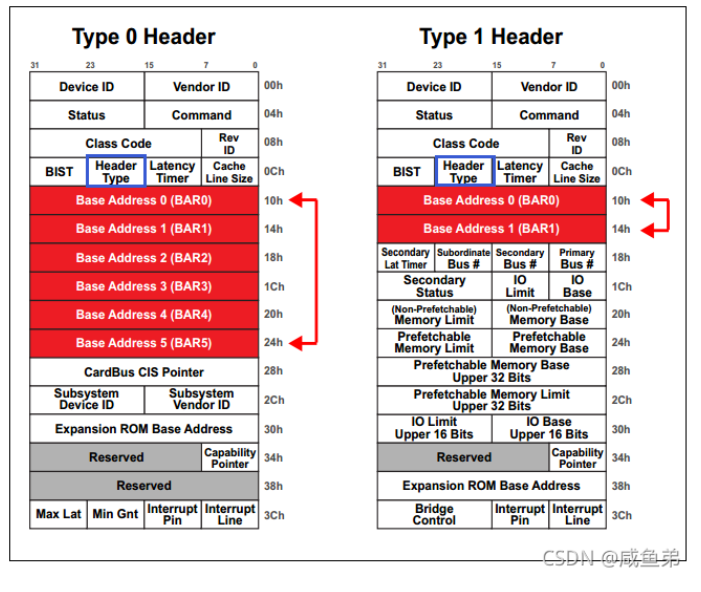

配置空间的头部有两种类型,Type0与Type1,分别给非桥设备(Endpoint),和桥设备(Root和Switch端口中的P2P桥)来使用,配置头部的对比如下图所示。

bar0

bar1

bar2

bar3

bar4

bar5

expansion rom base address

PCIe中只有Root才可以发起配置空间读写请求,并且我们知道Root的每个端口中都包含有一个P2P桥。当Root发起配置空间读写请求时,相应的桥首先检查请求的BDF中的Bus号是否与自己的下一级总线号(Secondary Bus Number)相等,如果相等,则先将Type1转换为Type0,然后发给下一级(即Endpoint)。如果不相等,但是在自己的下一级总线号(Secondary Bus Number)和最后一级总线号(Subordinate Bus Number)之间,则直接将Type1型请求发送给下一级。如果还是不相等,则该桥认为这一请求和自己没什么关系,则忽略该请求。

注:Root最先发送的配置请求一定是Type1型的。非桥设备(Endpoint)会直接忽略Type1型的配置请求。

2.1.1 type0 字段解读

2.1.2 type1 字段解读

2.2 PCIe 配置空间 100bytes

2.3 PCIe扩展扩展空间 436 bytes

AER(56bytes)

sriov(60bytes)

ARI

TPH

ACS

PSAID

2.4 ep、bridge

Type0与Type1,分别给非桥设备(Endpoint),和桥设备(Root和Switch端口中的P2P桥)来使用

2.4.1 ep

Type0给非桥设备(Endpoint),配置空间有6个bar地址。

2.4.2 bridge

Type1给桥设备(Root和Switch端口中的P2P桥)来使用。

2.4.3 dsp ( Downstream port)、usp (Upstream Port)

下游传输 (Downstream)

Root Complex (RC) 端口:只有Downstream Ports,所有数据从RC流出是"下游",流入是"上游";

Switch 端口:1个Upstream Port:连接上级设备(RC或其他Switch);N个Downstream Ports:连接下级设备(EP或其他Switch);内部实现虚拟PCI-to-PCI桥接

Endpoint (EP) 端口:只有Upstream Port

2.5 PCIE switch、multi-host

三 TLP报文格式

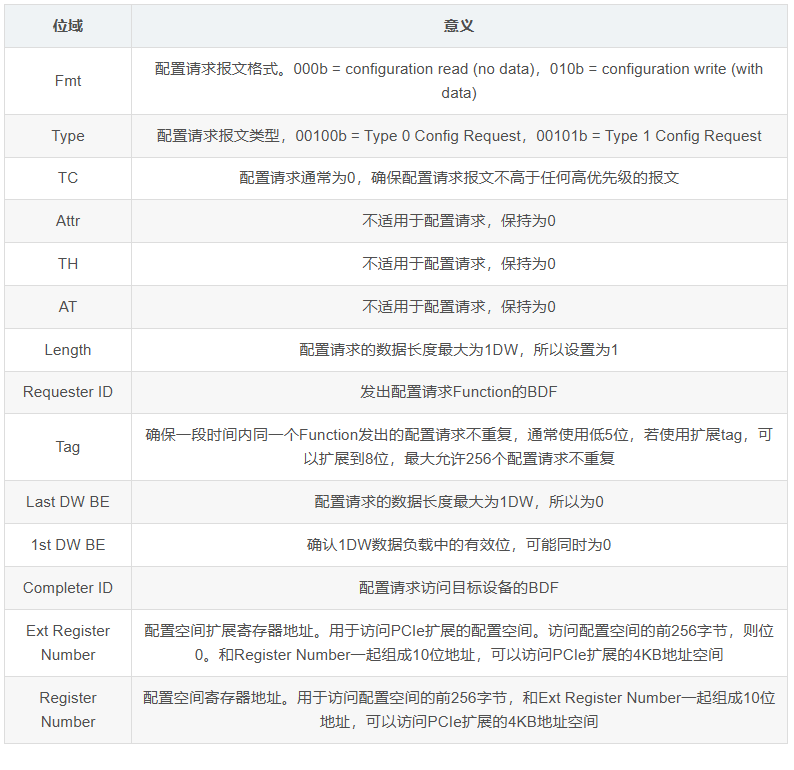

Configuration Requests、IO Requests、Memory Requests、completion

3.1 TLP报文

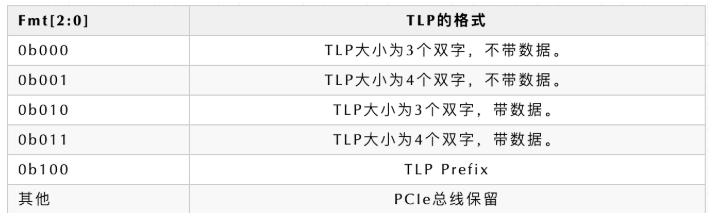

3.1.1 header 前一字节fmt格式

低一位 表示:是3DW,还是4DW

低第二位 表示: 是否携带数据

3.1.2 header 前一字节type格式

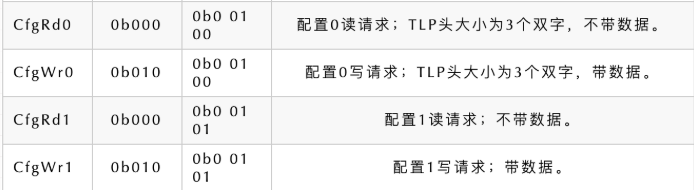

配置0 、配置1 指的是 PCIE配置空间 type0 (ep)还是type1(switch)

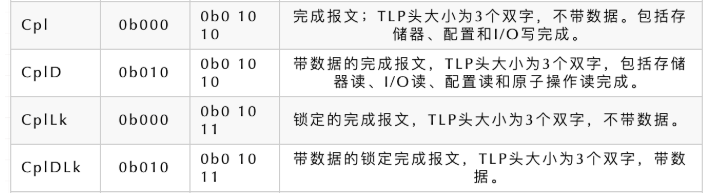

| TLP 类型 | fmt | type | 描述

- 配置空间 读写请求:设备枚举、配置和状态查询

- 存储器 读写请求:数据传输,访问的是通过BAR(Base Address Register) 映射到系统内存空间的地址

- I/O 读写请求:

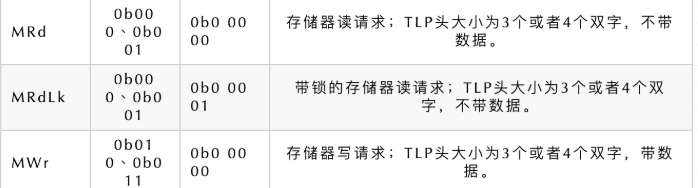

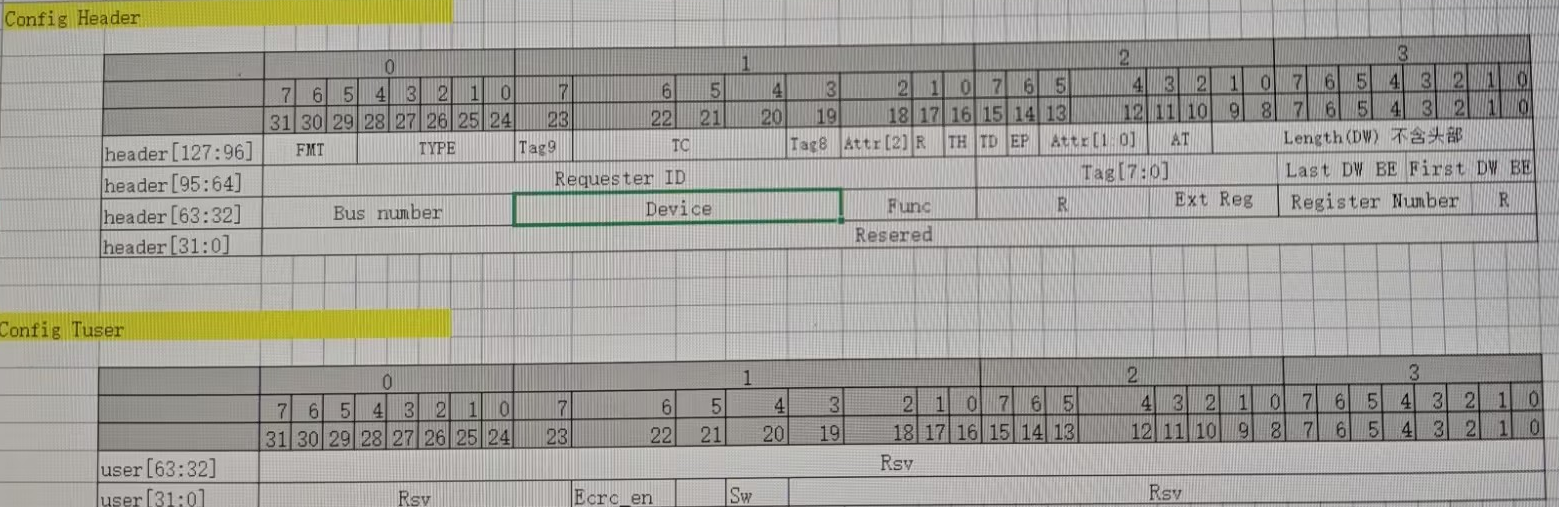

3.1.3配置读、写 报文字段

1st DW BE(First Double Word Byte Enable)作用:用于指示事务层数据包中第一个双字(Double Word,4个字节)内的哪些字节是有效的。PCIe总线以双字为单位进行数据传输,该字段通过位掩码的形式来标记有效字节。

取值含义:它是一个4位的字段,每一位对应**第一个双字中的一个字节**。例如,当该字段值为0xF(二进制为1111)时,表示第一个双字的全部4个字节都是有效的;若值为0x1(二进制为0001),则表示只有第一个双字的最低字节是有效的。在配置请求等操作中,它帮助接收方准确识别数据的有效部分,避免处理无效数据。

Last DW BE(Last Double Word Byte Enable)作用:与1st DW BE类似,不过它是用于指示事务层数据包中**最后一个双字**内的有效字节情况。同样使用位掩码来确定最后一个双字中哪些字节包含有效数据。取值含义:也是4位字段。如你提供的截图所说,在配置请求的数据长度最大为1DW(一个双字)的特殊情况下,Last DW BE为0。一般情况下,根据实际数据在最后一个双字中的有效字节范围来设置相应位。比如最后一个双字只有前两个字节有效,那么该字段值可能为0x3(二进制0011)。Ext Register Number

Register Number :重要

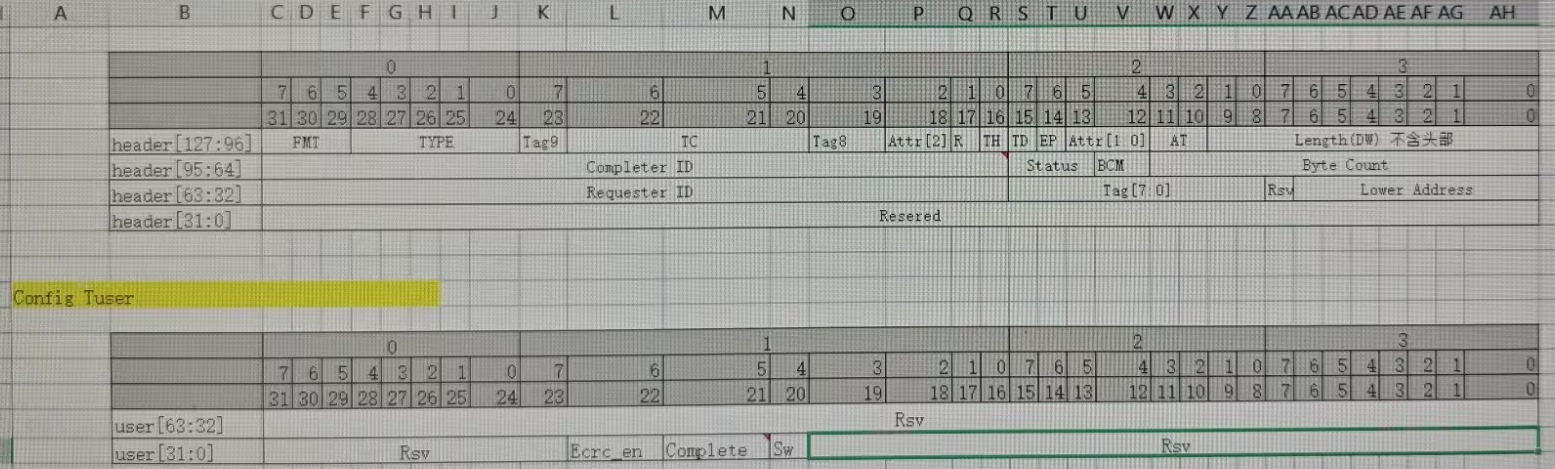

3.1.4 完成报文格式

接下里的四字节 用于 读到的数据带回。

3.2 TLP交互

深入解析PCIe地址空间与寄存器机制:从地址映射到TLP生成的完整流程

CPU访问一个地址,导致PCIe控制器发出TLP。TLP里含有PCIe地址、其他信息。

3.2.1 配置读

3.2.2 配置写

写请求的核心是“执行命令”,而非“获取信息”。它的目标是修改设备的配置寄存器。

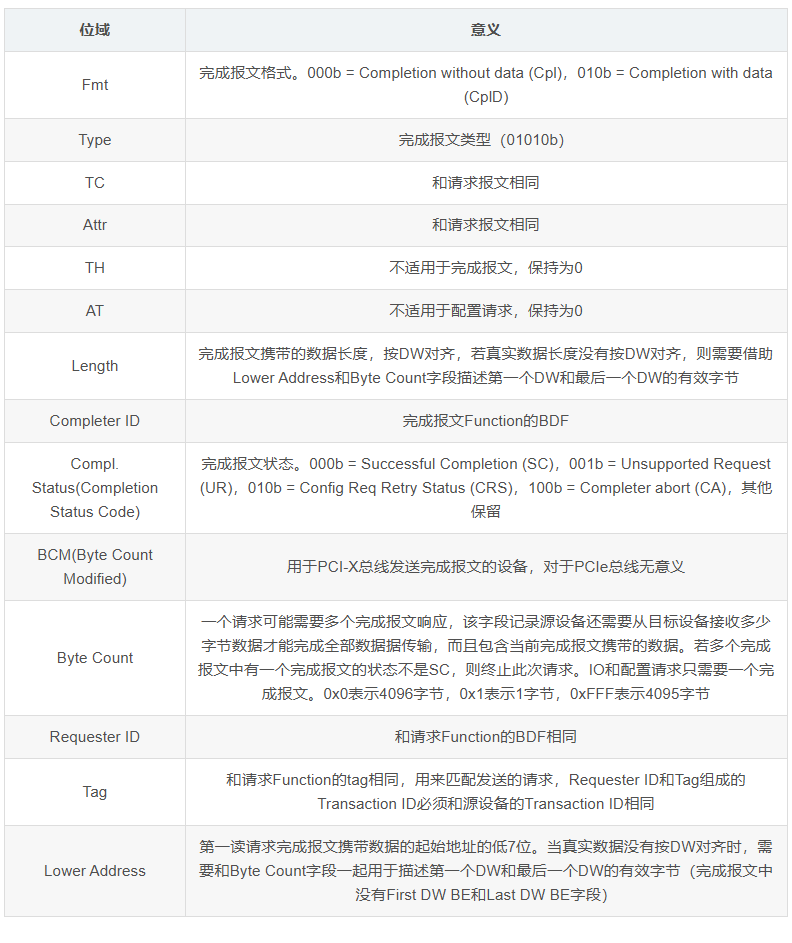

(1)bar寄存器字段

**注意:**Type 0报头有6个bar可用(每个bar的大小为32位);有memory bar 、I/O memory. 即bar 寄存器 会指示该该地址映射的空间是哪种访问(memory 访问、I/O访问)

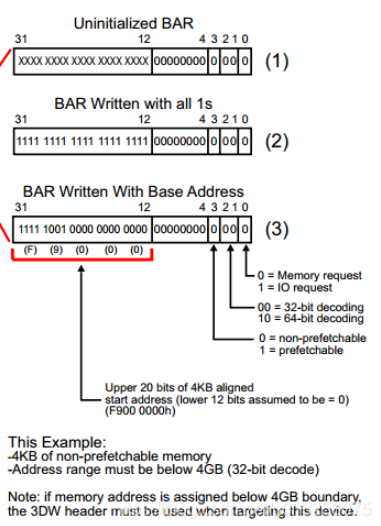

memory bar

- bit0:表示设备寄存器是映射到memory(0)还是IO(1)空间。

- bit2:1: 在base adress register for Memory 中0表示32位地址空间,1表示64位地址空间。

- bit4~31:用来表示设备需要占用的地址空间大小。

- 针对bit4~31,某些位为只读,且0来表示需要的地址空间大小,比如一个PCI设备需要占用1MB的地址空间,那么这个BAR就需要实现高12bit是可读写的,而20-4bit是只读且为0。

BAR(Base Address Register)详解

(2)bar空间作用及配置过程(确定地址范围和类型)

-

选择用 IO映射 还是 内存映射 方式来访问一个地址,完全是由CPU的硬件设计决定的;即 访问某块 寄存器时 使用的函数不一样;以及 访问 哪个地址段 —PCIE设备必须为系统软件提供一种方法来确定设备的地址空间需求,这种需求就是是通过**配置空间头部中的Base Address register (BAR)**实现的。

-

IO映射

普通内存读写指令,高,可直接用C指针操作 -

内存映射

-

地址空间大小的计算方法如下:

BAR配置过程

a.向BAR寄存器写全1

b.读回寄存器里面的值,然后clear 上图中特殊编码的值,(IO 中bit0,bit1, memory中bit0-3)。

c.对读回来的值取反,加一就得到了该设备需要占用的地址内存空间。

其中,当系统软件向 BAR 写入地址空间的起始地址时,这个地址是在主机的地址映射体系中为 PCIe 设备分配的地址,用于主机访问该设备的相关内存区域。主机通过这个地址来访问 PCIe 设备映射到主机地址空间的内存区域。

multi-host 模式下:

(3)TLP配置写流程

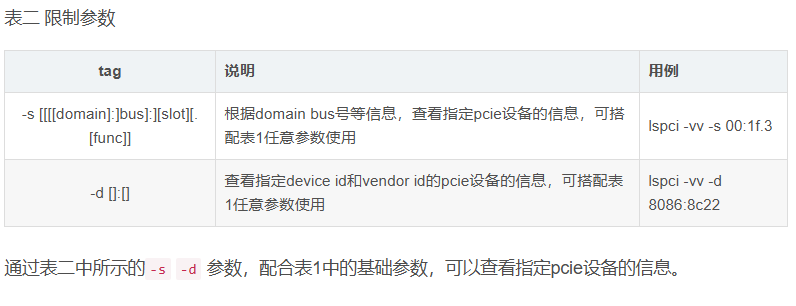

四 lspci 命令行解读

lspci 命令用于显示连接到 PCI 总线的所有设备。

-v ,lspci 会显示所有设备的各种子系统和内存地址、中断请求(IRQ)编号和一些其他功能信息。

五 软件模拟dsp

六 软件模拟ep

注意:

(1)PCIe协议规定,配置读请求必须至少请求 1DW 的数据。4字节

(2)DW 是 Double Word 的缩写。

(3)在x86架构和PCIe协议中,一个 Word 通常指 16位。2个字符即2个byte,=16bit

(4)一个 Double Word 就是 32位,即 4个字节。

-

host 上电时,bios会去(总线扫描、设备发现、配置空间读取、BAR设置、中断分配)枚举pcie总线设备 ,这时会生成TLP报文去交互。(是host 操作系统启动时自主发送TLP)。

-

软件模拟了bridge、pf、vf,逻辑内部处理TLP报文时

→可以自己内部处理,

→可以转发到软件,软件进行处理

有一个开关,即某个配置控制,可以让逻辑自己处理或者选择软件处理。目前软件实现只支持Configuration Requests。 不处理IO Requests、Memory Requests。

最后lspci 枚举成功后,会有更多device设备。

- 在整个调试过程,目标为 (1) 枚举成功,(2)pf驱动注册成功