【FPGA】设计流程——仿真验证

一、设计仿真源文件

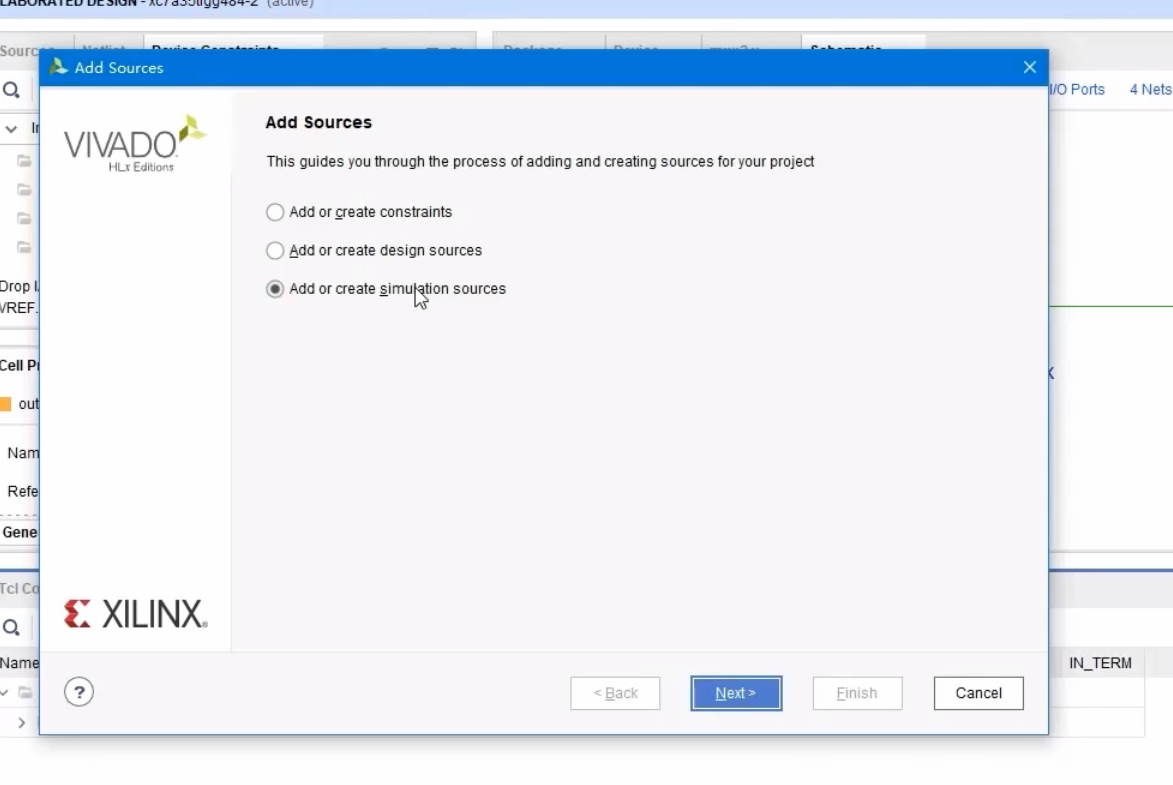

新建源文件,选择第三个

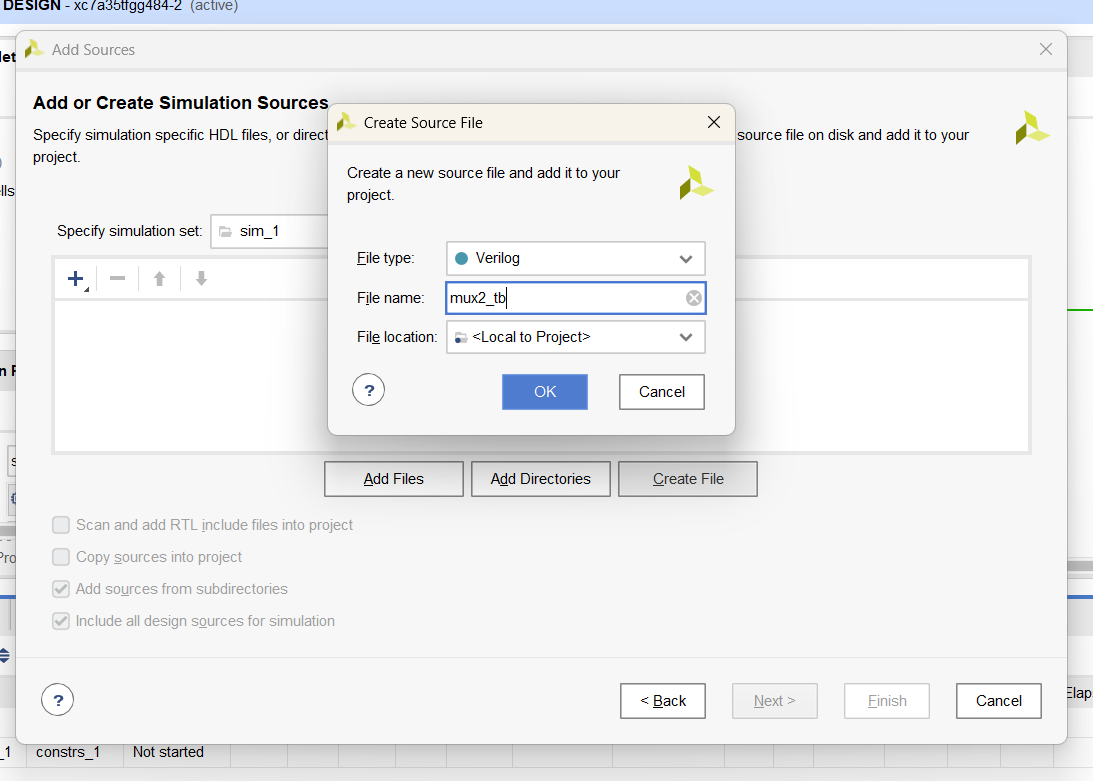

点击create file,给文件命名为mux2_tb,tb是test bench,加这个后缀以便告诉代码编写者

点击OK,点击finish,点击OK,点击yes

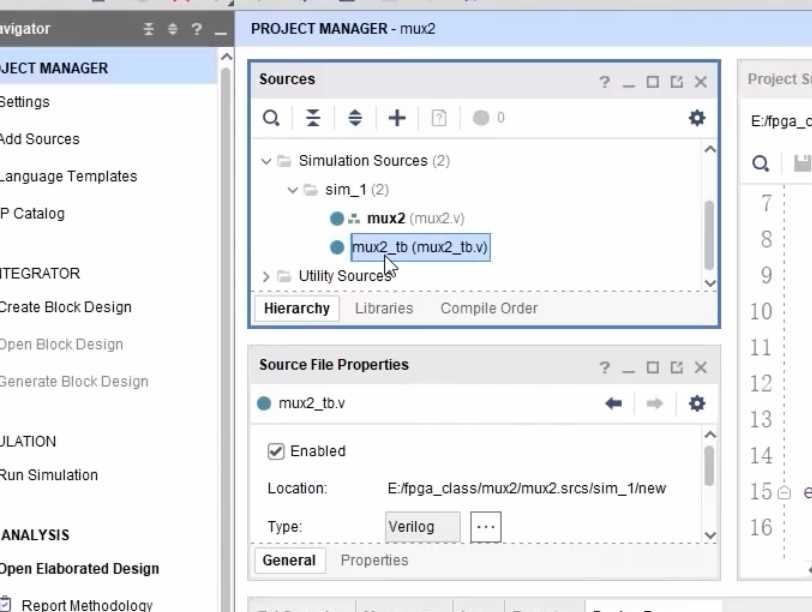

在这里可以看到刚刚生成的文件

二、编写代码

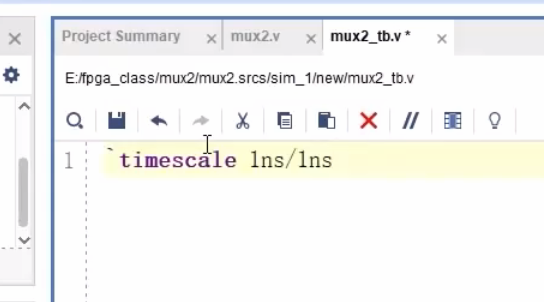

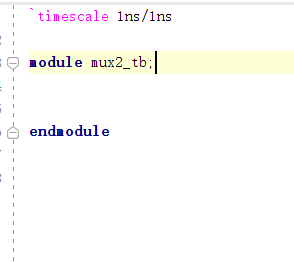

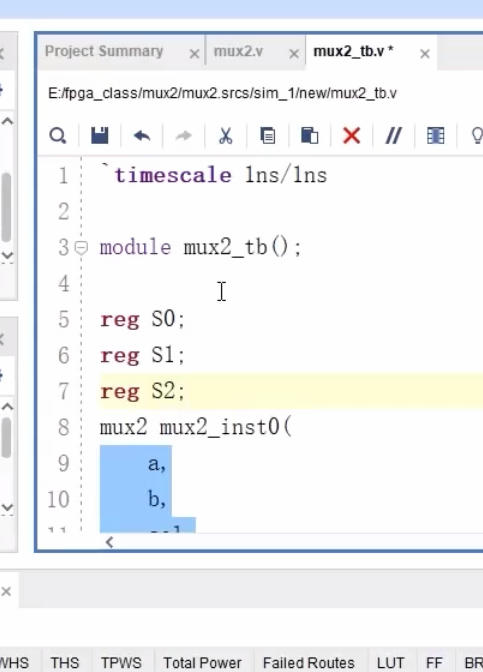

开头

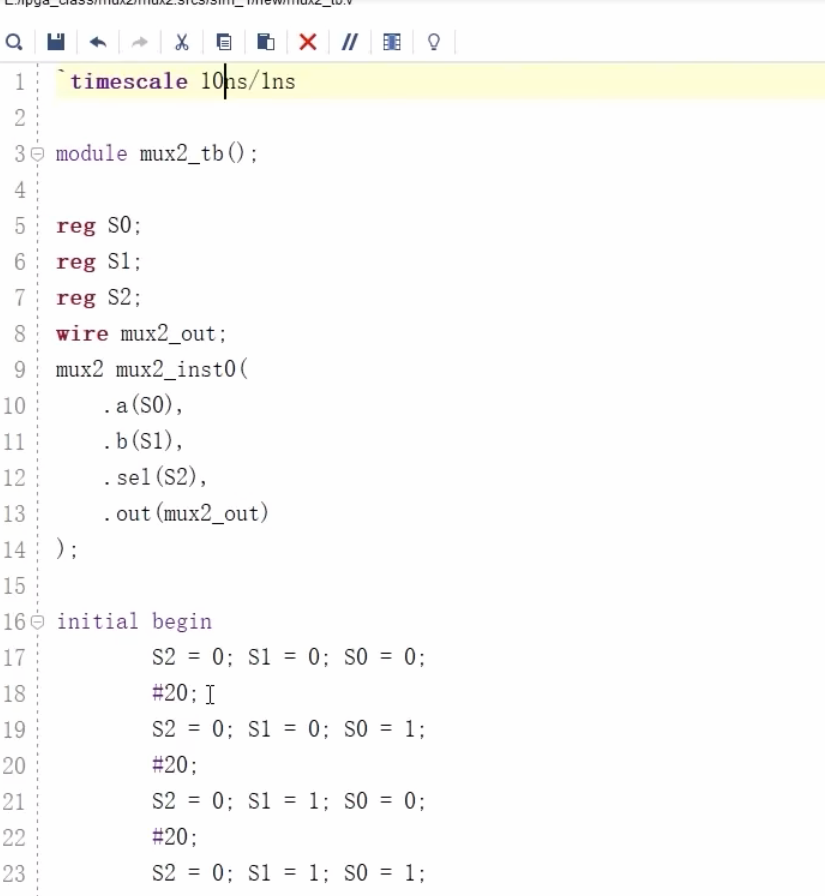

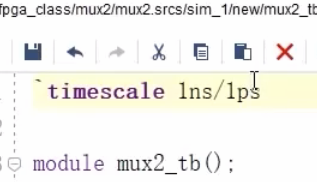

`timescale 1ns/1ns

- timescale 是语法标准的保留词,代码仿真时用到的延时语句的单位和精度

下面是模块的开头,结尾和名称

仿真文件不需要接口类型,可以不写,包括括号

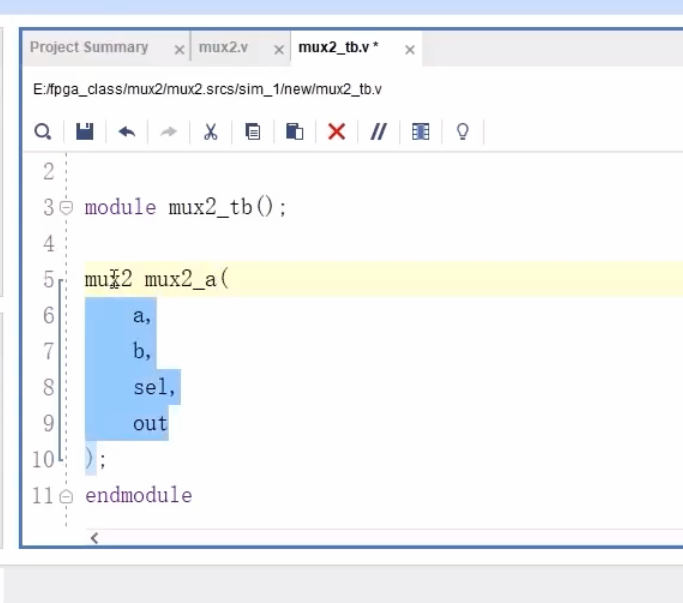

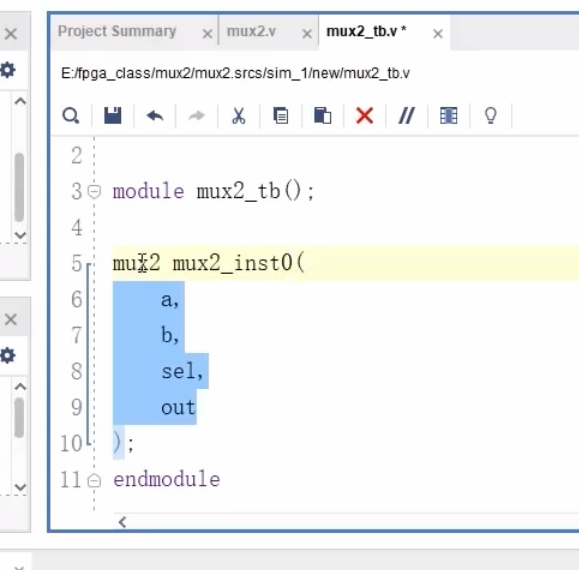

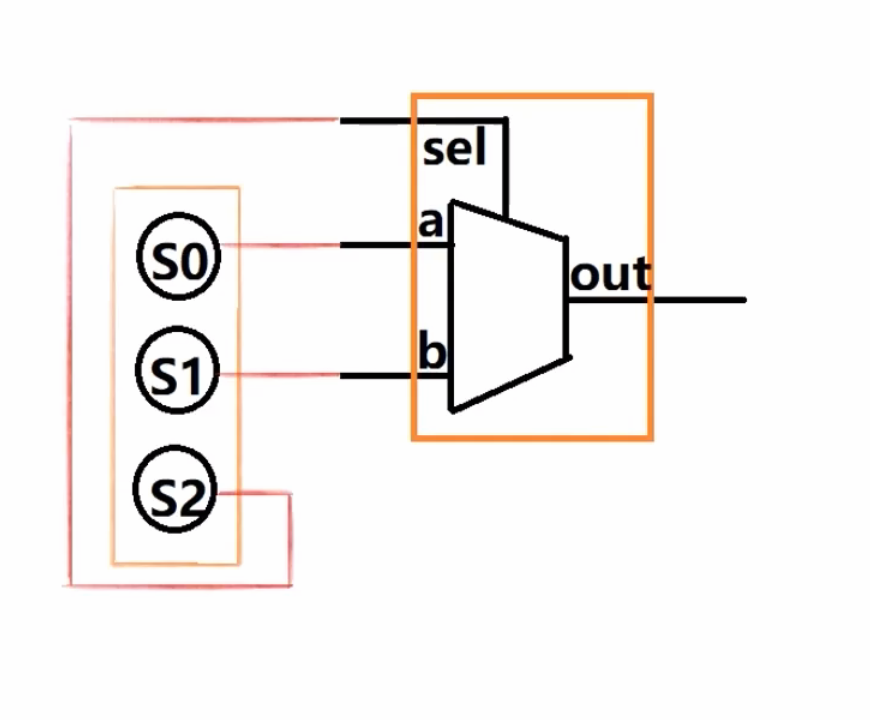

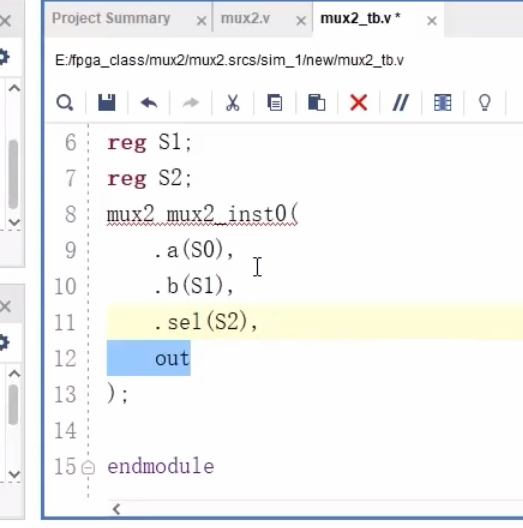

例化

复制想要测试的名称和端口列表到test bench里来

当出现两个相同的模块时,可以在模块名称后面空格然后重新命名

注意名称不能和端口名重复

定义信号

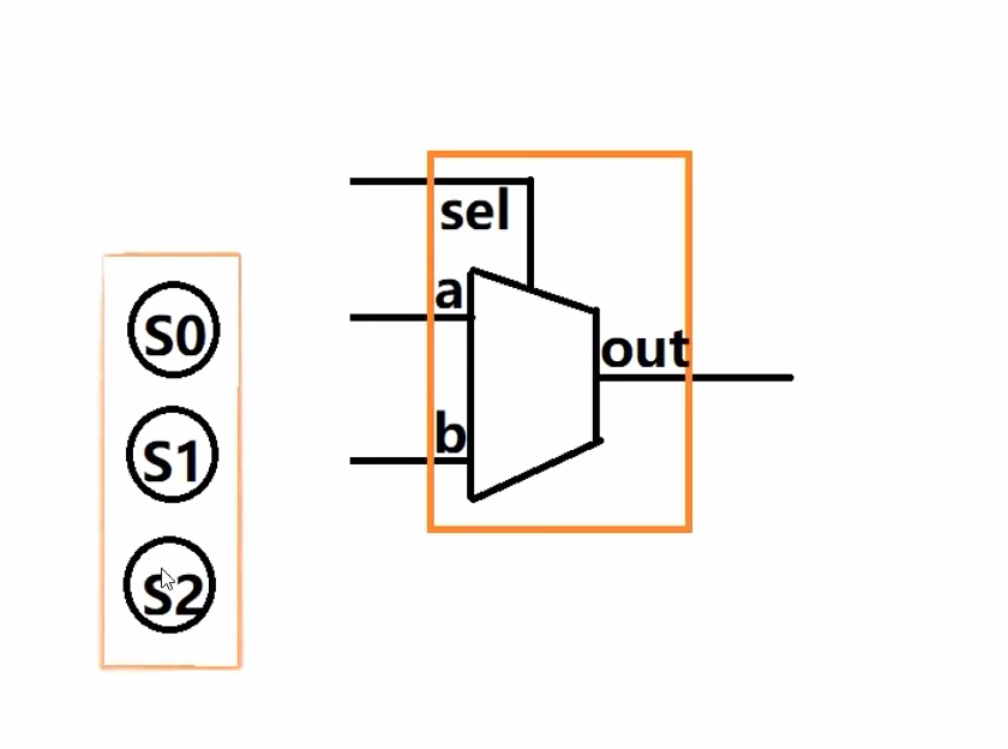

信号发生器的三个信号输入端口S0 S1 S2

对于随时需要修改值的信号,用reg来定义

激励信号与测试端口连接

将端口前加.后面用括号加要连接的信号名

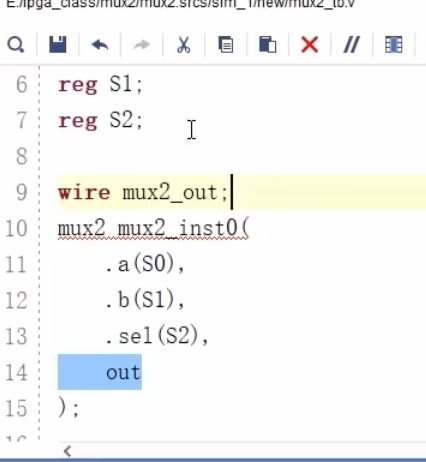

输出端口

对于输出端口,只需要连接一根导线进行观察就可以

用wire

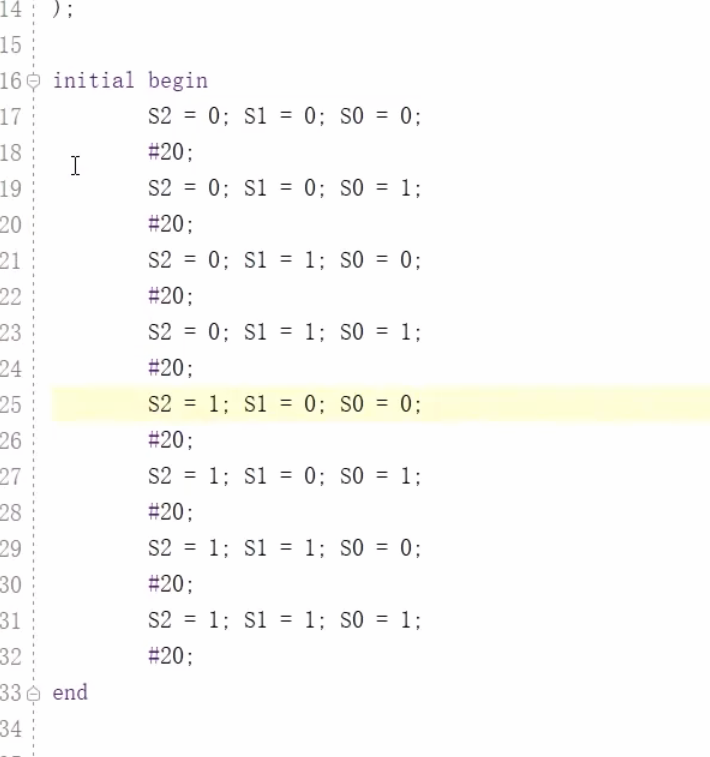

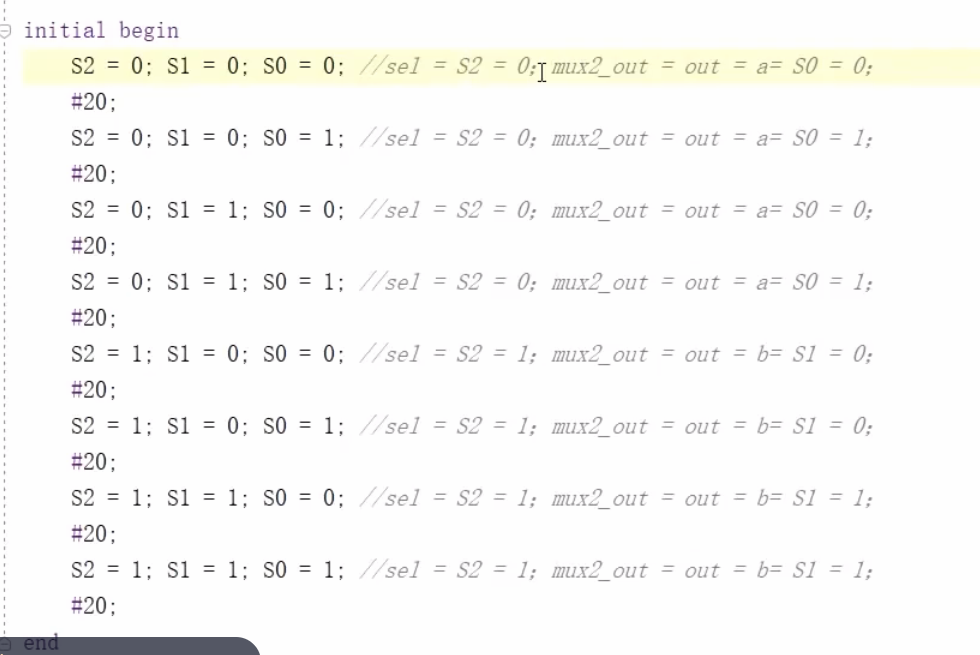

产生激励信号

initial 从仿真的零时刻开始执行

- #20;代表在仿真时间线上向后推行20ns,ns取决于刚开头的定义单位,只能用于仿真测试

如果这样写就是延时20个10ns

/后面代表延时的精度,代表每次延时的最小单位,

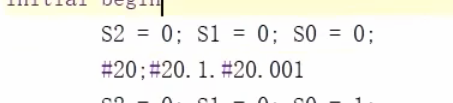

如果这样写就是1ps为最小精度,

那么这里就可以写小数点

三、用vivado自带仿真软件进行仿真

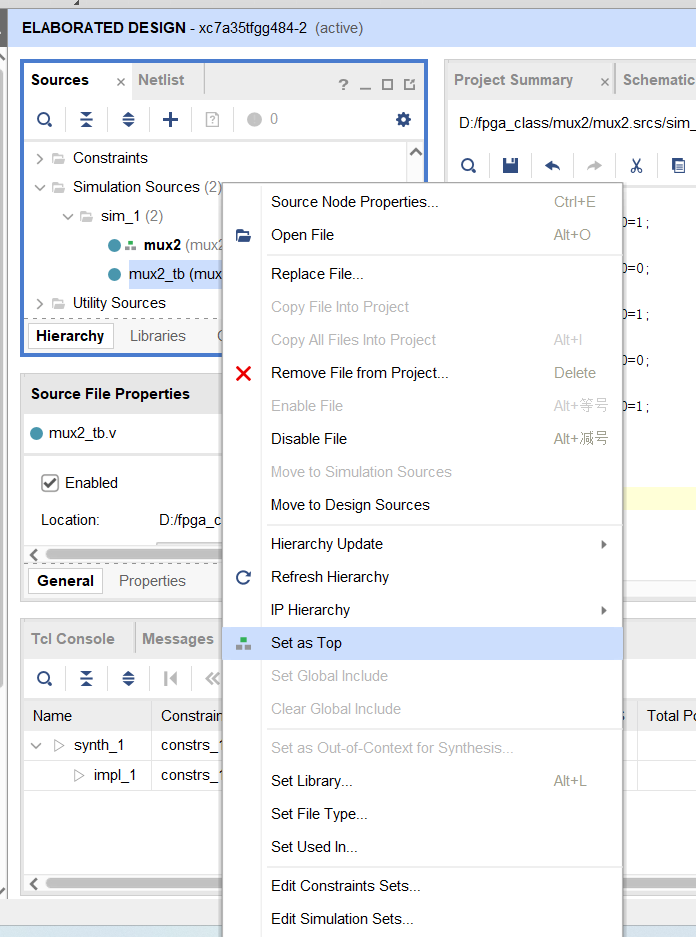

将该文件设置为顶层

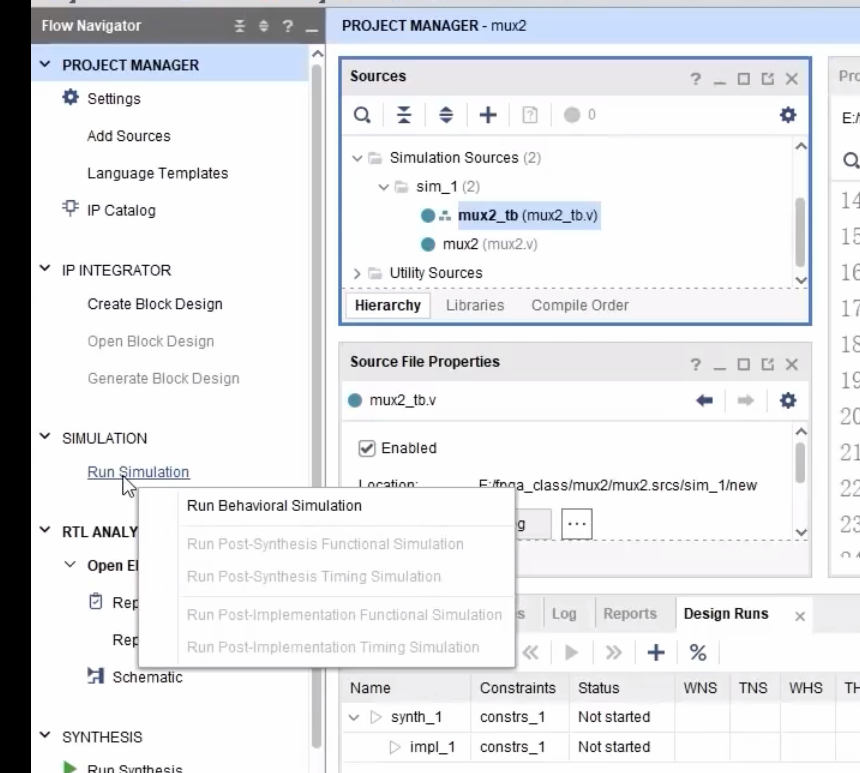

点击左侧run simulation

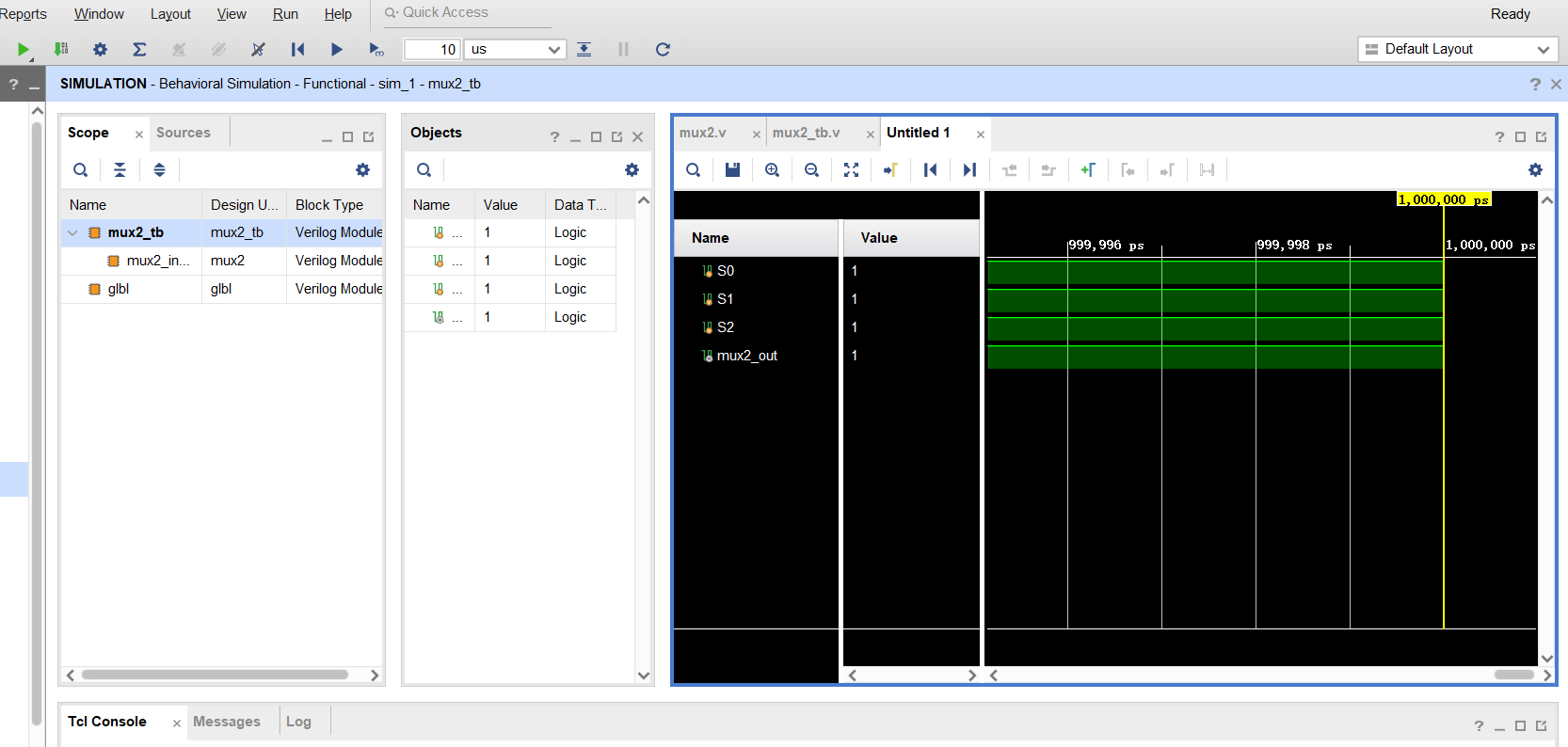

就出现了仿真波形

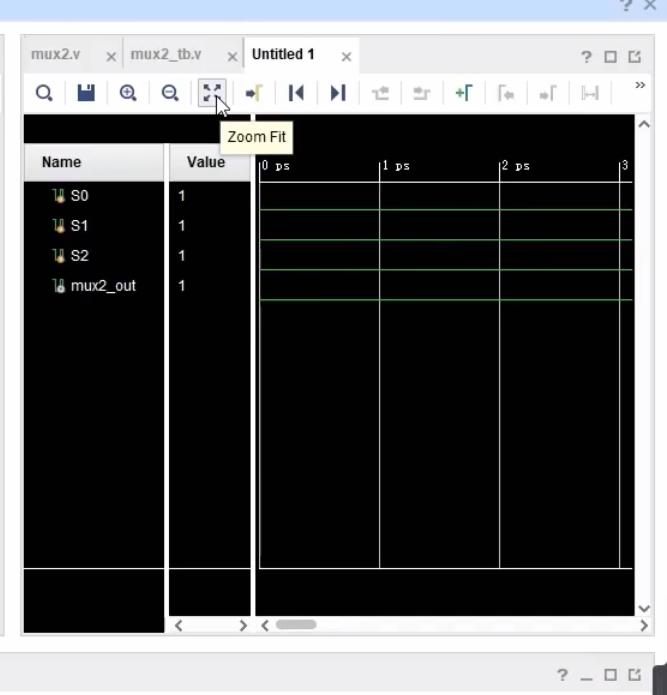

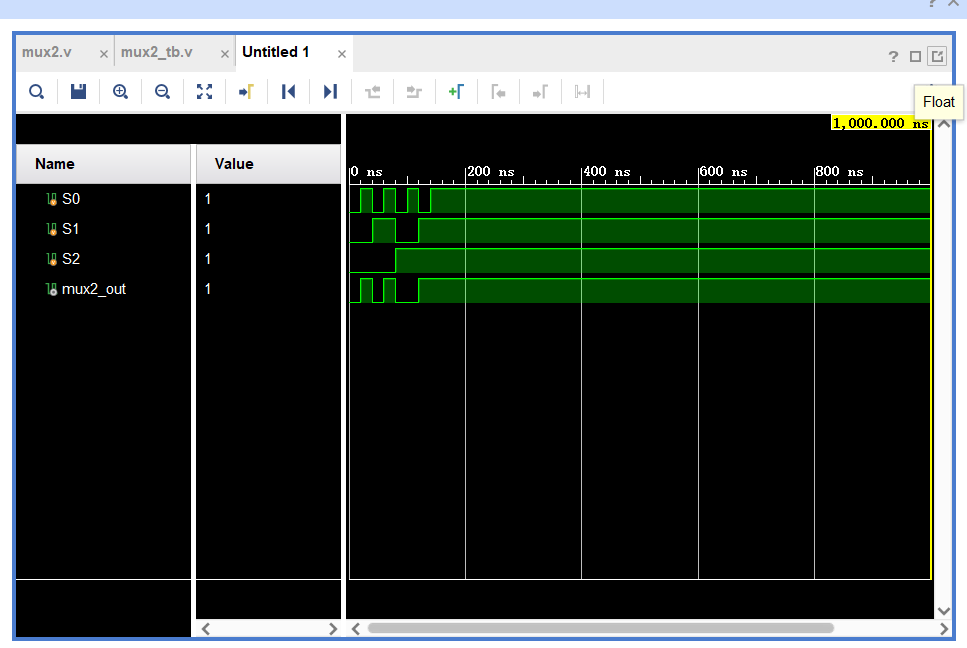

拖动下面的进度条,可以看个时刻波形,点击这个预览全局按钮,可以看完整波形

点击右上角的float可以单独脱离放大进行观察