基于半桥结构的双极性脉冲电源的研究

为了满足脉冲电场消融的应用需求,解决单极性脉冲电场分布不均匀的问题,研制了一台基于半桥结构的主电路、具有纳秒级前沿的高重复频率双极性亚微秒高压脉冲电源。该脉冲电源由 FPGA 提供控制信号,经过驱动芯片放大控制信号后,利用光耦隔离驱动多个 SiC MOSFET。驱动电路所需元器件较少,信号控制时序简单,可提供负压偏置,使开关管可靠关断,提高了电路的抗电磁干扰能力,使电源能稳定运行。通过电阻负载实验,对比分析了不同栅极电阻对驱动电压的影响,驱动电压上升沿时间越短对应的双极性高压脉冲前沿越快。实验结果表明:所设计的高频双极性脉冲电源在 100 Ω 纯阻性负载上能够稳定产生重复频率双极性纳秒脉冲,输出电压 0~±4 kV 可调,脉宽 0.2~1.0 μs 可调,正负脉冲相间延时 0~1 ms 可调,上升沿和下降沿 60~150 ns之间。该双极性脉冲电源电路设计结构紧凑,能满足应用的参数需求。

近年来,随着脉冲功率技术的不断发展,高压脉冲电源广泛应用于能源[1]、工业加工[2-4] 和医疗器械[5] 等领域。最近的研究表明,双极性脉冲电源产生的双极性脉冲电场所引起的不可逆电穿孔[6] 效应,能改善单极性脉冲电场分布不均和肌肉严重收缩的问题。例如,抑制冷却水中的微生物和藻类等应用中,高频双极性脉冲的抑制效果更为明显[7]。微秒脉冲电场作用在细胞外膜时,可以诱导博来霉素及顺铂等细胞毒性物质进入细胞内部,从而实现相对安全的靶向消融肿瘤[8]。当脉冲宽度降低至纳秒级,由于脉冲宽度较窄,高频率含量增加[9],电场强度在10~100 kV/cm 的高压脉冲时(nsPEF),可透过细胞膜的屏蔽作用,使电场直接作用到细胞胞内。纳秒脉冲电场靶向作用于胞内细胞器,将会诱导与微秒脉冲截然不同的生物电效应[10],如内部颗粒的通透性、内源性液泡[11] 和细胞的收缩及肿胀[12]、细胞核的 DNA 受损、细胞坏死或凋亡[13]。随着纳秒脉冲电场强度的提高,完成电穿孔所需的时间就会减少[14]。许多学者对全固态高压双极脉冲发生器进行了一些研究。产生双极性高压脉冲的传统方法是使用全桥逆变电路和高频升压变压器。这种方法有许多缺陷。例如,由于高频变压器的泄漏电感,上升/下降边沿不够陡峭。而 L. M. Redondo 通过 Marx 单元级联的方式研制了输出脉冲±5 kV,脉宽 2.5 μs,前沿 200 ns 的双极性 Marx发生器[15]。葛劲伟研制了电源输出±4 kV、最小脉宽 600 ns 的方波窄脉冲的全固态高压双极性脉冲叠加器[16]。石小燕研制了一台最高幅值可达 10 kV、瞬态频率达 400 kHz 的高重复频率高压脉冲电源[17]。也有学者提出了将两台 Marx 结合的方法,通过分别控制两台 Marx 的导通时间就可以输出双极性脉冲,但这种结构使用的开关管和储能电容是单极性 Marx 的两倍,采用复杂的控制方式,并且该结构不仅增加了元器件的数量,还不利于简化脉冲发生器的体积和控制成本等[18]。

综上所述,为了开发用于生物医学应用的脉冲功率发生器,提出了一种基于开关串联的半桥结构的主电路,产生具有纳秒级前沿的高重复频率的双极性亚微秒高压脉冲。本文首先介绍了该双极性脉冲电源的电路结构及其开关控制方法,说明了该发生器的工作原理,并开展了实验进行验证。实验中所用负载为 100 Ω 电阻,用于模拟细胞负载,输出了双极性亚微秒脉冲;研究了不同栅极电阻对脉冲边沿的影响、高压输出接不同负载对双极性脉冲输出性能的影响以及高压高频情况下对驱动信号产生的串扰问题等。

1 全固态双极性脉冲电源的设计

1.1 主电路拓扑设计

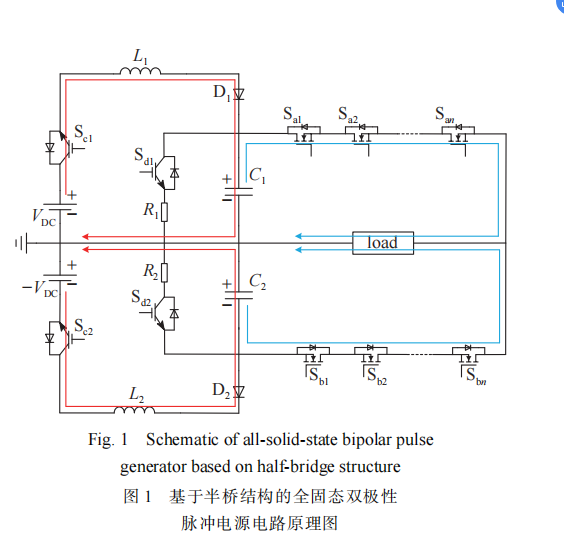

基于半桥结构的全固态双极性电路原理图如图 1 所示,它包括由开关管 Sc1、Sc2 控制给储能电容的充电回路,再分别控制上下桥臂的开关管导通,在负载上输出不同极性的高压脉冲。其中上下桥臂的开关管均采用耐压电压为 1 700 V的 SiC MOSFET 开 关 , 充 电 开 关 管 采 用 耐 压 为 4.5 kV 的IGBT,直流充电源 VDC 可提供最高 4 kV 的可调直流电压,储能电容选择由三个容量为 12 μF 耐压值 2 kV 的电容串联而成,电阻 R1、R2 为放电结束后用来泄放电容中残留的电荷的泄放电阻。

通过 FPGA 控制充电开关管 Sc1、Sc2 导通时序后,由高压直流电源给储能电容充电,当储能电容达到设置电压时,再同步导通放电开关管 Sa1-an 或 Sb1-bn,在负载上输出不同极性的高压脉冲。每组放电开关管的控制信号需要保证良好的同步性,稳定的同步驱动控制可以有效避免高频干扰导致的桥臂直通和器件损坏。由于放电开关管是通过串联提高耐压值,所以每一个放电开关管工作的过程中要考虑动静态均压问题及开关管之间的串扰问题;同一极性中驱动回路所用器件的选型需保持严格一致,否则会导致驱动信号的不同步,从而影响最终的高压输出波形。

1.2 主电路基本工作原理

基于半桥结构的全固态双极性主电路工作原理为控制高压直流电源给储能电容 C1、C2 充电过程,充电完成后由主电路中上下桥臂的开关管通断输出不同极性的高压脉冲方波,放电结束通过控制 Sd1、Sd2 闭合使其储能电容进行泄放电荷的作用。

充电回路如图 1 红色箭头所示,正极性的高压直流电源经过高耐压的充电管 Sc1、限流电感 L1 和二极管 D1 给储能电容 C1 充电,负极性的高压直流电源经过高耐压的充电管 Sc2、限流电感 L2 和二极管 D2 给储能电容 C2 充电。

放电回路如图 1 蓝色箭头所示,当储能电容 C1 充电至 VDC 时,关断充电开关管 Sc1,同时同步控制 6 个放电开关管 Sa1-an 导通,储能电容 C1 对负载放电,形成正极性脉冲;当储能电容 C2 充电至−VDC 时,关断充电开关管 Sc2,同时同步控制 6 个放电开关管 Sb1-bn 导通,储能电容 C2 对负载放电,形成负极性脉冲。

1.3 驱动电路及控制方案

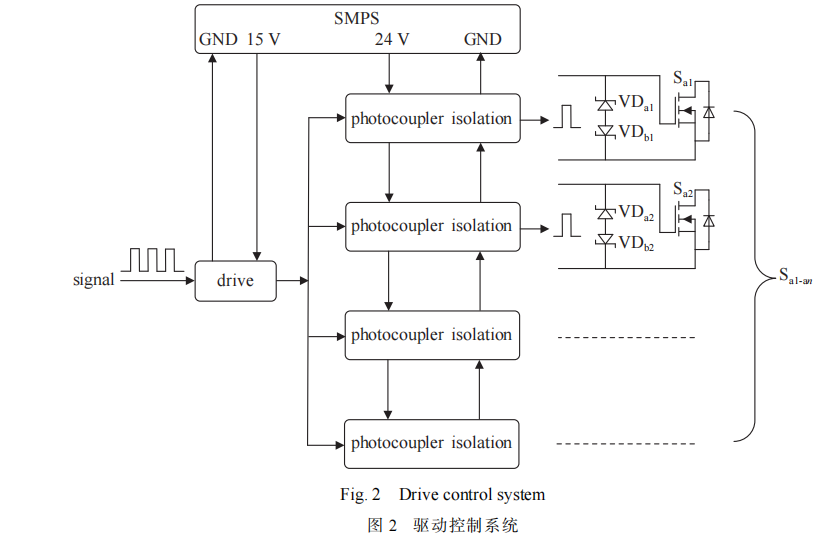

本文控制系统如图 2 所示,由 FPGA 输出触发脉冲信号控制所有开关管的导通和关断,触发信号经过传输线给驱动芯片 MCP1407,再通过光耦隔离器对驱动信号隔离,最终同步驱动多个 SiC MOSFET。触发信号的脉冲宽度、脉冲个数、重复频率以及死区间隔时间根据程序设定均为连续可调,通过控制触发信号来控制主电路的脉冲输出。所选用的驱动芯片稳定可靠、体积小、外围电路简单,可满足高频信号之间的传递。此外,为了实现 SiCMOSFET 的隔离驱动,驱动芯片和光耦隔离器的电源采用隔离的 DC-DC 转换器提供,参考地彼此隔离以提高驱动回路的抗电磁干扰能力。

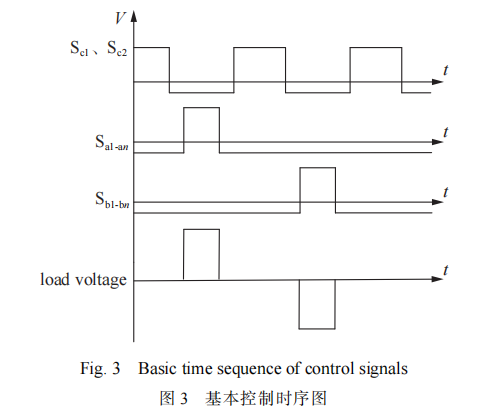

为了精准控制电路中所有开关管的导通和关断,本文利用 FPGA 输出触发脉冲信号,各开关对应的控制时序如图 3所示。控制充电回路的 Sc1 及 Sc2 同时导通给储能电容充电,充电结束后再输出触发脉冲信号控制一路脉冲电源上的开关管 Sa1-an 同时导通,调节触发信号延时时间,输出另一路脉冲电源中 Sb1-bn 的触发信号,使两路脉冲触发信号交错导通。

该驱动方案,在脉冲输出时提供负压偏置关闭充电开关管,放电结束后给充电开关管提供周期性的开通信号,使储能电容能够快速地充电,给放电管提供周期性的关断信号,并在门极施加负电压驱动信号确保其处于可靠关断状态。当放电管导通时,通过 FPGA 设定脉宽、脉冲相间延时、脉冲间隔及脉冲个数等参数可以输出特定的双极性脉冲波形。通过更改程序 FPGA 能输出百纳秒脉宽的触发信号,经过驱动芯片 MCP1407 增强驱动能力,再传输驱动信号到多个光耦隔离模块输入端,以同步驱动多个 SiC MOSFET 可靠导通和关断,调节驱动回路器件参数可以输出百纳秒脉宽的高压脉冲。

1.4 串联均压设计

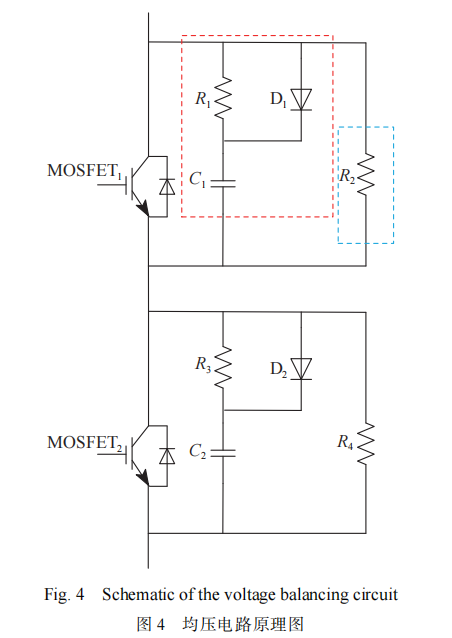

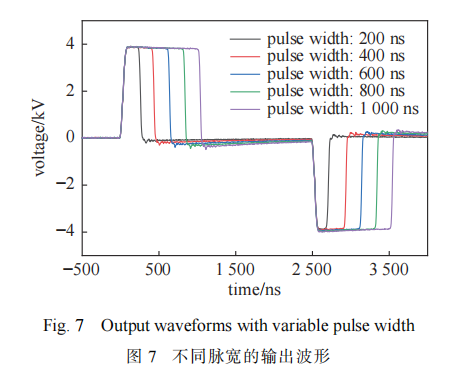

图 4 为主电路中放电开关管动静态均压的措施,SiC MOSFET 串联运行过程中,由于驱动信号延时会造成电压不均衡。目前研究发现电压不均衡主要发生在开关管关断的过程中电压上升的阶段,而在导通阶段中电压下降也同样存在电压失衡[19]。功率侧由于器件关断状态下阻抗不匹配,静态均压仅在器件漏源极两端并联无感均压电阻R2 与 R4,保证稳态时每个开关管所承受的电压相同,以保护开关管不被过压击穿,考虑每只开关管静态时承受的电压值,此处取 R2 为 250 mW/10 MΩ。当电压快速变化阶段产生的严重电压尖峰让 MOSFET 瞬间过压损坏,此时就需要在MOSFET 功率端并联 RCD 缓冲电路以实现动态均压。该RCD 缓冲电路[20-21],通过无感电容 C1 和高频且快速恢复的二极管 D1 实现动态电压均衡,可选取电容 C1=4.7 nF,R1=5 Ω。RCD 缓冲电路在实际应用中,动态均压电容 C1 参考公式[22]

式中:τ 为脉冲宽度。当 MOSFET 在关断过程中出现电压不均衡现象时,MOSFET 的漏源极电压开始升高,通过二极管D1 向电容 C1 充电,此时 C1 的存在会避免 MOSFET 的漏源极电压瞬间升高;当 MOSFET 从关断状态变为导通状态时,如果 MOSFET 的漏源极电压过高,由于电容 C1 的电压不能突变,使得 MOSFET 的漏源极电压钳位至电容 C1 两端,当 MOSFET 的漏源极电压开始下降时,电容 C1 通过电阻 R1 进行放电。此缓冲电路能够抑制串联 MOSFET 端电压的变化速率,通过吸收过电压来减小各 MOSFET 间的动态电压差,解决了 MOSFET 开关频率特性不一致而导致电压分配不均的问题。

2 实验结果与分析

通过上述理论分析,本文研制了一台基于半桥结构的全固态双极性脉冲发生器样机,实验中对所设计的脉冲发生器进行了低负载实验,通过调节高压直流电源的电压可输出不同幅值的高压脉冲。实验使用的采样带宽 200 MHz,采样率 4 GSa/s 的数字示波器 HDO4204(RIGOL)和高压探头 RP1100D 来记录实验数据。

2.1 脉冲发生器边沿调节验证

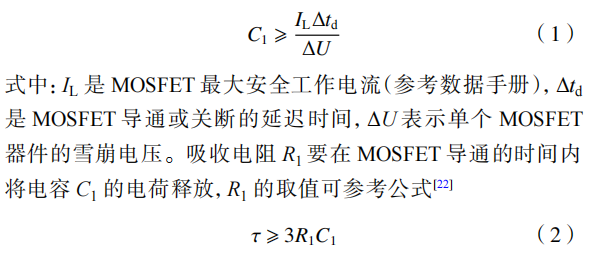

通过对 SiC MOSFET 驱动电路的分析,可以调节驱动电阻 Rg 阻值的大小获得不同的脉冲上升沿时间,从而双极性脉冲发生器可以输出更窄的脉冲波形。从图 5 可以看出,随着驱动电阻 Rg 的阻值增大,驱动电压的上升时间及下降时间变的更加缓慢。为了获得更快的脉冲上升沿,需使用较小的驱动电阻 Rg,并考虑驱动回路电感量的大小对驱动波形的影响,在设计驱动电路时要减小驱动回路面积及回路电感量,图 5(b)为不同驱动电压的脉冲输出波形,Rg 阻值越小输出电压的平顶振荡越明显,脉冲上升沿的时间越短。

2.2 实验结果及分析

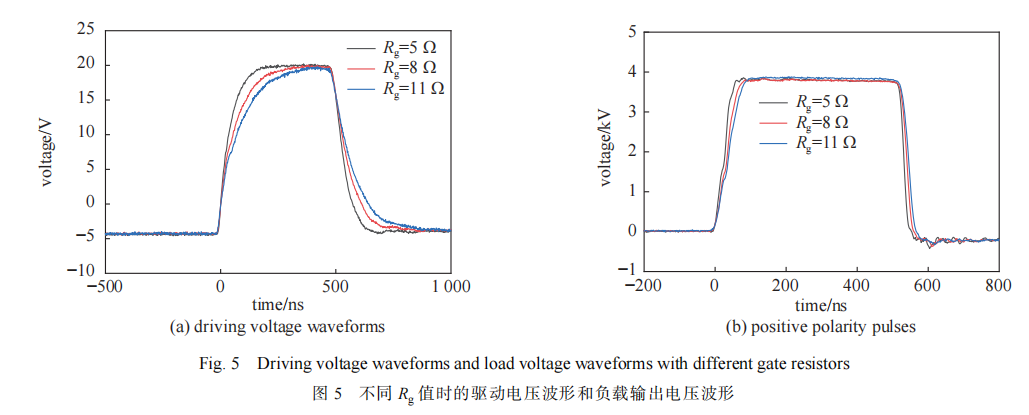

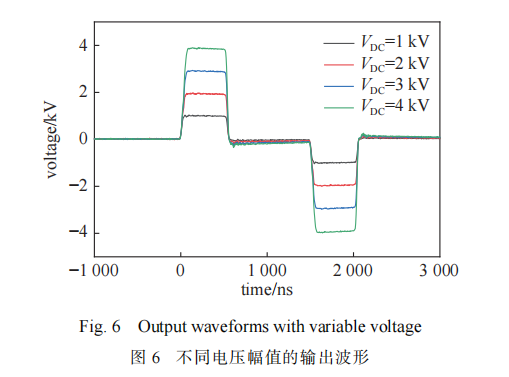

利用所研制的双极性脉冲电源进行了放电实验,实验负载为 100 Ω 的无感电阻,通过调节直流电源的输出电压幅值,脉冲电压的幅值随着输入电压的变化而变化。当输入电压 VDC 为 4 kV 时,其最大峰值电压幅值也为 4 kV,双极性脉冲发生器输出不同幅值电压波形如图 6 所示,脉冲上升时间和下降时间均低于 100 ns,实验中输出电压连续可调,正极性和负极性输出电压平稳,脉冲顶部和脉冲尾部的过冲和震荡都较小。如图 7 为双极性脉冲发生器不同脉宽时的输出电压波形,脉冲宽度为 0.2~1.0 μs 可调,正负极性脉冲顶部和尾部的过冲和震荡相似。脉冲尾部的过冲和震荡随着脉宽的增加更显著,由于随着输出脉宽的增加,电流流过回路电感的时间越长,电路中杂散电感和电容储存的能量越多,所以负压震荡就越大。

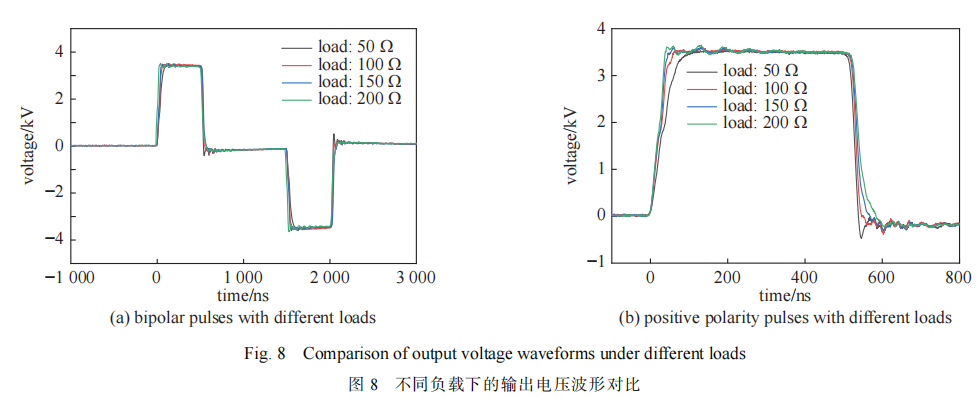

为了测试不同负载对输出脉冲波形的影响,选取了 50 Ω、100 Ω、150 Ω 和 200 Ω 的电阻作为放电负载,放电脉宽控制在 500 ns,充电电压设置为±3.5 kV。不同负载对应的输出双极性脉冲电压波形如图 8(a)所示,由图可知随着负载的阻值增大,脉冲的上升沿时间减小,当负载电阻阻值从 50 Ω 增大到 200 Ω 后,回路的前沿时间常数(L/R)也随之减小,回路中的放电电流减小,开关速度更快,脉冲的上升时间从 100 ns 减小到 50 ns。当放电结束后,下降沿时间随着负载阻值的减小而减小,因为等效电阻上的分布电容在放电中存储的能量会慢慢在负载内部进行放电,而阻值越小,此放电回路中的能量消耗越快,故下降时间越短。如图 8(b)所示,正极性脉冲顶部和脉冲尾部的过冲和震荡随着负载阻值的增大而更加明显,因为放电回路中的杂散电感和分布电容会随着负载的阻值增大而增大,导致在 MOSFET 导通和断开的瞬间电压的快速变化产生脉冲顶部和脉冲尾部的过冲及震荡。为满足不同负载的应用场景,需要优化器件的选型及电路空间布局,减小由于回路中的杂散电感和分布电容给输出波形带来的影响。

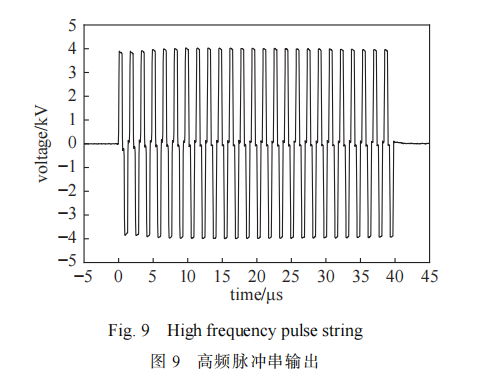

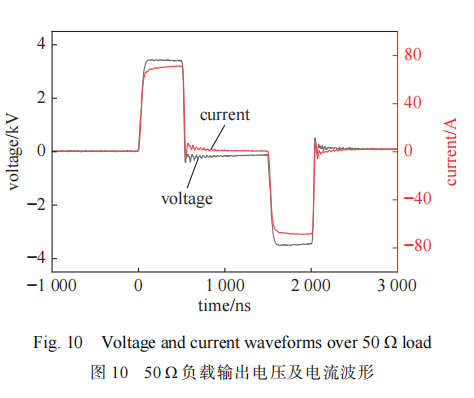

为了测试双极性脉冲发生器在连续放电及低负载情况下的工作状态,通过程序设定正负脉冲的死区时间,可以一次性释放多个双极性脉冲,输出电压稳定,符合预期效果。图 9 所示为放电负载 100 Ω、放电脉宽固定在 500 ns、充电电压设置为 4 kV 的双极性脉冲电压输出波形。为测试低负载放电时最大输出电流,将实验负载电阻减小为50 Ω,放电脉宽设置为 500 ns,正负极性死区时间为 1 μs,充电电压设置为 3.5 kV,获得的双极性脉冲电压输出波形如图 10 所示。由图可知,当最高电压为 3.5 kV 时,最大电流值为 75 A,波形良好。当脉冲电流增大时产生的电磁干扰也随之增强,对双极性发生器的抗电磁干扰能力提出很高的要求,可以通过调节驱动电阻的阻值减小 du/dt及 di/dt 而减弱电磁干扰,满足双极性脉冲发生器在低负载情况下的稳定工作,同时增强驱动信号的供电电压,防止电磁干扰影响驱动信号的不稳定。

3 结 论

基于半桥结构的全固态双极性电路拓扑,通过参数优化和器件选型,研制了一台全固态双极性亚微秒脉冲电源。电源的基本原理是通过控制不同极性的高压直流电源给储能电容充电,然后由 FPGA 控制半导体开关通断顺序来输出不同极性的脉冲电压。相当于 Marx 电路而言,本文提出的电路结构更简单,还可以选用高耐压的 IGBT直接控制充电过程,有利于减少开关数量,降低直通风险,也验证了增大栅极电阻阻值使得驱动电压上升时间减慢,从而减缓双极性高压的脉冲前沿。所设计的全固态双极性亚微秒脉冲电源输出电压、脉宽和频率均可调。在100 Ω 负载上的最大输出幅值为±4 kV,最短脉宽为 200 ns,且输出电流可达到 70 A。本方案结构简单,能有效产生亚微秒的双极性脉冲,可满足脉冲电场消融的应用需求。

碳化硅MOSFETs与SiC模块产品概览

文章为转载或网友发布,目的在于传递和分享信息,文章版权归原作者及原出处所有,如涉及作品内容、版权和其它问题,将根据著作权人的要求,第一时间更正或删除。