系统移植篇之uboot-5:DDR内存

DDR的基本工作原理

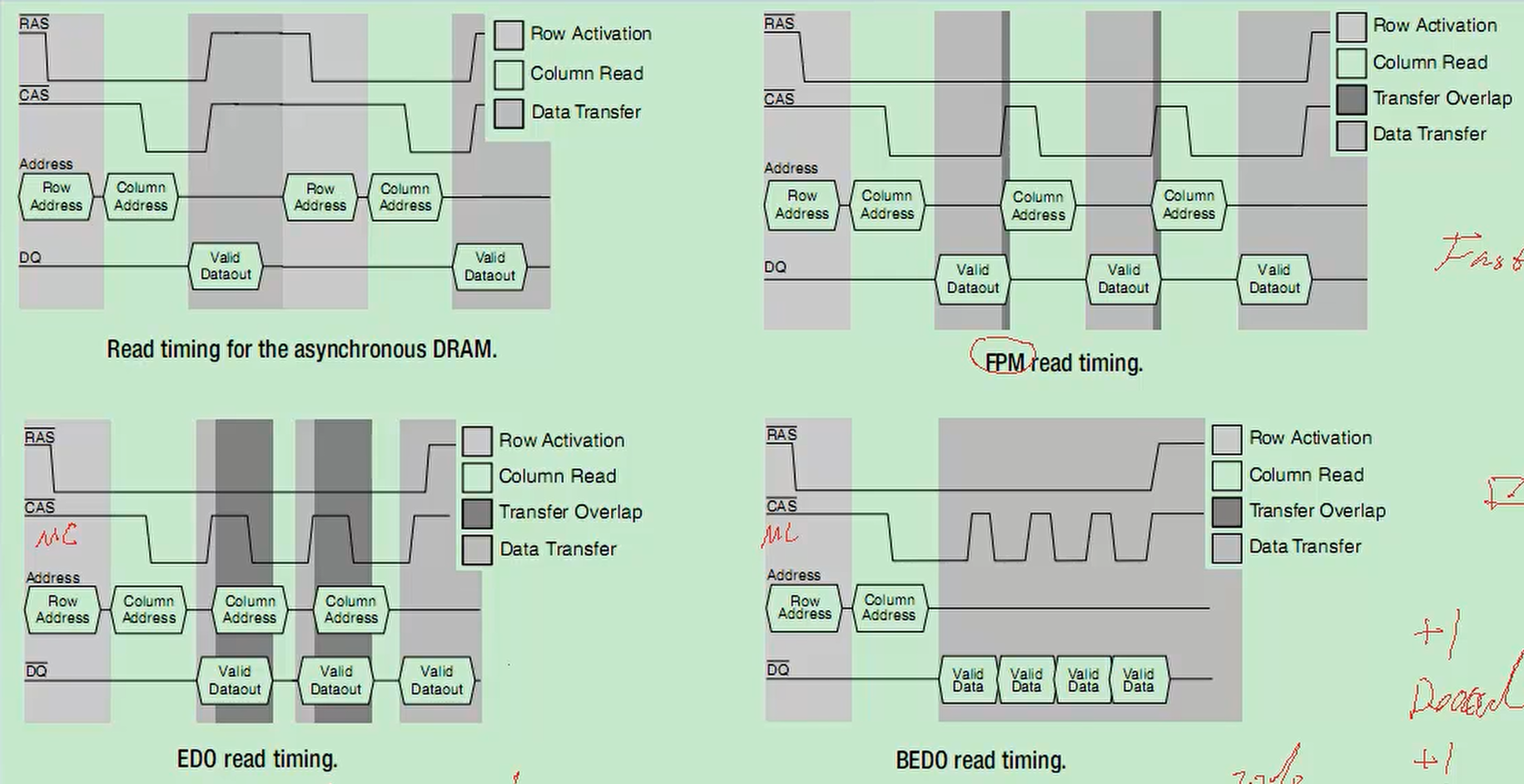

四块地址总线是完全一样的(地址线复用)

第一种就是需要准备行地址,列地址,然后一个个的把数据放上去, 第二个因为我们程序遵循局部性原理,所以,第一次给出行地址,后面一直给列地址就行,第三个是在准备列地址的时候其实可以顺便准备数据, 第四个是我们不用手动送数据了,里面有自动加一的程序,给出行地址,然后一直送数据就行了

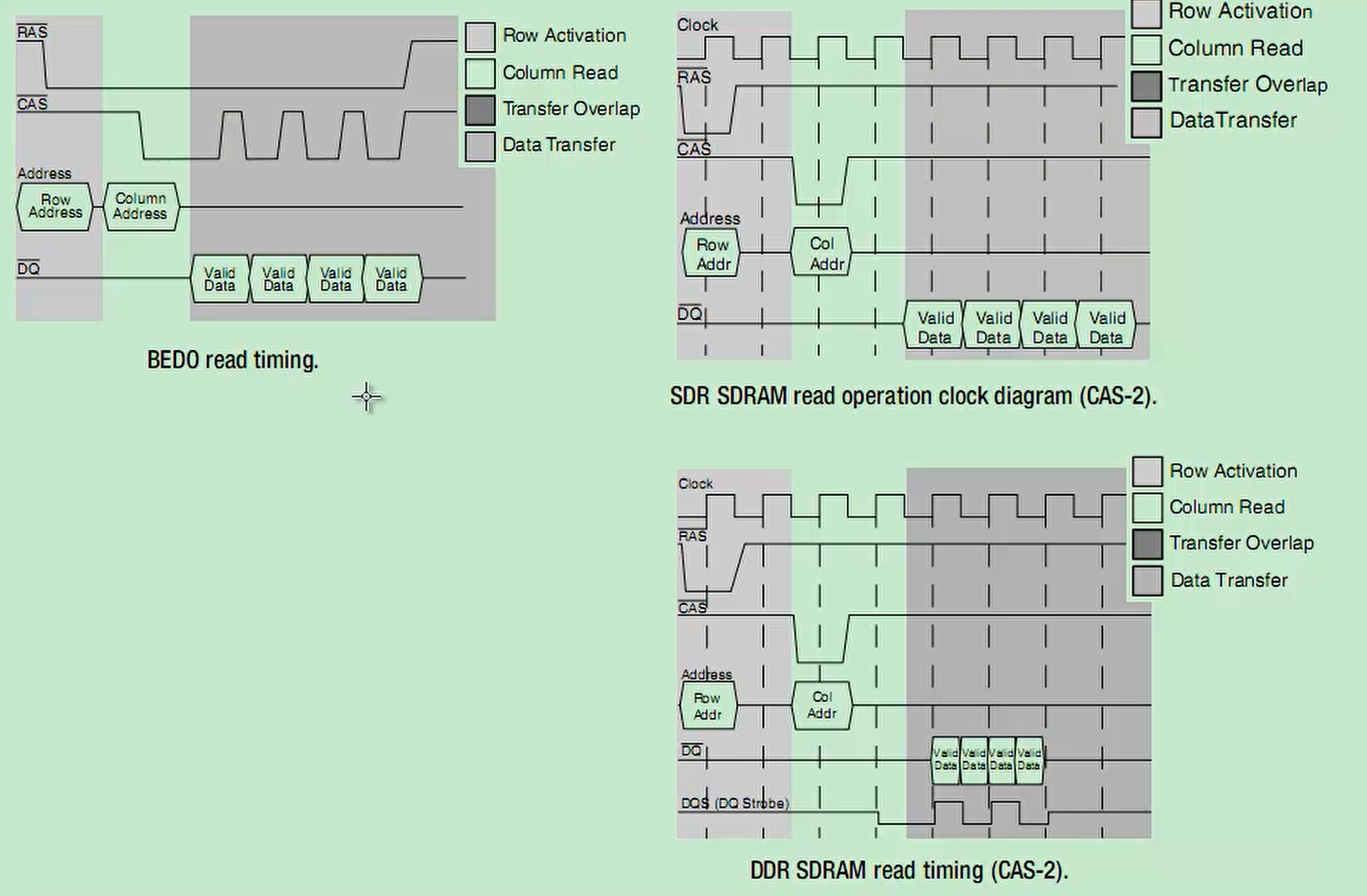

然后下面就是讲解从BEDO进化为SDRAM的过程

cpu和内存速度的变化并不同步, 异步的方式下, 异步给出控制信号之类的都有延迟,远距离用异步比较好,近距离板子上的话,同步速度一点不逊色异步传输方式,所以这个时候人们又重新考虑回内存和cpu同步通讯这种方式

SDR :给出了clock这样的同步信号以后,只在时钟的上升沿采集RAS信号,然后下一个上升沿对行地址解码,然后再一个上升沿,把CAS拉低,读取CAS为低电平,就去读取列地址,然后下一个上升沿解码,再后面每一次上升沿读一次数据, 这个地方就不像BEDO靠拉低CAS读取数据了,这样的话,升级潜力就大了,内存提高了频率,cpu就提高clock的频率来适应,内存落后,cpu就调慢clock的频率来适应这个落后的cpu

DDR:传输数据时候把下降沿也利用上了,就是double了

DQS在读数据时候没有太大作用,一般控制器会忽略这个作用,在写数据的时候,电平翻转一下

SDR比DDR还有一个优势,SDR下降沿可以用来稳定数据,稳定了,送到芯片里面去.DDR没有那么稳定,所以数据中间需要那么一个信号,来告诉CPU数据准备稳定了, 就需要由DQS给出,它通知SDRAM现在可以锁存数据了

DQS是和DATA对应的,有一个DATA输出就有一个DQS

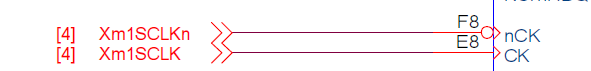

clock也采用差分信号, 如果用一根线来表示clock, 假设中间有噪音, 可能就会被认为是一个有效信号, 只有在clock和nclock产生的信号相反的时候才认为产生了有效的信号

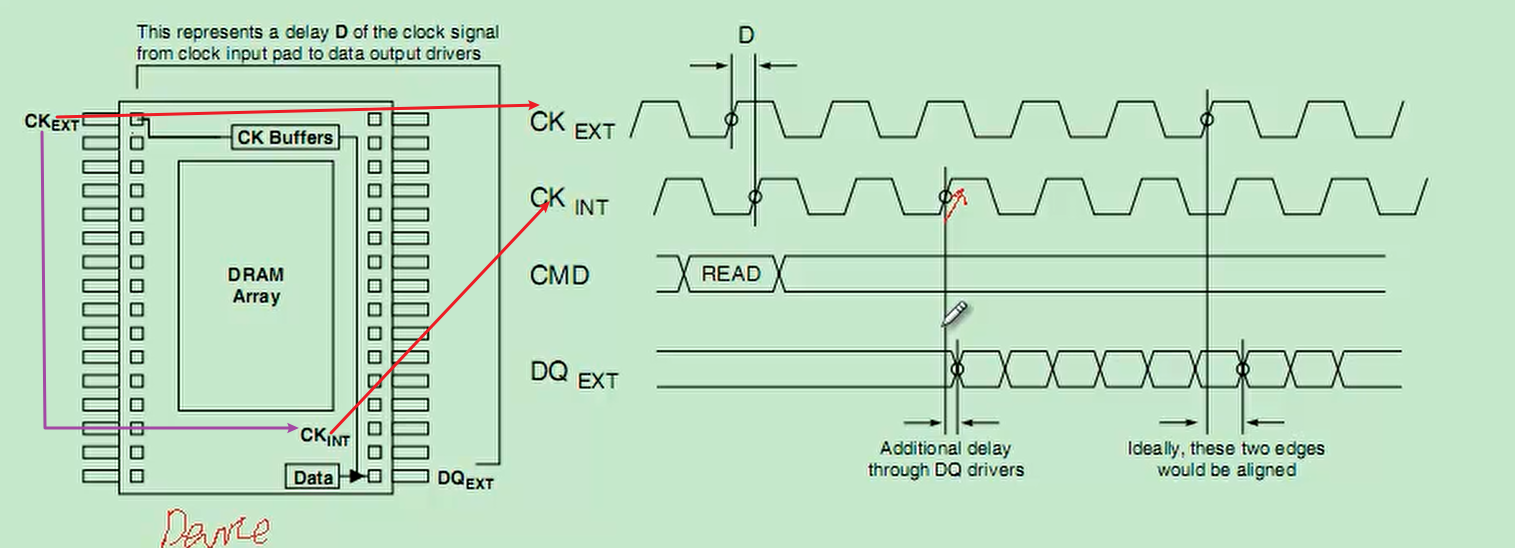

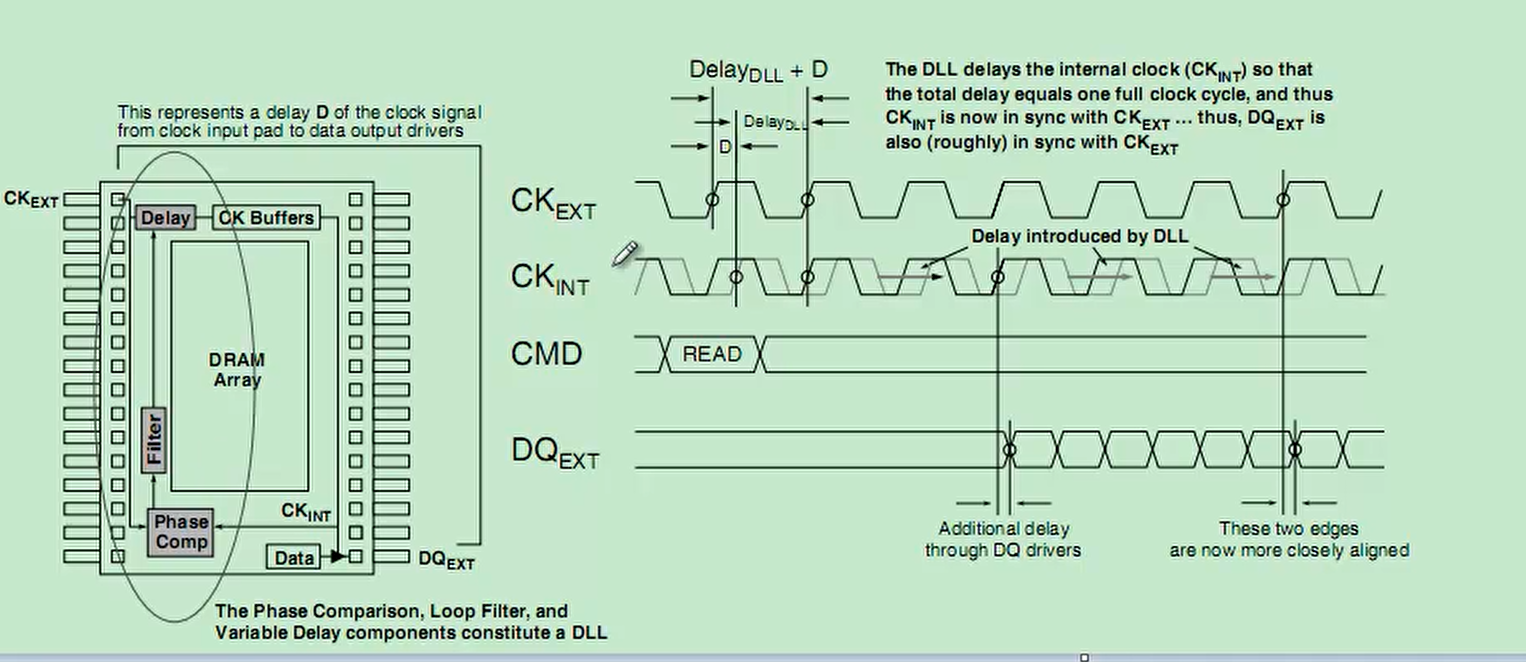

DLL(Delay lock loop) 结构,延迟环,延迟或者提前频率用的

这clock信号从外部输入到内部, 会有一定的延迟, 大概就D那么大的延迟, 然后DQ上同样也有延迟,然后内部就做了延迟环的结构

灰色线是没有加延迟环时候的clock内部时钟, 经过DLL以后灰线变成黑实线,clock往后移了一个周期,reset以后,有个延时就是做这样的调整

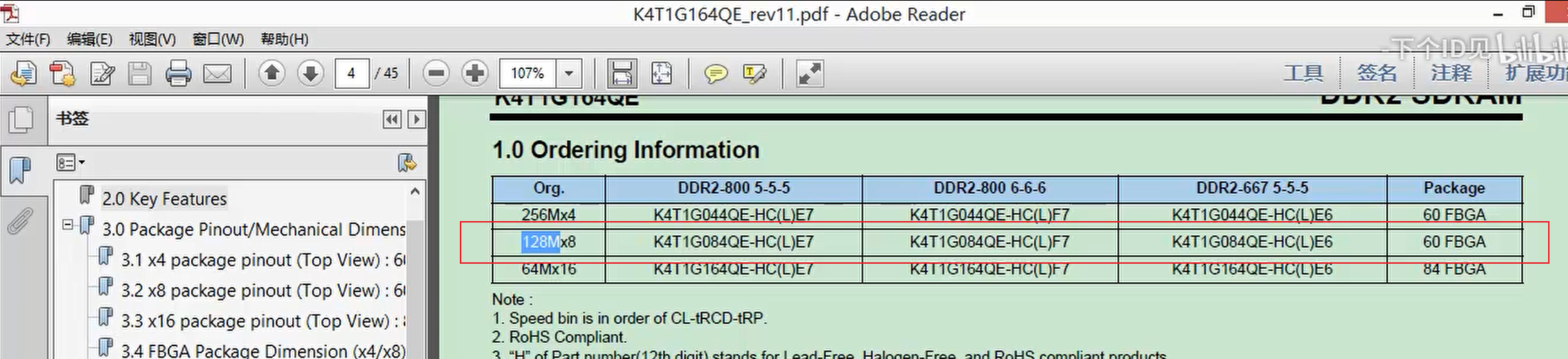

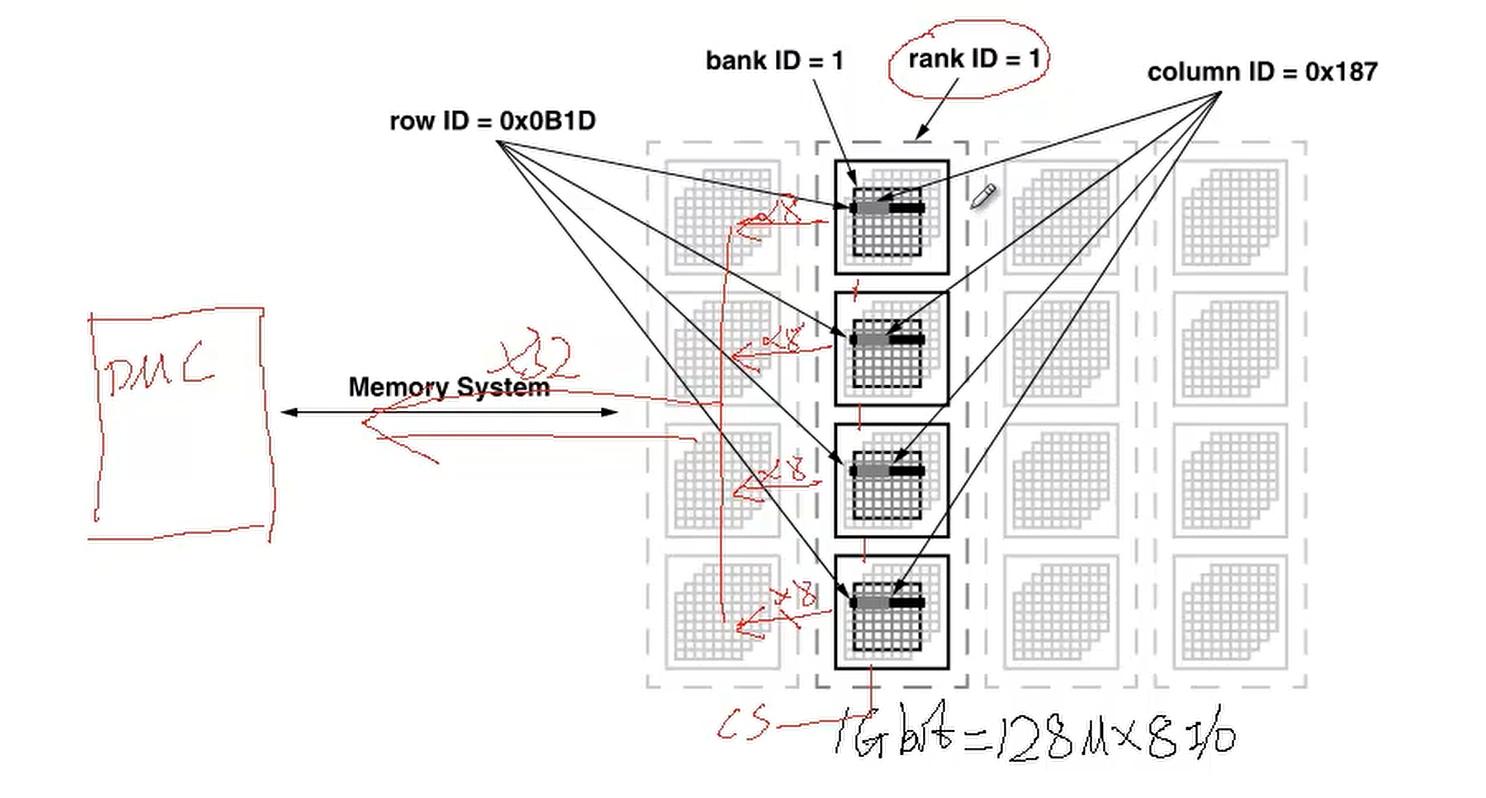

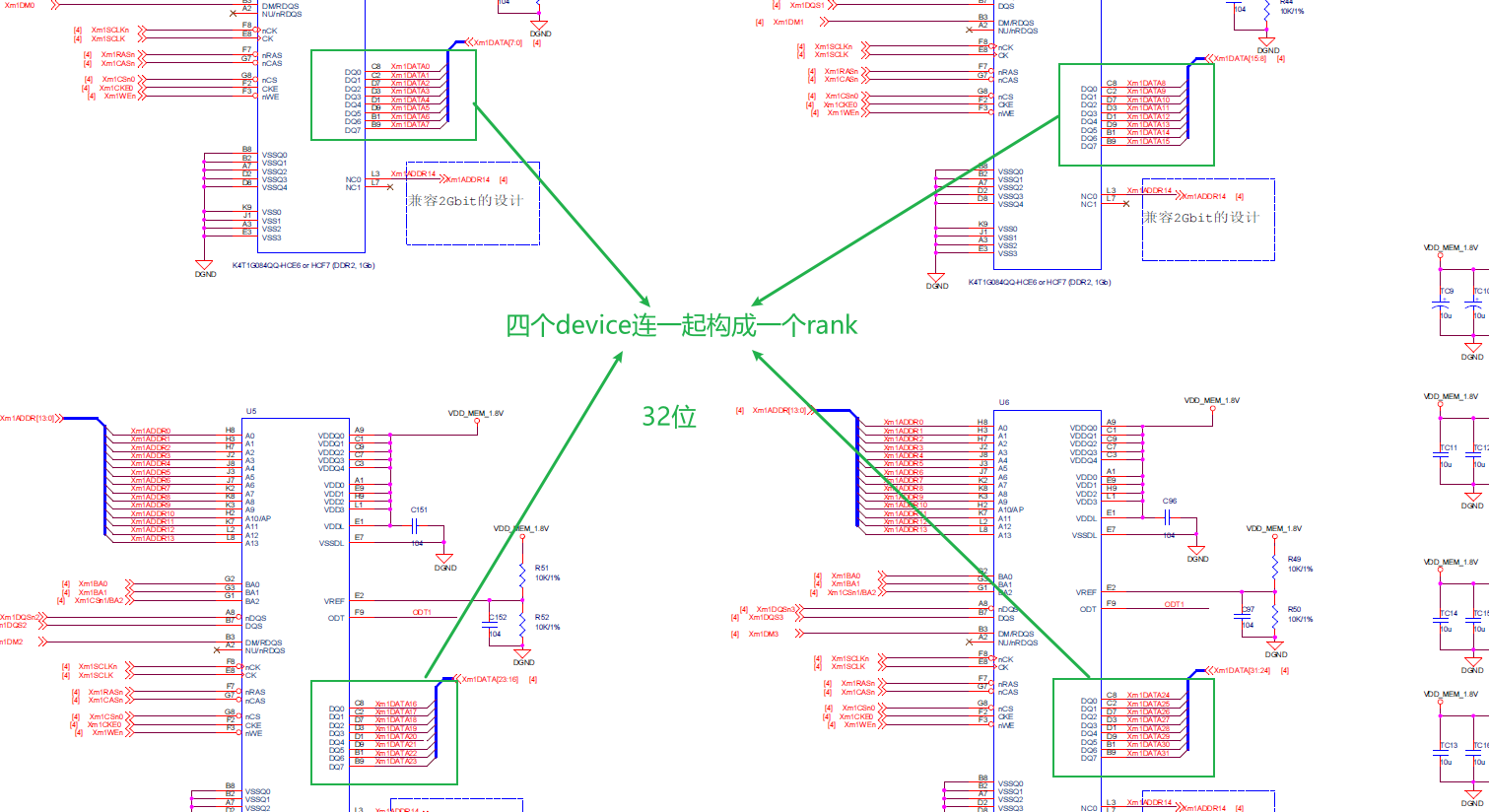

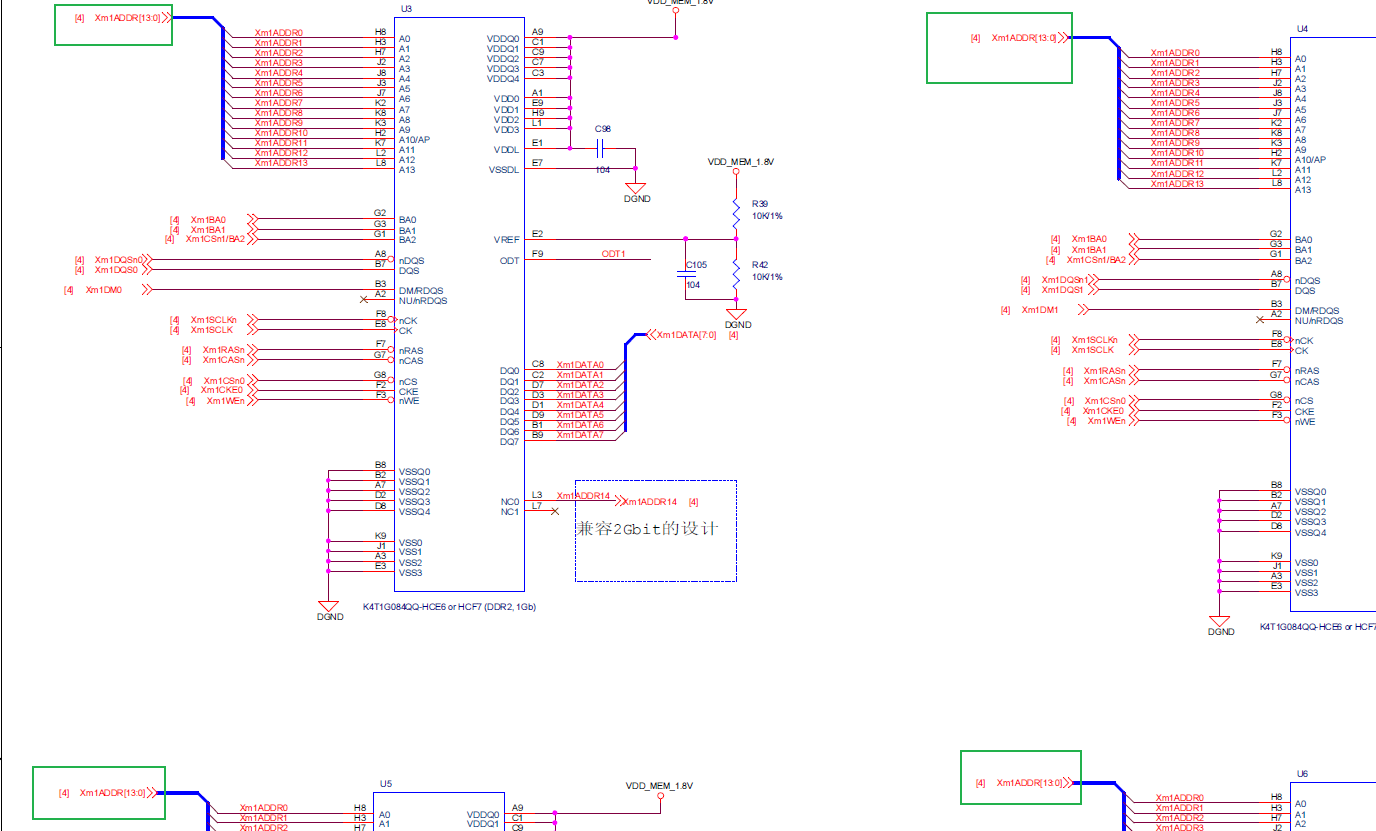

210开发板的内存结构