fpga开发板ZYNQ 璞致 PZ7010/7020 邮票孔核心板简介-ZYNQ7000系列小系统学习板

第一章 核心板简介

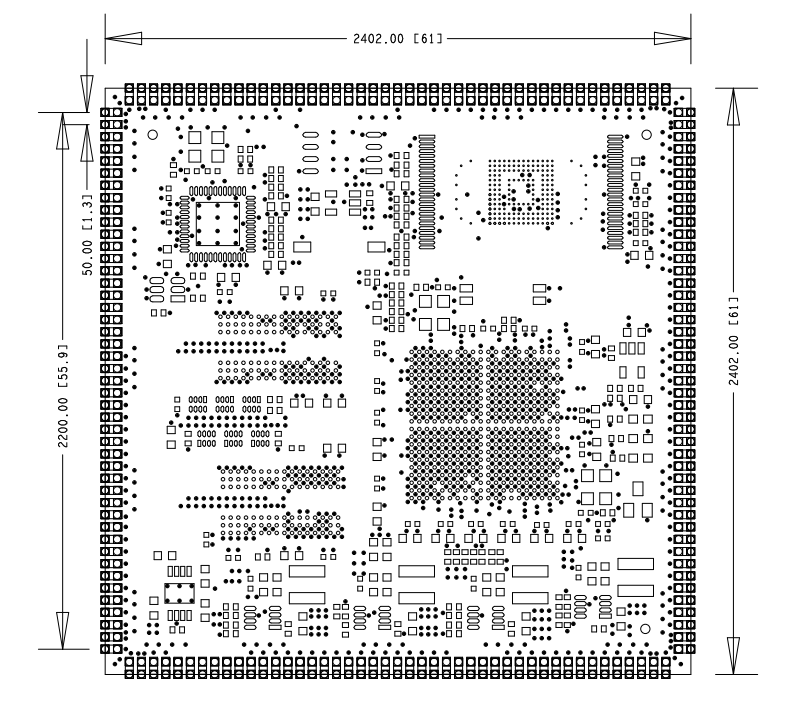

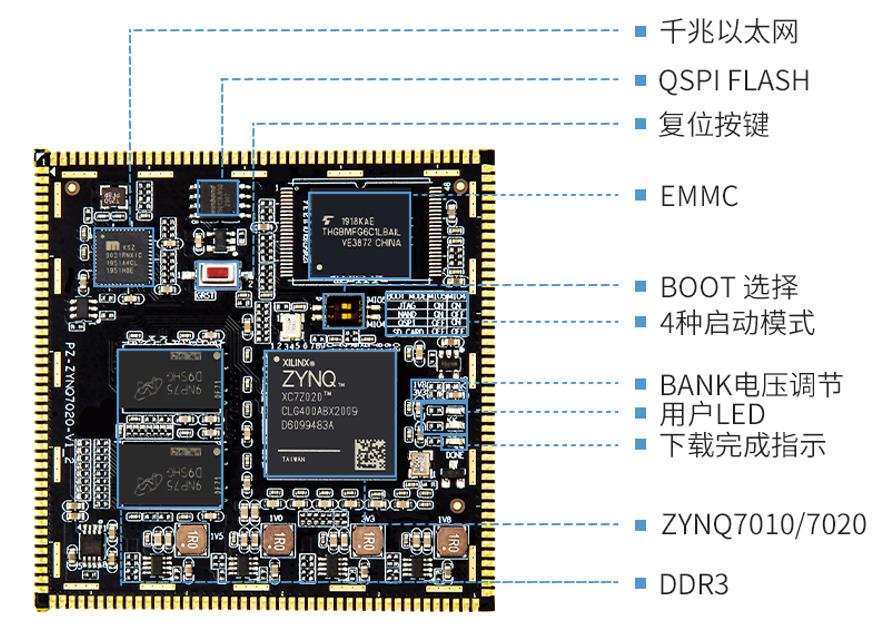

PZ7010/7020 核心板采用 XILINX 公司的 XC7Z010-2CLG400I/XC7Z020-2CLG400I 芯片 作为主控制器,核心板采用 1.27mm 间距连接器与邮票孔兼容方式与母板连接,确保了在强 烈震动的环境下稳定运行、杜绝了连接器方式因老化而造成接触不良。

1.2 产品规格

PZ7010 商业级/ PZ7010 工业级/ PZ7020 工业级核心板规格 | |||

主控制器 | XC7Z010-2CLG400C | XC7Z010-2CLG400I | XC7Z020-2CLG400I |

DDR3/DD3L | 512MB | 512MB | 1GB |

QSPI FLASH | 16MB | ||

EMMC | 4GB | 4GB | 8GB |

启动方式 | JTAG/QSPI/SD,板载拨码开关选择 | ||

千兆以太网 | 1 路 | ||

用户 LED | 2 路 | ||

工作电压 | 5V/1A | ||

IO 数量 | PS 侧 24 个 IO PL 侧 94 个 IO | PS 侧 24 个 IO PL 侧 94 个 IO | PS 侧 24 个 IO PL 侧 118 个 IO |

工作温度 | 0°C~+70°C | -40°C~+85°C | -40°C~+85°C |

核心板尺寸、工艺 | 61x61mm、沉金、1.27mm 间距邮票孔或排针 | ||

1.3 产品外观

PZ7010/7020 采用单面摆放器件,所有元件都在正面背面无器件,无需在底板上做镂 空设计。

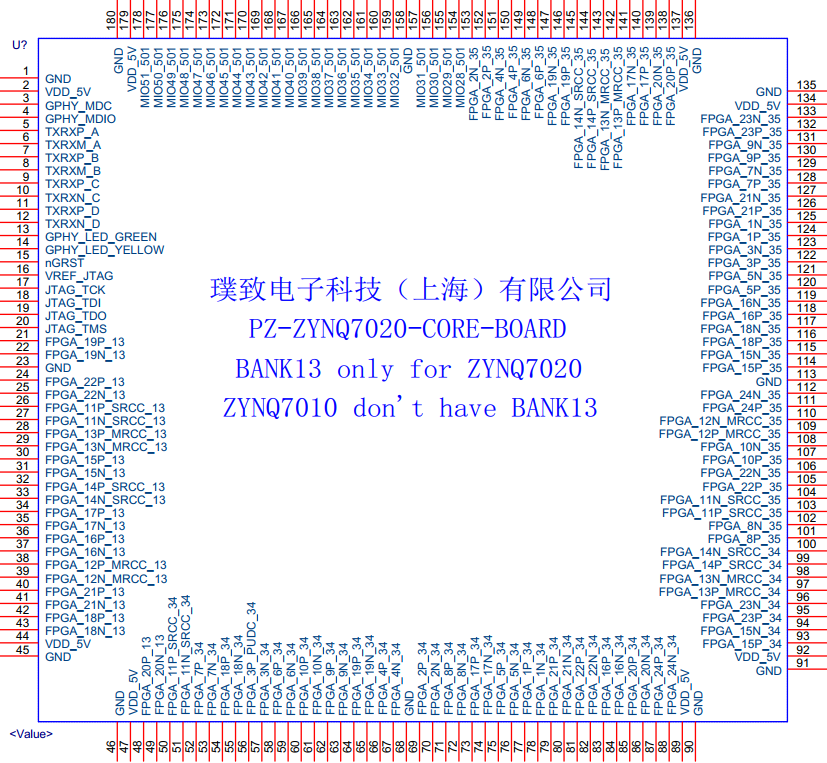

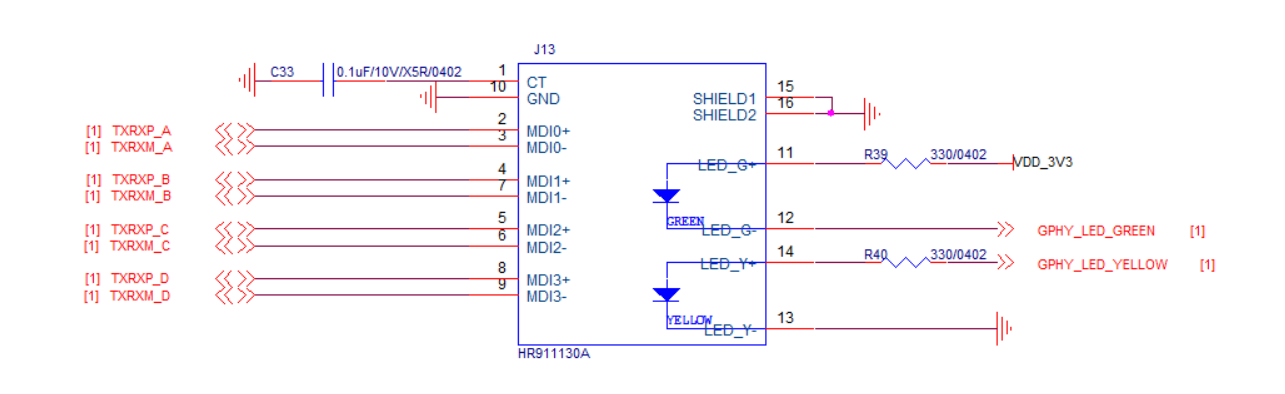

第二章 核心板管脚定义

管脚 | 管脚名称 | 管脚位置 | 管脚说明 | 管脚 | 管脚名称 | 管脚位置 | 管脚说明 |

1 | GND | 地 | 46 | GND | 地 | ||

2 | VDD_5V | 5V 电源输入 | 47 | VDD_5V | 5V 电源输入 | ||

3 | GPHY_MDC | C10 | 1.8V 电压域 | 48 | FPGA_IO_20P_13 | Y12 | BANK13 Fix 3.3V |

4 | GPHY_MDIO | C11 | 1.8V 电压域,已上拉 | 49 | FPGA_IO_20N_13 | Y13 | |

5 | TXRXP_A | 网口差分线 | 50 | FPGA_IO_11P_SRCC_34 | U14 | BANK34 Fix 3.3V (FPGA_IO_3P_34, 此引 脚为配置脚,内部做了 1K 电阻上拉,使用时需要注 意,MRCC/SRCC为时钟管 脚,既可以做 IO 也可以作 为时钟输入输出) | |

6 | TXRXM_A | 51 | FPGA_IO_11N_SRCC_34 | U15 | |||

7 | TXRXP_B | 52 | FPGA_IO_7P_34 | Y16 | |||

8 | TXRXM_B | 53 | FPGA_IO_7N_34 | Y17 | |||

9 | TXRXP_C | 54 | FPGA_IO_18P_34 | V16 | |||

10 | TXRXM_C | 55 | FPGA_IO_18N_34 | W16 | |||

11 | TXRXP_D | 56 | FPGA_IO_3P_34 | U13 | |||

12 | TXRXM_D | 57 | FPGA_IO_3N_34 | V13 | |||

13 | GPHY_LED_GREEN | OD 门,上拉接 LED | 58 | FPGA_IO_6P_34 | P14 | ||

14 | GPHY_LED_YELLOW | OD 门,上拉接 LED | 59 | FPGA_IO_6N_34 | R14 | ||

15 | nGRST | 复位,已上拉 3.3V | 60 | FPGA_IO_10P_34 | V15 | ||

16 | VREF_JTAG | JTAG 参考电平/3.3V | 61 | FPGA_IO_10N_34 | W15 | ||

17 | JTAG_TCK | JTAG 时钟 | 62 | FPGA_IO_9P_34 | T16 | ||

18 | JTAG_TDI | JTAG 输入 | 63 | FPGA_IO_9N_34 | U17 | ||

19 | JTAG_TDO | JTAG 输出 | 64 | FPGA_IO_19P_34 | R16 | ||

20 | JTAG_TMS | JTAG 模式 | 65 | FPGA_IO_19N_34 | R17 | ||

21 | FPGA_IO_19P_13 | T5 | 3.3V 电压域、BANK13 (only for zynq7020) | 66 | FPGA_IO_4P_34 | V12 | |

22 | FPGA_IO_19N_13 | U5 | 67 | FPGA_IO_4N_34 | W13 | ||

23 | GND | 地 | 68 | GND | 地 | ||

24 | FPGA_IO_22P_13 | V6 | BANK13 Fix 3.3V (BANK13 only for zynq7020) | 69 | FPGA_IO_2P_34 | T12 | BANK34 FIX 3.3V |

25 | FPGA_IO_22N_13 | W6 | 70 | FPGA_IO_2N_34 | U12 | ||

26 | FPGA_IO_11P_SRCC_13 | U7 | 71 | FPGA_IO_8P_34 | W14 | ||

27 | FPGA_IO_11N_SRCC_13 | V7 | 72 | FPGA_IO_8N_34 | Y14 | ||

28 | FPGA_IO_13P_MRCC_13 | Y7 | 73 | FPGA_IO_17P_34 | Y18 | ||

29 | FPGA_IO_13N_MRCC_13 | Y6 | 74 | FPGA_IO_17N_34 | Y19 | ||

30 | FPGA_IO_15P_13 | V8 | 75 | FPGA_IO_5P_34 | T14 | ||

31 | FPGA_IO_15N_13 | W8 | 76 | FPGA_IO_5N_34 | T15 | ||

32 | FPGA_IO_14P_SRCC_13 | Y9 | 77 | FPGA_IO_1P_34 | T11 | ||

33 | FPGA_IO_14N_SRCC_13 | Y8 | 78 | FPGA_IO_1N_34 | T10 | ||

34 | FPGA_IO_17P_13 | U9 | 79 | FPGA_IO_21P_34 | V17 | ||

35 | FPGA_IO_17N_13 | U8 | 80 | FPGA_IO_21N_34 | V18 | ||

36 | FPGA_IO_16P_13 | W10 | 81 | FPGA_IO_22P_34 | W18 | ||

37 | FPGA_IO_16N_13 | W9 | 82 | FPGA_IO_22N_34 | W19 | ||

38 | FPGA_IO_12P_MRCC_13 | T9 | 83 | FPGA_IO_16P_34 | V20 | ||

39 | FPGA_IO_12N_MRCC_13 | U10 | 84 | FPGA_IO_16N_34 | W20 | ||

40 | FPGA_IO_21P_13 | V11 | 85 | FPGA_IO_20P_34 | T17 | ||

41 | FPGA_IO_21N_13 | V10 | 86 | FPGA_IO_20N_34 | R18 | ||

42 | FPGA_IO_18P_13 | W11 | 87 | FPGA_IO_24P_34 | P15 | ||

43 | FPGA_IO_18N_13 | Y11 | 88 | FPGA_IO_24N_34 | P16 | ||

44 | VDD_5V | 5V 电源输入 | 89 | VDD_5V | 5V 电源输入 | ||

45 | GND | 地 | 90 | GND | 地 |

管脚号 | 管脚名称 | 管脚位 置 | 管脚说明 | 管脚 | 管脚名称 | 管脚位置 | 管脚说明 |

91 | GND | 地 | 136 | GND | 地 | ||

92 | VDD_5V | 5V 电源输入 | 137 | VDD_5V | 5V 电源输入 | ||

93 | FPGA_IO_15P_34 | T20 | 3.3V 电 压 域 、 BANK34 | 138 | FPGA_IO_20P_35 | K14 | BANK35 1.8V/2.5V/3.3V ADJ Default 3.3V |

94 | FPGA_IO_15N_34 | U20 | 139 | FPGA_IO_20N_35 | J14 | ||

95 | FPGA_IO_23P_34 | N17 | 140 | FPGA_IO_17P_35 | J20 | ||

96 | FPGA_IO_23N_34 | P18 | 141 | FPGA_IO_17N_35 | H20 | ||

97 | FPGA_IO_13P_MRCC_34 | N18 | 142 | FPGA_IO_13P_MRCC_35 | H16 | ||

98 | FPGA_IO_13N_MRCC_34 | P19 | 143 | FPGA_IO_13N_MRCC_35 | H17 | ||

99 | FPGA_IO_14P_SRCC_34 | N20 | 144 | FPGA_IO_14P_SRCC_35 | J18 | ||

100 | FPGA_IO_14N_SRCC_34 | P20 | 145 | FPGA_IO_14N_SRCC_35 | H18 | ||

101 | FPGA_IO_8P_35 | M17 | BANK35 1.8V/2.5V/3.3V ADJ Default 3.3V | 146 | FPGA_IO_19P_35 | H15 | |

102 | FPGA_IO_8N_35 | M18 | 147 | FPGA_IO_19N_35 | G15 | ||

103 | FPGA_IO_11P_SRCC_35 | L16 | 148 | FPGA_IO_6P_35 | F16 | ||

104 | FPGA_IO_11N_SRCC_35 | L17 | 149 | FPGA_IO_6N_35 | F17 | ||

105 | FPGA_IO_22P_35 | L14 | 150 | FPGA_IO_4P_35 | D19 | ||

106 | FPGA_IO_22N_35 | L15 | 151 | FPGA_IO_4N_35 | D20 | ||

107 | FPGA_IO_10P_35 | K19 | 152 | FPGA_IO_2P_35 | B19 | ||

108 | FPGA_IO_10N_35 | J19 | 153 | FPGA_IO_2N_35 | A20 | ||

109 | FPGA_IO_12P_MRCC_35 | K17 | 154 | MIO28_501 | C16 | ARM MIO Fix 1.8V | |

110 | FPGA_IO_12N_MRCC_35 | K18 | 155 | MIO29_501 | C13 | ||

111 | FPGA_IO_24P_35 | K16 | 156 | MIO30_501 | C15 | ||

112 | FPGA_IO_24N_35 | J16 | 157 | MIO31_501 | E16 | ||

113 | GND | 地 | 158 | GND | 地 | ||

114 | FPGA_IO_15P_35 | F19 | BANK35 1.8V/2.5V/3.3V ADJ Default 3.3V | 159 | MIO32_501 | A14 | ARM MIO Fix 1.8V |

115 | FPGA_IO_15N_35 | F20 | 160 | MIO33_501 | D15 | ||

116 | FPGA_IO_18P_35 | G19 | 161 | MIO34_501 | A12 | ||

117 | FPGA_IO_18N_35 | G20 | 162 | MIO35_501 | F12 | ||

118 | FPGA_IO_16P_35 | G17 | 163 | MIO36_501 | A11 | ||

119 | FPGA_IO_16N_35 | G18 | 164 | MIO37_501 | A10 | ||

120 | FPGA_IO_5P_35 | E18 | 165 | MIO38_501 | E13 | ||

121 | FPGA_IO_5N_35 | E19 | 166 | MIO39_501 | C18 | ||

122 | FPGA_IO_3P_35 | E17 | 167 | MIO40_501 | D14 | ||

123 | FPGA_IO_3N_35 | D18 | 168 | MIO41_501 | C17 | ||

124 | FPGA_IO_1P_35 | C20 | 169 | MIO42_501 | E12 | ||

125 | FPGA_IO_1N_35 | B20 | 170 | MIO43_501 | A9 | ||

126 | FPGA_IO_21P_35 | N15 | 171 | MIO44_501 | F13 | ||

127 | FPGA_IO_21N_35 | N16 | 172 | MIO45_501 | B15 | ||

128 | FPGA_IO_7P_35 | M19 | 173 | MIO46_501 | D16 | ||

129 | FPGA_IO_7N_35 | M20 | 174 | MIO47_501 | B14 | ||

130 | FPGA_IO_9P_35 | L19 | 175 | MIO48_501 | B12 | ||

131 | FPGA_IO_9N_35 | L20 | 176 | MIO49_501 | C12 | ||

132 | FPGA_IO_23P_35 | M14 | 177 | MIO50_501 | B13 | ||

133 | FPGA_IO_23N_35 | M15 | 178 | MIO51_501 | B9 | ||

134 | VDD_5V | 5V 电源输入 | 179 | VDD_5V | 5V 电源输入 | ||

135 | GND | 地 | 180 | GND | 地 |

第三章 核心板使用说明

核心板采用 5V 输入供电,在模块的四个角都留有5V 输入管脚,5V 管脚在模块内部已 做了连通,这样设计是为了方便底板的电源输入,设计时只需要连接一个角上的两根 5V 管 脚核心板即可工作,模块上的所有 GND 信号都需要连接到底板上,共计 12 根 GND。

为了保证电源更加稳定,建议在 5V 输入前级加一级 DCDC,从较高电压转到 5V,DCDC 输出电流能力可以选 2A 左右的 。在 5V 电源输入处需放置 100uF/10V 电容保证电源质量。 整个模组最大功耗约为 5V*600mA 左右。

注意:有用户前级 DCDC 从 12V 或者 24V 降压到5V 使用,但是在5V 输出加的电容不 够大,造成稳压异常模块过压损坏,所以用户在 5V 电源处电容留足容量。

核心板为 PS 侧提供了 33.333Mhz 的时钟输入,输入的管脚位置为 PS_CLK_500;为 PL 侧提供了 50Mhz 的时钟输入,PL 侧的时钟输入管脚是 FPGA_12P_MRCC_34,管脚位置是 U18。

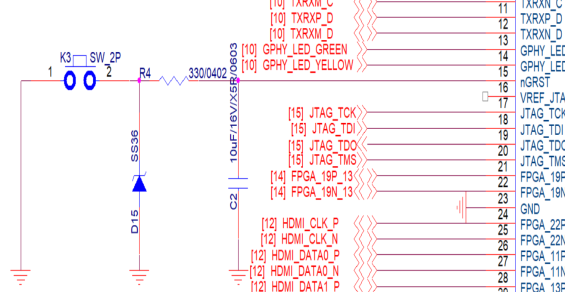

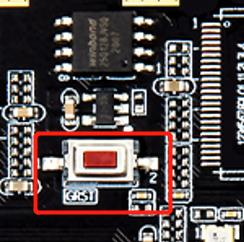

3.3 全局复位

核心板提供了 nGRST 复位按键,为系统复位按键,低电平有效。此引脚也引出到邮票 孔位置,方便用户外部使用。此复位脚为 PS/PL 侧共用复位,分别连接到PS 侧的 PS_POR_500 和 PL 侧的 FPGA_12N_MRCC_34 引脚上,管脚位置是 U19。

全局复位管脚 nGRST,在核心板内部已做上拉,在设计底板复位电路上有三种方案:一种是底板不需 要把 nGRST 拉到结构外壳上,这样只需要如下左图,在 nGRST 管脚上对地下拉 10uF 电容即可;

如果需要把 nGRST 拉到结构外壳上做复位使用,那么需要参考右图,除对地下拉 10uF 电容外,还需要外 加 ESD 保护电路,如下右图;另外如果对成本要求比较宽裕情况下可以使用专用复位芯片来替代 RC 复位 电路,如使用 ADM6711SAKSZ 或者 MAX811 都可以实现,复位芯片供电电源使用3.3V。

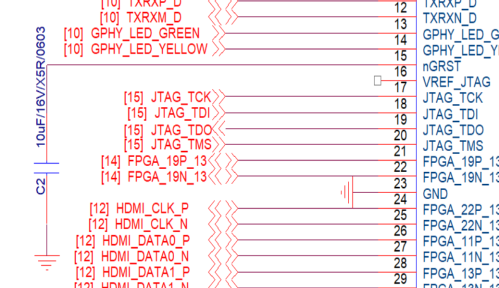

3.4 启动方式

核心板支持四种启动模式,分别是 JTAG、QSPI Flash 、NAND、SD 卡。板载了前三种方 式,SD 卡方式用户可以通过在底板上连接实现。四种启动方式可以通过板载的拨码开关来 选择。如下图已列出各个模式拨码开关所在的位置。

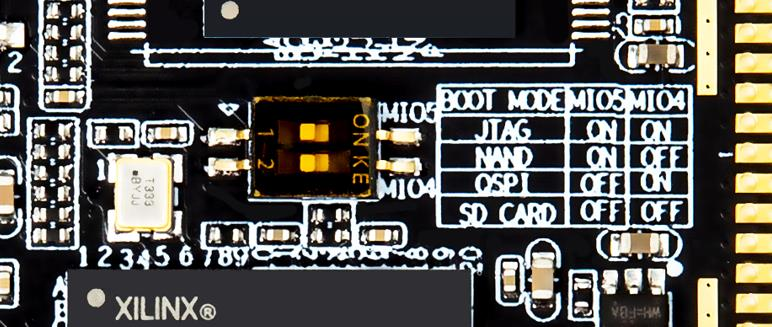

3.5 网口连接

核心板上放置了一颗千兆以太网芯片 RTL8211FI, 以太网芯片与 ZYNQ 芯片之间通过 RGMII 接口互联,连接对应管脚见下表, 以太网对外连接只需要一个带变压器的 RJ45 即可 使用,芯片地址 PHY_AD[2:0]=001,连接原理图可参考下图(产品电路需加 ESD 保护电路)。

另外,以太网芯片的复位脚采用系统复位和硬件管脚复位兼容设计,默认采用系统上电 复位。

RMGII 信号 | 管脚名称 | 管脚位置 |

GTX_CLK | MIO16_501 | A19 |

TXD0 | MIO17_501 | E14 |

TXD1 | MIO18_501 | B18 |

TXD2 | MIO19_501 | D10 |

TXD3 | MIO20_501 | A17 |

TX_EN | MIO21_501 | F14 |

RX_CLK | MIO22_501 | B17 |

RXD0 | MIO23_501 | D11 |

RXD1 | MIO24_501 | A16 |

RXD2 | MIO25_501 | F15 |

RXD3 | MIO26_501 | A15 |

RX_CTL | MIO27_501 | D13 |

PHY_nRST(默认系统复位) | FPGA_GPIO_0_35 | G14 |

MDC | MIO52_501 | C10 |

MDIO | MIO53_501 | C11 |

3.6 EMMC 管脚定义

板载 EMMC 容量 4GB/8GB 可选,PZ7010 使用 4GB,PZ7020 使用 8GB 。 EMMC 对应 管脚定义如下表。

EMMC 引脚 | 管脚名称 | 管脚位置 |

EMMC_D0 | MIO10 | E9 |

EMMC_D1 | MIO13 | E8 |

EMMC_D2 | MIO14 | C5 |

EMMC_D3 | MIO15 | C8 |

EMMC_CLK | MIO12 | D9 |

EMMC_CMD | MIO11 | C6 |

3.7 NAND FLASH 管脚定义

NAND FLASH 与 EMMC 在板子上采用兼容设计,只能二选一焊接使用,需要根据具体需 求指定焊接,默认焊接 EMMC 不焊接 NAND FLASH。

FLASH 引脚 | 管脚名称 | 管脚位置 |

DATA0 | MIO5 | A6 |

DATA1 | MIO6 | A5 |

DATA2 | MIO4 | B7 |

DATA3 | MIO13 | E8 |

DATA4 | MIO9 | B5 |

DATA5 | MIO10 | E9 |

DATA6 | MIO11 | C6 |

DATA7 | MIO12 | D9 |

RE | MIO8 | D5 |

CE | MIO0 | E6 |

CLE | MIO7 | D8 |

ALE | MIO2 | B8 |

WE | MIO3 | D6 |

R/B | MIO14 | C5 |

3.8 QSPI FLASH

板载 16MB 的 QSPI FLASH,型号为 W25Q128JVSIQ,用于存储启动文件和用户文件

QSPI FLASH 引脚 | 管脚名称 | 管脚位置 |

DATA0 | MIO2 | B8 |

DATA1 | MIO3 | D6 |

DATA2 | MIO4 | B7 |

DATA3 | MIO5 | A6 |

QSPI_CS | MIO1 | A7 |

QSPI_CLK | MIO6 | A5 |

3.9 板载 LED

为方便调试,核心板上放置了两颗 LED,LED 的管脚位置如下表,当管脚输出 0 时 LED 点亮。

序号 | 管脚名称 | 管脚位置 |

LED1 | FPGA-0-34 | R19 |

LED2 | FPGA-25-34 | T19 |

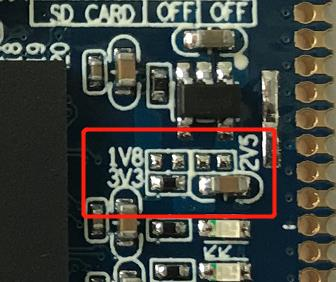

3.10 BANK35 接口电平选择

单板上 BANK35 接口电平可以通过选焊电阻来实现 1.8V/2.5V/3.3V 电平的变更,单板默 认接口电平为 3.3V,如需变更电压只需要把 3.3V 位置电阻更换到对应位置即可。电阻位置在 核心板的右侧。

3.11 核心板个性选择

核心板分为商业级和工业级两种,对于 DDR3 容量可以512MB/1GB 选择,EMMC 可以 4GB/8GB 选择,容量可以根据客户需求选择,默认 PZ7010 的配置为 512MB DDR3 、4GB EMMC,PZ7020 的配置为 1GB DDR3 、8GB EMMC。

第四章 底板设计注意事项

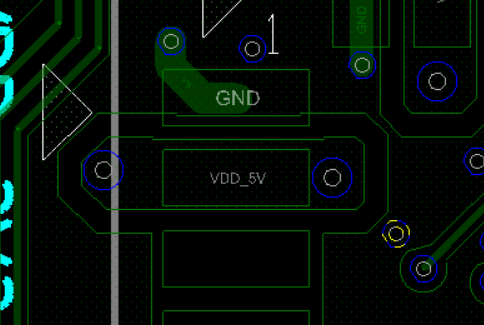

对于核心板 5V 电源与地的连接,需要每个电源 pad 打两个孔以上,保证通流能力。可 参考下图设计。

4.2 高速接口布局走线

1)USB 口:

USB PHY 芯片的并口速率在 60Mhz,并口走线需要保证等长,且长度不大于 1000mil (25.4mm), 所以 PHY 尽量靠近模组放置,USB 差分线 DP/DM 可以拉的长一些。

2)千兆以太网:

与 RJ45 端连接的信号需要保持等长,RGMII 接口的 TX 部分与 RX 部分需要单独保持等 长。

3)HDMI 接口

HDMI 接口信号需要走差分,且差分之间需保持等长控制。

4.3 LVDS 信号

模组的 BANK35 是可以在 1.8V/2.5V/3.3V 三种电平之间选择,默认为 3.3V 电平,如果需 要工作在 LVDS 模式下,需要把接口电平调整为 1.8V 或者 2.5V。同时 LVDS 信号走线需做 差分处理,并且差分之间保持等长。

4.4 产品防护

对于产品设计,需要在各类接口加上防护电路。需按防护等级需求进行设计。

4.5 ZYNQ7010 与 ZYNQ7020 差异

7010 和 7020 在逻辑容量、管脚数量上均有差异,详细可以参考 ZYNQ7000 手册,此 处需要特别指出的是 ZYNQ7010 是没有 BANK13 的,在设计底板电路时需要特别明确,不 要出错,只有 ZYNQ7020 有此 BANK。