计算机组成原理(14) 第二章 - 主存储器与CPU的连接

主存储器(通常指内存,如 DRAM)与 CPU 的连接是计算机系统中数据和指令传输的核心通路,直接决定了整机的运行效率。这种连接并非简单的物理焊接,而是通过标准化的硬件接口、总线架构和控制逻辑实现的协同工作,核心目标是低延迟、高带宽地完成 “CPU 请求 - 内存响应” 的交互。

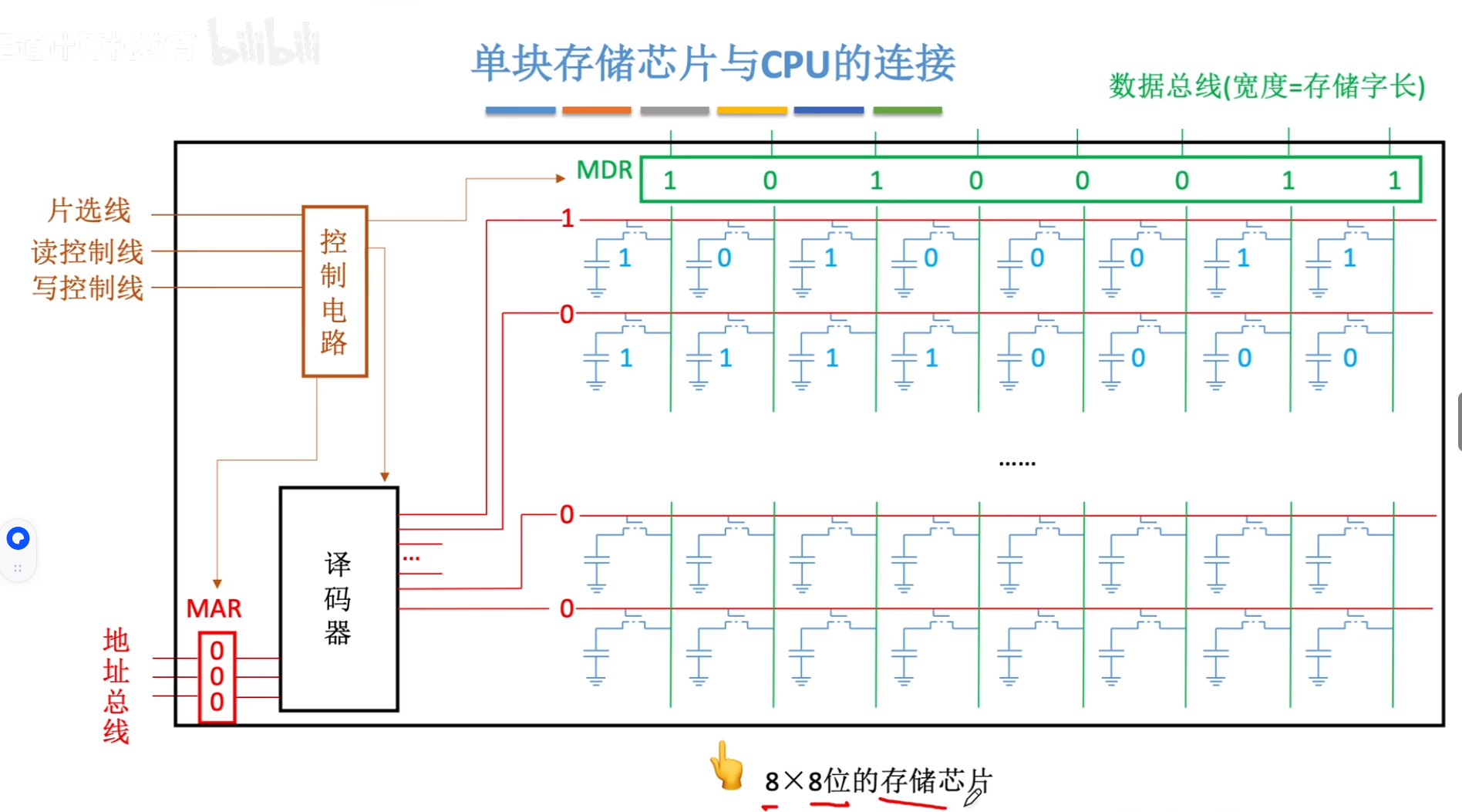

1. 单块存储芯片与CPU的连接

单块存储芯片与 CPU 的连接,核心是通过地址总线、数据总线、控制总线这三类关键信号线,实现 CPU 对存储芯片的 “寻址”“数据读写” 和 “操作控制”,最终完成数据交互。

单块存储芯片与 CPU 的连接,核心是通过地址总线、数据总线、控制总线这三类关键信号线,实现 CPU 对存储芯片的 “寻址”“数据读写” 和 “操作控制”,最终完成数据交互。

单块存储芯片无需考虑 “多芯片扩展”(如位扩展、字扩展),只需直接匹配 CPU 的总线信号,因此连接逻辑比多芯片更简洁。

单块存储芯片与 CPU 的连接,本质是通过地址总线寻址、数据总线传数、控制总线控序的 “三线协同” 实现的。核心是确保 “地址覆盖芯片容量、数据位宽匹配、控制信号极性与时序正确”,无需考虑多芯片的扩展逻辑,因此连接更直接、简洁,是多芯片存储系统(如内存模组)连接的基础。

在计算机存储系统中,单块存储芯片的容量(位数、字数)往往无法直接满足 CPU 对主存的需求(如 CPU 需要 32 位数据宽度、GB 级存储容量)。因此,需要通过位扩展和字扩展两种核心方式,将多块存储芯片组合成符合要求的主存模块,再与 CPU 连接。

在理解扩展方式前,需先明确存储芯片的两个核心参数,这是扩展的基础:

- 存储位数(位宽):芯片一次能读出 / 写入的二进制位数,如 1 位(1b)、4 位(4b)、8 位(8b)、16 位(16b)等。例如,一块 “1K×4b” 的芯片,位宽为 4b,意味着每次只能传输 4 位数据。

- 存储字数:芯片能存储的 “数据单元个数”,每个数据单元的位数即 “位宽”。字数通常用地址线的数量计算:若芯片有

n条地址线,理论上可寻址2ⁿ个数据单元(即字数为2ⁿ)。例如,10 条地址线对应2¹⁰=1024(即 1K)个字数。

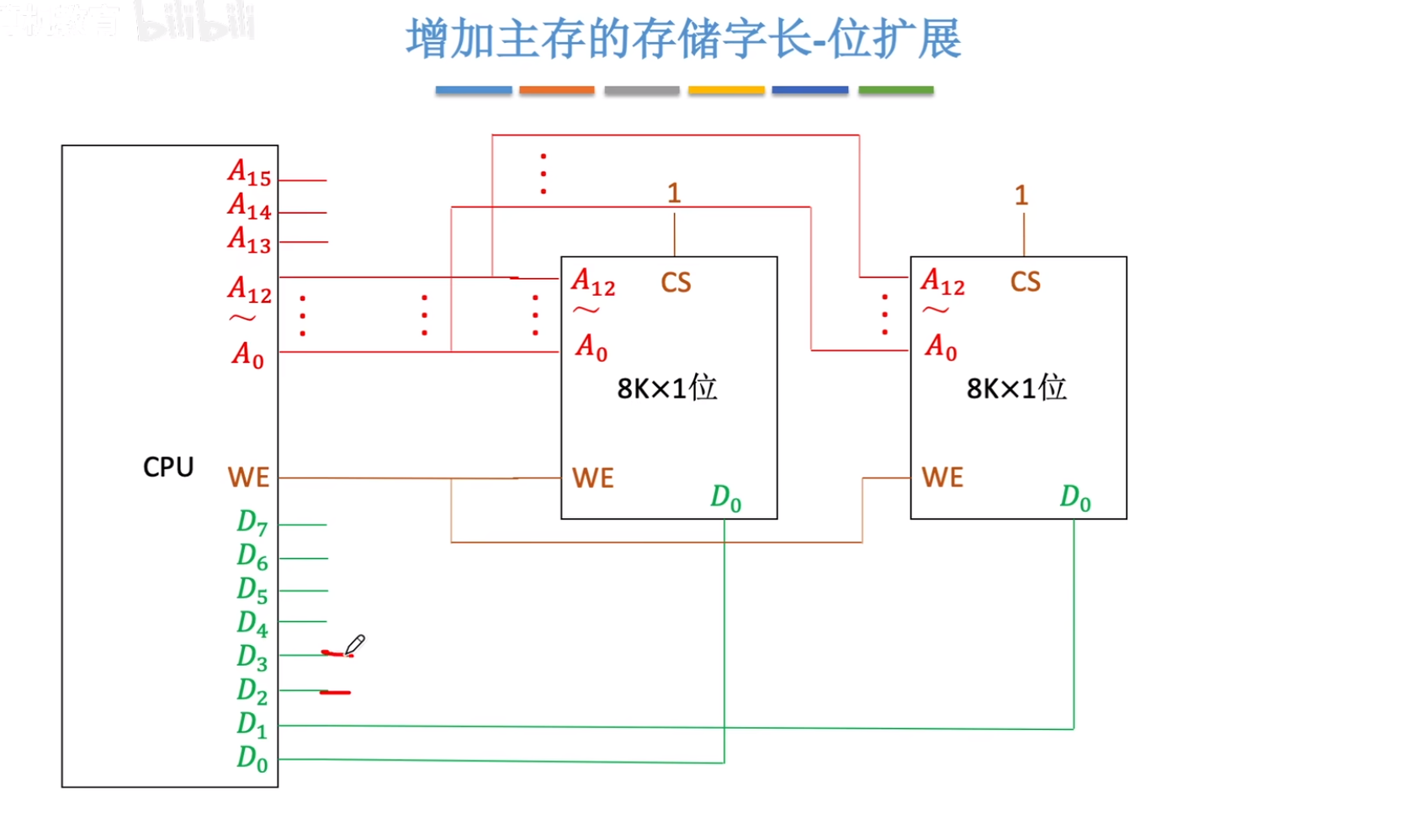

2. 位扩展(Bit Expansion):解决 “数据宽度不匹配” 问题

1. 核心目标

当单块存储芯片的位宽小于 CPU 要求的主存位宽时(如 CPU 需要 32 位数据,而芯片仅为 8 位),通过位扩展将多块芯片的 “位宽叠加”,使组合后的存储模块位宽与 CPU 一致。

2. 原理与关键特征

- 字数不变,位宽增加:扩展后存储模块的 “总字数” 与单块芯片的字数相同(地址线复用),“总位宽”= 单块芯片位宽 × 芯片数量。

- 地址线、控制线共用:所有芯片的地址线(A₀~Aₙ₋₁)、控制线(如读 / 写控制信号

WE#、片选信号CS#)完全并联(因为要同时选中所有芯片,读取 / 写入同一地址的不同位数据)。 - 数据线独立:每块芯片的数据线(D₀~Dₘ₋₁)分别连接到 CPU 数据线的不同位段,实现 “位拼接”。

3. 实例:8 位芯片扩展为 32 位主存

假设 CPU 要求主存位宽为 32 位,现有存储芯片参数为 “1M×8b”(1M=2²⁰,需 20 条地址线),则:

- 芯片数量计算:总位宽需求 ÷ 单芯片位宽 = 32b÷8b=4 块。

- 连接方式:

- 地址线:4 块芯片的地址线 A₀~A₁₉全部并联,连接到 CPU 的地址总线 A₀~A₁₉(确保同时寻址同一地址单元)。

- 控制线:4 块芯片的读 / 写控制端

WE#并联,连接到 CPU 的控制总线WE#(确保同时读或写);片选端CS#并联,由地址译码器控制(确保同时选中这 4 块芯片)。 - 数据线:

- 芯片 1 的数据线 D₀~D₇ → CPU 数据线 D₀~D₇(最低 8 位);

- 芯片 2 的数据线 D₀~D₇ → CPU 数据线 D₈~D₁₅(次低 8 位);

- 芯片 3 的数据线 D₀~D₇ → CPU 数据线 D₁₆~D₂₃(次高 8 位);

- 芯片 4 的数据线 D₀~D₇ → CPU 数据线 D₂₄~D₃₁(最高 8 位)。

- 扩展后效果:存储模块参数为 “1M×32b”,位宽与 CPU 匹配,可一次向 CPU 传输 32 位数据。

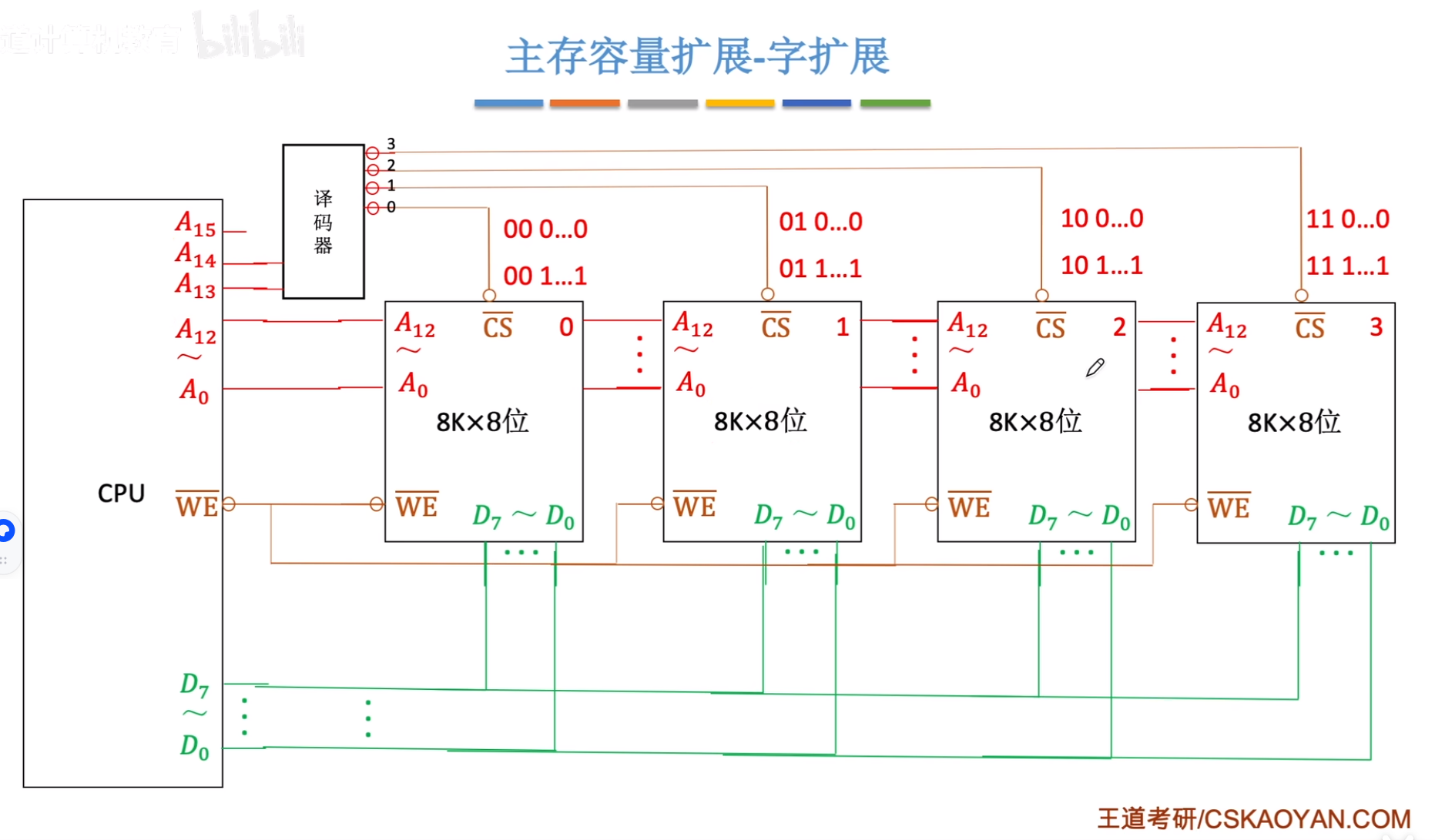

3. 字扩展(Word Expansion):解决 “存储容量不足” 问题

1. 核心目标

当单块存储芯片的总存储容量(字数 × 位宽)小于 CPU 要求的主存容量时(如 CPU 需要 4GB 主存,而单块芯片仅为 1GB),通过字扩展增加 “总字数”,使组合后的存储模块容量满足需求。

2. 原理与关键特征

- 位宽不变,字数增加:扩展后存储模块的 “总位宽” 与单块芯片的位宽相同(数据线复用),“总字数”= 单块芯片字数 × 芯片数量。

- 地址线拆分:CPU 地址总线分为两部分:

- 低位地址线(A₀~Aₙ₋₁):并联到所有芯片的地址线,用于寻址单块芯片内的具体数据单元;

- 高位地址线(Aₙ~Aₘ₋₁):连接到地址译码器,生成不同的 “片选信号”(

CS#),每次仅选中一块芯片(确保不同芯片对应不同的地址空间,避免冲突)。

- 数据线、控制线共用:所有芯片的数据线(D₀~Dₖ₋₁)、读 / 写控制线(

WE#)完全并联。

实例:1M×8b 芯片扩展为 4M×8b 主存

假设需构建 “4M×8b” 的主存(4M=2²²,需 22 条地址线),现有芯片为 “1M×8b”(1M=2²⁰,需 20 条地址线),则:

- 芯片数量计算:总字数需求 ÷ 单芯片字数 = 4M÷1M=4 块。

- 连接方式:

- 地址线拆分:

- 低位地址线(A₀~A₁₉):并联到 4 块芯片的地址线 A₀~A₁₉(寻址芯片内单元);

- 高位地址线(A₂₀~A₂₁):连接到 2-4 线地址译码器(2 条高位地址可生成 4 个不同的片选信号,对应 4 块芯片)。

- 控制线:

- 4 块芯片的

WE#并联,连接到 CPU 的WE#; - 译码器的 4 个输出端(Y₀~Y₃)分别连接到 4 块芯片的

CS#(每次仅 Y₀~Y₃中的一个有效,选中对应芯片)。

- 4 块芯片的

- 数据线:4 块芯片的数据线 D₀~D₇全部并联,连接到 CPU 的数据线 D₀~D₇(位宽不变)。

- 地址线拆分:

- 扩展后效果:存储模块参数为 “4M×8b”,容量从 1M×8b 提升到 4M×8b,地址空间覆盖 00000H~3FFFFH(4M 地址)

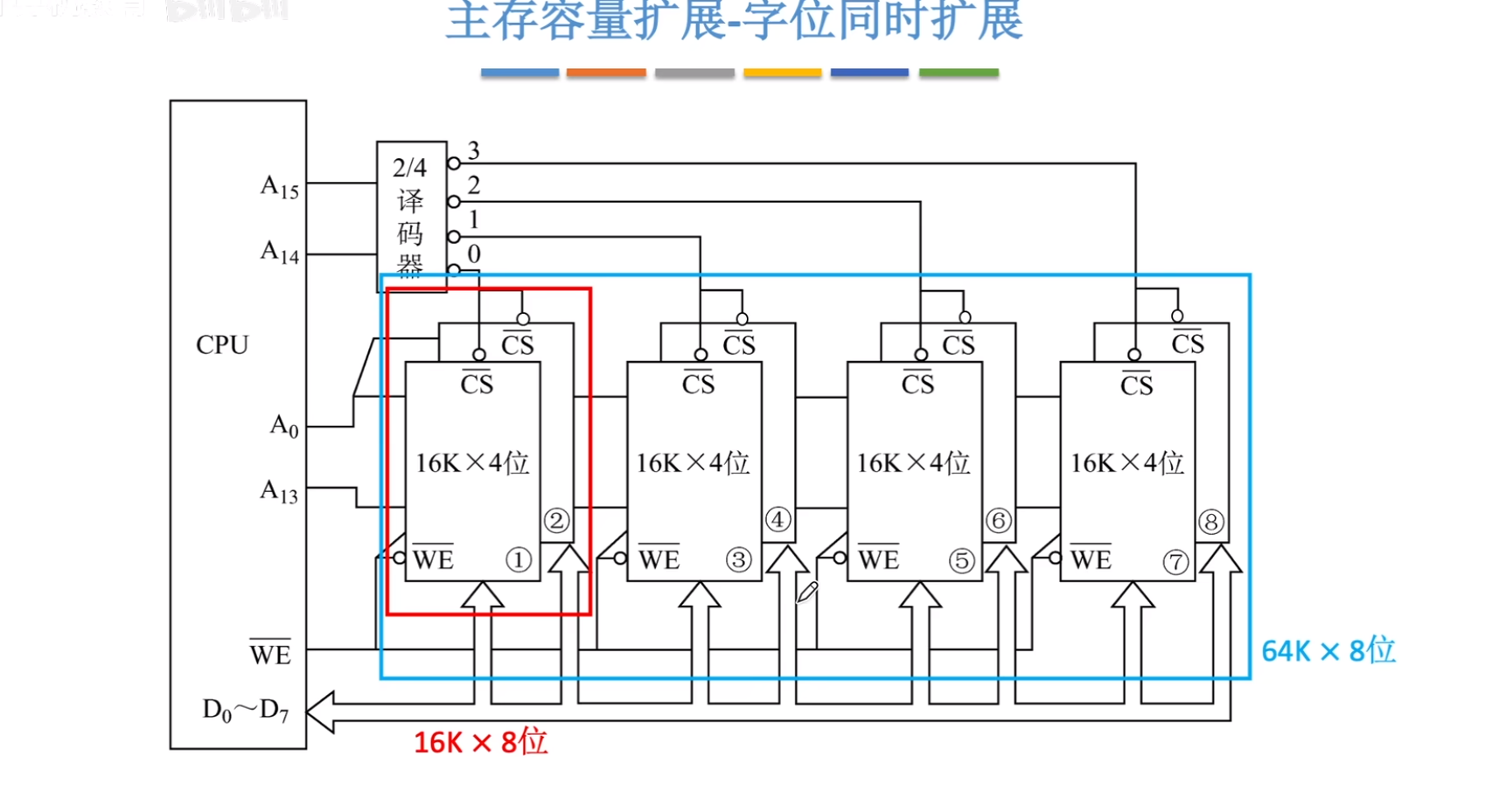

4. 字位同时扩展

实际场景中,主存往往既需要 “位宽匹配”,又需要 “容量足够”,此时需同时使用位扩展和字扩展(即复合扩展)。

实例:构建 “4M×32b” 主存

需求:CPU 要求主存位宽 32 位、容量 4M×32b(16MB)。

现有芯片:1M×8b(每块容量 8MBit=1MB)。

步骤:

- 先位扩展:用 4 块 1M×8b 芯片组成 “1M×32b” 模块(位宽从 8b→32b,满足位宽需求),此时 1 个 “位扩展模块” 容量为 1M×32b(4MB)。

- 再字扩展:需 4 个 “1M×32b” 模块,才能组成 4M×32b(16MB)容量(总字数从 1M→4M)。

- 总芯片数:4(位扩展)×4(字扩展)=16 块。

- 连接逻辑:

- 每个 “位扩展模块” 内部:4 块芯片地址线、控制线并联,数据线分接 CPU 32 位数据线的不同 8 位段;

- 4 个 “位扩展模块” 之间:低位地址线(A₀~A₁₉)并联,高位地址线(A₂₀~A₂₁)译码后分别控制 4 个模块的片选端(每次选中 1 个模块)。

通过位扩展、字扩展及复合扩展,可灵活组合存储芯片,最终实现与 CPU 地址总线、数据总线、控制总线完全匹配的主存系统,确保 CPU 能高效地进行数据读写。

5. 磁盘存储器

磁盘存储器是计算机中最常用的辅助存储器(外存) 之一,主要用于长期、大容量存储数据(如操作系统、应用程序、文档、媒体文件等),特点是容量大、成本低、非易失性(断电后数据不丢失),但读写速度远低于主存储器(内存)。

磁盘存储器的核心概念与分类

| 存储介质 | 机械硬盘(HDD) | 依赖物理盘片旋转 + 磁头移动,有机械运动部件,易受震动影响 | 台式机、服务器大容量存储 |

| 固态硬盘(SSD) | 基于 NAND 闪存芯片,无机械部件,依赖电子信号读写,抗震动、速度快 | 笔记本、高性能 PC、服务器 | |

| 盘片数量 | 单盘磁盘 | 仅 1 张盘片,容量较小,结构简单 | 早期小型设备、嵌入式系统 |

| 多盘磁盘 | 多张盘片叠放(如 HDD 常见 2-8 张),容量大,通过多磁头并行提升效率 | 主流 HDD/SSD(多芯片封装) | |

| 接口类型 | SATA 接口 | 传输速率中等(SATA III 最高 6Gbps),兼容性强,广泛用于消费级设备 | 家用 PC 的 HDD/SSD |

| NVMe 接口(PCIe 协议) | 直接基于 PCIe 总线,速率极高(PCIe 4.0 x4 达 32Gbps),延迟低 | 高性能 SSD(如游戏本、工作站) | |

| SAS 接口 | 可靠性高、支持热插拔,速率接近 SATA,主要用于服务器 | 企业级服务器 HDD/SSD |

机械硬盘(HDD)的结构与工作原理

HDD 是传统磁盘存储器的代表,核心是 “机械运动 + 磁记录”,结构和原理是理解磁盘存储的基础:

1. 核心物理结构

- 盘片(Platter):铝合金 / 玻璃基底,表面涂覆磁性材料(如钴合金),数据存储在盘片的 “磁道” 上。

- 磁头(Head):悬浮在盘片表面(距离约 3-5 纳米),负责 “读写磁信号”—— 写时通过电流改变磁畴方向,读时感应磁畴变化产生电流。

- 主轴电机(Spindle Motor):带动盘片高速旋转(常见转速:5400 转 / 分、7200 转 / 分,服务器级可达 15000 转 / 分),为磁头读写提供 “相对运动”。

- 磁头臂与驱动机构:带动磁头沿盘片径向移动,实现不同 “磁道” 的切换。

2. 数据存储逻辑:磁道、扇区、柱面

为了精准定位数据,HDD 的盘片被划分为多层逻辑结构,类似 “同心圆唱片”:

- 磁道(Track):盘片表面的同心圆,每个同心圆是一个磁道(半径不同,周长不同,但存储容量相同,因内圈磁道密度更高)。

- 扇区(Sector):每个磁道被等分为多个 “扇区”,是 HDD 的最小读写单位(早期 512 字节,现在主流 4096 字节,即 “4K 扇区”)。

- 柱面(Cylinder):多盘 HDD 中,所有盘片上 “半径相同的磁道” 组成一个柱面(如 2 张盘片共 4 个面,每个面的第 3 号磁道组成 “第 3 柱面”)。

注:HDD 读写时优先按 “柱面” 访问(减少磁头移动距离),提升效率。

5.1 磁盘阵列

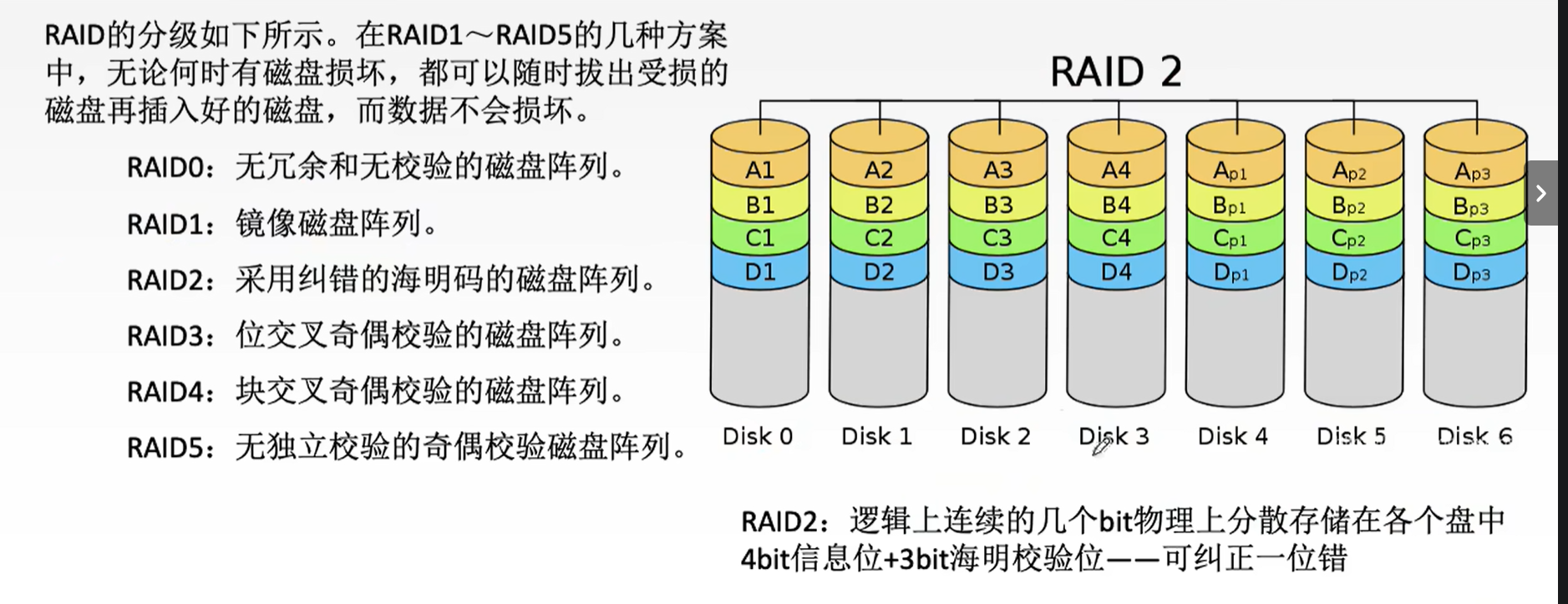

磁盘阵列,全称为独立磁盘冗余阵列(Redundant Arrays of Independent Disks,简称 RAID),是一种把多个硬盘组合起来,以提供比单个磁盘更高的存储性能和数据冗余高可靠性的存储技术。

- 按 RAID 级别分类:常见的有 RAID 0、1、5、6、10 等。RAID 0 通过数据条带化提高性能但无冗余;RAID 1 采用数据镜像,可靠性高但磁盘利用率低;RAID 5 使用分布式奇偶校验,兼顾性能与安全;RAID 6 在此基础上增加双重奇偶校验,可容忍两块磁盘故障;RAID 10 结合了条带化和镜像,兼具高性能和高可靠性。

应用场景

主要应用于企业级存储、数据中心、大规模数据库、大数据分析等领域,也有部分 PC 用户在自己的机器上使用硬件或软件 RAID 系统。

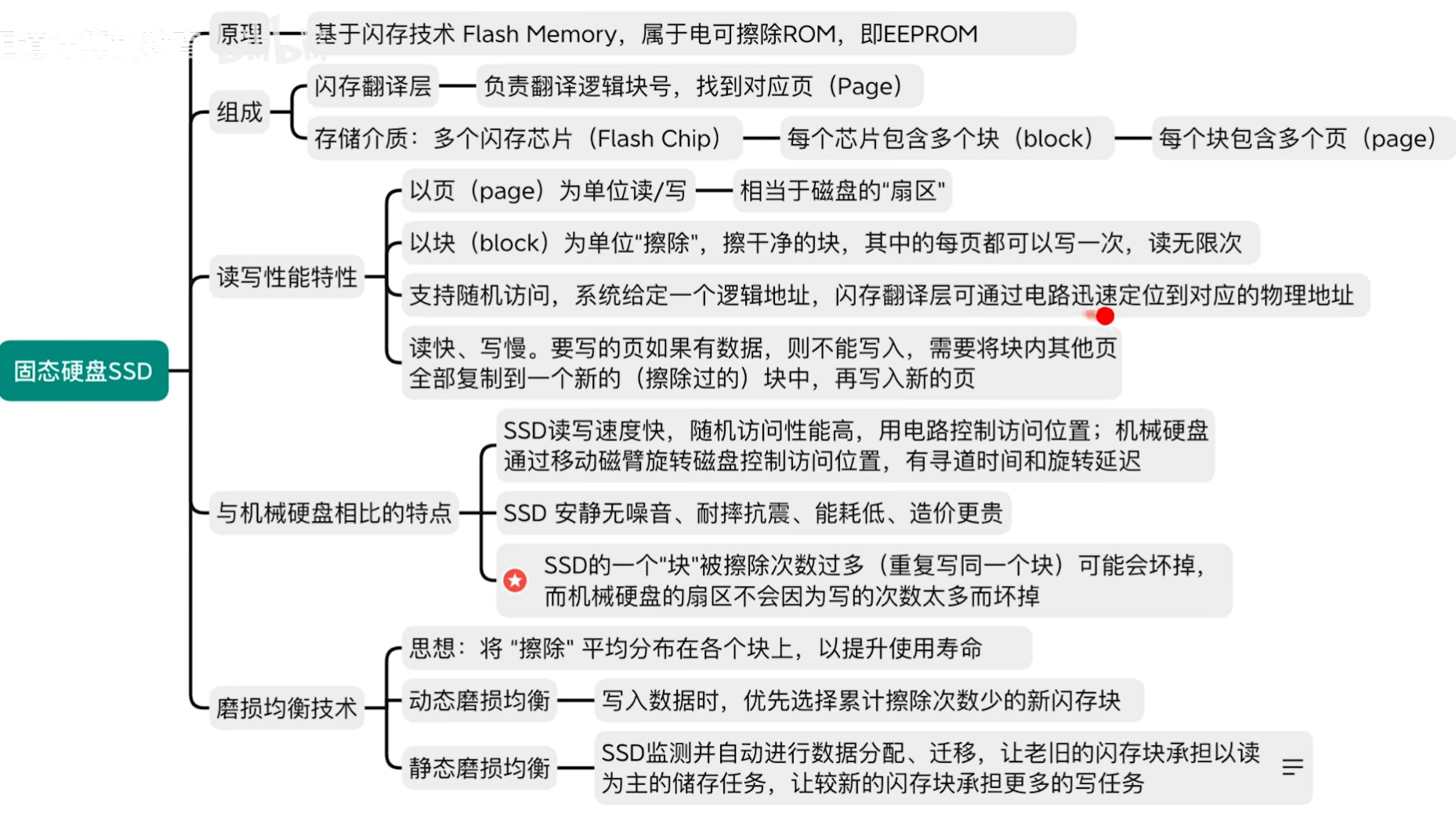

6. 固态硬盘SSD

固态硬盘(Solid State Drive,简称 SSD)是一种使用闪存存储数据的数据存储设备。

6.1 组成与工作原理

- 核心组件:包括闪存芯片(NAND Flash),这是存储数据的基本单元,分为 SLC、MLC、TLC、QLC 等类型,性能与寿命依次递减;控制器,相当于 SSD 的大脑,负责管理数据的读写操作、执行错误校正、优化性能和延长闪存寿命等任务;缓存,为了提高数据读写速度,SSD 通常会配备一定容量的缓存,缓存可以是 DRAM,也可以是闪存本身的一部分。

- 工作原理:基于闪存的存储机制,闪存是一种非易失性存储介质,其基本存储单元是浮栅晶体管,通过控制电压在浮栅中存储电荷来表示二进制信息。数据的读写操作通过控制器来完成,读操作时,控制器从指定地址读取数据并传输给主机;写操作时,由于闪存写入前需先擦除原有数据,且擦除操作以 “块” 为单位,写入操作以 “页” 为单位,所以控制器会使用 “垃圾回收” 和 “磨损均衡” 等技术来优化性能和延长闪存寿命。

接口类型

SATA 接口:是最常见的 SSD 接口,主要用于消费级市场,传输速率一般为 6Gbps。

PCIe 接口:具有更高的传输速率,通常用于高性能计算和数据中心等领域,可提供几 GBps 的传输速率。

M.2 接口:是一个小型化的接口标准,广泛应用于超薄笔记本、台式机和服务器等设备,可支持 SATA 和 PCIe 两种模式,PCIe 模式的 M.2 SSD 性能更为强劲。

NVMe 接口:是一种针对 SSD 优化的协议,专为 PCIe 接口设计,性能比传统的 AHCI 协议更为出色,延迟更低,读写速度更快。

优势与不足

- 优势:读写速度快,尤其是随机读写性能远高于传统机械硬盘(HDD),能使系统启动、程序加载和文件传输等操作更迅速;功耗低,没有机械部件,有助于延长移动设备的电池续航时间;可靠性高,不容易受到震动和冲击的影响,数据丢失风险较低,且故障模式相对可预测;噪音低,工作时几乎没有噪音。

- 不足:成本较高,单位存储成本仍然高于 HDD;寿命有限,闪存单元的写入次数有限,长时间大量写入操作可能导致性能下降甚至损坏;容量有限,目前市场上的 SSD 容量通常在几十 GB 到几 TB 之间,在极大容量存储方面不及 HDD。