二、二选一多路器的设计流程

dd1.设计输入(编写verilog语言代码)

module mux2(

/*

整个模块所存在端口

*/a,b,sel,out

);

/*

对端口进行定义

*/input a;input b;input sel;output out;

/*

二选一多路器

assign表示赋值语句

(sel==1)?a:b,sel==1条件满足把a赋给out,条件不满足把b赋给out

*/ assign out = (sel==1)?a:b;endmodule2.分析和综合

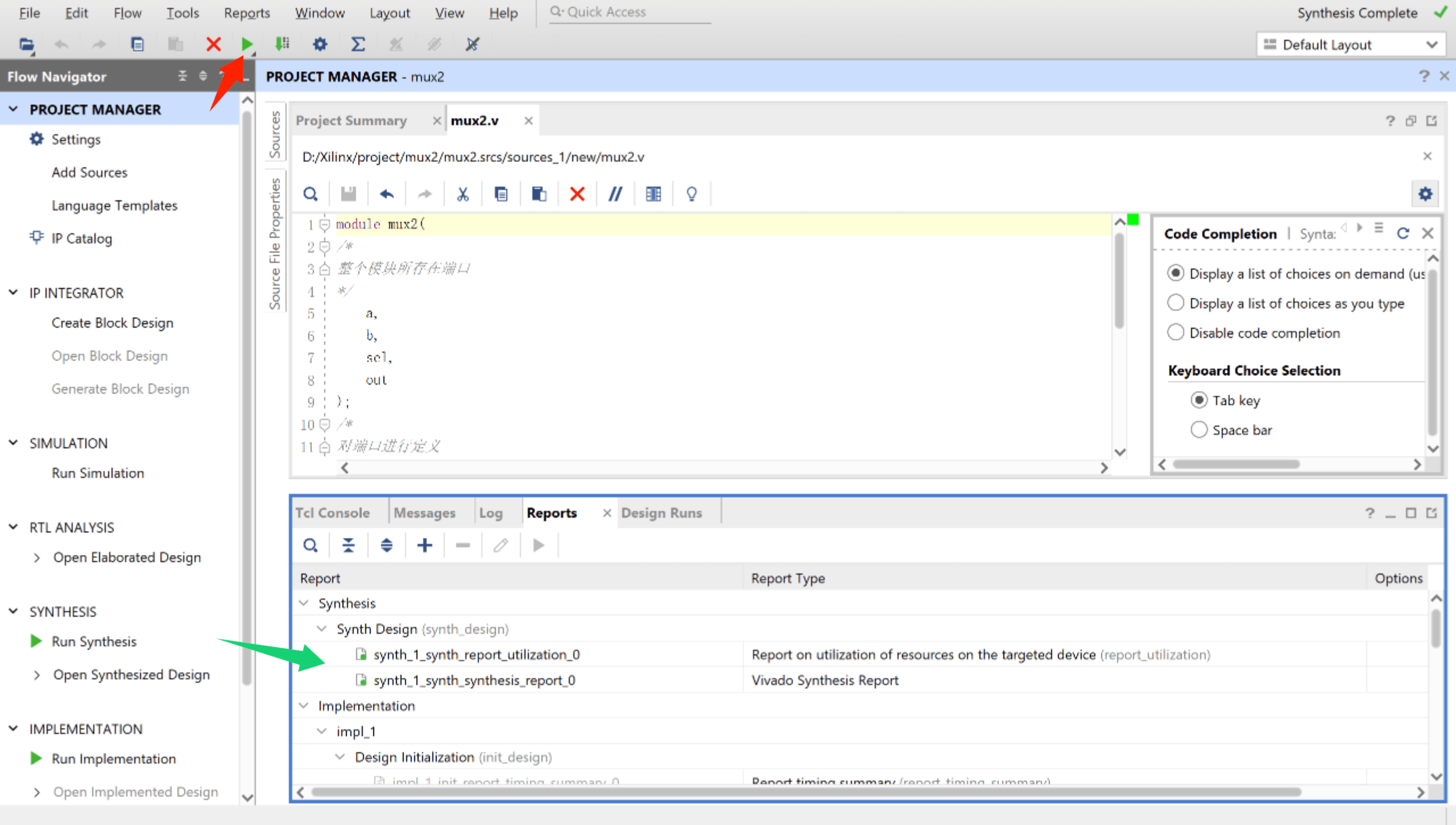

点击红色箭头按钮选择'Run Synthesis',右上角圈圈在转表明在运行,运行完后选则观察报告,如绿色箭头所示,没有红色报错,说明语法和逻辑错误。

3.仿真

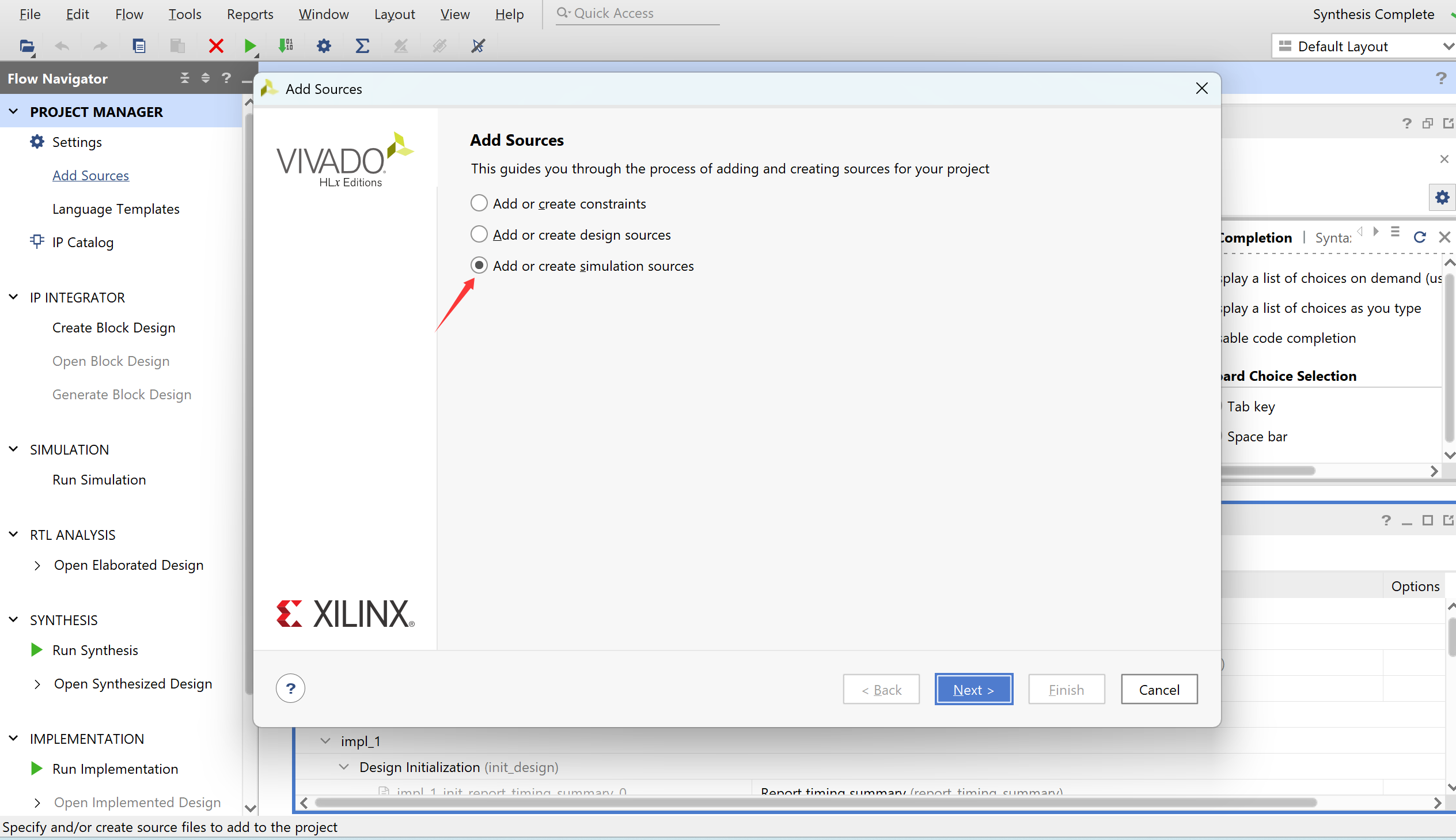

a.创建仿真文件

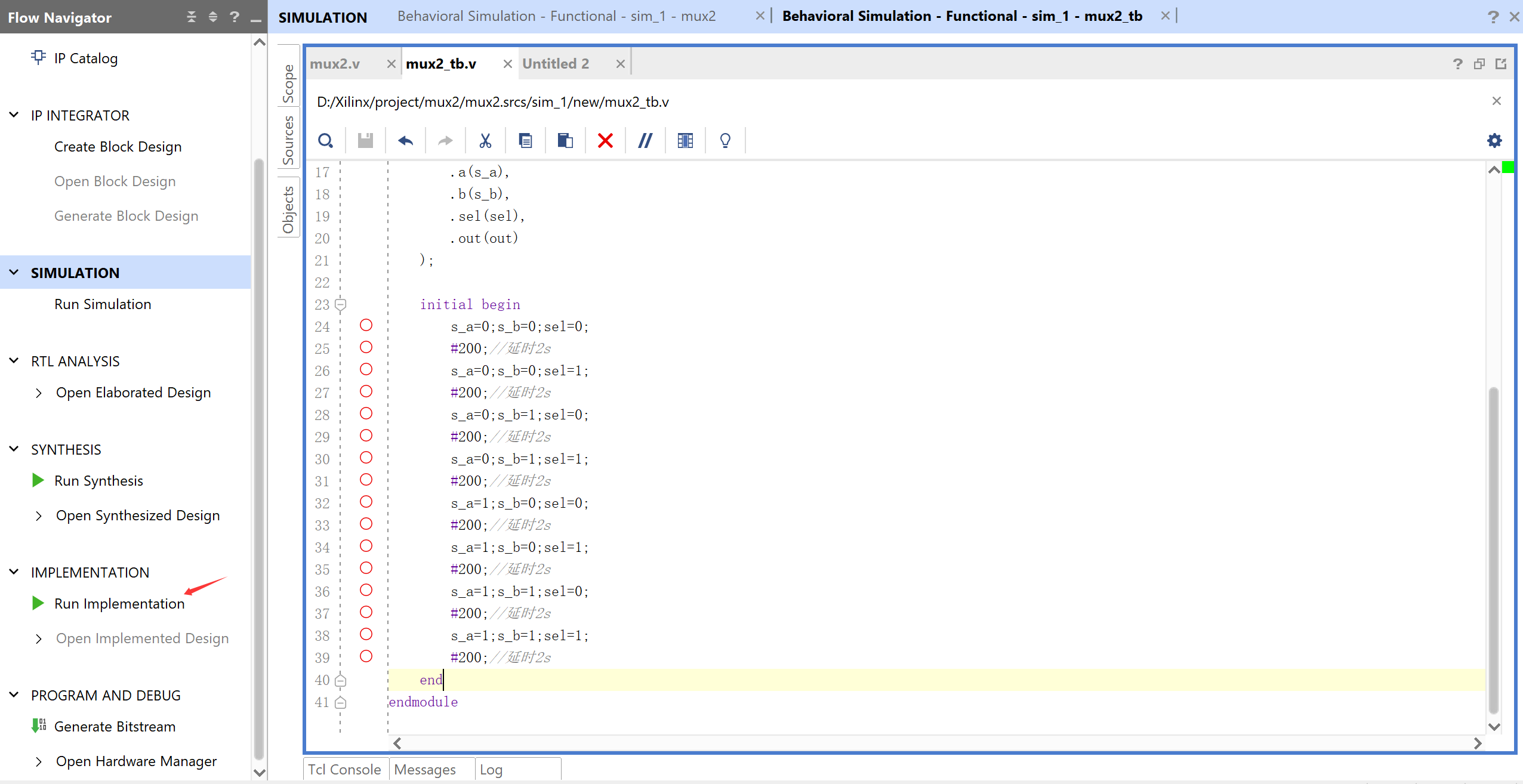

b.仿真代码

`timescale 1ns / 1nsmodule mux2_tb();

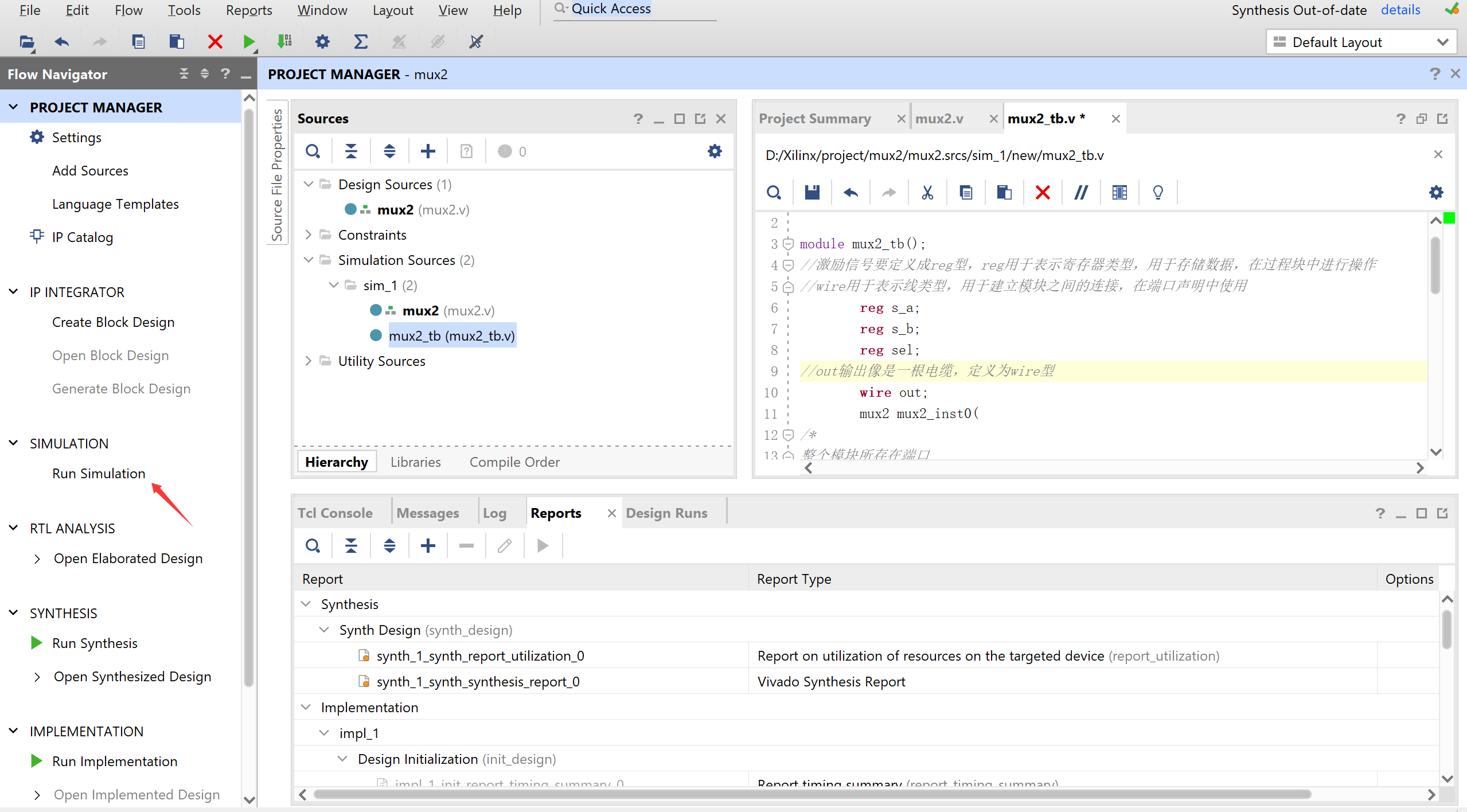

//激励信号要定义成reg型,reg用于表示寄存器类型,用于存储数据,在过程块中进行操作

//wire用于表示线类型,用于建立模块之间的连接,在端口声明中使用reg s_a;reg s_b;reg sel;

//out输出像是一根电缆,定义为wire型wire out;mux2 mux2_inst0(

/*

整个模块所存在端口

*/.a(s_a),.b(s_b),.sel(sel),.out(out));initial begins_a=0;s_b=0;sel=0;#200;//延时2ss_a=0;s_b=0;sel=1;#200;//延时2ss_a=0;s_b=1;sel=0;#200;//延时2ss_a=0;s_b=1;sel=1;#200;//延时2ss_a=1;s_b=0;sel=0;#200;//延时2ss_a=1;s_b=0;sel=1;#200;//延时2ss_a=1;s_b=1;sel=0;#200;//延时2ss_a=1;s_b=1;sel=1;#200;//延时2send

endmodulec.进行仿真

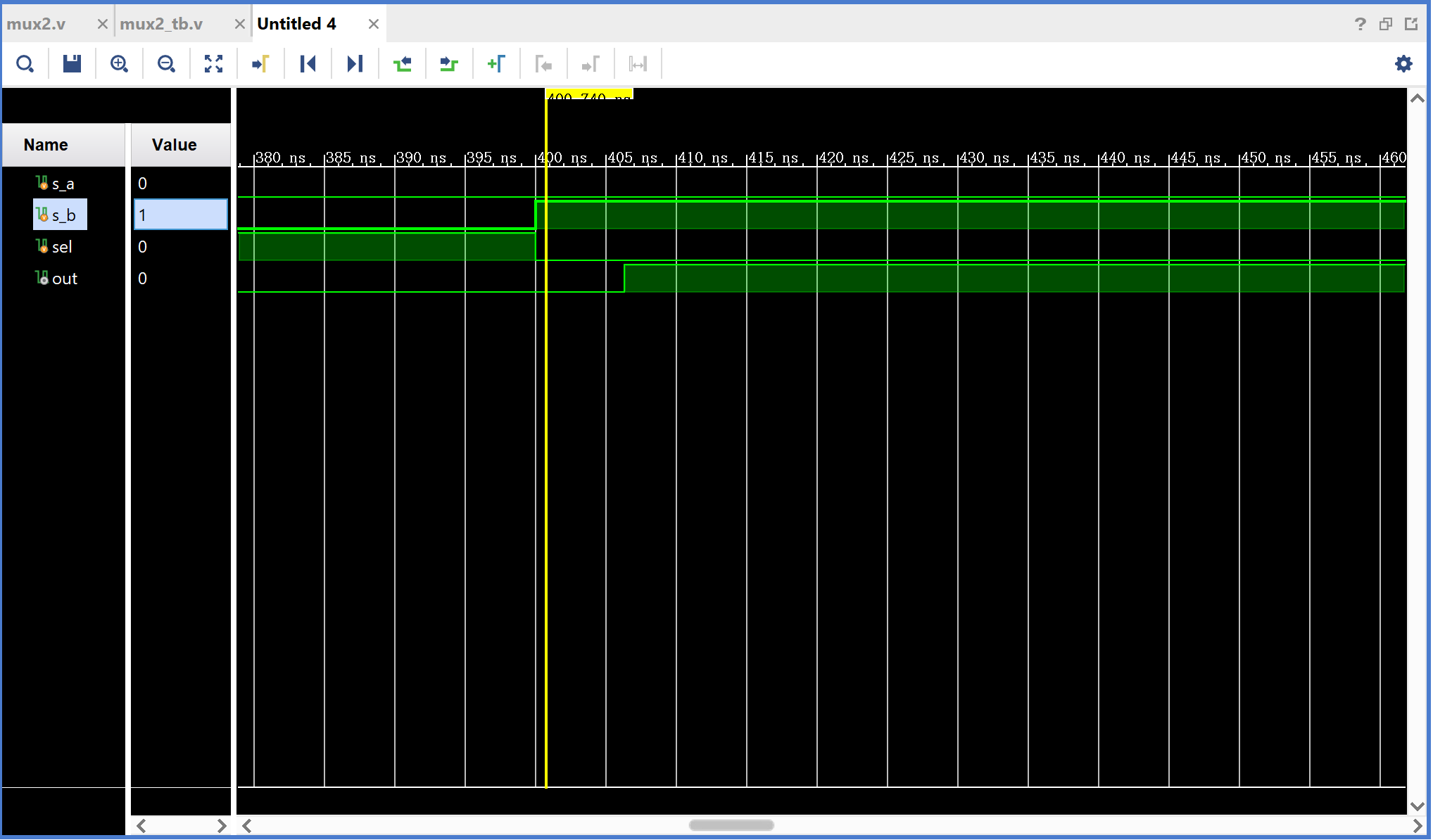

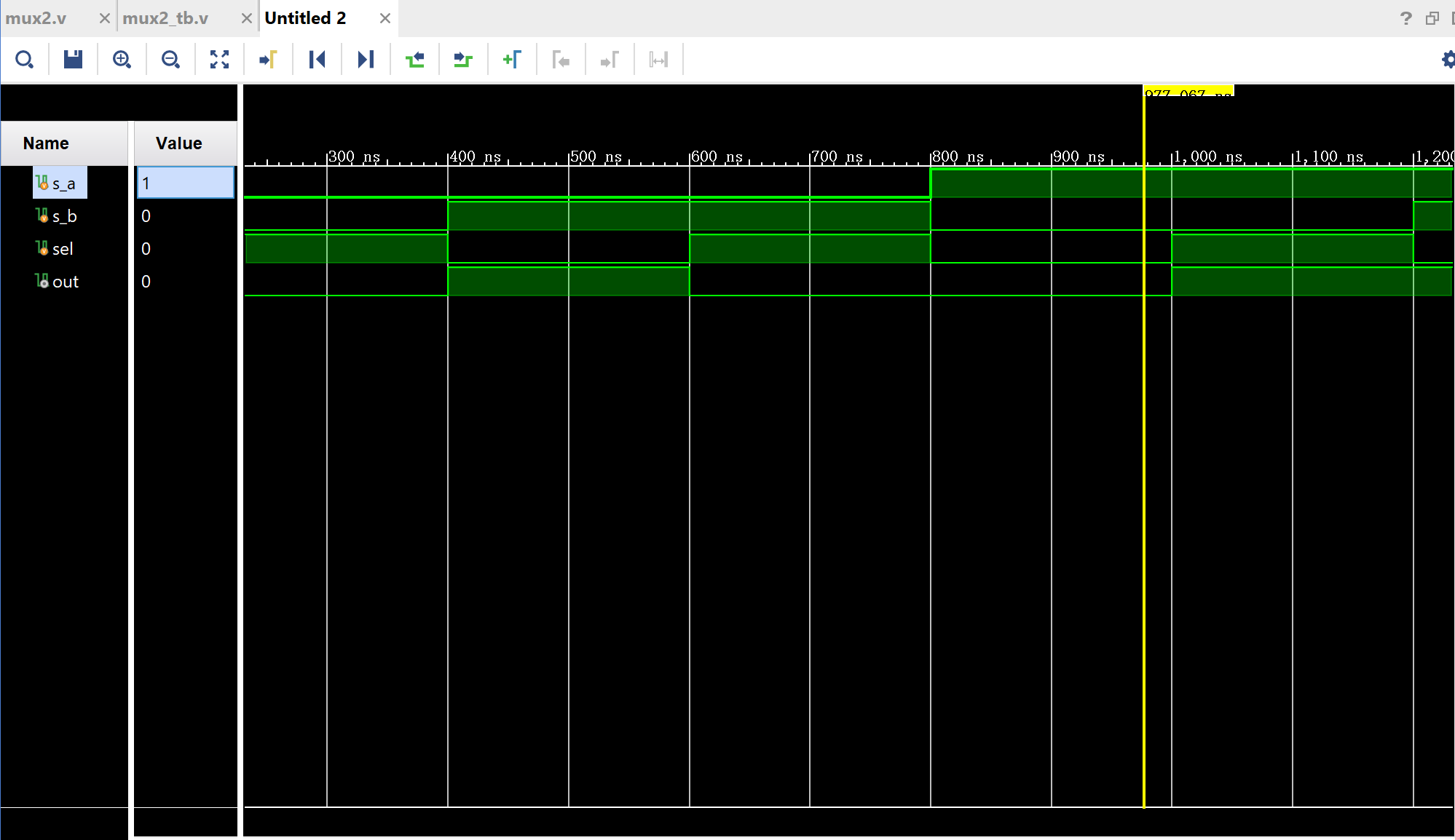

d.仿真结果

4.布局布线

布局布线之后再次仿真,发现out信号变化出现延迟。