20250928的学习笔记

一、线与(Wired-AND)特性

1.定义

多个开漏/集电极输出共用一条上拉线,任一器件拉低 → 总线即为低电平;只有全部器件释放时,上拉电阻才把总线置高。

2.本质

物理线实现负逻辑与运算

3.关键条件

①输出级必须是开漏(OD)或开集(OC);

②单根上拉电阻提供高电平电流路径。

4.典型应用

I²C、SMBus、One-Wire、多中断源“线或”报警、总线仲裁。

5.优点

①无源冲突,支持多主仲裁;

②电平兼容不同电压域;

③硬件自动完成“与”逻辑,省门电路。

A输出 | B输出 | 总线电平 | 逻辑结果 |

|---|---|---|---|

0 (拉低) | 0 (拉低) | 低 (L) | 0 |

0 (拉低) | 1 (高阻) | 低 (L) | 0 |

1 (高阻) | 0 (拉低) | 低 (L) | 0 |

1 (高阻) | 1 (高阻) | 高 (H) | 1 |

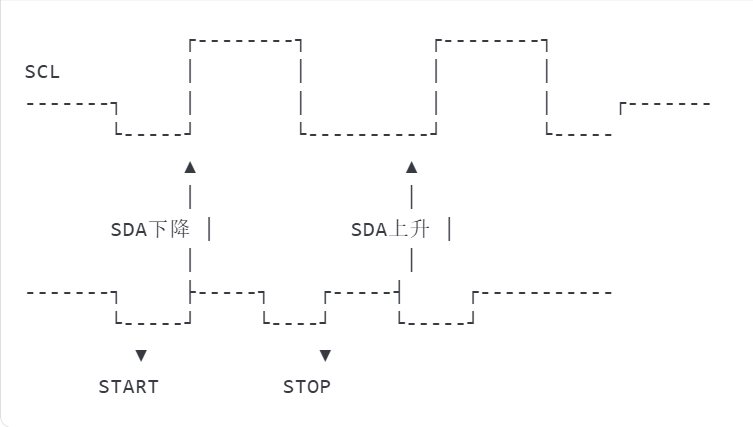

二、I2C的start信号和stop信号

1.时序图

2.定义

START (S):

SDA 从高到低的跳变,且 SCL 保持高电平。

作用:复位所有从机移位器,准备接收 7 位地址 + R/W̅。

STOP (P):

SDA 从低到高的跳变,且 SCL 保持高电平。

作用:结束当前传输,释放总线,从机返回空闲。

3 关键要点

①唯一性:

数据位只允许在 SCL 低电平期间 改变;任何 SDA 跳变 + SCL = 1 只能是 S 或 P。

②重复起始(Sr):

与 START 波形完全相同,只是出现在一次传输中间(无前置 STOP),用来切换方向或设备。

③总线状态:

检测到 S → 总线变为 Busy (I2SR.IBB=1)

检测到 P → 总线变为 Free (I2SR.IBB=0)

三、I2C通信时序

1.START

SCL高➡SDA下降沿,总线忙。

2.地址 + R/W

7位从地址 + 1位方向(0写/1读),MSB先出;第9时钟从机回ACK(拉低SDA)。

3.数据帧

每8bit后跟紧1ACK,方向由R/W决定;主机读时在第末字节回NACK(释放SDA高)。

4.重复START(可选)

不释放总线,再次发地址 + 新R/W,切方向。

5.STOP

SCL高➡SDA上升沿,总线空闲。