FPGA学习篇——Verilog学习之全加器的实现

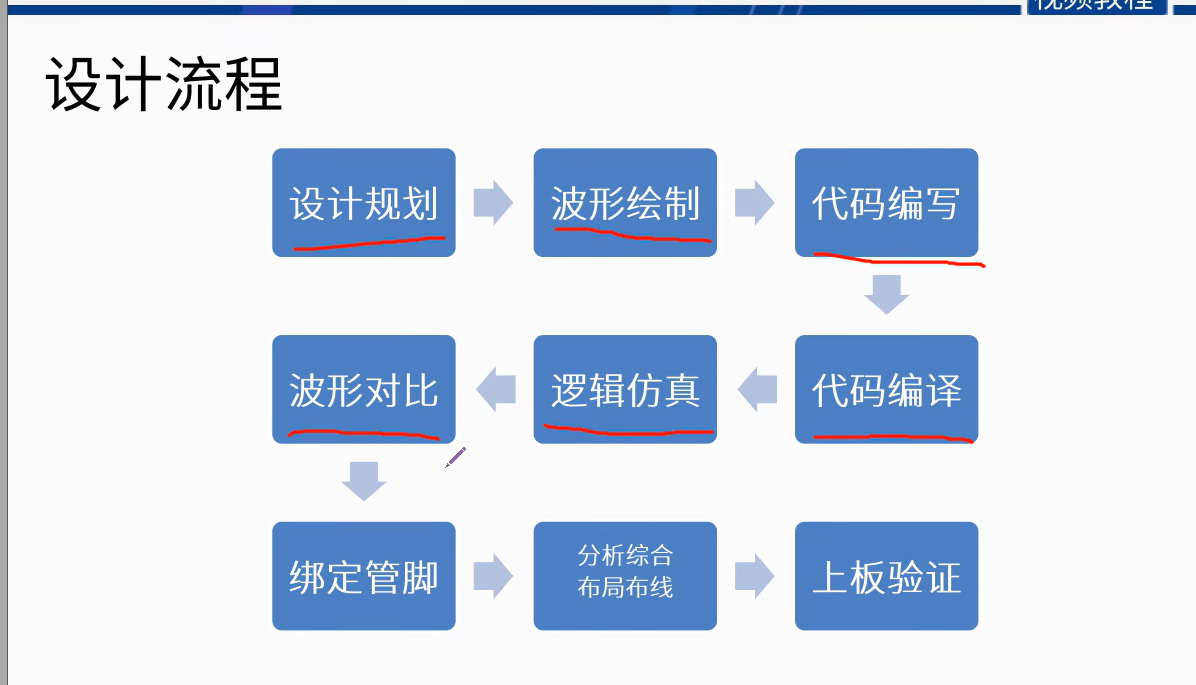

PS:目前手上仍然没有板子,按照野火视频的讲解,目前我们只能做到前面六步(其实第一步设计规划也是需要看板子的硬件的,但是现在没有板子就完全与野火传授的板子一致来看)

1 设计规划及真值表(波形绘制)

全加器原理:

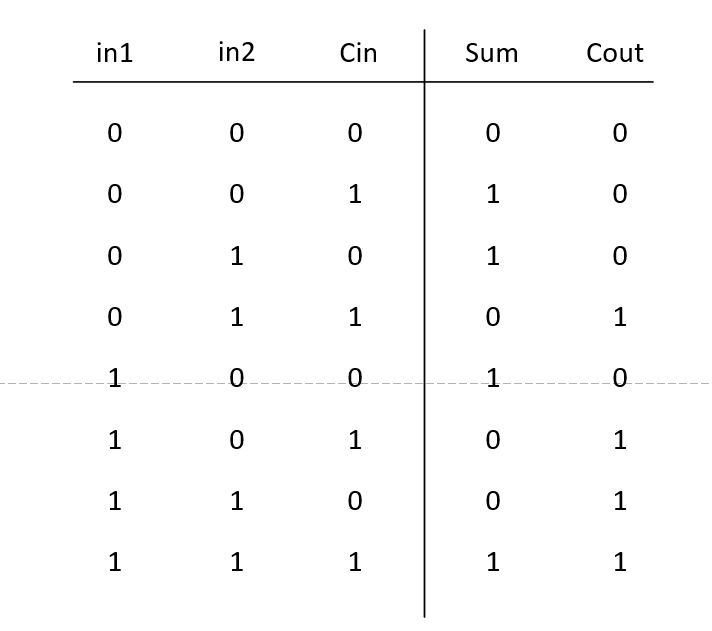

方法一:全加器的实现原理可以像上一节半加器的实现原理来解释——通过真值表得到全加器两个输出的表达式(此前也写了一篇全加器的实现,主要是写了两个公式的理解,有兴趣可以看看):

(当输入有奇数个1时,Sum输出为1)

(至少有两个输入为1时,Cout为1)

方法二:使用半加器来实现全加器

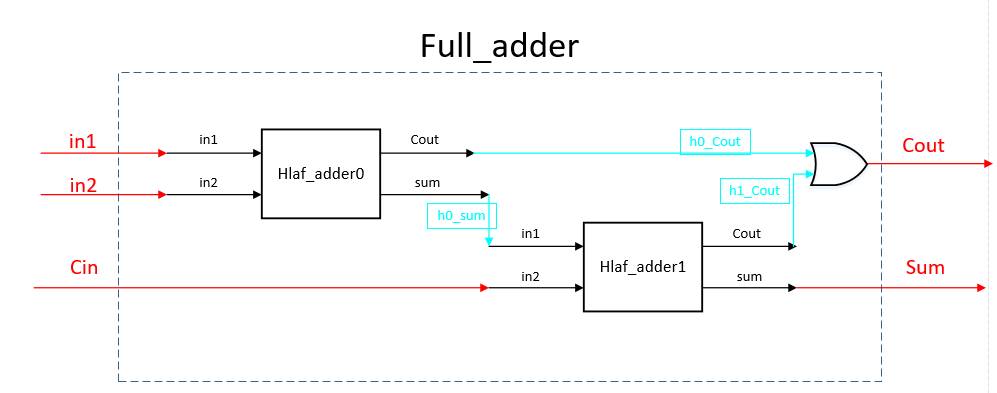

两个半加器来实现一个全加器,先让两个输入进入半加器算出结果作为sum,再与另一个输入相加,则可以得到in1+in2+Cin的结果;而Cout则是两个半加器只要有其中一个输出有进位,Cout就为1(所以用一个或门表示)。

在这里我们主要使用原理二来实现全加器,即使用层次化的思想用两个半加器加一个或门来实现全加器。

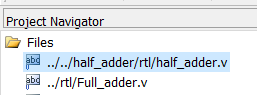

思路:我们上一节已经写好了一个半加器的.v文件,如图只需要把对应信号连接起来再加一个或门即可(所以要把半加器的.v文件加到工程中)。

(1)写Full_adder时,module........endmodule的架构,输入输出信号要写好。Full_adder 有in1,in2,Cin三个输入,Cout 和 Sum 两个输出。

Full_adder 有in1,in2,Cin三个输入,对应分别连接到Half_adder0的in1,in2和Half_adder1的in2; Full_adder 有Cout 和 Sum 两个输出,对应连接到或门输出(assign语句实现或门)和Half_adder1 的输出sum。

(2)同时由图中可以看到,我们需要三个中间信号h0_sum、h1_Cout、h0_Cout来连接其余部分,因此这是除了Full_adder 输入输出外,另外定义的三个中间信号(编写代码时写在module块的外面。)

2 代码编写

根据1 中的思路,编写代码:

module Full_adder

(input in1 ,input in2 ,input Cin ,output Sum ,output Cout);wire h0_sum ;

wire h0_Cout ;

wire h1_Cout ;half_adder half_adder0_inst

(.in1 (in1),.in2 (in2),.sum (h0_sum),.Cout (h0_Cout));half_adder half_adder1_inst

(.in1 (h0_sum),.in2 (Cin),.sum (Sum),.Cout (h1_Cout));assign Cout = h0_Cout | h1_Cout;endmodule3 逻辑仿真及波形验证

编写仿真文件:

`timescale 1ns/1nsmodule tb_Full_adder();reg tb_in1;

reg tb_in2;

reg tb_Cin;wire tb_Cout;

wire tb_Sum;initial begintb_in1 <= 1'b0; tb_in2 <= 1'b0;tb_Cin <= 1'b0;

endalways #10 tb_in1 <= {$random} % 2;

always #10 tb_in2 <= {$random} % 2;

always #10 tb_Cin <= {$random} % 2;Full_adder Full_adder_inst

(.in1(tb_in1),.in2(tb_in2),.Cin(tb_Cin),.Sum(tb_Sum),.Cout(tb_Cout)

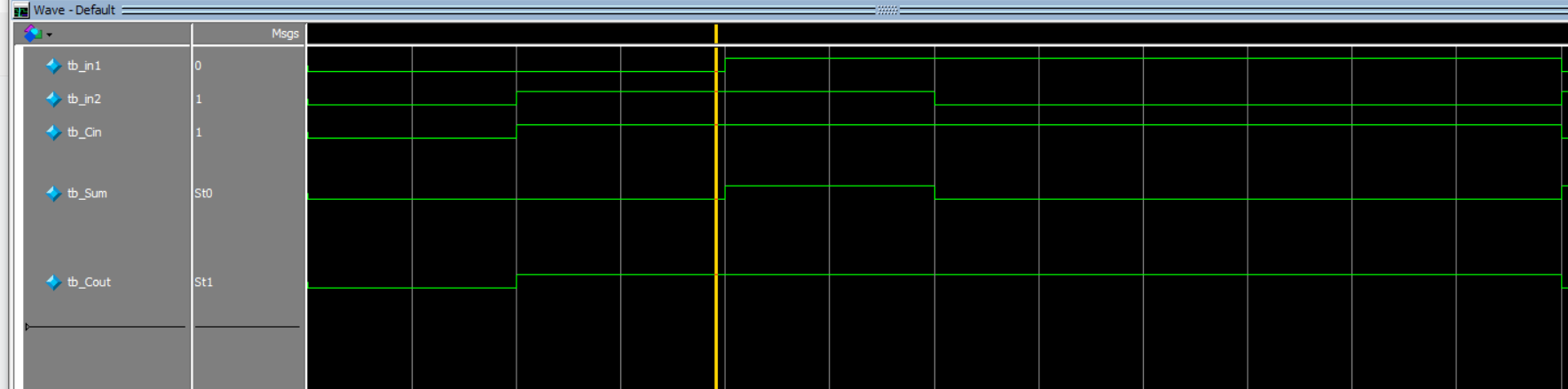

);endmodule波形图种可以看到,能够对应真值表的内容,仿真验证通过。

(本贴仅是个人经验,参考哔哩哔野火视频:10-第九讲-层次化设计_哔哩哔哩_bilibili如有侵权请联系我~)