ARM芯片架构之CoreSight SoC-400组件详解

在现代 SoC(系统芯片)设计中,调试和追踪功能对于确保系统的稳定性和性能至关重要。ARM 的 CoreSight SoC-400 提供了一套灵活、模块化的调试和追踪组件,广泛应用于多核处理器系统的开发。本文将深入探讨 CoreSight SoC-400 的各个组件及其功能,帮助开发者更好地理解和应用这一技术。

1. CoreSight SoC-400 概述

CoreSight SoC-400 是 ARM 提供的一套用于 SoC 的调试和追踪解决方案。它由多个可配置的组件组成,支持从单核到多核的处理器系统,提供全面的调试和追踪功能。这些组件包括:调试访问端口(DAP)、系统追踪宏单元(STM)、追踪内存控制器(TMC)、时间戳生成器(TSG)、交叉触发接口(CTI)、交叉触发矩阵(CTM)等。

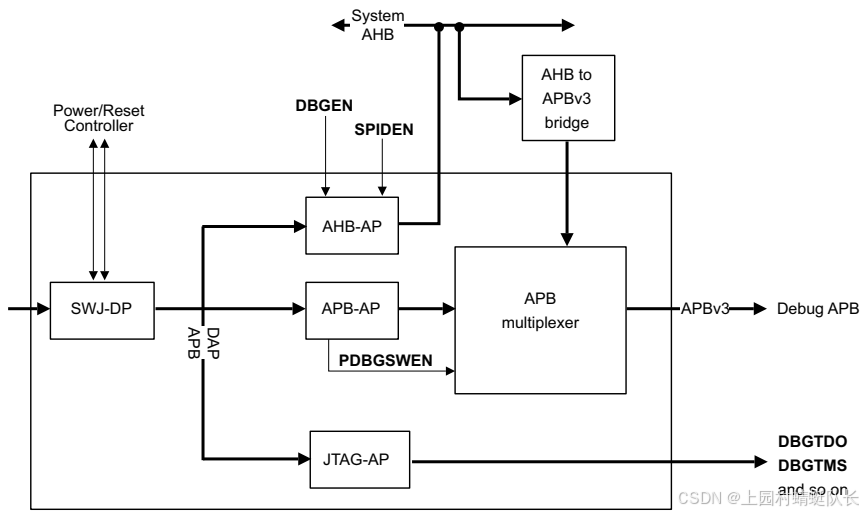

2. 调试访问端口(DAP)

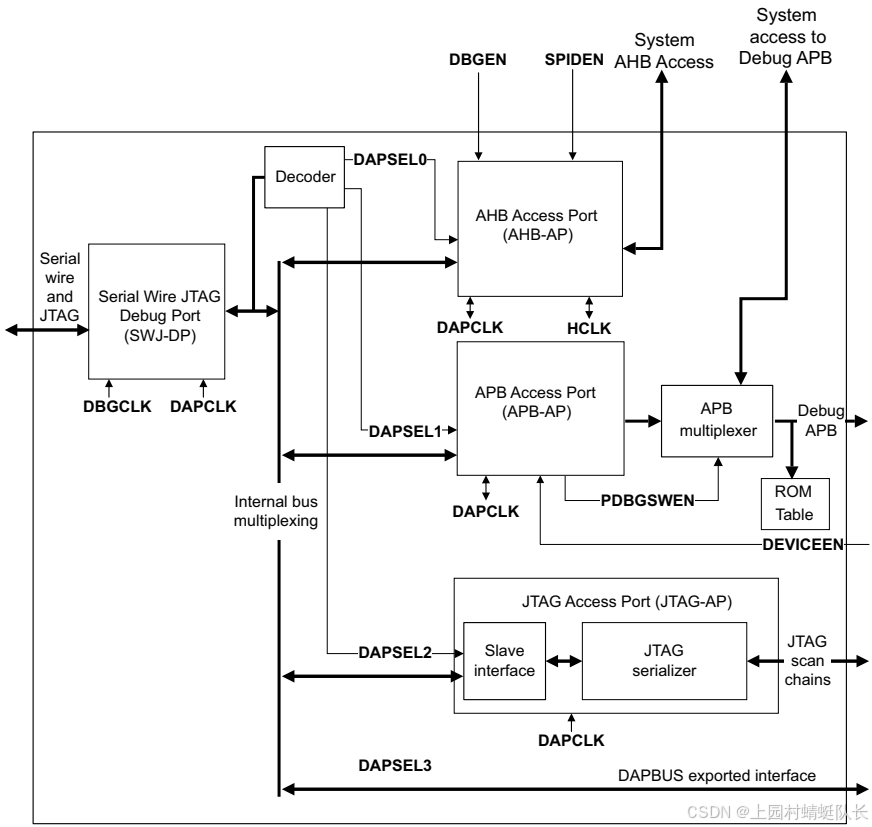

调试访问端口(Debug Access Port, DAP)是 ARM Debug Interface v5.1 (ADIv5.1) 的完整实现,由多个组件构成一个统一的调试解决方案。DAP 通过单一外部接口提供对多个主端口的访问和控制能力,使调试器能够实时访问系统内存、外设寄存器及所有调试配置寄存器,而无需暂停处理器运行。

2.1 DAP 核心组成

DAP 包含以下关键接口模块:

外部调试访问:通过串行线JTAG调试端口(SWJ-DP)实现,支持:

外部串行线访问(使用SW-DP)

外部JTAG访问(使用JTAG-DP)

休眠状态,禁用串行线接口以支持其他协议共享连接

系统访问:通过三种访问端口实现:

AHB-AP:提供AHB-Lite主接口

APB-AP:提供APB主接口(AMBA v3.0)

JTAG-AP:提供JTAG主接口

DAPBUS导出接口:支持连接额外的外部访问端口

APB多路复用器:使系统能够访问连接到调试APB的CoreSight组件

ROM表:提供连接到调试APB的CoreSight组件内存位置列表

2.2 DAP 控制流架构

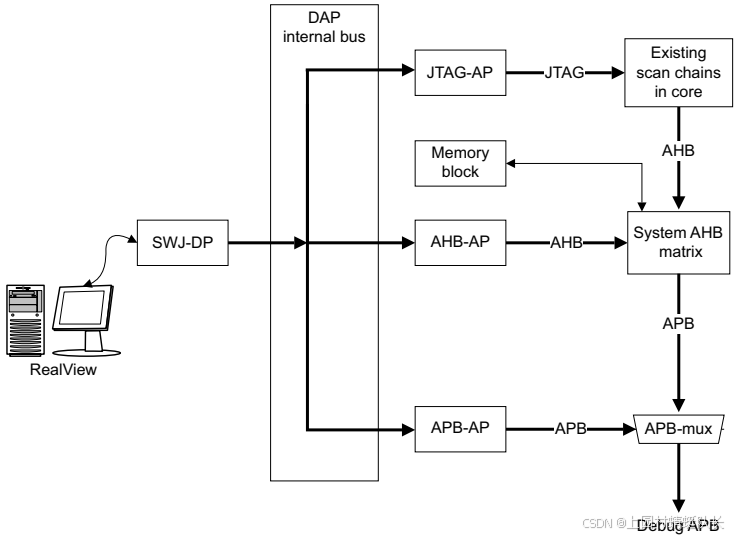

DAP 作为整体架构,承担着将一种接口类型的数据传输转换为不同内部事务的重要角色。调试端口接收JTAG或串行线传输,但通过标准总线接口控制JTAG-AP、AHB-AP和APB-AP。

外部硬件工具(如RealView)直接与DAP中的SWJ-DP通信,并执行一系列对调试端口的操作。其中一些访问会导致在DAP内部总线上执行操作。

2. 3 SWJ-DP 详细解析

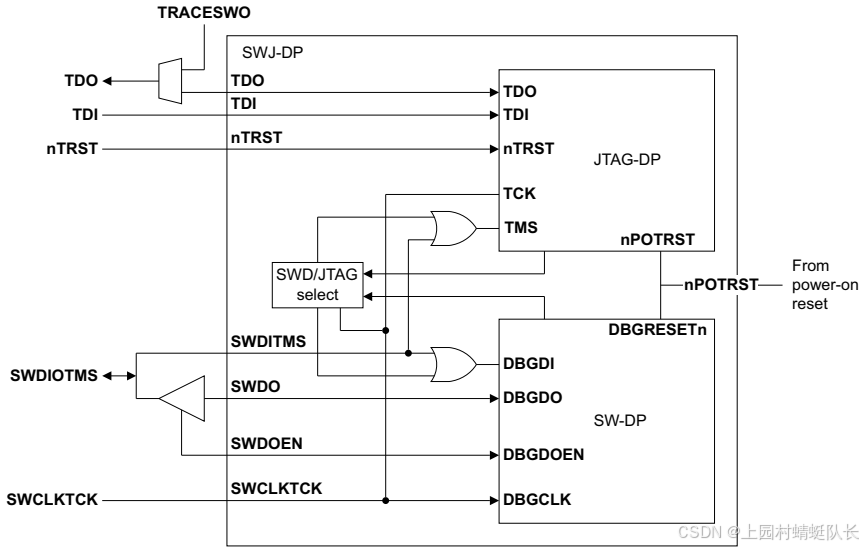

SWJ-DP是一个组合了JTAG-DP和SW-DP的调试端口,允许用户通过串行线调试(SWD)或JTAG探头连接到目标设备。

2.3.1 结构与操作原理

SWJ-DP由一个包装器组成,包裹着JTAG-DP和SW-DP。它选择JTAG或SWD作为连接机制,并使JTAG-DP或SW-DP作为DAP的接口。

SWJ-DP支持设计人员创建既需要JTAG接口又需要SWD接口的ASIC。在引脚使用数量和与现有硬件及测试设备的兼容性之间需要进行权衡。

2.3.2 接口共享机制

为了高效使用封装引脚,串行线共享或覆盖JTAG引脚,使用自动检测机制,根据连接的探头在JTAG-DP和SW-DP之间切换。在SWDIOTMS引脚上的特殊序列用于在JTAG-DP和SW-DP之间切换。

2.3.3 模式选择

SWJ-DP支持以下模式选择:

JTAG协议

串行线调试协议

休眠模式

当处于休眠模式时,TMS、TDI和TDO信号可用于其他目的,使其他设备能够使用相同的引脚实现替代调试协议。

2.3.4 状态指示

SWJ-DP包含一个模式状态输出JTAGNSW,当SWJ-DP处于JTAG模式时为高电平,在SWD或休眠模式时为低电平。该信号可用于:

当SWJ-DP处于SWD或休眠模式时禁用其他TAP控制器

当不在JTAG模式时,将串行线输出TRACESWO多路复用到另一个引脚(如TDO)

另一个状态输出JTAGTOP指示JTAG-DP TAP控制器的状态,包括Test-Logic-Reset、Run-Test/Idle、Select-DR-Scan和Select-IR-Scan状态。

2.3.5 电源域支持

为了帮助提供单独的电源域,可以对SWJ-DP的RTL进行分区,以支持始终开启域和调试域,如ADIv5.1中所定义。

2.4 JTAG-DP 技术细节

JTAG-DP是ADIv5.1中定义的JTAG-DP的实现,包含一个控制JTAG-DP操作的调试端口状态机(JTAG),包括提供到JTAG-DP的外部物理接口的扫描链接口。

2.4.1 操作概述

使用JTAG-DP时,IEEE 1149.1扫描链用于读取或写入寄存器信息。使用一对扫描链寄存器来访问调试端口内的主要控制和访问寄存器:

DPACC:用于调试端口(DP)访问

APACC:用于访问端口(AP)访问

2.4.2 物理接口实现

JTAG-DP的物理接口与ADIv5.1中信号引用的关系如表所示:

信号名称 | 方向 | 描述 |

|---|---|---|

TCK | 输入 | JTAG时钟 |

TMS | 输入 | JTAG模式选择 |

TDI | 输入 | JTAG数据输入 |

TDO | 输出 | JTAG数据输出 |

nTRST | 输入 | JTAG复位(可选) |

接口不包括返回时钟信号。RTCK和nTRST信号是可选的,因为这仅涉及重置DBGTAP状态机,可以通过传输5个TCK脉冲且TMS为高电平来执行。

2.4.3 寄存器实现

JTAG-DP实现的所有寄存器均可通过JTAG-DP访问。所有其他IR指令都实现为BYPASS,如果需要更多IR寄存器(例如JTAG TAP边界扫描),必须根据ADIv5.1实现外部TAP控制器。

2.5 SW-DP 深入分析

SW-DP提供低引脚数的双向串行连接到DAP,带有用于同步操作的参考时钟信号。

2.5.1 通信协议

与SW-DP的通信使用三相协议:

主机到目标的数据包请求

目标到主机的确认响应

数据传输阶段(如果需要)

来自调试器的数据包请求指示所需访问是针对DP寄存器(DPACC)还是AP寄存器(APACC),并包括一个两位的寄存器地址。

2.5.2 时钟特性

SW-DP时钟SWCLKTCK可以与DAPCLK异步。当调试端口空闲时,SWCLKTCK可以停止。

主机必须在任何数据传输的数据阶段之后继续时钟接口数个周期。这确保传输可以通过SW-DP进行时钟同步。

2.5.3 线路接口特性

SW-DP使用串行线传输主机和目标源信号。主机仿真器驱动协议时序——只有主机仿真器生成数据包头。

SW-DP在同步模式下运行,需要时钟引脚和数据引脚。同步模式使用时钟参考信号,可以从片上源导出,或由主机设备提供。

2.6 AHB-AP 详细说明

AHB-AP实现MEM-AP架构,直接连接到基于AHB的内存系统。通过适当的本地桥接可以连接到其他内存系统。

2.6.1 外部接口特性

连接到系统的主要外部接口是AHB-Lite主端口,支持:

AMBA v2.0 AHB

ARM11 AMBA扩展

TrustZone扩展

AHB-Lite主端口不支持:

BURST和SEQ

独占访问

未对齐传输

2.6.2 HPROT编码

HPROT[6:0]作为外部端口提供,并从CSW寄存器中的Prot字段编程,具有以下条件:

支持HPROT[4:0]编程

HPROT[5]不可编程且始终设置为低电平

支持HPROT[6]编程:高电平表示非安全传输,低电平表示安全传输

2.6.3 实现特性

AHB-AP提供以下特定的MEM-AP特性:

传输地址寄存器自动递增,地址在1KB边界上回绕

对AHB内存系统上设备的字、半字和字节访问

子字传输的打包传输

不支持以下MEM-AP特性:

大端序:所有访问预期为小端序内存结构

从机内存端口禁用:AHB-Lite主接口不与其他连接共享

APB-AP上的主要接口是APB AMBAv3兼容接口,支持:

扩展从机传输

传输响应错误

APB-AP提供以下特定的MEM-AP特性:

传输地址寄存器自动递增,地址在1KB边界上回绕

从机内存端口禁用:通过APB-MUX提供从机接口,使另一个APB主设备能够连接到与APB-AP相同的内存映射

不支持以下MEM-AP特性:

大端序:所有访问预期为小端序内存结构

子字传输:仅支持字传输

2.7. JTAG-AP 功能详解

JTAG访问端口(JTAG-AP)提供对片上组件的JTAG访问,作为JTAG主端口驱动整个SoC中的JTAG链。

2.7.1 外部接口

JTAG到从机设备的信号包括CSTCK、CSTMS、CSTDI、PORTCONNECTED等。八个JTAG扫描链在每个JTAG信号的相同位位置上。例如,扫描链0的连接可以位于每个总线连接的位[0]上。

2.7.2 RTCK连接处理

全局端口和RTCK:当设置多个PORTSEL[7:0]位时,所有活动的JTAG-AP多路复用器端口RTCK组合连接,使得:

如果TCK=0,则选择活动RTCK的OR

如果TCK=1,则选择活动RTCK的AND

活动RTCK由活动端口生成,活动端口定义为:

被选择(其PORTSEL[7:0]位被设置)

已连接(其PORTCONNECTED[7:0]位被设置)

在此会话中未被禁用或断电(其PSTA位为0)

如果没有端口活动,RTCK直接连接到TCK。

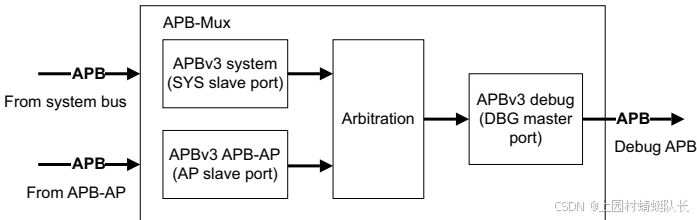

2.8. APB多路复用器(APB-MUX)

APB多路复用器用于DAP,使外部工具和系统能够访问CoreSight调试APB。APB-Mux将多个接口封装到单个可交付组件中,实现对调试APB的多主访问。

2.8.1 端口定义

APB-Mux具有以下端口:

APB-AP从机端口,信号后缀为AP

系统从机端口,信号后缀为SYS

调试APB主端口,信号后缀为DBG

2.8.2 仲裁机制

APB-Mux使用固定仲裁方案来支持两个从机接口。仲裁逻辑确保只有一个APB总线主设备(APB-AP或系统总线主设备)在任何时候都有权访问CoreSight调试APB。

APB-AP从机端口始终优先于系统从机端口。如果同时发起两个传输,来自APB-AP从机端口的传输总是传播到主端口输出以进行调试APB访问。

2.9. ROM表详细说明

DAP提供一个内部ROM表,连接到APB-Mux的主调试APB端口。调试ROM表加载到此总线的地址0x00000000和0x80000000,可从APB-AP和系统APB输入访问。

2.9.1 寄存器结构

ROM表具有标准的APB接口,但排除了PWRITEDBG和PWDATADBG。所有传输都假定为读取。ROM表是只读设备,写入被忽略。

ROM表具有特定的PrimeCell类。在所有寄存器0xFD0-0xFFC中,位[31:8]保留且应读为零。位置0xF00-0xFCC保留且应读为零。

2.9.2 ROM表条目

每个条目在0x000-0xEFC区域中的位分配如表所示:

位范围 | 描述 |

|---|---|

31:12 | 组件的基本地址 |

11:1 | 保留 |

0 | 格式类型:0=内存映射设备,1=ROM表 |

ROM表中的最后一个条目的值为0x00000000,这是保留的。如果CoreSight组件占用几个连续的4KB块,则给出内存中最低块的基本地址。

2.10. 认证要求详解

2.10.1 APB-AP认证

APB-AP有一个认证信号,称为DEVICEEN:

如果APB-AP连接到调试总线,此信号必须接高电平

如果APB-AP连接到专用于安全世界的系统总线,此信号必须连接到SPIDEN

如果APB-AP连接到专用于非安全世界的系统总线,此信号必须连接到DBGEN

2.10.2 认证信号处理

如果NIDEN为低电平且TINIDENSELx为低电平,则对CTI触发输入状态寄存器的任何读取都会返回相应的位为低电平。这适用于正常操作模式和集成测试模式。

如果DBGEN为低电平且TODBGENSELx为低电平,则对CTI触发输出状态寄存器的任何读取都会返回相应的位为低电平。CTTRIGOUTx寄存器也为低电平。

2.11. 时钟、电源和复位管理

DAP实现4个时钟和电源域:

调试端口接口域:由SWCLKTCK驱动,控制串行线和JTAG调试端口

调试域:覆盖DAP的内部总线通信、APB-AP和专用调试APB,基于PCLKDBG

AHB系统域:由HCLK时钟驱动,是AHB-AP上的AHB-Lite主接口

APB系统域:由PCLKSYS时钟驱动,是APB-MUX上的APB从机输入

2.11.1 时钟要求

PCLKDBG必须由恒定时钟驱动。当DAP正在使用时(由调试端口的调试电源请求确定),不得停止或更改它。PCLKENDBG可用作时钟门控项,以降低来自PCLKDBG的有效时钟速度。

2.11.2 复位管理

PRESETDBGn初始化PCLKDBG域中所有寄存器的状态。PRESETDBGn允许初始化DAP而不影响集成DAP的SoC的正常操作,并且应由工具在外部连接到调试端口时驱动。

可以通过写入调试端口的控制寄存器(调试复位请求寄存器)来启动复位。这将复位调试时钟域中的所有寄存器,即调试APB和DAP域。

3. 系统追踪宏单元(STM)

系统追踪宏单元(STM)用于生成系统级的追踪信息,主要通过内存映射的写操作将数据发送到 STM 的扩展刺激端口(STMESP)。STM 支持高带宽的追踪输出,适用于软件嵌入式的仪器化数据采集。

4. 追踪内存控制器(TMC)

追踪内存控制器(TMC)负责管理追踪数据的传输和存储。它支持将追踪数据从 STM 等源传输到外部存储器,提供数据缓冲、流量控制和数据格式化等功能。

5. 时间戳生成器(TSG)

时间戳生成器(TSG)用于生成系统级的时间戳信息,提供精确的时间标记。这些时间戳可用于对追踪数据进行时间对齐,支持系统级的事件分析和调试。

6. 交叉触发接口(CTI)与交叉触发矩阵(CTM)

交叉触发接口(CTI)和交叉触发矩阵(CTM)用于在多个处理器或模块之间传递调试事件。CTI 允许处理器或模块响应事件,而 CTM 则负责广播事件信号。这种机制支持同步暂停、事件触发等调试操作,适用于多核系统的调试需求。

7. 组件配置与集成

CoreSight SoC-400 提供了多种配置和集成方式。开发者可以使用 Build_Component 脚本或 AMBA Designer 工具对各个组件进行配置,生成符合需求的 RTL 代码。在集成过程中,需要注意时钟和复位的连接,确保系统的稳定性和可靠性。

8. 实践应用与案例分析

在实际的 SoC 设计中,CoreSight SoC-400 被广泛应用于多核处理器系统的调试和追踪。例如,在某多核处理器平台中,使用 DAP 提供调试接口,STM 采集系统级的追踪数据,TMC 管理数据的传输和存储,CTI 和 CTM 实现多核之间的事件同步。

9. 总结与展望

CoreSight SoC-400 提供了一套完整的调试和追踪解决方案,适用于各种规模的 SoC 设计。通过灵活的配置和集成,开发者可以根据具体需求定制调试和追踪功能,提高系统的可调试性和可靠性