DMA硬件架构解析:总线矩阵与核心组件

目录

1 关键硬件组件与总线架构(DMA 工作的硬件基础)

1.1 总线矩阵(Bus Matrix)的核心作用

1.2 核心硬件组件与 DMA 的协作逻辑

先看完我这篇博客效果会更好:

https://blog.csdn.net/2402_83411382/article/details/151654099?spm=1001.2014.3001.5501

1 关键硬件组件与总线架构(DMA 工作的硬件基础)

DMA 能够高效工作,依赖于嵌入式系统的 “总线矩阵(Bus Matrix)” 及各硬件组件的协同配合。理解这部分架构,是掌握 DMA 传输原理的关键。

1.1 总线矩阵(Bus Matrix)的核心作用

总线矩阵是连接所有 Bus-Master(CPU、DMA)和 Bus-Slave(外设、SRAM、Flash)的 “调度中心”,其核心功能是解决多 Master 对多 Slave 的访问冲突,实现高效并行传输:

-

实现多 Master 并行访问 若多个 Master 访问不同 Slave,总线矩阵可同时建立多条传输通路,互不干扰。例如:

-

CPU 通过 AHB 总线读取 Flash 中的指令(Master:CPU → Slave:Flash);

-

DMA1 通过 APB 总线读取 ADC1 数据,并写入 SRAM(Master:DMA1 → Slave:ADC1/SRAM); 两条传输通路并行执行,无需等待。

-

-

解决总线冲突与仲裁 当多个 Master 竞争访问同一 Slave(如 CPU 和 DMA 同时写 SRAM),总线矩阵会根据预设优先级进行仲裁,确保高优先级传输优先执行:

-

优先级规则:通常 DMA 通道优先级 > CPU 总线优先级(可软件配置),避免 DMA 传输被 CPU 频繁打断(尤其在高速传输场景)。

-

仲裁方式:采用 “固定优先级” 或 “轮转优先级”(部分架构支持),前者实现简单,后者确保各 Master 公平访问。

-

-

适配跨总线协议 嵌入式系统中存在不同速率的总线:

-

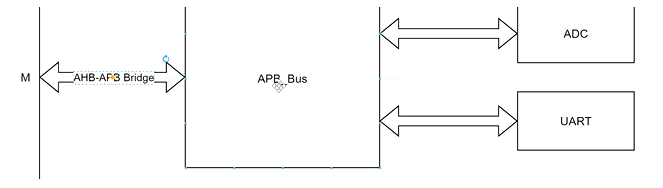

AHB 总线(Advanced High-performance Bus):高速总线,挂载 CPU、DMA、SRAM、Flash 等高速设备,传输速率高(如 72MHz);

-

APB 总线(Advanced Peripheral Bus):低速总线,挂载 ADC、UART、GPIO 等外设,传输速率低(如 36MHz); 总线矩阵可实现 AHB 与 APB 之间的协议转换,让 DMA 能跨总线传输数据(如从 APB 总线上的 ADC 读取数据,写入 AHB 总线上的 SRAM)。AHB 总线的访问速度很快,而外设的速度跟不上 AHB 的速度,通过 AHB-APB bridge 降低 AHB 的速度给 APB 进行通信。

-

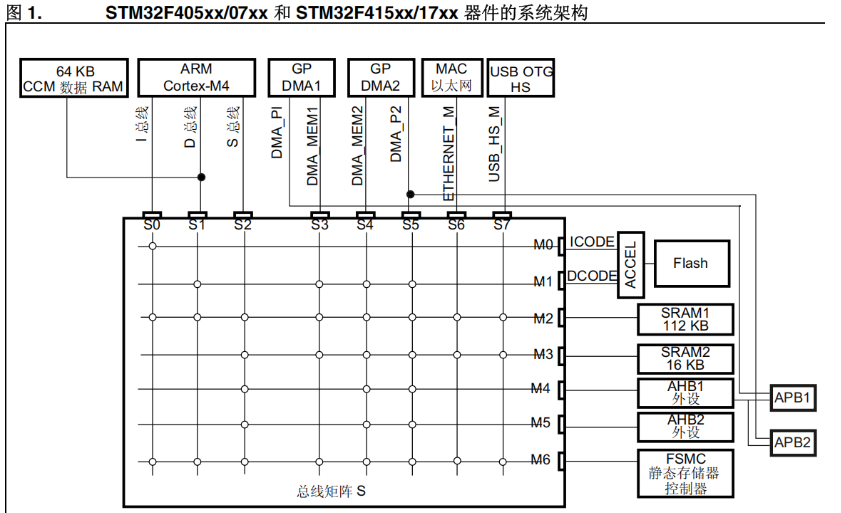

八条主控总线:

— Cortex™-M4F 内核 I 总线、D 总线和 S 总线

— DMA1 存储器总线

— DMA2 存储器总线

— DMA2 外设总线

— 以太网 DMA 总线

— USB OTG HS DMA 总线

七条被控总线:

— 内部 Flash ICode 总线

— 内部 Flash DCode 总线

— 主要内部 SRAM1 (112 KB)

— 辅助内部 SRAM2 (16 KB)

— 辅助内部 SRAM3 (64 KB)(仅适用于 STM32F42xxx 和 STM32F43xxx 器件)

— AHB1 外设(包括 AHB-APB 总线桥和 APB 外设)

— AHB2 外设

— FSMC

借助总线矩阵,可以实现主控总线到被控总线的访问,这样即使在多个高速外设同时运行期间,系统也可以实现并发访问和高效运行。

矩阵的小圆圈说明 S 和 M 接口连通,可以进行数据交互

S0:I 总线

此总线用于将 Cortex™-M4F 内核的指令总线连接到总线矩阵。内核通过此总线获取指令。 此总线访问的对象是包含代码的存储器(内部 Flash/SRAM 或通过 FSMC 的外部存储器)。

S1:D 总线

此总线用于将 Cortex™-M4F 数据总线和 64 KB CCM 数据 RAM 连接到总线矩阵。内核通过 此总线进行立即数加载和调试访问。此总线访问的对象是包含代码或数据的存储器(内部Flash 或通过 FSMC 的外部存储器)。

S2:S 总线

此总线用于将 Cortex™-M4F 内核的系统总线连接到总线矩阵。此总线用于访问位于外设 或 SRAM 中的数据。也可通过此总线获取指令(效率低于 ICode)。此总线访问的对象是 112 KB、64 KB 和 16 KB 的内部 SRAM、包括 APB 外设在内的 AHB1 外设、AHB2 外设以 及通过 FSMC 的外部存储器。

S3、S4:DMA 存储器总线

此总线用于将 DMA 存储器总线主接口连接到总线矩阵。DMA 通过此总线来执行存储器数据 的传入和传出。此总线访问的对象是数据存储器:内部 SRAM(112 KB、64 KB、16 KB) 以及通过 FSMC 的外部存储器。

S5:DMA 外设总线

此总线用于将 DMA 外设主总线接口连接到总线矩阵。DMA 通过此总线访问 AHB 外设或执行存储器间的数据传输。此总线访问的对象是 AHB 和 APB 外设以及数据存储器:内部SRAM 以及通过 FSMC 的外部存储器。

AHB/APB 总线桥 (APB)

借助两个 AHB/APB 总线桥 APB1 和 APB2,可在 AHB 总线与两个 APB 总线之间实现完全同步的连接,从而灵活选择外设频率。

1.2 核心硬件组件与 DMA 的协作逻辑

各硬件组件在 DMA 传输过程中各司其职,形成完整的 “配置→触发→传输→通知” 流程:

| 组件 | 设备类型(Master/Slave) | 在 DMA 传输中的角色与协作逻辑 |

| CPU | Master | 1. 初始化配置:通过写入 DMA 控制寄存器(CCR)、源地址寄存器(PAR)、目标地址寄存器(MAR)、传输计数器(CNDTR),设置 DMA 传输参数; 2. 使能 DMA 通道与外设请求:允许外设触发 DMA 传输; 3. 处理中断:接收 DMA 传输完成 / 出错中断,进行后续数据处理(如解析、存储)。 |

| DMA 控制器 | Master + Slave | 1. 作为 Master:监听外设请求,发起总线传输(读外设 DR → 写 SRAM),自动更新地址和传输计数器; 2. 作为 Slave:接收 CPU 的配置指令(如写入寄存器),反馈自身状态(如传输完成标志)。 |

| 外设(ADC/UART) | Slave | 1. 数据就绪后,通过硬件信号向 DMA 通道发送 “传输请求”(如 ADC 的 EOC 信号触发 DMA1_Channel1 请求); 2. 响应 DMA 读 / 写请求:向外设 DR 寄存器写入数据(内存→外设)或读取数据(外设→内存)。 |

| SRAM/Flash | Slave | 作为 DMA 传输的 “数据源” 或 “目标地址”: 1. 内存→外设:响应 DMA 读请求,输出 SRAM 中的数据; 2. 外设→内存:响应 DMA 写请求,存储外设传输的数据。 |

| NVIC(中断控制器) | Slave | 1. 接收 DMA 控制器的中断请求(如传输完成中断 TC、传输错误中断 TE); 2. 按优先级向 CPU 转发中断,触发 CPU 执行 DMA 中断服务程序(如 DMA1_Channel1_IRQHandler)。 |

| MPU(内存保护单元) | Slave | (可选)配置 SRAM 中 DMA 访问区域的权限(如只读 / 只写、数据长度限制),防止 DMA 误写 CPU 核心代码区或关键数据区,提升系统稳定性。 |