ARM内核知识概念

计算机体系结构核心知识总结

-

RISC、CISC的定义及ARM的归属

- CISC(复杂指令集计算机):指令集复杂,包含大量不同长度、功能多样的指令,支持多种寻址方式,可直接实现复杂操作(如x86架构)。其设计目标是通过丰富指令减少程序指令条数,但硬件实现复杂。

- RISC(精简指令集计算机):指令集精简,指令长度固定(通常32位),寻址方式简单,多数操作在寄存器间进行,通过多条简单指令组合实现复杂功能。硬件实现更简单,执行效率更高。

- ARM属于RISC:ARM架构采用精简指令集设计,指令长度统一(32位ARM指令或16/32位Thumb指令),注重高效的寄存器操作和流水线执行。

-

ARM内核的组成部分

ARM内核通常包含以下核心组件:- 运算器:包括算术逻辑单元(ALU)、乘法器等,负责执行算术和逻辑运算。

- 控制器:负责指令的取指、译码和执行控制,协调内核各部分工作。

- 寄存器组:包括通用寄存器、程序计数器(PC)、状态寄存器(如CPSR)等,用于数据暂存和状态标识。

- 流水线单元:将指令执行过程拆分为取指、译码、执行等阶段并行处理,提升效率(如ARM9的5级流水线)。

- 异常处理逻辑:负责检测和响应异常(如中断、复位等),切换工作模式并保存现场。

- 存储器接口:用于与外部存储器(如RAM、ROM)交互,获取指令和数据。

-

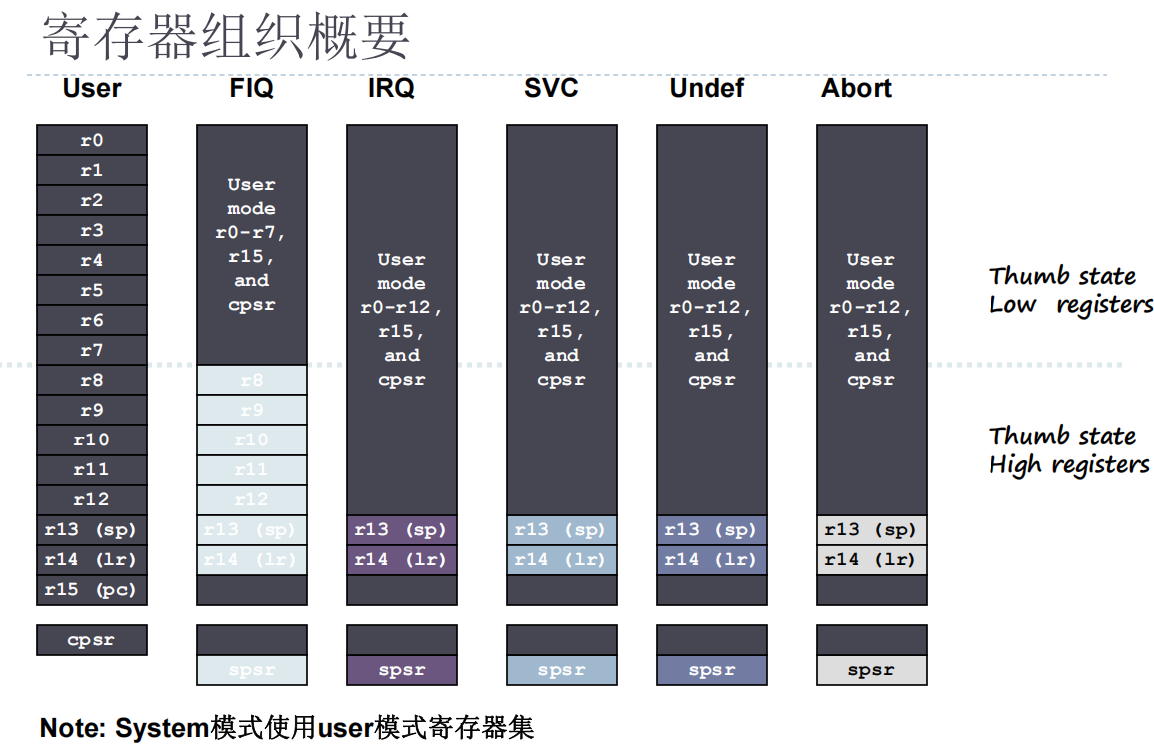

ARM9与Cortex-A的工作模式及作用

-

ARM9 支持7种工作模式:

- 用户模式(User):普通程序运行模式,权限最低,不能直接切换到其他模式。

- 快速中断模式(FIQ):用于高速数据传输或紧急处理,优先级最高,有独立寄存器组以加速响应。

- 外部中断模式(IRQ):用于处理通用外部中断,优先级低于FIQ。

- 管理模式(SVC):操作系统内核模式,用于系统初始化或执行特权操作(如系统调用)。

- 中止模式(Abort):用于处理存储器访问异常(如地址错误、权限不足)。

- 未定义模式(Undefined):用于处理未定义指令异常。

- 系统模式(System):运行具有特权的操作系统任务,使用用户模式的寄存器组,不受异常处理影响。

-

Cortex-A系列(基于ARMv7-A及以上架构)支持8种工作模式,在ARM9基础上增加:

8. 监控模式(Monitor):用于实现安全扩展(如TrustZone技术),在安全世界和非安全世界之间切换。

-

-

异常产生时ARM内核的工作

当异常发生时,ARM内核自动执行以下操作:- 保存现场:将当前程序状态寄存器(CPSR)的值复制到异常模式对应的备份状态寄存器(SPSR_)。

- 修改CPSR:切换工作模式(如IRQ异常进入IRQ模式),禁止相应中断(如FIQ异常时禁止FIQ),更新状态位(如Thumb状态标识)。

- 保存返回地址:将异常发生时的下一条指令地址存入异常模式的链接寄存器(LR_),以便后续返回。

- 跳转至异常向量表:强制程序计数器(PC)指向异常向量表中对应异常的入口地址,执行异常处理程序。

-

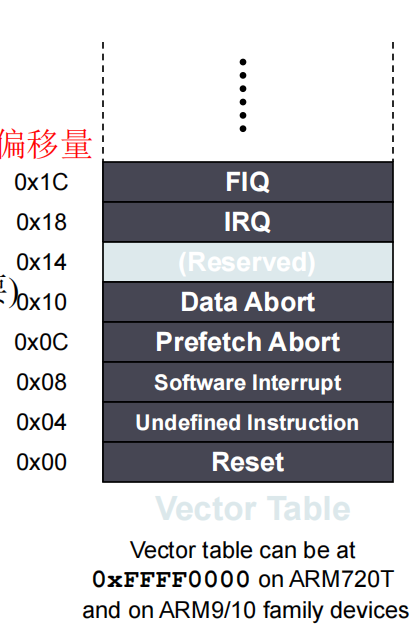

异常向量表

异常向量表是存储器中一段固定地址的区域,每个地址对应一种异常类型,存储该异常的处理程序入口地址(或跳转指令)。当异常发生时,ARM内核会根据异常类型自动跳转到向量表中对应的地址执行处理逻辑。- 例如,ARMv7架构中,异常向量表的基地址可通过配置寄存器设置(如低地址0x00000000或高地址0xFFFF0000),各异常对应的偏移地址固定(如复位向量在0x00,IRQ向量在0x18等)。

- 向量表的作用是统一管理异常入口,简化异常处理的跳转逻辑,确保异常能被快速响应。

一、状态寄存器

CPSR(Current Program Status Register)

ARM 处理器核心状态寄存器,存储程序运行关键状态:

- 处理器工作模式(用户/特权等)。

- 中断禁止位(控制中断使能)。

- 标志位(进位、零、符号、溢出等),决定条件分支、异常处理流程。

SPSR(Saved Program Status Register)

备份程序状态寄存器,对应不同异常模式(如 SPSR_fiq、SPSR_irq)。

- 异常(中断、数据中止等)发生时,自动保存 CPSR 内容。

- 异常处理完成后,将 SPSR 内容恢复到 CPSR,还原程序状态。

二、内存管理单元(MMU)

全称

Memory Management Unit。

作用

- 内存映射:虚拟地址转物理地址,构建虚拟 - 物理内存映射,支持程序使用超大虚拟地址空间,助力多程序并发与大型程序运行。

- 内存保护:设置内存区域访问权限(只读/只写/可执行等),防止非法访问(如用户程序访问内核内存),保障系统稳定安全。

- 内存优化:通过虚拟内存技术,实现分页/分段管理,动态分配回收内存,减少碎片,提升物理内存利用率。

与操作系统移植的关系

依赖虚拟内存的系统(如 Linux)移植时,需确认硬件带 MMU。无 MMU 需用特殊版本(如 uClinux)。

MMU 关闭时的缓存操作

关闭 MMU 时(裸机编程场景):

- 使能 I - Cache(加速指令读取)。

- 关闭 D - Cache(避免与直接内存操作冲突,确保数据访问准确)。

三、高速缓存(CACHE)

作用

解决 CPU 与内存速度差,缓存高频访问的指令/数据,提升数据访问速度与系统效率。

分类

- I - Cache(Instruction Cache):缓存待执行指令,CPU 取指令时优先查询,命中则快速获取,减少内存读指令时间。

- D - Cache(Data Cache):缓存待访问数据,CPU 读写数据时优先访问,提升数据存取速度。

与体系结构的关系

| 架构 | 存储与缓存特点 | 效率影响 |

|---|---|---|

| 冯·诺依曼架构 | 指令数据同存,缓存统一 | 指令/数据访问易冲突,效率受限 |

| 哈佛架构 | 指令数据分存,I/D - Cache 独立 | 可同时访问指令/数据,并行性与效率高 |

四、总线

AHB 总线(Advanced High - performance Bus)

AMBA 规范中的高性能总线,连接 CPU 内核、内存控制器、DMA 控制器等高速模块,高带宽、低延迟,支持高速数据传输。

APB 总线(Advanced Peripheral Bus)

AMBA 规范中的低速外设总线,连接 UART、GPIO、I2C 控制器等低速外设,设计简单、功耗低,满足低速通信需求。

Kernel 与外设连接

内核与外设通过 总线桥(Bus Bridge) 连接,实现不同总线(如 AHB 与 APB)的协议转换与信号中继,支持内核与外设数据交互。

单桥与双桥

- 单桥:单总线架构桥接,负责一种总线转换/连接。

- 双桥:双总线架构桥接,可同时处理两条总线通信,提供更高传输带宽。

五、RISC - V 架构

程序编译流程

预处理(宏展开、头文件处理)→ 编译(高级语言转汇编)→ 汇编(汇编转机器码)→ 链接(组合目标文件/库为可执行文件),最终生成 RISC - V 硬件可执行的机器码。

存储相关

- RAM(Random Access Memory):易失性存储器,断电数据丢失,是程序运行时数据存储与临时运算的核心区域,CPU 可快速读写。

- Flash:非易失性存储器,断电数据保留,用于存储程序代码、固件(类似 ROM,但支持电擦写,更灵活)。

六、ARM 架构

指令集类型

采用 精简指令集(RISC):

- 指令简单规整、长度固定,多数指令单时钟周期执行,执行效率高。

- 硬件设计简单,成本与功耗低,适合嵌入式领域。

Cortex - A7(32 位处理器,ARMv7 - A 架构)

- 指令:每条 4 字节,支持 ARM、Thumb - 2 指令集。

- 通用寄存器:13 个(R0 - R12),无固定地址,可灵活用于数据存储、运算、函数传参。

- 算术逻辑单元(ALU):执行算术(加/减/乘/除)与逻辑运算(与/或/非/异或),是数据处理核心。

- 所属 SOC:集成 CPU 内核、GPIO(与外部设备数字交互)、Timer(定时/计数)、RAM 控制器(管理 RAM 访问)等,单芯片实现复杂功能。

特殊寄存器

- PC(Program Counter,R15):程序计数器,指向待执行下一条指令地址,控制程序流程,指令执行后自动更新地址。

- LR(Link Register,R14):函数调用时(如 BL 指令),存储调用指令的下一条地址;嵌套调用时,可压栈保存,确保函数返回。

- SP(Stack Pointer,R13):栈指针,指向栈顶;多层函数调用时,用栈保存 LR、局部变量,实现函数调用/返回与局部数据存储。

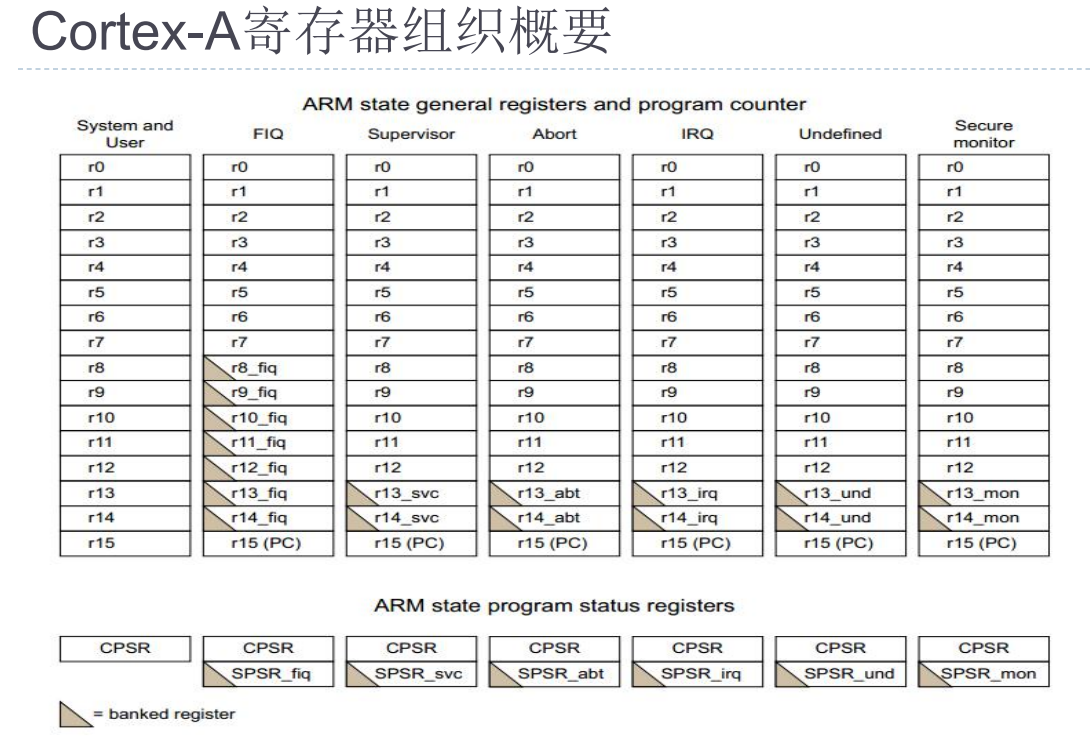

工作模式(9 种,不同模式权限/可访问寄存器不同)

| 模式 | 触发场景与权限 |

|---|---|

| User | 程序默认模式,非特权,限访问用户资源 |

| FIQ | 高优先级中断触发,专属寄存器组,快速处理高速事务 |

| IRQ | 低优先级中断触发,处理一般外设中断 |

| Supervisor | 复位/软中断后进入,高权限,运行操作系统内核 |

| Abort | 内存访问错误(地址非法/权限违规)时进入,处理异常 |

| Undef | 遇到未定义指令时进入,支持指令集扩展/软件仿真 |

| System | 特权模式,可访问 User 模式寄存器,方便系统与用户任务交互 |

| Cortex - A 特有 | 适配虚拟化、大地址空间等 Cortex - A 特性 |

| Monitor | 支持 TrustZone 时,管理安全/非安全世界切换 |

寄存器数量与异常处理

- 32 位 ARM 架构:37 个寄存器(含通用、状态寄存器)。

- 异常处理流程:保存当前状态(CPSR 存 SPSR、调整 PC 等)→ 通过异常向量表进入处理流程 → 恢复状态,程序继续执行。

- Cortex 架构:40 个 32 位寄存器,支持更复杂操作,提升执行效率。

移位操作

| 操作 | 功能与应用 | 补充说明 |

|---|---|---|

| LSL(逻辑左移) | 数据左移 n 位,低位补 0,等价于乘 (2^n),加速乘法 | 若左移后数据超出寄存器位数(如32位寄存器左移32位及以上),结果通常为0(不同架构可能有细微差异);可用于快速构建特定位模式,如将1左移n位得到只有第n位为1的数,用于位掩码等操作。 |

| 逻辑右移 | 数据右移 n 位,高位补 0,等价于无符号数除 (2^n),加速除法 | 只适用于无符号数的除法运算,对有符号数进行逻辑右移会改变其符号(若原数为负,高位补0后会变成正数),导致结果错误。 |

| 算术右移 | 数据右移 n 位,高位补符号位(正补 0,负补 1),支持有符号数除法 | 是为有符号数除法设计的,能保证移位后数的符号不变,正确实现有符号数除以 (2^n) 的运算;与逻辑右移的核心区别在于高位补位的依据(符号位 vs 固定补0)。 |

| ASR(算术右移,明确指令名) | 同上述算术右移功能 | 在ARM等架构中,算术右移有专门的指令(如ASR),编程时可直接使用该指令对有符号数进行移位操作。 |

| ROR(循环右移) | 将数据的各位循环右移n位,最右边的n位移动到最左边 | 可用于位循环操作,比如在加密算法、校验和计算等场景中,需要对数据位进行循环移位时使用;例如,一个8位的数10101100循环右移2位后变为00101011。 |

| ROL(循环左移) | 将数据的各位循环左移n位,最左边的n位移动到最右边 | 类似循环右移,方向为左,应用场景与ROR类似,用于需要循环左移位的操作;如8位数10101100循环左移2位后变为10110010。 |

一、数据和指令类型

架构与数据宽度约定

ARM 采用 32 位架构,对数据类型有明确约定:

- Byte:8 位。

- Halfword:16 位(2 字节)。

- Word:32 位(4 字节)。

- Doubleword:64 位(8 字节,Cortex - A 处理器支持)。

指令集

大部分 ARM 核心提供:

- ARM 指令集:32 位,功能完整,性能强。

- Thumb 指令集:16 位,代码密度高,适合对代码大小敏感的场景。

Cortex - A 处理器额外支持:

- Thumb - 2 指令集:16 位和 32 位混合,兼具代码密度与性能。

- ThumbEE 指令集:16 位和 32 位,为嵌入式实时应用和动态代码生成优化。

此外,Jazelle cores 支持 Java bytecode,可直接执行 Java 字节码,提升 Java 程序在 ARM 平台的执行效率。

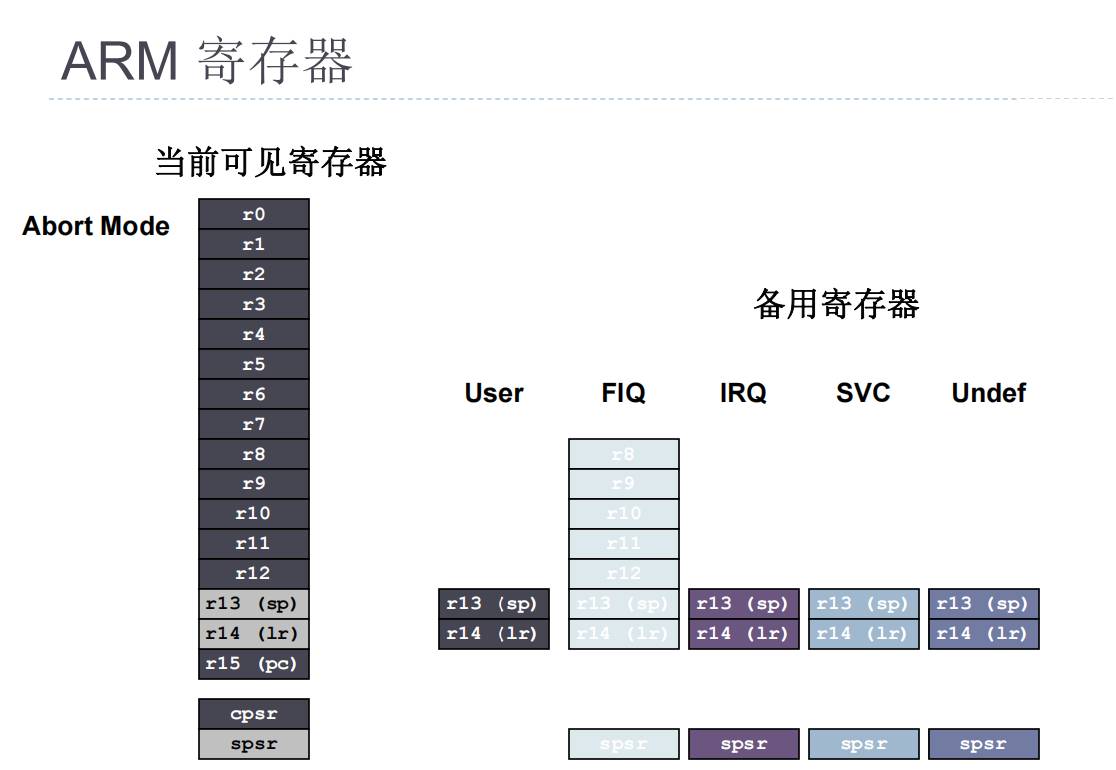

二、ARM 寄存器

基本寄存器(传统 ARM 架构)

ARM 有 37 个 32 位长的寄存器,分类如下:

- 1 个用作 PC(Program Counter,程序计数器),指向当前执行指令的下一条指令地址。

- 1 个用作 CPSR(Current Program Status Register,当前程序状态寄存器),存储当前程序运行的状态信息(如处理器模式、标志位等)。

- 5 个用作 SPSR(Saved Program Status Registers,备份程序状态寄存器),在异常发生时保存 CPSR 的内容。

- 30 个 通用寄存器,用于数据的临时存储、运算等。

Cortex 体系结构寄存器

Cortex 体系结构下有 40 个 32 位长的寄存器。以 Cortex - A 为例,多出 3 个寄存器(Monitor 模式下的 r13_mon、r14_mon、spsr_mon),用于支持 Monitor 模式相关操作。

寄存器访问权限

- 任何模式都可存取:

- 相应的

r0 - r12子集。 - 相应的

r13(栈指针sp)、r14(链接寄存器lr)。 - 相应的

r15(程序计数器pc)。 - 相应的

CPSR。

- 相应的

- 特权模式(除 System 模式) 还可存取相应的

SPSR。

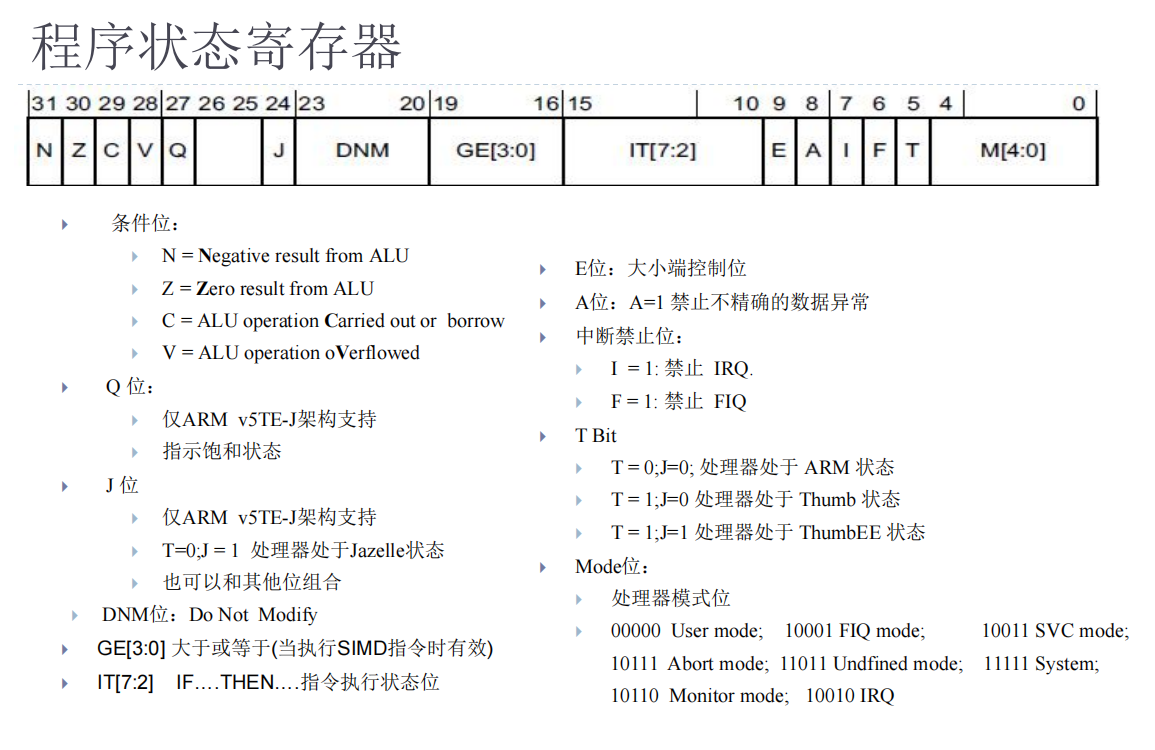

三、程序状态寄存器(PSR)

PSR 是 32 位寄存器,各 bit 段有不同功能,以下是关键位说明:

条件位(N、Z、C、V)

- N(Negative):ALU 运算结果为负时置 1。

- Z(Zero):ALU 运算结果为 0 时置 1。

- C(Carry/Borrow):ALU 运算产生进位(加法)或借位(减法)时置 1。

- V(Overflow):ALU 运算发生溢出时置 1。

其他关键位

- Q 位:仅 ARM v5TE - J 架构支持,指示饱和状态。

- J 位:仅 ARM v5TE - J 架构支持,

T = 0, J = 1时处理器处于 Jazelle 状态,可与其他位组合。 - DNM 位(Do Not Modify):禁止修改。

- GE[3:0]:执行 SIMD 指令时有效,用于表示“大于或等于”等比较结果。

- IT[7:2]:IF - THEN 指令执行状态位。

- E 位:大小端控制位。

- A 位:

A = 1禁止不精确的数据异常。 - 中断禁止位(I、F):

I = 1:禁止 IRQ(普通中断)。F = 1:禁止 FIQ(快速中断)。

- T Bit:指示处理器状态:

T = 0, J = 0:ARM 状态。T = 1, J = 0:Thumb 状态。T = 1, J = 1:ThumbEE 状态。

- Mode 位(M[4:0]):处理器模式位,不同值对应不同模式,如:

00000:User 模式。10001:FIQ 模式。10011:SVC 模式等。

四、程序指针 PC(r15)

PC 是特殊的寄存器,其行为因处理器状态不同而变化:

ARM 状态

- 所有指令 32 位宽,且必须按 word 对齐。

- PC 值由 bits [31:2] 决定,bits [1:0] 未定义,因此指令不能按 halfword 或 byte 对齐。

Thumb 状态

- 所有指令 16 位宽,且必须按 halfword 对齐。

- PC 值由 bits [31:1] 决定,bits [0] 未定义,因此指令不能按 byte 对齐。

Jazelle 状态

- 所有指令 8 位宽。

- 处理器执行 word 存取时,一次可取 4 条指令。

五、异常处理

异常产生时的操作(ARM core)

- 拷贝

CPSR到SPSR_<mode>(对应异常模式的备份程序状态寄存器)。 - 设置适当的

CPSR位:- 改变处理器状态进入 ARM 态。

- 改变处理器模式进入相应的异常模式。

- 设置中断禁止位禁止相应中断(若需要)。

- 保存返回地址到

LR_<mode>(对应异常模式的链接寄存器)。 - 设置

PC为相应的异常向量(异常向量表中对应异常的地址)。

异常返回时的操作

- 从

SPSR_<mode>恢复CPSR。 - 从

LR_<mode>恢复PC。 - 注意:这些操作只能在 ARM 态执行。

异常向量表

异常向量表存储各异常处理程序的入口地址,不同异常对应不同偏移量,例如:

0x00:Reset(复位)。0x04:Undefined Instruction(未定义指令)。0x08:Software Interrupt(软件中断)等。在 ARM720T 和 ARM9/10 系列设备上,向量表可位于0xFFFF0000处。