ARM处理器基础

一、ARM

- 基础信息

- 成立时间:1990年11月,前身为Acorn计算机公司。

- 核心业务:设计ARM系列RISC处理器内核,不生产芯片,仅授权内核给半导体厂商(如三星、高通、NXP)。

- 附加服务:提供ARM架构相关的开发技术(软件工具、评估板、调试工具、总线架构、外设单元等)。

- CISC RISC

架构 全称 核心设计理念 CISC Complex Instruction Set Computer 追求 “单条指令完成复杂任务”,通过丰富的复杂指令减少程序指令总数,降低编程复杂度 RISC Reduced Instruction Set Computer 追求 “指令精简、执行高效”,仅保留最常用的简单指令,通过 “多指令组合” 完成复杂任务,提升硬件执行速度

二、ARM处理器系列分类与定位

ARM处理器按应用场景分为四大系列,核心差异在于性能、功耗和实时性,典型产品及应用如下表:

| 系列 | 定位 | 典型内核 | 核心特性 | 典型应用 |

|---|---|---|---|---|

| Cortex-A | 高性能应用型 | Cortex-A5/A7/A8/A9/A15 | 支持复杂OS(安卓、Linux),多核,高算力 | 智能手机、平板、数字电视、服务器 |

| Cortex-R | 实时控制型 | Cortex-R4/R5/R7 | 低延迟、高可靠性,强实时响应 | 硬盘控制器、汽车电子、无线基带 |

| Cortex-M | 低功耗微控制器(MCU) | Cortex-M0/M3/M4/M7 | 低成本、低功耗,简化指令集 | 家电、传感器、工业控制、便携设备 |

| 经典系列 | 早期嵌入式 | ARM7TDMI、ARM9TDMI、ARM11 | 奠定RISC基础,部分支持Java加速 | 早期手机、MP3、嵌入式网关 |

1.

三、ARM编程模型

1. 数据类型与指令集模式

- 数据类型(ARM默认32位架构):

- Byte(8位)、Halfword(16位)、Word(32位)、Doubleword(64位,仅Cortex-A支持)。

- 指令集模式:

- ARM模式:32位指令,需字对齐(地址末2位为0),性能优先。

- Thumb模式:16位指令,需半字对齐(地址末1位为0),节省内存。

- Thumb-2模式(Cortex-A/M支持):兼容16/32位指令,平衡性能与内存。

- Jazelle模式:直接执行8位Java字节码,提升Java程序效率。

2. 工作模式

ARM处理器通过模式区分权限与功能,不同模式对应独立的寄存器组(影子寄存器),核心模式如下:

| 系列 | 工作模式 | 核心作用 |

|---|---|---|

| ARM9(7种) | 用户模式(User) | 普通应用运行,权限最低,无法访问系统资源 |

| 快速中断模式(FIQ) | 处理高优先级事件(如定时器、高速ADC),含7个专属影子寄存器,延迟最低 | |

| 外部中断模式(IRQ) | 处理普通外设中断(如UART、GPIO按键),最常用中断模式 | |

| 管理模式(SVC) | 操作系统内核运行(如系统调用、复位后初始模式),权限最高 | |

| 数据中止模式(ABT) | 内存访问出错触发(地址越界、权限不足),用于内存保护 | |

| 未定义指令模式(UND) | 执行非法指令触发,可模拟扩展指令或报错 | |

| 系统模式(Sys) | 特权级“类用户模式”,用User寄存器组,运行高权限用户程序(如内核线程) | |

| Cortex-A(新增1种) | 监控模式(Mon) | 配合TrustZone安全技术,隔离“安全世界”(指纹、支付)与“非安全世界”(普通APP) |

3. Cortex-A7内核核心模块

ARM寄存器为32位,数量随模式扩展,核心分类如下:

- ARM9(共37个):

- 通用寄存器:31个(16个基础寄存器 + FIQ 7个影子寄存器 + IRQ/SVC/ABT/UND各2个影子寄存器)。

- 状态寄存器:6个(1个CPSR + 5个SPSR,对应FIQ/IRQ/SVC/ABT/UND,User/Sys无SPSR)。

- Cortex-A(共40个):

- 比ARM9多2个Monitor模式影子寄存器(R13_mon/R14_mon)+ 1个SPSR_mon,总通用寄存器33个、状态寄存器7个。

- 关键寄存器功能:

通用寄存器(R0~R12)共13个,编号范围为R0~R12

核心功能:作为临时数据存储单元,用于存放运算中间结果、函数参数等,是ALU运算的“数据来源与结果暂存地”算术逻辑单元(ALU)

- 模块类型:内核计算核心

- 核心功能:执行两类基础操作

- 算术运算:加减乘除等数值计算(如寄存器间加法、减法)

- 逻辑运算:与、或、非、异或等位操作(如寄存器值按位清零、比较)

- PC(R15):程序计数器,指向下一条要执行的指令地址(ARM模式字对齐,Thumb模式半字对齐)。

- LR(R14):链接寄存器,保存子程序返回地址,异常时存返回地址。

- SP(R13):栈指针,指向当前模式的栈顶,每个模式需独立初始化。

- CPSR:当前程序状态寄存器,存条件码(N/Z/C/V)、中断禁止位(I/F)、模式位、指令集模式位(T)。

- SPSR:备份程序状态寄存器,仅特权模式有,异常时备份CPSR,恢复时用。

4. 字节顺序

- 小端(Little-endian):低字节存低地址(如0x11223344存为44 33 22 11),主流嵌入式系统默认。

- 大端(Big-endian):高字节存低地址(如0x11223344存为11 22 33 44),部分通信设备使用。

5.内存管理与缓存模块

1.内存管理单元(MMU)

全称:Memory Management Unit

- 当前状态:关闭

- 核心作用(关闭前):实现虚拟地址到物理地址的映射、内存权限控制(如禁止用户模式访问内核内存)、内存保护(防止非法地址访问)

四、S33C2440芯片核心存储与总线模块

S3C2440(三星ARM920T内核嵌入式SoC)

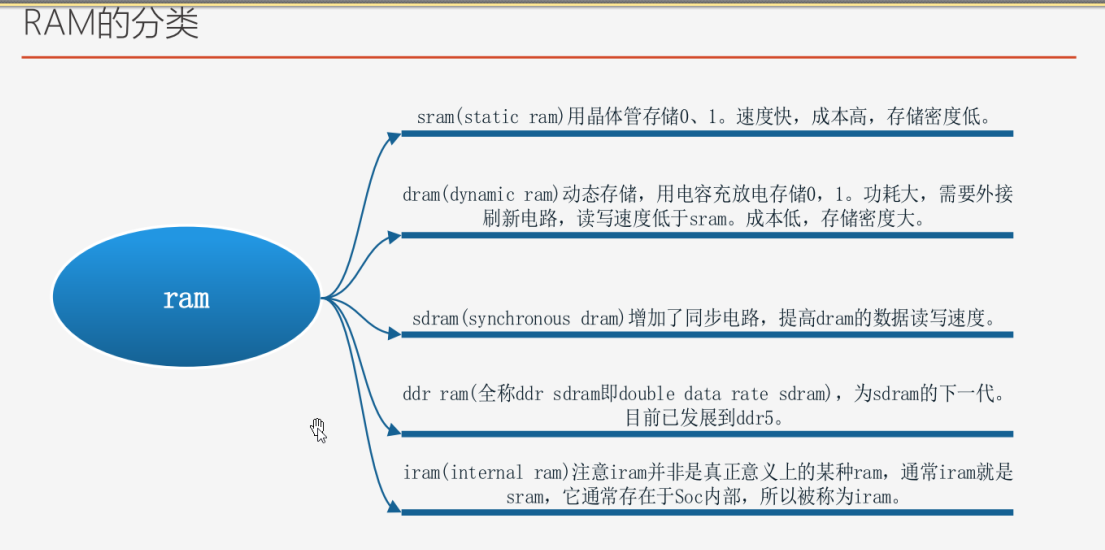

1. RAM(随机存取存储器)

- 核心类型:S3C2440主流搭配 SDRAM(同步动态随机存取存储器)

(注:非静态RAM,需周期性刷新维持数据,区别于CPU内部Cache的SRAM) - 关键参数:

- 总线宽度:32位(支持16位/32位配置,匹配SoC数据总线);

- 容量范围:常见64MB~256MB(如MT48LC16M16A2,16M×16bit×4bank=128MB);

- 时钟同步:与S3C2440的HCLK(AHB总线时钟,最高133MHz)同步,提升数据读写效率。

- 分类

- 核心功能:

- 运行时存储:存放当前执行的程序代码(如操作系统内核、应用程序)和临时数据(如变量、栈数据);

- 掉电特性:数据易失(掉电后立即丢失),需依赖ROM(如Flash)存储长期数据。

2. ROM(只读存储器,含NOR Flash/NAND Flash)

(1)NOR Flash(或非型闪存)

- 结构:“或非(NOR) 结构”,通过单个晶体管存储1位数据。

- 核心特性:

- 寻址方式:每个字节可独立寻址(类似RAM),CPU可直接从NOR Flash读取指令并执行(支持“XIP:Execute In Place”);

- 容量与速度:容量较小(常见1MB~32MB),读速快(类似SDRAM),但写/擦除速度慢(擦除按“扇区”,通常512B~16KB/扇区);

- 擦除寿命:约10万~100万次,适合存储“少量、需频繁读取”的关键数据。

- S3C2440适配场景:

作为启动设备(Boot Device),存放Bootloader(如U-Boot)——因S3C2440上电后默认从NOR Flash地址(0x00000000)读取启动代码,无需额外控制器即可启动。

(2)NAND Flash(与非型闪存)

- 结构特性:采用“与非(NAND) 结构”,多晶体管串联存储数据,单位面积容量更高。

- 核心特性:

- 寻址方式:块级寻址(无法直接访问单个字节,需先读取“块”数据到缓存),不支持XIP,需先将程序加载到RAM才能执行;

- 容量与速度:容量大(常见64MB~1GB),写/擦除速度快(擦除按“块”,通常128KB~2MB/块),成本低于NOR Flash;

- 额外需求:需S3C2440内置的NAND Flash控制器(支持ECC校验,修复数据位错误)才能正常读写。

- S3C2440适配场景:

作为大容量存储设备,存放操作系统镜像(如Linux内核、根文件系统)、用户数据——因容量大、成本低,弥补NOR Flash容量不足的问题。

五、外部扩展存储(eMMC与SD卡)

1. eMMC(嵌入式多媒体卡)

- 本质:将“NAND Flash芯片 + 闪存控制器 + 标准接口”集成的一体化存储模块,简化硬件设计。

- 核心特性:

- 接口标准化:采用MMC协议,通过8位数据总线与S3C2440连接,无需额外设计NAND控制器(模块内置);

- 容量与可靠性:容量可达数GB(如4GB/8GB),支持坏块管理、ECC校验,稳定性优于独立NAND Flash;

- 嵌入式场景:直接焊接在PCB上,不可插拔,适合对稳定性要求高的设备(如工业控制板)。

- S3C2440适配:通过SoC的“MMC/SD控制器”连接,需配置控制器时钟(HCLK分频)和数据总线宽度,可替代NAND Flash作为系统存储。

2. SD卡(安全数字卡)

- 本质:可插拔的外部扩展存储,基于MMC协议,分为SD(最大2GB)、SDHC(最大32GB)、SDXC(最大2TB)规格。

- 核心特性:

- 可插拔性:支持热插拔,方便数据传输(如更换SD卡导出用户数据);

- 接口简化:4线接口(CLK/CMD/DAT0/DAT1),与eMMC共用S3C2440的MMC/SD控制器;

- 应用场景:用于存储“非核心、可移动”的数据(如日志文件、采集的传感器数据)。

- S3C2440适配:需通过GPIO模拟或专用控制器驱动,注意热插拔时的时序控制,避免数据损坏。

六、总线模块(APB与AHB)

S3C2440采用ARM标准的AMBA总线架构,核心分为AHB(高速总线) 和APB(低速总线),通过“APB桥”实现两者互联:

1. AHB(Advanced High-performance Bus,高速总线)

- 定位:连接S3C2440内部“高速设备”,承担高带宽数据传输。

- 挂载设备:

- CPU内核(ARM920T)、SDRAM控制器、NAND Flash控制器、eMMC/SD控制器、LCD控制器(高带宽外设);

- 总线时钟:HCLK(最高133MHz),与CPU核心时钟(FCLK,最高400MHz)分频同步。

- 核心特性:

- 支持突发传输(一次地址发送,连续传输多字节数据),提升SDRAM/NAND的读写效率;

- 多主设备支持(如CPU、DMA控制器可同时作为主设备发起总线请求)。

2. APB(Advanced Peripheral Bus,低速总线)

- 定位:连接S3C2440内部“低速外设”,降低低速设备的功耗与硬件复杂度。

- 挂载设备:

- GPIO(通用输入输出)、UART(串口)、I2C(两线总线)、SPI(四线总线)、RTC(实时时钟)、看门狗;

- 总线时钟:PCLK(最高66MHz),由HCLK分频得到(如HCLK/2)。

- 核心特性:

- 仅支持“单周期传输”,无突发传输(匹配低速外设的响应速度);

- 仅CPU作为主设备,外设均为从设备,简化总线仲裁逻辑。

- 基于Load/Store架构:仅Load(读内存)/Store(写内存)指令访问内存,数据处理仅操作寄存器,提升速度。

- 支持条件执行:所有指令可加条件码(如EQ、NE),满足条件才执行,减少分支跳转。

- 单周期指令为主:多数指令(如ADD、MOV)1个时钟周期完成,部分复杂指令(如乘法)多周期。

2. 指令

| 指令类别 | 核心功能 | 典型指令示例 |

|---|---|---|

| 数据处理指令 | 算术/逻辑运算、数据传送 | ADD R0,R1,R2(R0=R1+R2)、MOV R0,#1(R0=1)、AND R0,R1,R2(按位与) |

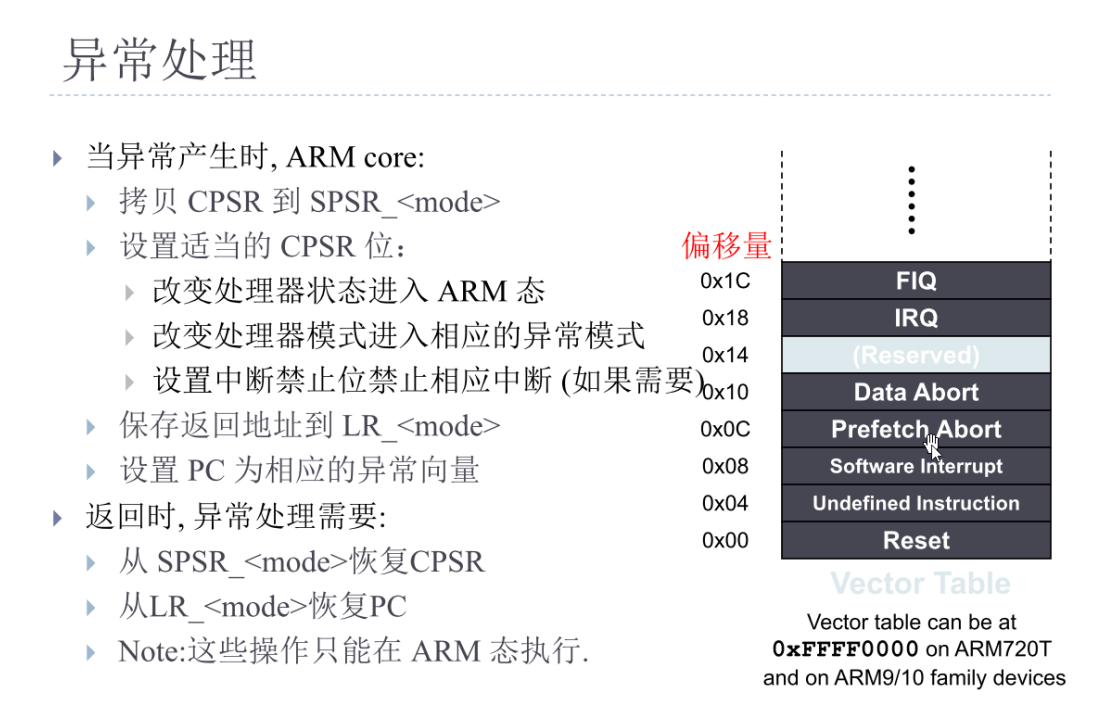

七、异常处理

1. 异常类型与优先级

| 异常类型 | 触发场景 | 优先级(从高到低) | 异常向量地址(默认) |

|---|---|---|---|

| 复位(Reset) | 处理器上电/复位 | 1 | 0x00000000 |

| 数据中止(Data Abort) | 内存访问出错(如越界) | 2 | 0x00000010 |

| 快速中断(FIQ) | 高优先级外设请求 | 3 | 0x0000001C |

| 外部中断(IRQ) | 普通外设请求 | 4 | 0x00000018 |

| 预取中止(Prefetch Abort) | 指令预取出错 | 5 | 0x0000000C |

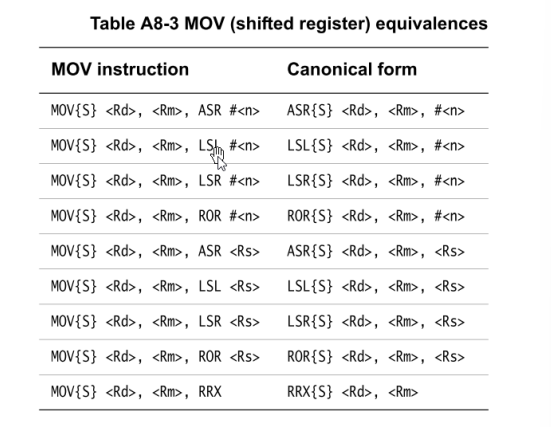

八、汇编指令

1.指令

| 指令类别 | 核心功能 | 典型指令示例 |

|---|---|---|

| 数据处理指令 | 算术/逻辑运算、数据传送 | ADD R0,R1,R2(R0=R1+R2)、MOV R0,#1(R0=1)、AND R0,R1,R2(按位与) |

| 右移类型 | 英文全称 | 处理数据类型 | 补位规则(右移后左侧空位) | 核心目的 |

|---|---|---|---|---|

| 算术右移(A) | Arithmetic Shift Right (ASR) | 有符号数(如 int) | 补 “符号位”(最高位): - 正数(符号位 0)补 0 - 负数(符号位 1)补 1 | 保持数值的 “正负性”,实现 “除以 2 的整数次幂”(如右移 1 位 = 除以 2,向下取整) |

| 逻辑右移(L) | Logical Shift Right (LSR) | 无符号数(如 unsigned int) | 固定补 “0” | 仅做 “位的右移”,不考虑正负,常用于地址计算、位提取 |