S32K3平台eMIOS 应用说明

- S32K3 系列 eMIOS 介绍

1.1 资源介绍

该设备具有 3 个 eMIOS 模块,每个模块的配置如表 1.1 所示。

1.2 功能介绍

eMIOS 提供了用于生成或测量时间事件的功能。它使用 UCs,您可以为不同的芯片应

用中的不同功能进行编程。此外,eMIOS 体系结构允许使用执行特定功能的专用通道。

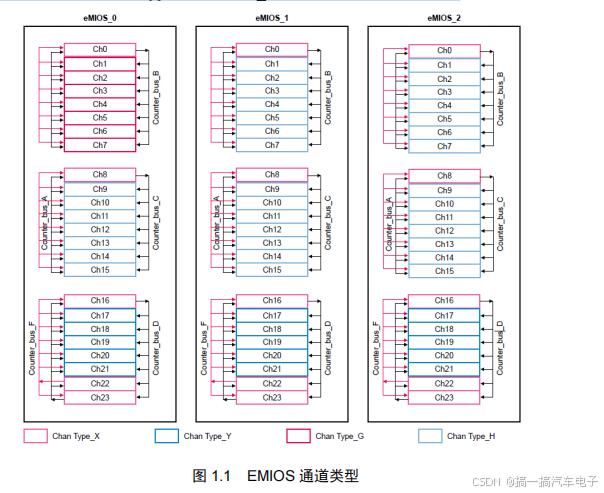

1.2.1 通道配置

下面图 1.1 显示了有关 Type 和 Counter_bus 的 eMIOS 通道配置。

1.2.2 框图

1.2.3 功能

在统一或专用通道中最多选择 24 个通道,不必按连续顺序编号

8 位,16 位,24 位或 32 位宽度的数据寄存器

计数器总线 B,C,D 可以分别由 UC 0、8 和 16 驱动计数器总线 A 可以由 UC 23 驱动。

计数器总线 F 可以由系统配置定义的 UC 驱动。

每个通道都有自己的时基,与计数器总线不同

两个全局预分频器

每个通道一个 CP

通过计数器总线共享时基

每个 UC 都有自己的一组控制和状态寄存器

时基之间的同步

影子标志寄存器(全局标志(GFLAG))

可以冻结 UC 状态以进行调试

电机控制能力

您可以将 UC 配置为在以下模式下运行:

通用输入/输出(GPIO)模式

单边沿输入捕捉(SAIC)模式

单动作输出比较(SAOC)模式

输入脉冲宽度测量(IPWM)模式

输入周期测量(IPM)模式

双动作输出比较(DAOC)模式

脉冲/边沿计数(PEC)模式

模数计数器(MC)模式

模数计数器缓冲(MCB)模式

输出脉冲宽度和频率调制缓冲(OPWFMB)模式

具有死区插入缓冲的中心对齐输出脉冲宽度调制(OPWMCB)模式

输出脉冲宽度调制缓冲(OPWMB)模式

带触发的输出脉冲宽度调制(OPWMT)模式

每个通道可以具有一组特定的模式。

1.2.4 功能描述

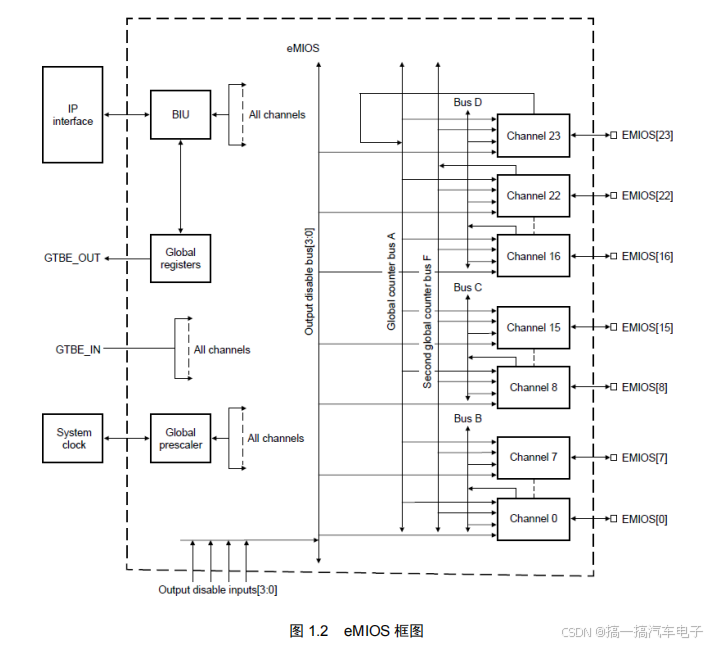

eMIOS 提供了独立的统一通道,可由主机 MCU 配置和访问。通道们最多可以共享五个

时基,但每个通道只能有一个时基。

eMIOS 模块基于多总线计时器体系结构,其中多个计时器通道用于驱动在通道之间共

享的计数器总线,也就是说有些用作计数器的通道可以用于作为驱动计数器的通道。通过五

个计数器总线,通道们最多可以共享五个时基,每个通道可以生成自己的时基。有两条全局

计数器总线:时基 A 和时基 F,可以被所有通道共享,可以在时基 A 或 F 中进行选择作为

全局计数器总线;还有三条本地计数器总线(B,C,D),每条专用于 8 个通道。计数器总

线 A 和 F 称为全局计数器总线。计数器总线 B,C,D 是本地计数器总线。

eMIOS 计数器总线是由特定位置的通道驱动的。全局计数器总线 A 由通道插槽[23]中

的通道驱动,计数器总线 F 由通道插槽 22 中的通道驱动。计数器总线 B,C,D 分别由插

槽 0、8 和 16 中的通道驱动。计数器总线 A 或 F 驱动所有通道。计数器总线 B 驱动从 0 到

7 的插槽中的通道。计数器总线 C 驱动从 8 到 15 的插槽中的通道。计数器总线 D 驱动从 16

到 23 的插槽中的通道。

eMIOS 模块异步复位。复位时,所有寄存器均被清除。

1.2.5 模数计数器(MC)模式

MC 模式可用于为计数器总线或通用计时器提供时基。

MODE [0]位分别在清零或置位时选择内部或外部时钟源。选择外部时钟时,将输入信

号引脚用作时钟源,并通过 EMIOSC [n]寄存器中的 EDPOL 和 EDSEL 选择触发极性边沿。

内部计数器从当前值开始递增计数,直到与寄存器 A1 中的值匹配为止。寄存器 B1 被

清除,MCU 无法访问。MODE [2]位分别在清除或设置时选择向上模式或向上/向下模式。

在递增计数模式下,内部计数器和寄存器 A1 之间的匹配将设置 FLAG 并清除内部计数

器。

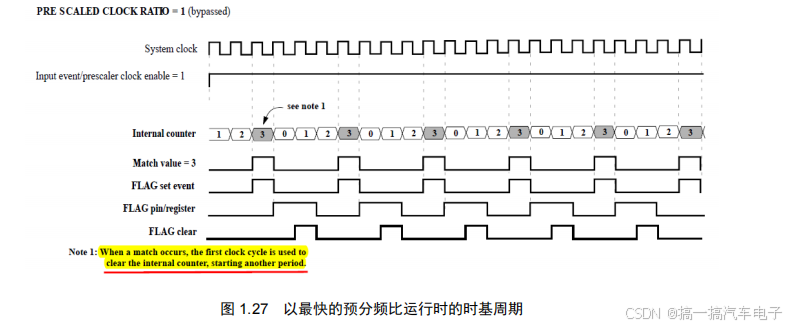

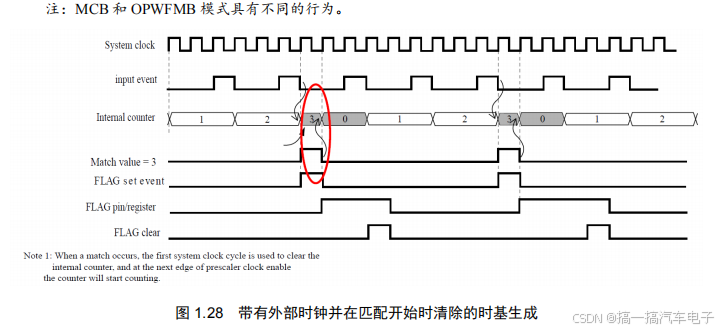

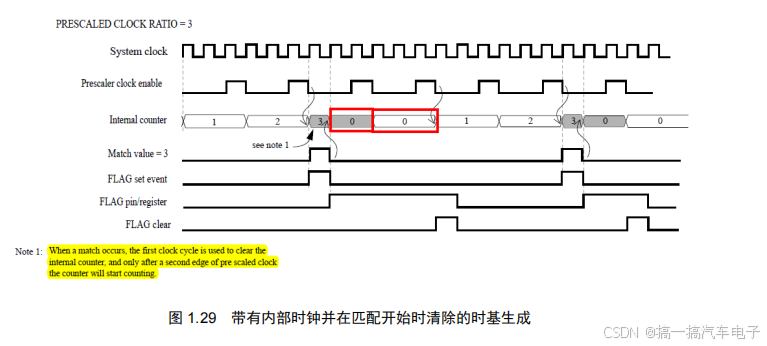

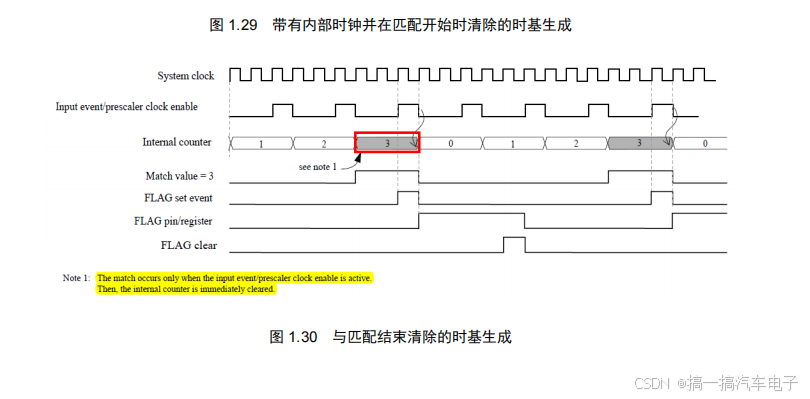

这些事件的时间根据 MC 模式设置而有所不同,如下所示:

匹配开始时内部计数器清除(MODE[6:0] = 001000b)

—如果设置了 MODE[6],则选择外部时钟。在这种情况下,一旦出现匹配信号,内部

计数器就会清除。匹配发生的同时设置通道 FLAG。请注意,通过在发生匹配时立即清除内

部计数器,并在下一个输入事件时将其递增,便会生成较短的零计数。参见图 1.27 和图 1.28。

—如果清除了 MODE[6],则选择内部时钟源。在这种情况下,一旦出现匹配信号,计

数器就会清除。匹配发生的同时设置通道 FLAG。匹配结束后的下一个预分频器滴答时,内

部计数器保持为零,仅在下一个滴答时恢复计数。参见图 1.27 和图 1.29。

匹配结束时的内部计数器清除(MODE[6:0] = 001001b)

—如果设置了 MODE[6],则选择外部时钟。在这种情况下,当匹配信号有效并且发生

输入事件时,内部计数器将清零。清除计数器的同时设置通道 FLAG。参见图 1.27 和图 1.30。

—如果清除了 MODE[6],则选择内部时钟源。在这种情况下,当匹配信号有效并且发

生预分频器滴答时,内部计数器将清零。清除计数器的同时设置通道 FLAG。参见图 1.27

和图 1.30。

注:如果选择了内部时钟源,并且内部计数器的预分频器设置为 1,MC 模式的行为相同,即使在“匹

配开始时清除”或“匹配结束时清除”子模式下也是如此。

当处于递增/递减计数模式(MODE[6:0] = 00101bb)时,内部计数器与寄存器 A1 之

间的匹配将设置 FLAG,并将计数器方向从递增更改为递减。寄存器 B1 与内部计数器之间

的匹配将计数器的方向从递减更改为递增,并且仅在 MODE[1]位置 1 时设置 FLAG。

只能将非 0x0 的值写入 A 寄存器。加载 0x0 会导致不可预测的结果。

如果传输在匹配附近发生,则在 MC 模式下对寄存器 A 或计数器的更新可能会导致当

前周期的匹配丢失。

在这种情况下,计数器可能会翻转并在下一个周期恢复操作。

寄存器 B2 在 MC 模式下无效。不过,可以通过寻址 EMIOSB 来访问寄存器 B2 以进行

读取和写入。

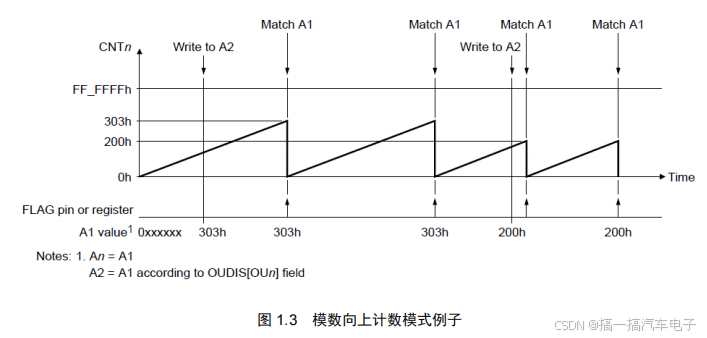

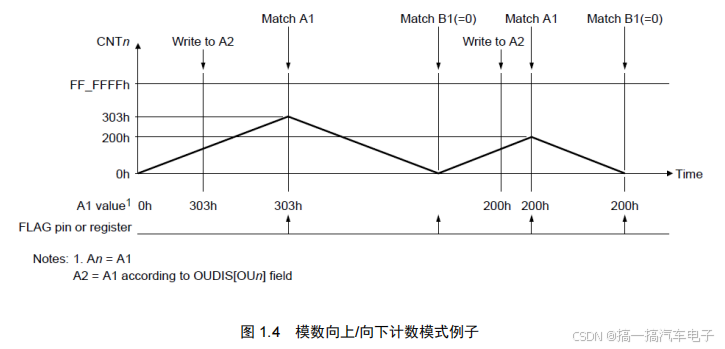

图 1.3 和图 1.4 显示了如何分别在向上模式和向上/向下模式下将统一通道作为模数计数

器。

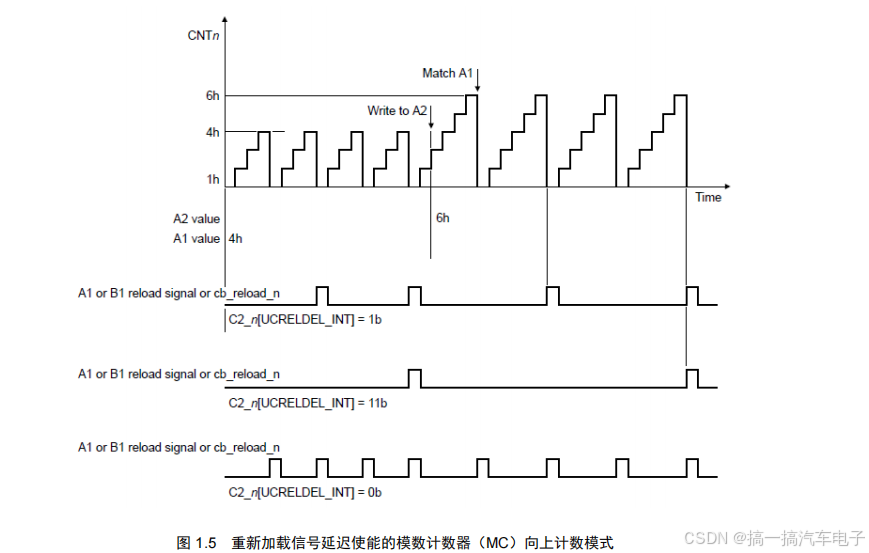

每当计数器值与向上模式下的 A1 寄存器或向上/向下模式下的 B1 寄存器匹配时,MC

模式下的统一通道都会生成一个“计数器总线重载信号”。该重载信号可以由在 OPWMB,

OPWFMB,OPWMCB 模式下运行的相关 UC 使用。也可以延迟“计数器总线重载信号”,

以便在第 n 个时机(n = 2、3、4,… 32)生成重载信号。重新加载信号延迟使能的模数计数

器(MC)向上计数模式如图 1.5 所示

1.2.6 模数计数器缓冲(MCB)模式

MCB 模式提供了一个时基,可以通过内部计数器总线与其他通道共享该时基。寄存器

A1 是双缓冲的,因此在动态更改 A2 寄存器值时允许在周期之间平滑过渡。寄存器 A1 在周

期边界更新,周期边界定义为内部计数器转换为 0x1 时的边界。

内部计数器的值在 0x1 到寄存器 A1 值的范围内运行。如果从 GPIO 模式进入 MCB 模

式时,内部计数器值不在 A1 值范围内,则不会发生 A 匹配,这从而导致通道内部计数器换

为 16 位计数器的最大计数器值,即 0xffff。计数器变换发生后,它将返回 0x1 并恢复正常的

MCB 模式操作。因此,为避免计数器变换条件,请确保进入 MCB 模式时计数器值在 0x1

以内以寄存器 A1 的值范围。

MODE[0]位选择内部时钟源(如果清零)或外部时钟源(如果置位)。选择外部时钟时,

输入通道引脚用作通道时钟源。该时钟的有效沿由 EMIOSC[n]通道寄存器中的 EDPOL 和

EDSEL 位定义。

进入 MCB 模式时,如果通过 MODE [2] = 0(MODE[6:0] = 101000b)选择了递增计数

器,则内部计数器将从其当前值开始向上计数,直到发生 A1 匹配为止。当内部计数器的值

与 A1 值匹配并且发生时钟滴答(预分频时钟或输入引脚事件)时,内部计数器将设置为 0x1。

如果通过设置 MODE[2] = 1 选择了递增/递减计数器,则计数器会在 A1 匹配处改变方

向并递减计数,直到达到值 0x1。达到 0x1 后,将其设置为再次向上计数。如果选择了向上

/向下模式,则寄存器 B1 用于产生匹配,以便将内部计数器设置为向上计数方向。选择此模

式时,不能更改寄存器 B1。

请注意,与 MC 模式不同,MCB 模式在 0x1 和 A1 寄存器值之间计数。只能将大于 0x1

的值写入寄存器 A1。加载那些值之外的值会导致不可预测的结果。在递增计数器模式下,

计数器周期等于 A1 值。如果处于递增/递减计数器模式,则周期由以下表达式定义:(2 * A1)

-2。

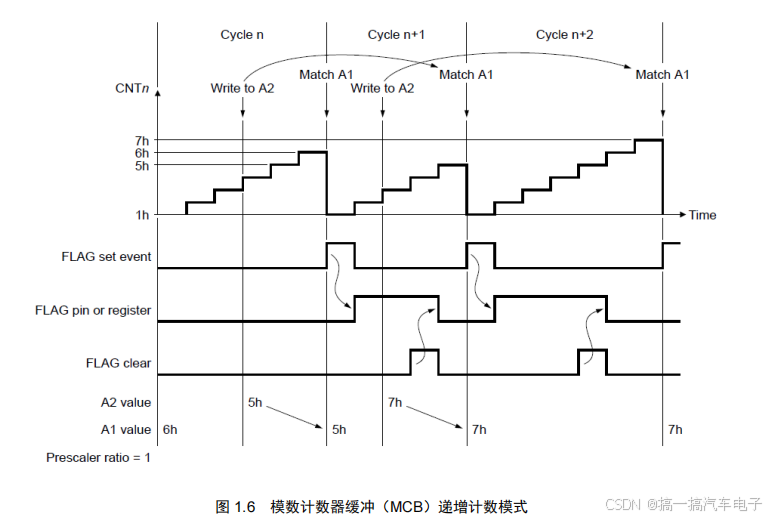

图 1.6 描述了几个 A1 值的计数周期。寄存器 A1 在循环边界处加载有 A2 寄存器值。因

此,在周期 n 内写入 A2 寄存器的任何值都将在下一个周期边界更新为 A1,因此将在周期 n

- 1 上使用。定义周期 n 和周期 n + 1 之间的周期边界为内部计数器从周期 n 中的 A1 值过渡

到周期 n + 1 中的 0x1 的时间。请注意,FLAG 在周期边界生成并具有同步操作,这意味着

在 FLAG 设置事件后的一个系统时钟周期将其置为有效。

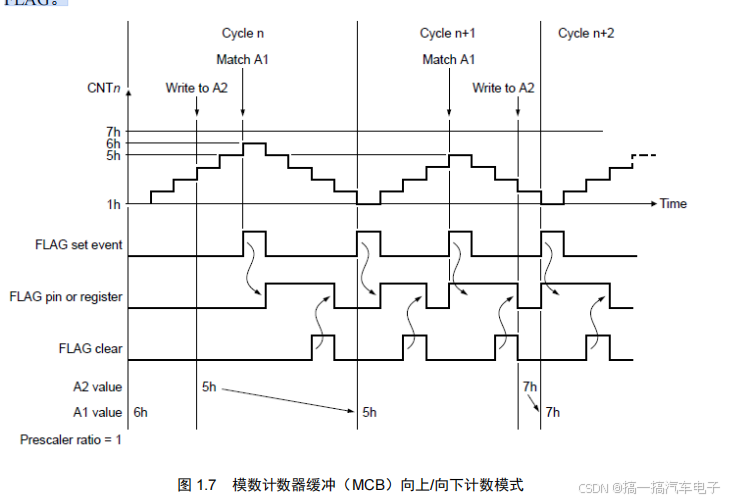

图1.7描述了向上/下计数器模式的 MCB(模式[6:0] = 10101BB)。寄存器 A1 在循环

边界处更新。如果 A2 写入循环 N,则此新值将用于 A1 匹配的循环 N + 1。如果 MODE [1]

为 0,仅在 A1 匹配启动时生成 FLAG。如果 MODE [1]设置为 1,则在循环边界处也产生

FLAG。

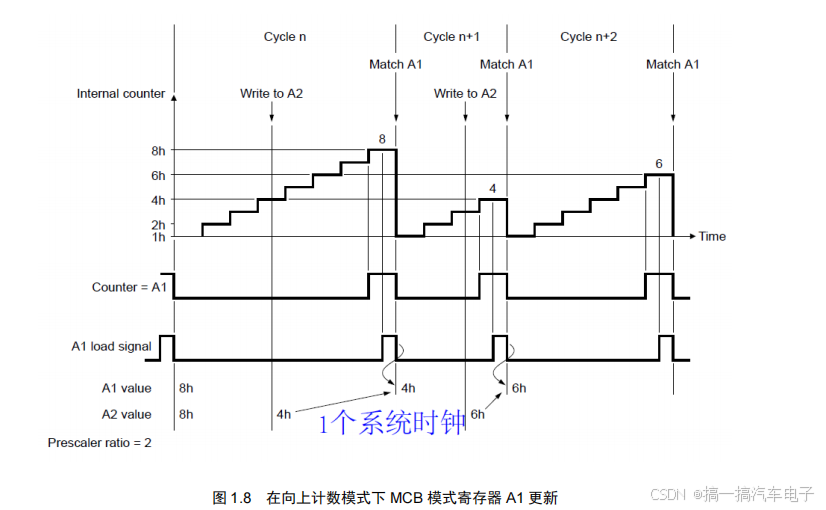

1.8图 更详细地描述了向上计数器模式下的寄存器 A1 更新过程。A1 加载信号在计数器

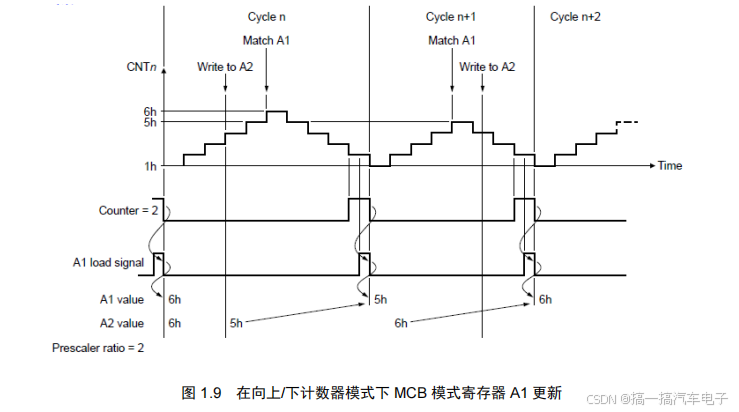

1.9描述了递增/递减计数器模式下的寄存器 A1 更新。注意,可以在周期 n 内的任何

时间写入 A2,以便在周期 n + 1 中使用。因此,A1 在下一个循环边界处接收到该新值。注

意,EMIOSOUDIS 寄存器的更新禁止位 OU [n]可用于禁止寄存器 A1 的更新。

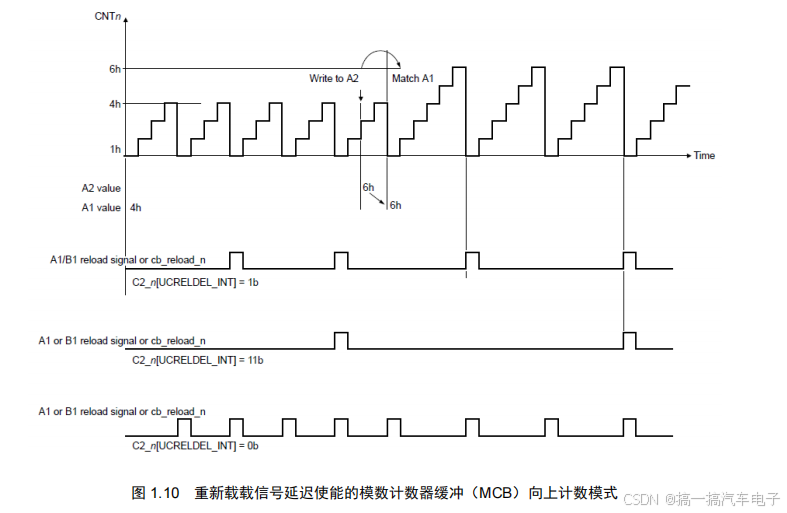

每当计数器值与向上计数模式下的 A1 寄存器或向上/向下计数模式下的 0x1 匹配时,

MCB 模式下的统一通道都会生成一个“计数器总线重载信号”。该重载信号可以由在

OPWMB,OPWFMB,OPWMCB 模式下运行的相关 UC 使用。也可以延迟“计数器总线重

载信号”,以便在第 n 次机会生成重载信号(n = 2、3、4,…32)。图 1.10 是重新载载信号延

迟使能的模数计数器缓冲(MCB)向上计数模式的时序图。

注:处于冻结状态时,不应将 EMIOSCNT 寄存器的值写入 0x1。原因:在 MCB 上下模式下,如果计

数器递减至 1;否则,计数器递减。将计数器覆盖为 1 可能会错过 B 匹配,并且计数器可能会溢出

1.2.7 输出脉冲宽度和频率调制缓冲(OPWFMB)模式

此模式(MODE[6:0] = 10110b0)提供占空比和频率可变的波形。选择此模式时,将

自动选择内部通道计数器作为时基。寄存器 A1 指示占空比,而 B1 记录频率。寄存器 A1

和 B1 都经过双缓冲,以在更改寄存器值时允许平滑的信号生成。支持 0%和 100%占空比。

在进入 OPWFMB 模式时,输出触发器被设置为 EMIOSC [n]寄存器中 EDPOL 位的值。

为了提供平稳一致的通道操作,此模式与 OPWFM 模式大不相同。主要区别在于 A1 和

B1 寄存器的更新,从 A1 匹配到输出引脚转换的延迟以及内部计数器值的范围(从 0x1 开

始直到寄存器 B1 值)。

当进入从 GPIO 模式退出的 OPWFMB 模式时,内部计数器值不在 B1 值范围内,则不

会发生 B 匹配,从而导致通道内部计数器换为 16 位计数器的最大计数器值,即 0xffff。计

数器变换发生后,它将返回 0x1 并恢复正常的 OPWFMB 模式操作。因此,为避免计数器变

换条件,请确保进入 OPWFMB 模式时计数器值在 0x1 至 B1 寄存器值范围内。

当比较器 A 发生匹配时,输出寄存器将设置为 EDPOL 的值。当比较器 B 发生匹配时,

输出寄存器将设置为 EDPOL 的补码。B1 匹配还会使内部计数器转换为 0x1,从而重新启动

计数器周期。

只允许将大于 0x1 的值写入寄存器 B1。加载那些值之外的值会导致不可预测的结果。

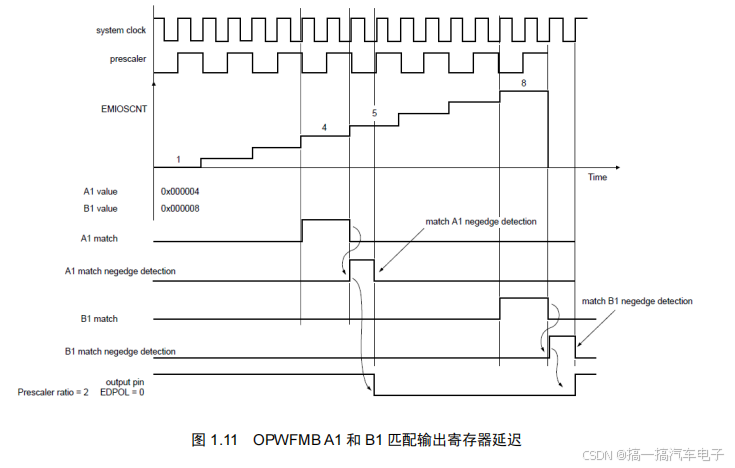

图 1.11 描述了 OPWFMB 模式的操作,涉及输出引脚转换和 A1 / B1 寄存器匹配事件。

请注意,当 A1 或 B1 匹配信号置为无效时,将发生输出引脚转换,这由 A1 匹配忽略

检测信号指示。如果寄存器 A1 设置为 0x4,则在周期开始后加上一个系统时钟周期后,输

出引脚将转换 4 个计数器周期。请注意,在图 1.11 所示的示例中,内部计数器预分频器的

比率为 2。

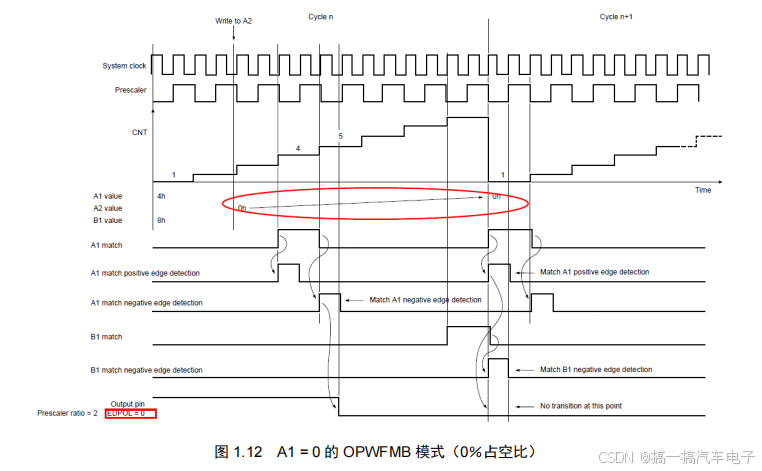

图 1.12 描述了如果 A1 设置为 0x0 时产生的输出信号。由于在此模式下计数器未达到零,

因此通道内部逻辑就像 A1 = 0x1 一样推断匹配,所不同的是,当 A1 = 0x1 时,在这种情况

下,使用匹配信号的摆幅来触发输出引脚转换,而不是使用忽略值。注意,来自周期 n +1

的 A1 匹配信号与来自周期 n 的 B1 匹配信号同时出现。当它们同时发生时,这允许使用 A1

匹配来掩盖 B1 忽略匹配。结果是在输出触发器上不会发生跳变,并且会产生 0%的占空比。

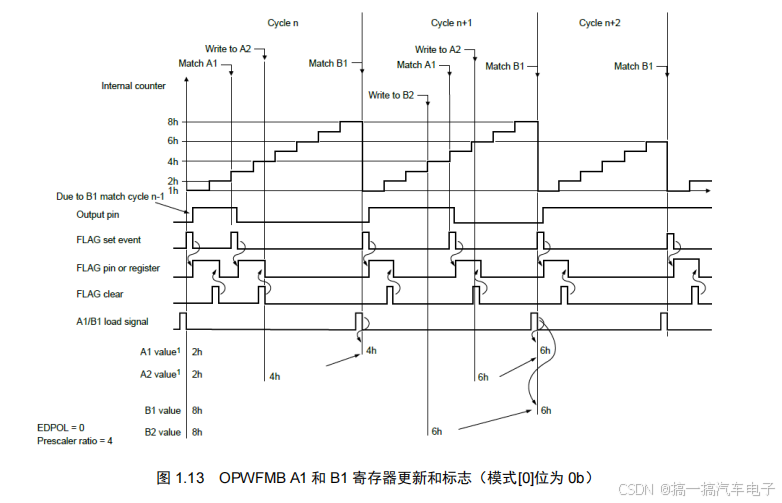

图 1.13 描述了 A1 和 B1 寄存器加载的时序。A1 和 B1 加载信号在计数器周期的最后一

个系统时钟周期生成的相同信号。因此,在计数器(EMIOSCNT [n])加载 0x1 的同时,分

别用 A2 和 B2 值更新 A1 和 B1。该事件定义为循环边界。加载信号脉冲具有一个系统时钟

周期的持续时间。如果在周期 n 内写入 A2 和 B2,则它们的值分别在周期 n + 1 的第一个时

钟在 A1 和 B1 可用,并且新值用于周期 n + 1 的匹配。EMIOSOUDIS 寄存器的更新禁止位

OU [n]可用于控制这些寄存器的更新,从而允许延迟 A1 和 B1 寄存器的更新以进行同步。

在图 1.13 中,假定通道和全局预分频器都设置为 0x1(每个分频比为 2),这意味着通

道内部计数器每四个系统时钟周期转换一次。仅当 MODE [1]设置为 0 时在 B1 匹配上生成

FLAG,或者在 MODE [1]设置为 1 时在 A1 和 B1 匹配上生成 FLAG。由于 B1 标志出现在

周期边界,因此该标志可用于指示将写在周期 n 上的 A2 或 B2 数据分别加载到 A1 或 B1,

从而在周期 n + 1 中生成匹配项。请注意,FLAG 具有同步操作,这意味着在 FLAG 设置事

件后的一个系统时钟周期将其置为有效。

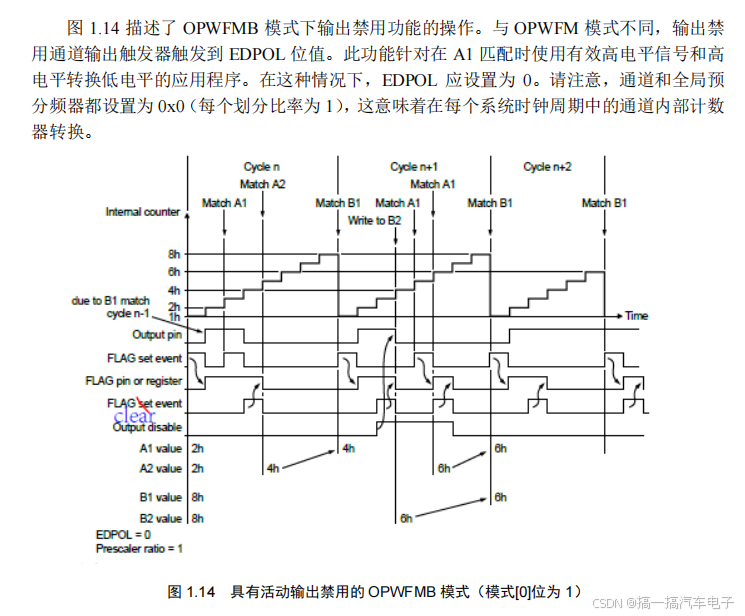

请注意,输出禁用具有同步操作,这意味着输出禁用输入引脚的置位将导致通道输出触

发器在下一个系统时钟周期转换为 EDPOL。如果输出禁用输入被置为无效,则输出引脚在

以下 A1 或 B1 匹配处转换。

在图 1.14 中,假设输出禁用输入已启用并被通道选择。请参考 UC 控制寄存器

(EMIOSCn),以获得有关 ODIS 和 ODISSL 位(分别启用和选择输出禁用输入)的详细说

明。

FORCMA 和 FORCMB 位分别允许软件将输出触发器强制为对应于比较器 A 或 B 上的

匹配的电平。与 B1 匹配类似,FORCMB 将内部计数器设置为 0x1。FORCMA 或 FORCMB

位置为有效,不能把 FLAG 位置 1。

图 1.15 描述了占空比为 100%和 0%的信号的产生。假设 EDPOL = 0,并且预分频器的

最终值为 1。最初,A1 = 0x8,B1 = 0x8。在这种情况下,B1 匹配优先于 A1 匹配,因此输

出触发器被设置为 EDPOL 位的补码。该周期对应于 100%的占空比信号。对于任何大于或

等于 B1 的 A1 值,都可以生成相同的输出信号。

如图 1.15 周期 9 所示,如果 A1 = 0x0,则产生 0%占空比信号。在这种情况下,与周期

9 的 A1 = 0x0 匹配同时发生周期 8 的 B1 = 0x8 匹配。有关 A1 和 B1 匹配生成的说明,请参

见图 1.12。在这种情况下,A1 匹配优先于 B1 匹配,并且输出信号转换为 EDPOL。

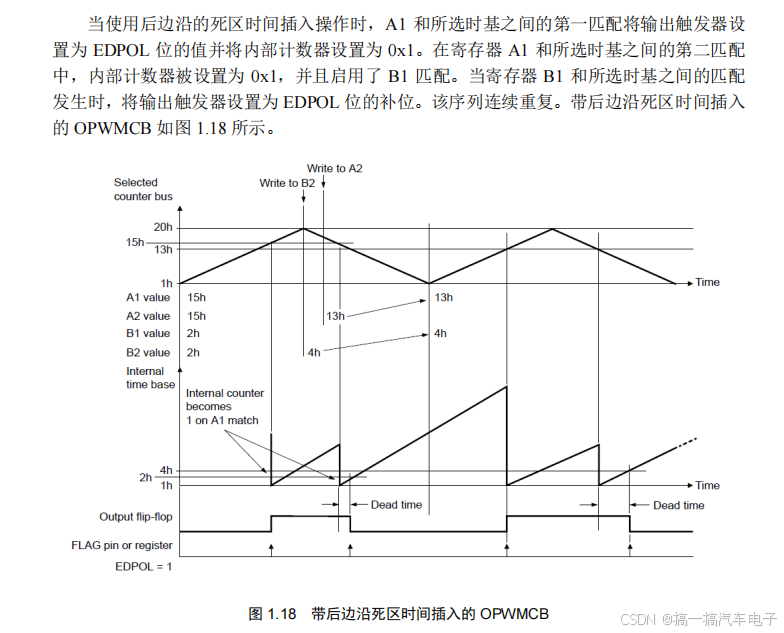

1.2.8 死区时间插入的中心对齐输出脉冲宽度调制缓冲(OPWMCB)模式

该操作模式生成一个死区时间插入前边沿(模式[6:0] = 10111b1)或后边沿(模式[6:

0] = 10111b0)的中心对齐的 PWM。A1 和 B1 寄存器是双缓冲的,以允许在更改 A2 或 B2

寄存器值时允许平滑的输出信号。

BSL [1:0]位选择时基。被配置为 OPWMCB 模式的通道所选择的时基应是配置为 MCB

向上/向下模式的通道,如图 1.7 所示。建议在输入 OPWMCB 模式后启动 MCB 通道时基,

以避免在第一个占空比下丢失匹配项。

寄存器 A1 包含 PWM 信号的理想占空比,与所选时基进行比较。

寄存器 B1 包含死区时间值并与内部计数器进行比较。对于前边沿死区时间插入,输出

PWM 占空比等于寄存器 A1 和寄存器 B1 之间的差异,并且对于后边沿死区时间插入,输出

PWM 占空比等于寄存器 A1 和寄存器 B1 的总和。MODE[0]分别在后边沿和前边沿插入之

间选择。

注:内部计数器以内部预分频器的比率运行,而所选择的时间基数可以以不同的预分频器比率运行。

当输入 OPWMCB 模式,从 GPIO 模式出来时,将输出触发器设置为 EMIOSC[n]寄存器

中 EDPOL 位的补位。

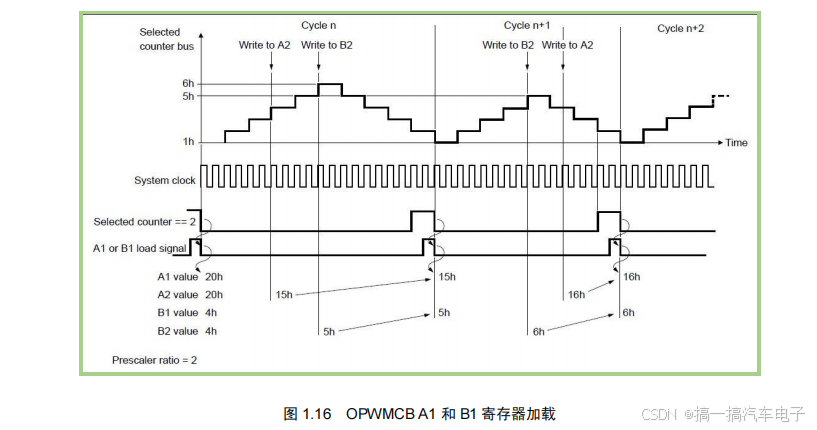

图 1.16 描述了当所选择的计数器总线从 0x2 到 0x1 转换时发生 A1 和 B1 寄存器的加载。

此事件定义为循环边界。注意,将在循环 n 内写入 A2 或 B2 的值分别加载到 A1 或 B1 寄存

器中,并用于在循环 n + 1 中生成匹配。

EMIOUDIS 寄存器的 OU [n]位可用于禁用 A1 和 B1 更新,从而允许在其他通道中与

A1 或 B1 寄存器的加载同步这些寄存器上的加载。注意,使用更新禁用位 A1 和 B1 寄存器

可以在相同的计数器周期上更新,从而允许同时改变两个寄存器。

在此模式下,A1 匹配始终将内部计数器设置为 0x1。当使用前边沿死区时间插入时,

第一 A1 匹配将内部计数器设置为 0x1。当寄存器 B1 和内部时基之间发生匹配时,将输出

触发器设置为 EDPOL 位的值。在寄存器 A1 和所选时基接下来的匹配中,将输出触发器设

置为 EDPOL 位的补充。该序列连续重复。由于翻转后,内部计数器不应达到 0x0。为了避

免它,用户不应写入 EMIOSB 寄存器的值大于外部计数限制和 EMIOSA 值之间的差异的两

倍。

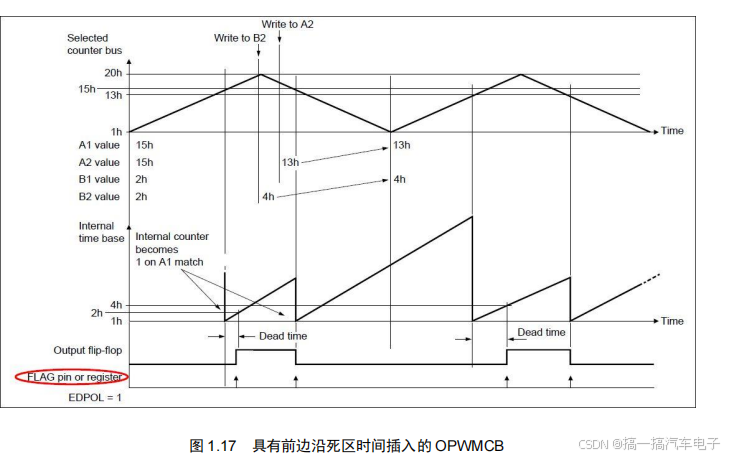

图 1.17 显示了中心对齐 PWM 信号的两个循环。请注意,A1 和 B1 寄存器值都在同一

周期内更改,允许同时变化占空比和死区时间值。

PWM 信号可以在后边沿当 MODE[1]设置为 0 时或者在前后边沿当 MODE[1]设置为 1

时生成 FLAG。如果在比较器 A 和 B 上发生后续匹配,则不管 FLAG 位的状态如何,继续

生成 PWM 脉冲。

注:在 OPWMCB 模式下,FORCMA 和 FORCMB 与常规匹配没有相同的行为。相反,它们将输出触

发器强制到恒定值,这取决于所选的死区时间插入模式,前边沿或者后边沿以及 EDPOL 位的值。

FORCMA 具有不同的行为,具体取决于所选择的死区时间插入模式,前边沿或者后边

沿。在前边沿死区时间插入 FORCMA 强制输出触发器过渡到 EDPOL 的补位。在后边沿死

区时间插入,输出触发器被强制到 EDPOL 位的值。

如果设置了 FORCMB 位,则输出触发器值取决于所选的死区时间插入模式。在前边沿

死区时间插入 FORCMB 强制输出触发器转换到 EDPOL 位值。在后边沿死区时间插入输出

触发器被强制与 EDPOL 值的补位。

注:FORCMA 位设置不会将内部时间基于 0x1 设置为常规 A1 匹配。

在 FORCMA 或 FORCMB 置位的情况下,不设置 FLAG 位,甚至是 ORCMA 和 FORCMB

同时置位。

注:FORCMA 和 FORCMB 即使在关于输出引脚转换的冻结或正常模式中也具有相同的行为。

当 FORCMB 和 FORCMA 一起置位时,输出触发器设置为相反的 EDPOL 位值。这等

于说,在选择前边沿插入死区时间时 FORCMA 的优先级高于 FORCMB,并且在选择后边

沿死区时间插入时 FORCMB 的优先级高于 FORCMA。

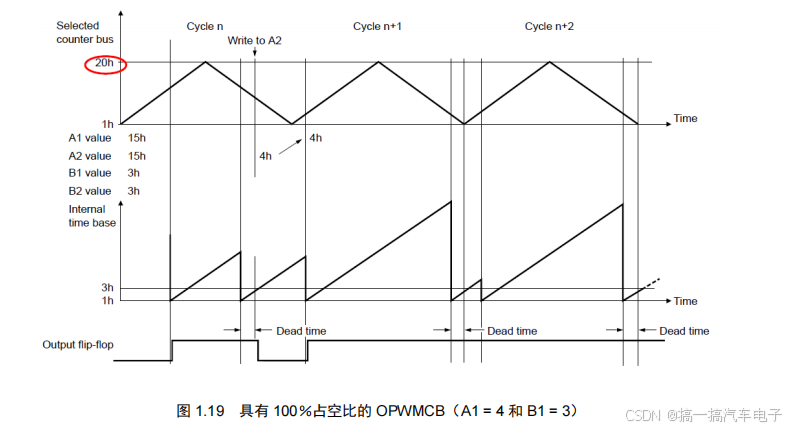

根据外部时基的周期,可以通过将适当的值设置为 A1 和 B1 寄存器来生成 0%至 100%

的占空比。设置 A1 = 0x1 生成 100%占空比波形。假设 EDPOL 被设置为 1 和带后边沿死区

时间插入的 OPWMCB 模式,如果 B1 发生在循环边界(外部计数器= 1)之后,则可以生成

100%占空比信号。仅当引脚以 EDPOL 值的补位的当前周期开始,如果 A1 大于所选择的计

数器总线周期的最大值,则才会产生 0%的占空比。在 100%占空比的情况下,可以通过使

用 FORCMA 和/或 FORCMB 来获得从 EDPOL 到 EDPOL 的补位的转变。

注:如果当 A1 在 OPWMCB 置为有效设置为 0x1,可能由于模式进入的时候引脚的电平,在第一个

PWM 周期中可能无法获得 100%占空比。

只允许将不同于 0x0 的值写入 A1 寄存器。如果 0x0 加载到 A1,则结果是不可预测的。

注:当 A1 设置为(外部计数器总线周期)/ 2 时,会发生特殊情况,这是外部计数器的最大值。在这

种情况下,输出触发器不断设置为 EDPOL 位值。

内部通道逻辑可防止从一个周期匹配以传播到下一个周期。在后边沿死区时间插入 B1

匹配从循环 n 最终通过循环边界越过并发生在循环 n + 1 中。在这种情况下,B1 匹配被屏蔽,

不会导致输出触发器转换。因此,循环 n + 1 中的匹配不受来自循环 n 的 B1 匹配的影响。

图 1.19 显示了通过设置 A1 = 0x4 和 B1 = 0x3 产生的 100%占空比输出信号。在这种情

况下,后边沿位于循环 n + 1 的边界处,实际上被认为属于循环 n + 2,因此不会导致输出触

发器转换。

输出禁用功能(如果已启用)会导致输出触发器转换到 EDPOL 的补位状态。此功能允

许应用程序将通道输出引脚强制到“安全”状态。即使在这种情况下,内部通道匹配也继续

发生,从而生成 FLAG。一旦输出禁用被禁用,通道输出引脚再次由 A1 和 B1 匹配控制。

请注意,此过程是同步的,这意味着输出通道引脚仅在系统时钟边缘转换。

重要的是要注意到,例如在 OPWMB 和 OPWFMB 模式中,

用于设置或清除通道输出触发器的匹配信号在通道组合比较器输出信号的失效上生成,

该频道组合与 A1 或 B1 寄存器值比较信号。请参阅图 1.11,该图 1.11 描述了 OPWFMB 模

式下从匹配到输出触发器转换的延迟。OPWMCB 模式在关于匹配和输出引脚转换的操作类

似于 OPWFMB。

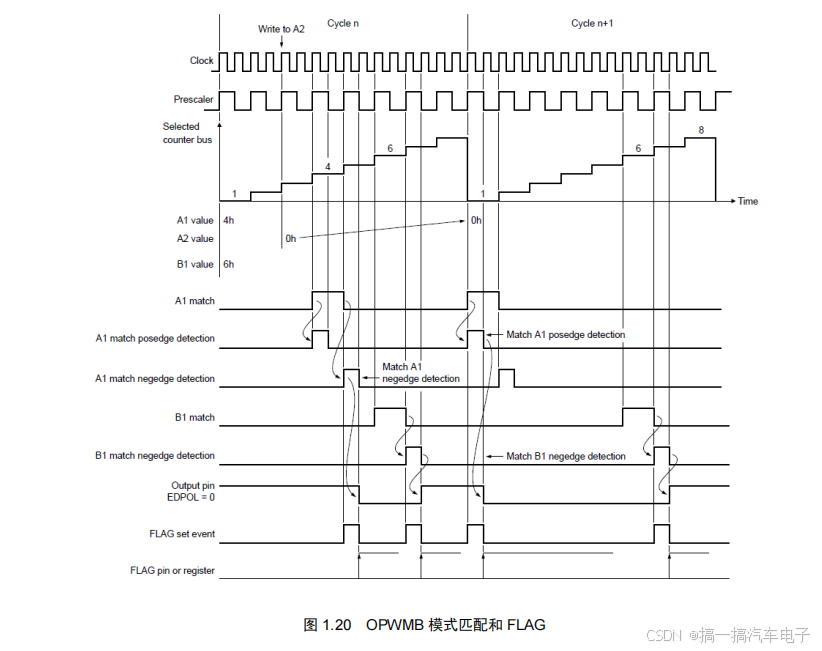

1.2.9 输出脉冲宽度调制缓冲(OPWMB)模式

OPWMB 模式(MODE[6:0] = 11000B0)用于生成具有可编程前边沿和后边沿放置的

脉冲。必须从计数器总线中选择一个 MCB 向上模式驱动的外部计数器。

A1 寄存器值定义第一个边缘和 B1 寄存器定义第二边缘。输出信号极性由 EDPOL 位定

义。如果 EDPOL 为零,则当 A1 匹配所选择的计数器总线时发生负边沿,并且当 B1 与所

选计数器总线匹配时发生正边沿。

A1 和 B1 寄存器在循环边界处分别从 A2 和 B2 双缓冲和更新。加载操作类似于

OPWFMB 模式。有关 A1 和 B1 寄存器更新的更多信息,请参阅图 1.13。

当 Mode[1]清除时,B1 匹配时可以生成 FLAG,或当 MODE[1]置 1 时,在 A1 和 B1 匹

配可以生成 FLAG。如果在比较器 A 和 B 上发生后续匹配,则不管 FLAG 位的状态如何,

继续生成 PWM 脉冲。

FORCMA 和 FORCMB 位允许软件强制输出触发器分别对应于 A1 或 B1 上匹配的电平。

FORCMA 和 FORCMB 操作不能设置 FLAG 位。

在 OPWMB 模式下,将输出触发器设置为 EMIOSC[n]寄存器中的 EDPOL 位的值。

适用于 OPWMB 模式的一些规则是:

如果在同一计数器周期内发生同时发生,B1 匹配最优先于 A1 匹配项;

A1 = 0 匹配来自循环 n,优先于 B1 匹配从循环 n-1 匹配;

如果在同一周期内的 B1 匹配后发生,则屏蔽 A1 匹配项;

在循环 n 上写入 A2 或 B2 的任何值都加载到以下循环边界处的 A1 和 B1 寄存器(假

设 OUIOUDIS 寄存器的位不被置位)。因此,新值将用于循环 n + 1 中的 A1 和 B1

匹配。

图 1.20 描述了关于 A1 和 B1 匹配的 OPWMB 模式的操作和通道输出引脚的转换。在此

示例中,EDPOL 设置为零。

请注意,输出引脚转换基于 A1 和 B1 匹配信号。图 1.20 显示了循环 n + 1 中的 A1 寄存

器的值设置为零。在这种情况下,使用匹配上升沿代替下降沿来转换输出触发器。

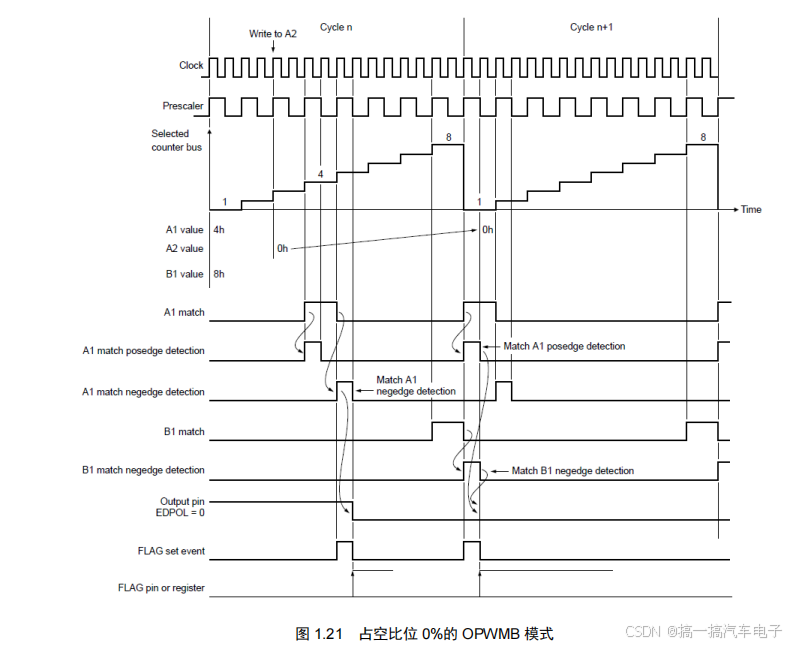

图 1.21 描述了 0%占空比的通道操作。请注意,A1 匹配的上升沿信号与 B1 = 0x8 下降

沿信号同时发生。在这种情况下,A1 匹配优先于 B1 匹配,使输出引脚保持在 EDPOL 值,

从而产生 0%的占空比信号。

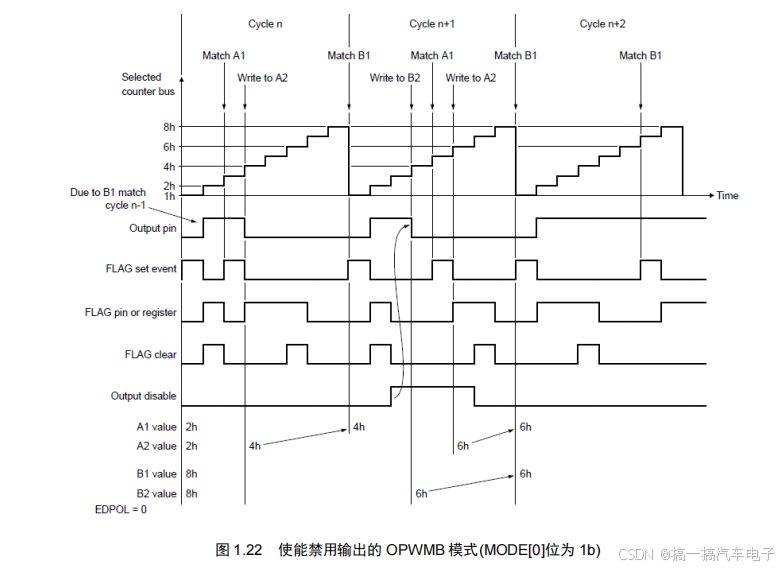

图 1.22 描述了输出禁用信号有效的 OPWMB 模式的操作。输出禁用在输出引脚中的转

换强制转换到 EDPOL 值。在输出禁用信号为无效后,输出禁用允许输出引脚在接下来的

A1 或 B1 匹配时转换。请注意,输出禁用不会修改 FLAG 位行为。注意,在输出禁用信号

的有效和输出引脚的转换之间存在一个系统时钟延迟与 EDPOL 的转换。

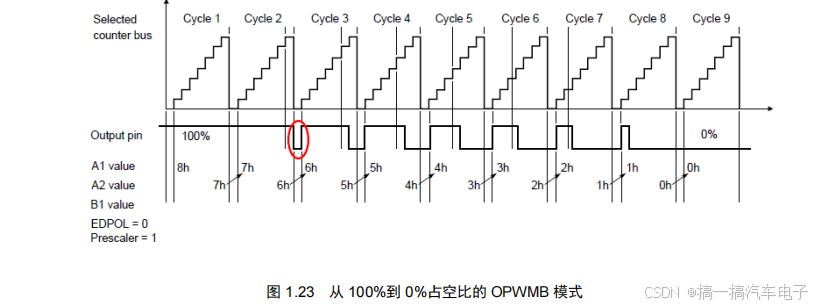

图 1.23 显示了从 100%到 0%占空比的波形。在这种情况下 EDPOL 为零。在该示例中,

B1 被编程为与外部所选时基的周期相同的值。

在图 1.23 中,如果 B1 被设置为低于 0x8 的值,则通过仅通过改变 A1 寄存器值来实现

0%的占空比。

由于 B1 匹配优先于 A1,因此将输出引脚转换与 B1 匹配的 EDPOL 位的补位。还要注

意,例如如果 B1 设置为 0x9,不发生 B1 匹配,因此生成 0%占空比信号。

1.2.10 用触发器(OPWMT)模式输出脉冲宽度调制

OPWMT 模式(MODE[6:0] = 0100110)旨在支持产生脉冲宽度调制信号,其中在信

号输出时不修改周期,但是在占空比将变化并且不得产生毛刺。该模式旨在与以相同模式执

行并共享共同时基的其他通道结合使用。它将支持相对于其他通道的固定 PWM 前沿位置的

每个信道以及在可以从模块输出的周期的任何点处产生触发信号的能力,以启动 SOC 的其

他部分中的活动,例如启动 ADC 转换。

必须从其中一个计数器总线中选择以 MC 向上或 MCB 向上模式驱动的外部计数器。

寄存器 A1 定义 PWM 输出脉冲的前沿,并如 PWM 期间的开始。这使得可以确保在使

用共享时基时可以在相对于其他通道的特定时间内发生 OPWMT 模式中的多个通道的前沿。

这可以允许引入每个通道的固定偏移,这在发光 PWM 控制信号的产生中可以特别有用,其

中期望边缘彼此不一致以帮助消除噪声产生。寄存器 A1 的值表示 PWM 通道相对于所选时

位的偏移。A1 可以配置在所选时基范围内的任何值。请注意,如果时基模式由 MCB 模式

下的通道驱动,则加载有 0x0 的寄存器不会产生匹配。

由于在生成 PWM 信号时不得修改 PWM 通道的偏移,因此不缓冲 A1。在修改 A1 的情

况下,立即更新,一个 PWM 脉冲可能会丢失。

EMIOSB [n]地址可以访问 B2 寄存器,用于写入和 B1 寄存器。寄存器 B1 定义 PWM 输

出脉冲的后边沿,以及 PWM 信号的占空比。要使用 PWM 信号同步 B1 更新,因此确保正

确的输出脉冲生成从 B2 到 B1 的转移在寄存器 A1 的每一个匹配时完成。此行为与 OPWM

模式在下一周期更新的操作相同。

EMIOSOUDIS 寄存器仅影响 B2 和 B1 之间的传输。

为了考虑由寄存器 A1 定义的波形的前沿的偏移,将需要在寄存器 B1 中保持的后边沿

可以进入下一个时段。这意味着对 B1 寄存器的匹配不必通过 A1 寄存器中的匹配项来限定。

这样的影响意味着错误地将寄存器 B1 设置为小于寄存器 A1 的值将导致输出在一个循环边

界上保持,直到遇到 B1 值为止。

该模式通过仅在寄存器A1匹配时用寄存器 B2内容更新寄存器B1 来提供后沿的缓冲更

新。

将寄存器 A1 中的值与所选时基的值进行比较。当比较器 A1 上发生匹配时,将输出触

发器设置为 EDPOL 位的值。当比较器 B 上发生匹配时,将输出触发器设置为 EDPOL 位的

补位。

请注意,输出引脚和 FLAG 转换基于 A1,B1 和 A2 匹配信号的上升沿。有关匹配上升

沿的详细信息,请参阅输出脉冲宽度调制缓冲(OPWMB)模式的图 1.20。

寄存器 A2 定义了 PWM 周期内的触发事件的生成,A2 应配置在所选时基范围内的任

何值,否则不会生成触发器。比较器上的匹配将生成 FLAG 信号,但它对 PWM 输出信号产

生没有影响。典型的设置要获取带 FLAG 的触发可以启用 DMA 并驱动通道的 ipd_done 输

入。

A2 没有缓冲,因此其更新即时。如果通道在发生更改时运行,则可能导致一个触发事

件的丢失或同一时段内的两个触发事件的生成。可以通过 eMIOS UC 在 UC [n]基地址的备

用 A 寄存器(eMIOS_ALTA)+ 0x14 中读取或写入来访问寄存器 A2。

FLAG 信号仅在与 A2 上的比较器上匹配。使用 A1 或 B1 或 B2 的比较器上的匹配对

FLAG 没有影响。

随时,FORCMA 和 FORCMB 位允许软件强制输出触发器分别对应于对应于 A 或 B 上

匹配的电平。任何 FORCMA 和/或 FORCMB 都优先于有关输出引脚转换的任何同时匹配。

注意,由于同时执行 FORCMA / FORCMB 置为有效,因此不禁止在 A 匹配处将 B2 内容加

载到 B1 寄存器中。如果同时 FORCMA 和 FORCMB 设置为有效,则输出引脚为 EDPOL 值

的补位,例如 A1 和 B1 寄存器具有相同的值。FORCMA 置为有效导致从寄存器 B2 转移到

B1,例如常规 A 匹配,无论 FORCMB 设置如何。

如果在比较器 A1 和 B 上发生后续匹配,则不管 FLAG 位的状态如何,都会继续产生

PWM 脉冲。

在 OPWMT 模式下,将输出触发器设置为 EMIOSC [n]寄存器中的 EDPOL 位的补位。

为了实现 0%占空比,寄存器 A1 和 B 必须设置为相同的值。当对比较器 A 和 B 的同时

匹配发生时,输出触发器在每个时段都设置为 EDPOL 的补位值。

为了达到 100%的占空比,必须将寄存器 B1 的值设置为大于所选时基的最大值,因此,

如果必须实现 100%的占空比,则对于 A 而言,时基的最大计数器值为 0xFFFFFE 24 位计

数器和 16 位计数器的 0xFFFE。当比较器 A1 发生匹配时,输出触发器在每个周期都设置为

EDPOL 位的值。从寄存器 B2 到 B1 的传输仍然由比较器 A 的匹配触发。

与其他 EMIOS 模式一样,OPWMT 模式将实现输出禁用功能。在 EMIOS UC 控制寄存

器(EMIOSC[n])中设置 ODIS 位将启用输出禁用功能。如果所选输出禁用输入信号被置位

通道,则输出引脚将转到 EDPOL 的倒数。通道将继续正常运行,但输出将是固定的。当输

出禁用输入信号被否定时,输出引脚将返回正常操作。

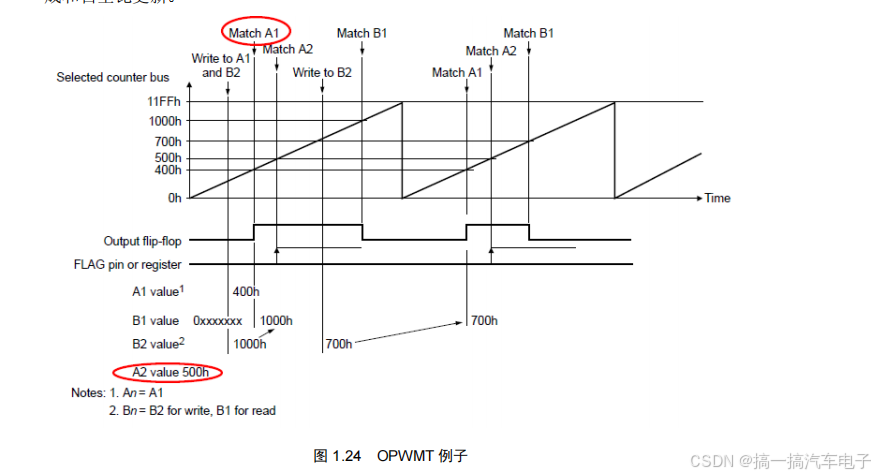

图 1.24 显示了在 OPWMT 模式下运行的统一通道,在下一周期更新中具有触发事件生

成和占空比更新。

图 1.25 显示了在触发事件生成 0%占空比 OPWMT 模式运行的统一通道。

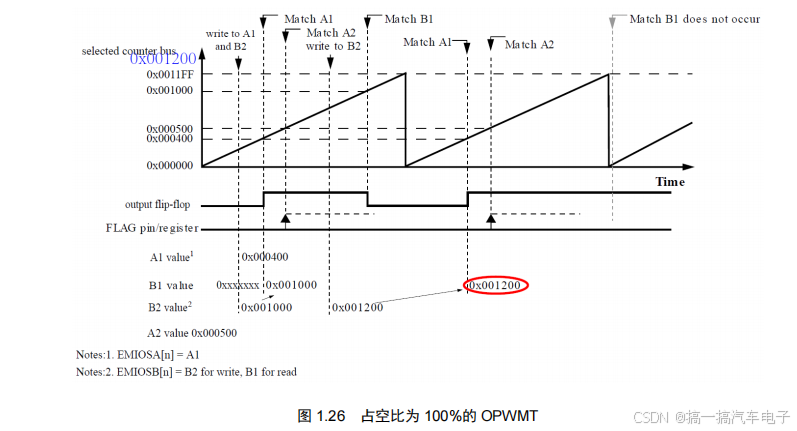

图 1.26 显示了在触发事件生成 100%占空比 OPWMT 模式运行的统一通道。

1.2.11 时钟预分频器(CP)

CP 将 GCP 输出信号划分为为统一通道的内部计数器生成时钟启用。通过在 EMIOSC [n]

寄存器中的 UCPRE [1:0]字段描述中定义的值预先置换 GCP 输出信号。通过在 EMIOSC [n]

中的 UCPREN 位来启用预分频器,并且可以通过清除该位随时停止,从而停止统一信道中

的内部计数器。

为了确保安全工作并避免故障,每当需要预定速率的任何更新时,必须执行以下步骤:

- 在 EMIOSMCR 寄存器中的 GPREN 位和 EMIOC [n]寄存器中的 UCPREN 位,从而

在寄存器中写入 0,从而禁用预分频器; - 在 EMIOSC [n]寄存器中的 UCPRE [1:0]位的预分频速率下写出所需的值;

- 通过在 EMIOSC [n]寄存器中的 UCPREN 位,通过在 UCPREN 位中写入通道预分

频器; - 通过在 EMIOS MCR 寄存器中的 GPREN 位写入 1 来启用全局预分频器。

在冻结状态或否定 GTBE 输入期间,预分频器未禁用。

1.2.12 冻结对统一频道的影响

当在调试模式下,EMIOSMCR 寄存器中的 FRZ 位和 EMIOSC [n]中的 FREN 位都设置,

内部计数器和统一通道捕获和比较功能被停止。UC 在其当前状态冻结。

在冻结期间,所有寄存器都可以访问。当统一通道在输出模式下运行时,匹配功能仍然

可用,允许软件强制输出到所需的电平。

请注意,对于输入模式,忽略通道冻结时可能发生的任何输入事件。

在退出调试模式或冻结启用位时(EMIOSMCR 中的 FRZ 或 FREN 在 EMIOSC [n]寄存

器中),通道操作恢复,但在通道再次进入 GPIO 模式之前可能会不一致。

1.2.13 IP 总线接口单元(BIU)

BIU 在内部接口总线和外围总线之间提供接口,允许所有子模块和此 IP 接口之间的通

信。

BIU 允许 8,16 和 32 位访问。它们在单个循环时钟中的 32 位数据总线上执行。 - 冻结对 BIU 的影响

当设置 EMIOSMCR 寄存器中的 FRZ 位并且模块处于调试模式时,BIU 的操作不受影

响。

1.2.14 全局时钟预分频器子模块(GCP)

GCP 划分系统时钟以为通道的 CPS 生成时钟。主时钟信号由 EMIOSMCR 寄存器中的

GPRE [7:0]位中的全局预分频器时钟分频器表中定义的值预先定义。通过在 EMIOSMCR

寄存器中设置 GPLEN 位,通过清除该位,可以随时停止全局预分频器,从而停止所有通道

中的内部计数器。

为了确保安全工作并避免故障,每当需要预定速率的任何更新时,必须执行以下步骤: - 在 EmioSMCR 寄存器中的 Gpren 位写 0,从而禁用全局预分频器;

- 在 EMIOSMCR 寄存器中的 GPRE [7:0]位,在 GPRE [7:0]比特中写入所需的值;

- 通过在 EmiOSMCR 寄存器中的 Gpren 位写入 1 来启用全局预分频器。

在冻结状态或否定 GTBE 输入期间,预分频器未禁用。 - 冻结对 GCP 的影响

设置 EMIOSMCR 寄存器中的 FRZ 位并在模块处于调试模式时,GCP 子模块的操作不

受影响,即该子模块中没有冻结功能。

1.2.15 初始化/应用信息

在重置 EMIO 时,统一通道进入 GPIO 输入模式。

在更改操作模式之前,必须将 UC 编程为 GPIO 模式,并且 EMIOSA [n]和 EMIOSB [n]

寄存器必须使用正确的下一个操作模式进行正确的值来更新。然后可以使用新的操作模式写

入 EMIOSC [n]寄存器。如果在不执行此过程的情况下将 UC 从一种模式更改为另一种模式,

则所选时基的第一个操作周期可以是随机的,即,如果 EMIOSA [n]或 EMIOSB [n]的内容为

在时基与 EMIOSA [n]或 EMIOSB [n]的先前内容匹配之前未使用正确的值更新。

启用中断时,软件必须在退出中断服务程序之前清除 FLAG 位。 - 应用信息

可以通过所有输出操作模式生成相关输出信号。EMIOS_OUDIS 寄存器的位 OU [n]可用

于控制这些输出信号的更新。

为了保证相关通道的内部计数器在同一时钟周期中递增,必须在启用全局预分频器之前

设置内部预分频器。如果在启用全局预分频器后设置内部预分频器,则内部计数器可能以相

同的比率递增,但在不同的时钟周期中。

建议使用在 SAIC 模式下运行的一些 UCs 的 EMIO_FLAG_OUT 信号驱动输出禁用输入

信号。

当输出禁用条件发生时,软件中断例程必须在服务运行SAIC通道之前为输出通道服务。

此过程避免输出引脚中的毛刺。 - 时基生成

对于 MC 和 OPWFM 具有内部时钟源操作模式,可以通过配置时钟预分频器比来修改

内部计数器速率。图 1.27 所示了具有等于 1 的预分频器比的时基的示例。

注:MCB 和 OPWFMB 模式具有不同的行为。

如果预分频器比率大于一或外部时钟,则计数器可能以四种不同的方式中的一种,具体

取决于通道模式:

如果 MC 模式和在匹配开始时清除和外部时钟源被选择,则内部计数器的行为如图 1.28

所示。

如果 MC 模式和在匹配开始时清除和内部时钟源被选择,则内部计数器的行为如图 1.29

所示。

如果 MC 模式和在匹配结束时清除被选择,则内部计数器的行为如图 1.30 所示。

如果选择了 OPWFM 模式,则如图 1.29 所示的内部计数器行为。内部计数器在匹配信

号的开始时清除,跳过下一个预定时钟边沿,然后在后续预定时钟边沿中增加。

- S32K3 系列 eMIOS 配置说明

3.1 版本说明

本次配套例程使用的开发环境为:S32 Design Studio for S32 Platform 3.5。

RTD 版本为:RTD 4.0.0。

3.2 RTD 配置详解

PWM 的 RTD 配置有两种方式:IP 层配置和 MCAL 层配置,下面这两种配置方式进行

讲解介绍:

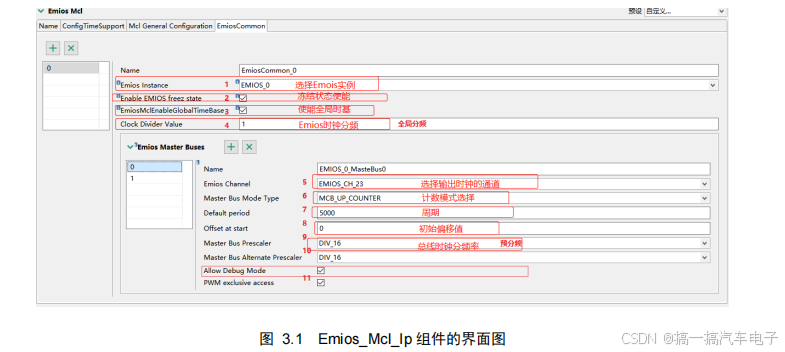

3.2.1 IP 层配置 - Emios_Mcl_Ip 组件

这个组件是控制通用的 eMIOS 和设置 eMIOS 为 MC 和 MCB 模式的组件,关于这个组

件的内容介绍如下,图是 Emios_Mcl_Ip 组件的界面图。

图中 1-4 是 eMIOS 的总体参数设置,5-11 是对通道设置为 MC 和 MCB 模式进行设置,

介绍如下:

图中 1 是选择 eMIOS 的实例,有 EMIOS_0、EMIOS_1 和 EMIOS_2 三个可以选择;

图中 2 是使能 eMIOS 冻结状态的选项;

图中 3 是使能全局时基的选项,这是只有这个 eMIOS 组件才能进行设置的,其他组件

没有这个选项;

图中 4 是设置全局预分频器;

图中 5 是设置设置 MC 和 MCB 模式的通道

图中 6 是设置通道的计数模式;

图中 7 是设置通道的计数周期;

图中 9 是设置通道预分频器;

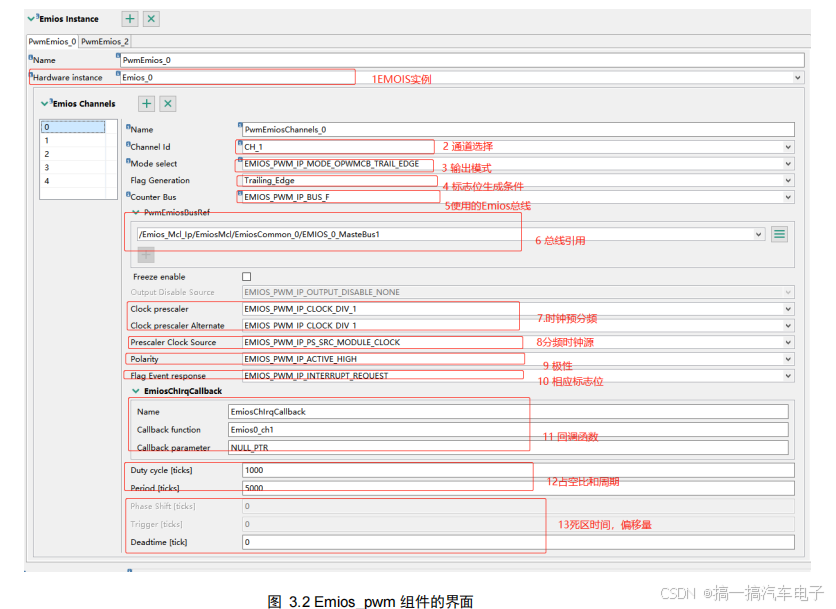

图中 11 是对通道使能 debug 模式; - Emios_pwm_1 组件

这个组件是控制通道输出 PWM 模式的组件,关于这个组件的内容介绍如下,图中

Emios_pwm 组件的界面。

图中 1 是设置 eMIOS 的通道选项;

图中 3 是设置 PWM 的输出模式,总共有 5 种模式可以进行选择;

图中 4 是选择 Flag 生成的位置,可以选择后边沿触发,也可以选择前后边沿都触发;

图中 5 是选择计数器的总线,选择内部总线可以不用去设置 MC 或 MCB 模式,但是选

择其他的总线要去 Emios_Mcl_Ip 组件设置相应的通道。

图中 6 是 MCL 模块中配置的时钟总线地址;

图中 7 是设置通道时钟分频系数;

图中 8 是选择分频的时钟源;

图中 9 是选择通道的极性;

图中 10 是选择 Flag 事件的响应,可以无选择无响应、中断响应和 DMA 响应三种;

图中 11 是设置中断回调函数,在图中 9 选择中断响应之后可以进行设置;

图中 12 是设置占空比,周期值;

图中 13 是分别是相移、触发位置和死区时间的设置选项,在图中 3 选择不同的模式下,

就可以进行对应的设置。 - 例程程序解读

4.1 IP 层例程:eMIOS 模块

以 S32K344 例程为例。该例程配置了 PWM 的四种模式,分别是 OPWFMB、OPWMCB、

OPWMB 和 OPWMT 模式,其中 OPWMCB 和 OPWMT 的计数总线分别用 MC 模式通道和

MCB 模式通道作为计数总线。

eMIOS0 通道 1 和 eMIOS0 通道 6 配置为输出 OPWMCB 模式,输出为边沿对齐,其中

eMIOS0 通道 1 输出的 PWM 时钟分频系数设置为 1,eMIOS0 通道 6 输出的 PWM 时钟分频

系数为 2;使用 PTB13 输出 eMIOS0 通道 1 的 PWM 波形,使用 PTC10 输出 eMIOS0 通道 6

的 PWM 波形, MC 向上向下计数模式作为计数总线

eMIOS0 通道 17 配置为输出 OPWMB 模式,使用 PTA0 输出 eMIOS0 通道 17 的 PWM

波形;

eMIOS0 通道 9 配置为输出 OPWMT 模式,并设置中断函数,使用 PTA1 输出 eMIOS0

通道 9 的 PWM 波形;

eMIOS2 通道 0 配置为 OPWFMB 模式,不设置中断,使用内部时钟进行输出 PWM 波

形,使用的是 PTD28 输出 PWM 波形。

主函数的程序代码如程序清单 4.1 所示。

程序清单 4.1

/* 时钟初始化*/

Clock_Ip_Init(&Clock_Ip_aClockConfig[0]);

/* 所有 port 口初始化 /

Siul2_Port_Ip_Init(NUM_OF_CONFIGURED_PINS_PortContainer_0_BOARD_InitPeripherals,

g_pin_mux_InitConfigArr_PortContainer_0_BOARD_InitPeripherals);

/ 使能 EMIOS 中断(建议在 RTD INT 模块设置,减少代码量)

- 根据 s32K3 RM 附件的中断映射,使能 5 IRQ /

IntCtrl_Ip_Init(&IntCtrlConfig_0);

/ 初始化 EMIOS /

Emios_Mcl_Ip_Init(0, &Emios_Mcl_Ip_0_Config_BOARD_INITPERIPHERALS);

/ Emios_0 两个 带死区的 PWM /

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch1);// PTB13 trail

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH1, EMIOS_PWM_IP_INTERRUPT_REQUEST); // 设

置标志为中断标志

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch6);// PTC10 lead

//设置标志为中断标志

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH6, EMIOS_PWM_IP_INTERRUPT_REQUEST);

/ Emios_0 输出另外 3 种 PWM*/

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch3); // PTB0 DAOC

//设置标志为中断标志

Emios_Pwm_Ip_SetFlagRequest(0 ,EMIOS0_CH3, EMIOS_PWM_IP_INTERRUPT_REQUEST);

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch17);// PTA0 OPWMB

//设置标志为中断标志

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH17, EMIOS_PWM_IP_INTERRUPT_REQUEST);

Emios_Pwm_Ip_InitChannel(0, &Emios_Pwm_Ip_I0_Ch9); // PTA1 OPWMT

//设置标志为中断标志

Emios_Pwm_Ip_SetFlagRequest(0, EMIOS0_CH9, EMIOS_PWM_IP_INTERRUPT_REQUEST);

/* Emios_3 一个 PWM - OPWFM 生成一个简单单通道 PWM /

Emios_Pwm_Ip_InitChannel(2, &Emios_Pwm_Ip_I2_Ch0);// PTD23 OPWFMB

/ 回调函数如下 /

/ 设置trail 死区时间 */

void Emios0_ch1(void p)

{

uint8 time = 0;

(void)p;

time = Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH1);

if(Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH1) == 500)

{

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH1,100);

}

else

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH1,500);

}

/ 设置lead死区时间 */

void Emios0_ch6(void p)

{

uint8 time = 0;

(void)p;

time = Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH6);

if(Emios_Pwm_Ip_GetDeadTime(0,EMIOS0_CH6) == 500)

{

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH6,100);

}

else

Emios_Pwm_Ip_SetDeadTime(0,EMIOS0_CH6,500);

}

/ 新配置 */

void Emios0_ch3(void p)

{

(void)p;

/ 设置新周期等 /

Emios_Pwm_Ip_SetDutyCycle(0,EMIOS0_CH3,3000);

}

/ 设置触发值 */

void Emios0_ch9(void p)

{

uint8 partmemt = 0;

(void)p;

/ 查看触发值 /

partmemt = Emios_Pwm_Ip_GetTriggerPlacement(0,EMIOS0_CH9);

}

/ 重新配置 */

void Emios0_ch17(void p)

{

(void)p;

/ 设置新周期 */

Emios_Pwm_Ip_SetDutyCycle(0,EMIOS0_CH17,2000);

}