解密GTH时钟架构:一网打尽收发器时钟之谜

背景:在学习高速接口协议中,往往容易被GTH架构的时钟结果混淆。为什么会有这么多时钟?这些时钟分别是干什么的?

资料:UltraScale Architecture GTH Transceivers UG576 (v1.7.1) August 18, 2021

本文为UG576的学习记录。以下内容全部在官方文档中有介绍。

参考时钟输入输出结构

GTH 收发器中的基准时钟结构支持两种工作模式:输入模式和输出模式。

输入模式

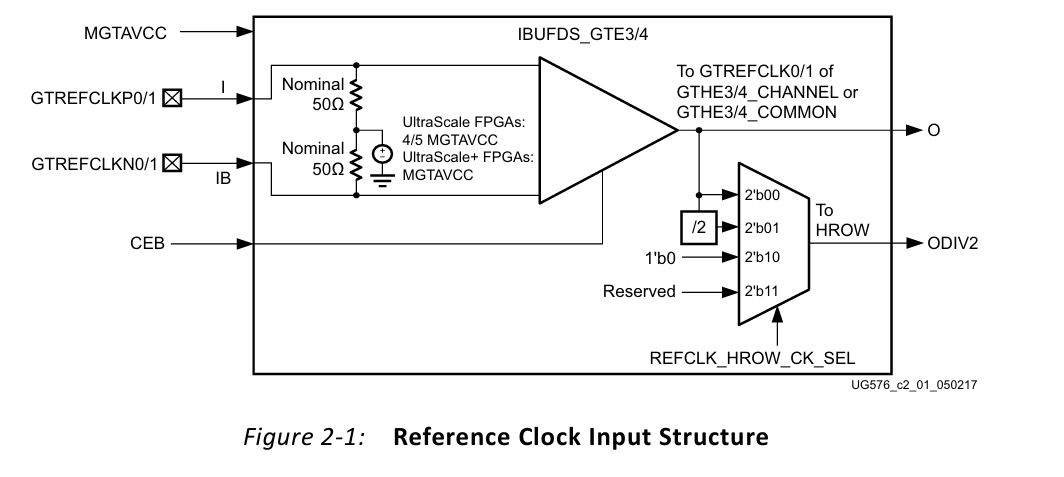

基准时钟输入模式的结构如下图所示。输入端在每个支路均采用内部 50Ω 端接,具体连接如下:

输出模式

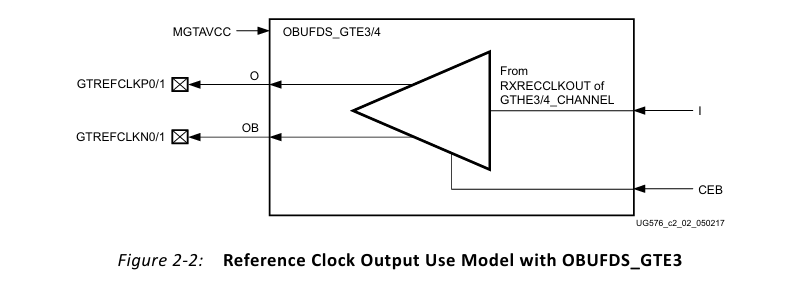

可以将内部恢复时钟以差分信号的形式稳定输出到外部专用基准时钟I/O引脚。

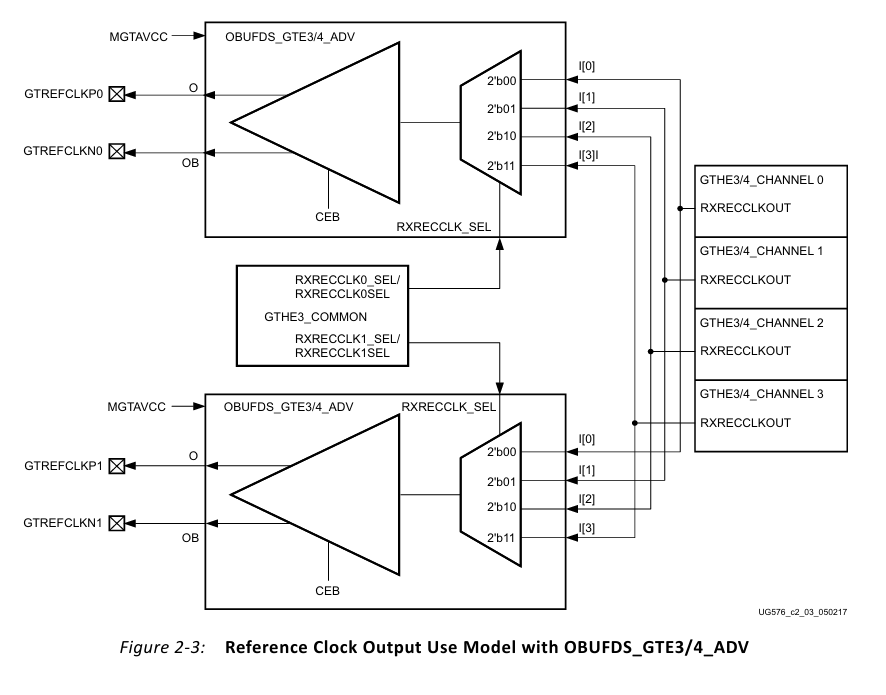

一个quad里面有四个独立通道,每个通道都有恢复出的独立的恢复时钟。可以用专用的原语输出这四个通道的任意一个时钟到专用的引脚。

参考时钟选择和分配

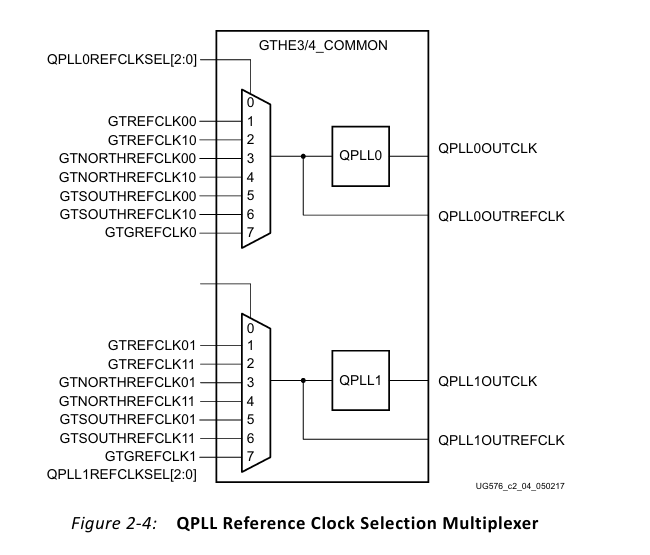

UltraScale系列GTH提供多种参考时钟输入。在一个quad中,包含四个GTH收发器通道,每个通道可以使用的参考时钟为6种。参考时钟根据速率的不同选择输入到QPLL或者CPLL。包含本地参考时钟GTREFCLK00/10和GTGREFCLK1。为了实现跨通道的时钟传输,XLINX还支持南向SOUTH和北向NORTH时钟。GTNORTHREFCLK00/10和GTSOUTHREFCLK00/10。

下图是参考时钟接入QPLL0和QPLL1两个。

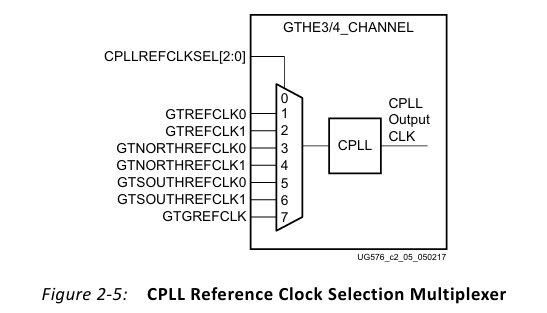

下图是参考时钟接入CPLL。

单路外部参考时钟模式

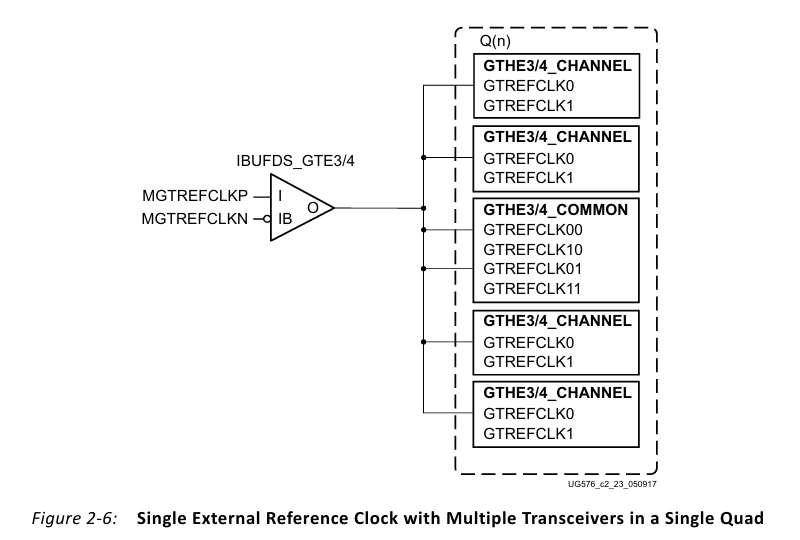

一个quad包含两对专用差分基准时钟输入引脚。MGTREFCLKP/MGTREFCLKN。要使用这个必须要例化IBUFDS_GTE3/4原语,这个是xilinx专用的一个时钟输入模块。内部拥有50Ω的端接电阻,确保时钟稳定传入芯片内部。

单路外部参考时钟可以同时为一个quad内的收发器提供统一标准。GTHE3/4_COMMON 原语:QPLL参考。GTHE3/4_CHANNEL 原语:CPLL参考。用户设计中需要将通过IBUFDS_GTE3/4输出端口的O的时钟连接到GTHE3/4_COMMON 原语和GTHE3/4_CHANNEL 原语的GTREFCLK0端口。

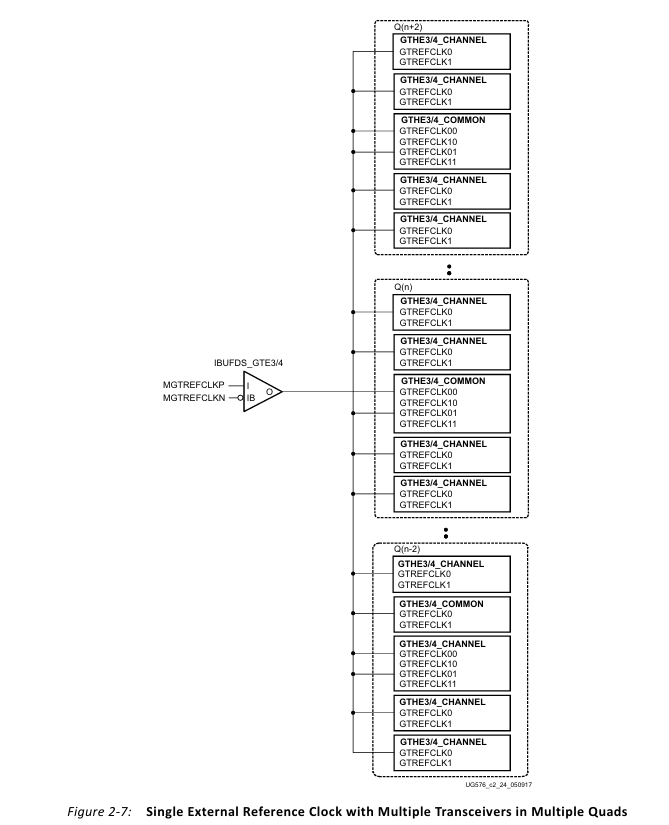

一个参考也可以连接到内部多个quad的参考时钟端口。使用这种模式是xilinx工具会自动完成必要的调整,包括,南北时钟布线资源配置。这种设计模式大大简化了跨组时钟路由的复杂度。

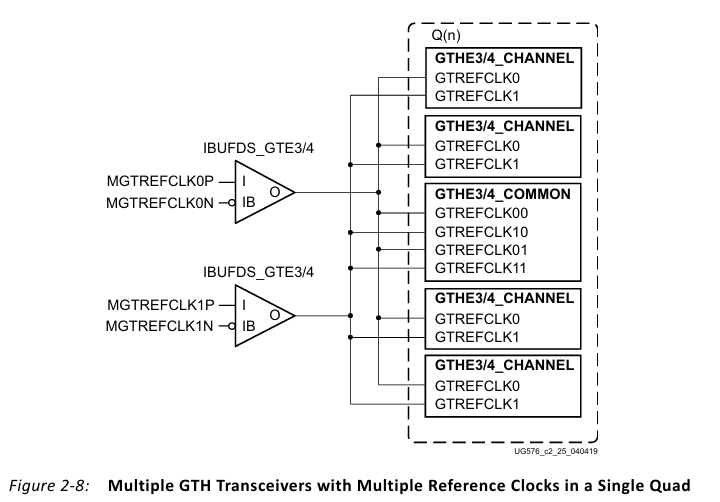

多路外部参考时钟使用模型

一个quad里面包含两对专用差分时钟输入引脚。MGTREFCLK0P/N和MGTREFCLK1P/MGTREFCLK1N。都可以连接到外部时钟源。使用过程中必须要遵循以下规则,每对引脚都必须实例化对应IBUFDS_GTE3/4原语。内部需要将外部的参考基准时钟MGTREFCLK0P/N连接到GTHE3/4_COMMON和GTHE3/4_CHANNEL的GTREFCLK0端口。第二路参考时钟MGTREFCLK1P/N连接到GTHE3/4_COMMON和GTHE3/4_CHANNEL的GTREFCLK1端口。

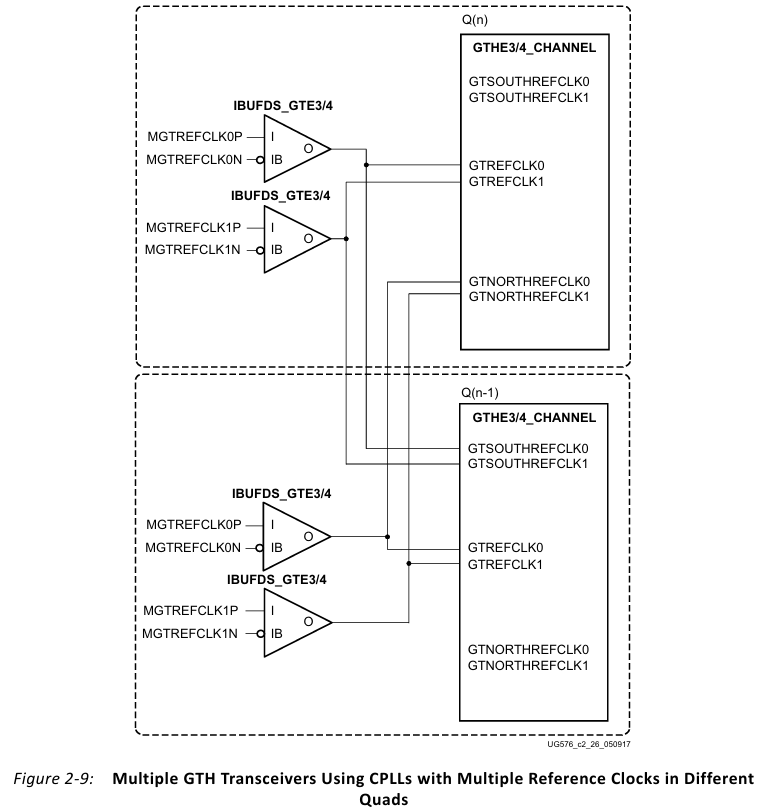

多路时钟跨通道配置

当外部接入两组参考时钟,对于同一通道组quad内的每个收发器,均可访问其正上方和正下方各一个quad的专用时钟。如下图所示,上方通道quad的MGTREFCLK0P/N可以连接到下方quad的GTSOUTHREFCLK0。MGTREFCLK1P/N可以连接到下方quad的GTSOUTHREFCLK1。下图是使用CPLL的参考时钟连接方法。

下图是使用QPLL的参考时钟连接方法。使用QPLL时,南北参考时钟变为GTSOUTHREFCLK00/01和GTSOUTHREFCLK10/GTSOUTHREFCLK11。

CPLL

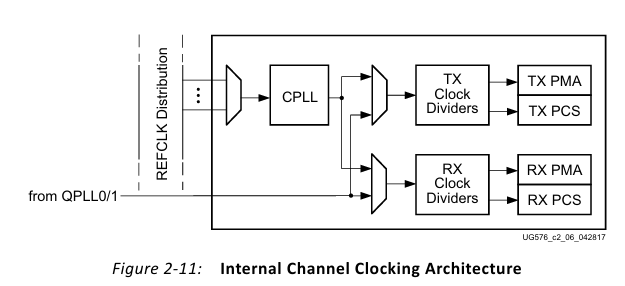

每个GTH收发器通道均包含一个环形振荡器的通道锁相环CPLL。其时钟架构如图所示。

发送端和接收端时钟分频器可以独立选择时钟源。即可以从QPLL0/1获取时钟,也可以从本通道CPLL获取时钟。这种独立选择机制使得TX数据通路与RX数据通路可使用不同的基准时钟输入,从而实现异步频率运行。如上图所示,CPLL时钟为发送接收端的时钟分频器提供了时钟,为后续的PMA和PCS部分提供时钟。(注:感觉这地方也和transceiver输出的时钟分为TX和RX的userclk相关)

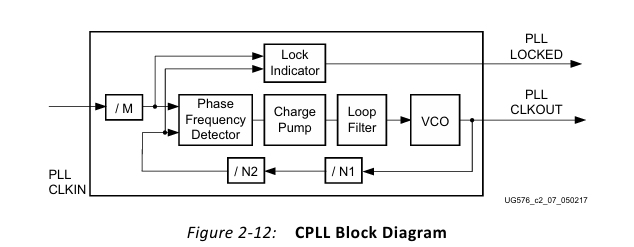

CPLL架构概念图

输入时钟在进入phase frequency Detector之前,可以被M进行分频。同时输出时钟VCO会被N1和N2进行分频反馈给phase frequency Detector。PLL锁定指示会根据M分频器和N1/N2分频器来判断时钟是否锁定。

另外CPLL收发器时钟工作频率范围为2.0GHZ到6.25GHZ。

CPLL输出频率计算公式

线速率计算公式

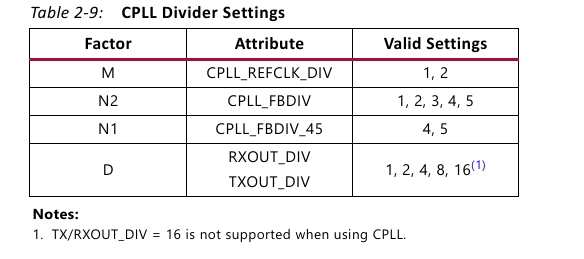

D为分频系数。代表TX or RX clock divider block的分频值。下表是CPLL的分频参数。

另外xilinx还支持动态配置CPLL。

QPLL

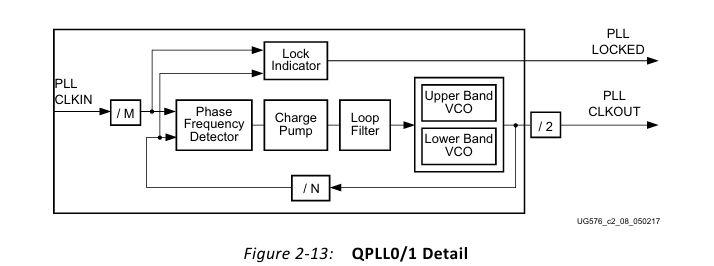

每个Quad包含两个基于LC结构的锁相环,称为QPLL0和QPLL1。当工作线速率超出CPLL的工作范围时,必须使用QPLL0/1。QPLL0/1的输出会送至Quad内每个串行收发器发送和接收端的分频器模块。用于控制后续的硬核PMA部分以及软核的PCS部分。与CPLL的时钟架构类似,如下图。

QPLL架构概念图

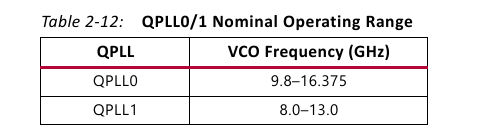

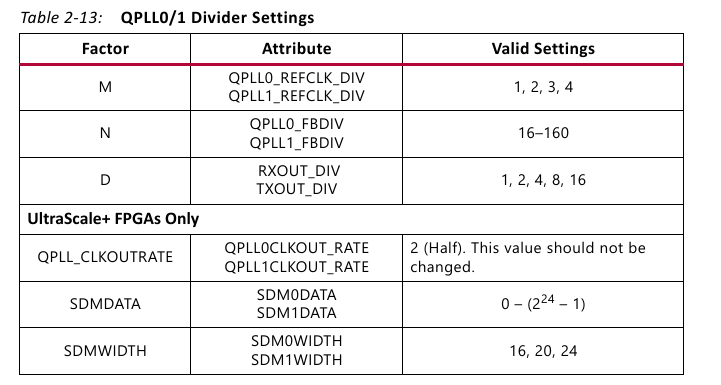

不同的是QPLL的VCO支持的时钟频率范围不一致。大致的频率范围如下表。但是由于不同的器件存在差异,需要自行查阅相关器件数据。当选择低频段VCO时,高频段VCO会自动断电。(这个软件会自动根据应用需求调整)

QPLL输出频率计算公式

线速率计算公式

下表是QPLL参数。

Xilinx的transceiver的时钟架构学习完毕。