74HC595芯片简析

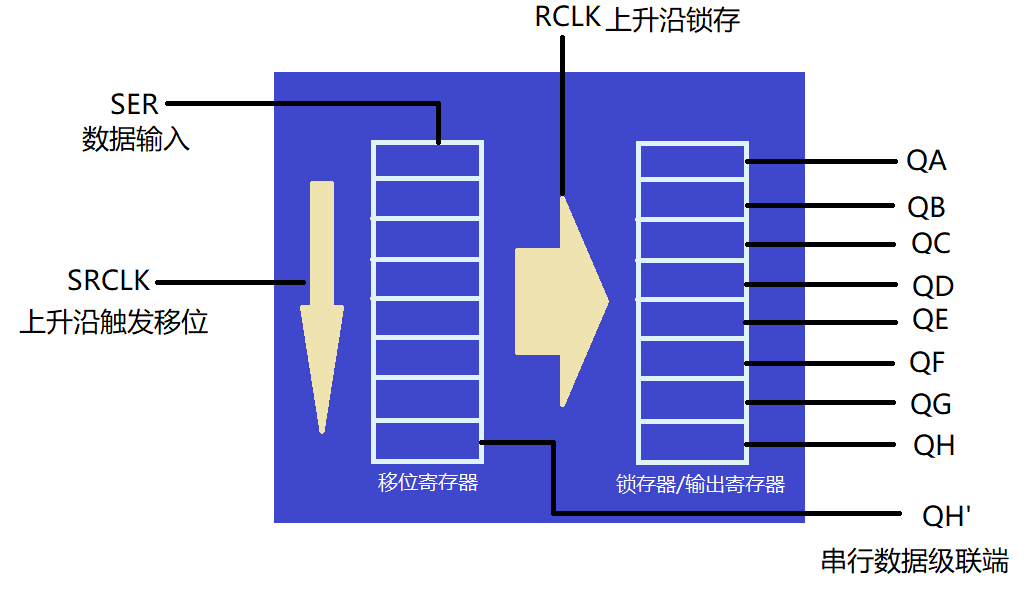

74HC595芯片是 8 位串行 - 并行移位寄存器,核心功能是将少量串行输入的数据转换为8 路并行输出的数据,同时具备数据锁存和级联扩展能力。

如下图:

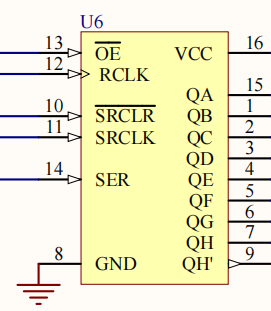

各引脚功能简述如下:

- QA - QH 为8位输出。

- QH’ 为串行数据级联端,即将本芯片的第 8 位数据传给下一个 74HC595 的 DS 引脚,实现多芯片扩展。

- OE为使能控制口,当对该引脚加低电压时,本芯片才会工作。即当OE为低电平时,并行输出QA - QH才会有效,当OE为高电平时,QA - QH呈高阻态。

SER(14脚)为串行数据输入端,逐位输入所需的数据。当SRCLK(11脚)为上升沿时,SER的数据就会移入移位寄存器的最低位,对应输出寄存器(锁存器)的位置就是QA(这时候数据还在移位寄存器),而原有的数据都会依次移位,即QA -> QB, QB -> QC, … QG -> QH, QH - QH’(移位寄存器和输出的寄存器相对应的)。- 当

RCLK(12脚)为上升沿时,移位寄存器的8位数据会同时(并行)移动到锁存器,即输出寄存器。 - 当

SRCLR(10脚)为低电平时,则会将移位寄存器的数据清零。

| 引脚 | 含义 |

|---|---|

| QA-QH(15,1-7) | 8 路并行数据输出端 |

| SER(14脚) | 串行数据输入端 |

| SRCLK (11脚) | 上升沿触发,每来一个上升沿,SER端的串行数据就会移入移位寄存器的最低位,原有数据整体逐位移动。 |

| SRCLR (10脚) | 为低电平时,会将移位寄存器的数据清零 |

| RCLK (12脚) | 上升沿触发,将移位寄存器中暂存的 8 位数据锁存到输出锁存器,进而从 QA~QH 输出 |

| OE | 输出使能端(低电平有效):接低电平(GND)时,并行输出 QA~QH 有效; 接高电平(VCC) 时,Q0~Q7 呈高阻态(相当于断开输出)。 |