电子电路学习日记

这里的 K 表示 千欧(kilo-ohm),而 F 在很多国产 EDA 软件(比如立创EDA、Altium 的一些中文封装库)里用来标注精度(公差),

-

F 代表 ±1% 精度(英文 Fine tolerance)。

-

其他常见标法:

-

J → ±5%

-

K → ±10%

-

M → ±20%

-

-

10KF = 10 kΩ ±1%

MP2451 简介

MP2451 是 Monolithic Power Systems(MPS)推出的一款高频率(2 MHz)、最大输出约 0.6 A 的降压稳压器,输入电压范围从 3.3 V 至 36 V,广泛用于汽车、工业、分布式电源等领域。它采用 SOT-23-6 或 TSOT-23-6 封装,具备高效率、内部软启动、频率衰减保护等特性

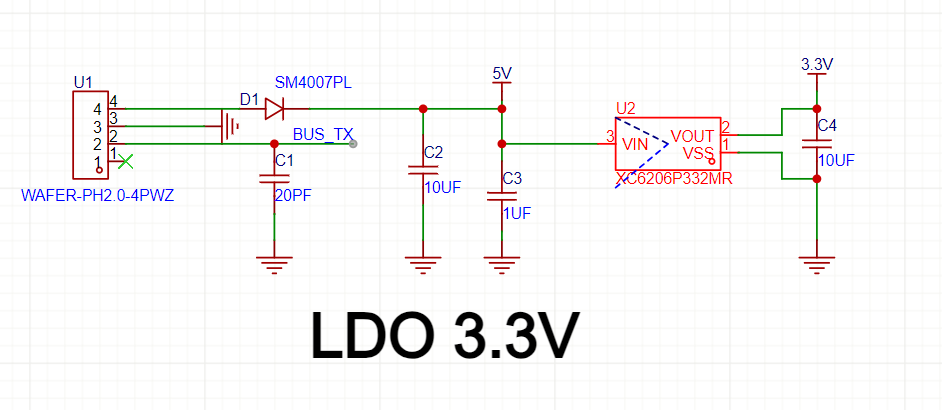

目前我用的5V转3.3V的LDO电路,如图所示:

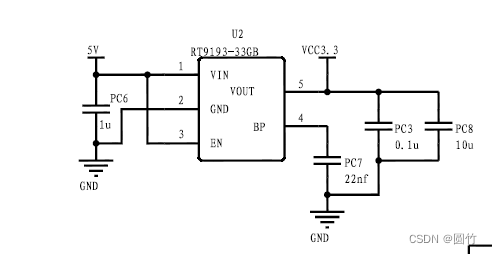

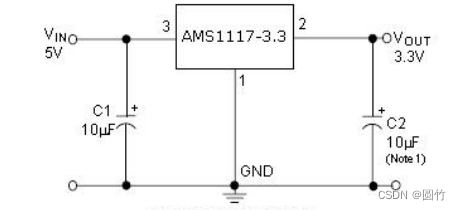

下面的是我借鉴的电路:RT9193和ASM1117

上述款为LDO稳压器组成的5V转3.3V电路,LDO电路相对于DCDC电路外围电路简单,仅需要几个电容即可。则两款电路都是常用的3.3V电路,只是价格稍有差异。

关于DCDC电路设计我的总结是一下几点:

1.确定需求(输入电压,输出电压,负载电流);

2.选择芯片(价格、封装、供货情况);

3.根据芯片规格书确定电路设计(输入电容、输出电容、输出电感、输出电压配置等),需要考虑降额设计。

降额设计:降额设计(Derating Design)就是在电路设计时,不让元器件长时间工作在它们的最大额定值附近,而是降低一定比例来使用,以提升可靠性和寿命。“元器件“吃七分饱”比“天天撑到极限”更耐用。”

PCB设计注意事项:

实际应用中PCBlayout中要注意的事项:

1)输入电容尽量靠近Vin引脚,减少寄生电感的存在,因为输入电流不连续,寄生电感引起的噪声对芯片的耐压以及逻辑单元造成不良影响 。输出滤波电容尽量靠近Vout引脚;

2)功率回路尽可能的短粗,保持较小的环路面积,较少噪声辐射。SW是噪声源,保证电流的同时保持尽量小的面积,远离敏感的易受干扰的位置。如,电感靠近SW引脚,远离反馈线。输出电容靠近电感,地端增加地过孔;

3)加粗地线宽度或者接地铜皮面积,如果不同层,要多打地孔;

4)反馈电阻尽量靠近FB引脚,从RFB到FB引脚的连线尽量短,因为这段线极易受到干扰,对输出特性影响较大;大电流负载的FB在负载远端取,反馈电容走线要就近取。

5)电感尽量选取屏蔽类型的,电感正下方所在区域不要有地线,电感量辐射容易影响地平面电平,电感下方的Bottom Layer布线影响不大。

6)芯片散热要按设计要求,尽量在底下增加过孔散热。

RFB到FB引脚的连线尽量短,因为这段线极易受到干扰,对输出特性影响较大;大电流负载的FB在负载远端取,反馈电容走线要就近取。

5)电感尽量选取屏蔽类型的,电感正下方所在区域不要有地线,电感量辐射容易影响地平面电平,电感下方的Bottom Layer布线影响不大。

6)芯片散热要按设计要求,尽量在底下增加过孔散热。

详细请参考这篇文章:学习笔记之——DCDC降压芯片基本原理及选型主要参数介绍-CSDN博客

DCDC芯片选型

DCDC Buck电源芯片选型_buck芯片选型-CSDN博客

电感的作用:“电感阻流变,储能靠磁场,高频它挡路,低频它放行。”

1.储能与释放

-

电感本质上是将电能以磁场的形式储存的元件。

-

当电流通过电感线圈时,会在周围产生磁场;当电流变化时,磁场会变化,从而根据法拉第电磁感应定律在电感两端产生感应电动势(EMF)。

-

特点:电感会阻碍电流的变化(抗变化性),电流变化越快,感应电压越大。

-

上升快 → 产生反向电压阻止电流增大

-

下降快 → 产生正向电压阻止电流减小

-

2.滤波与抗干扰

-

低通滤波:电感对高频信号阻抗大、对低频信号阻抗小,所以常用于平滑电流、去除高频噪声。

-

在开关电源(DCDC)中,电感与电容配合形成LC滤波器,降低纹波。

-

在电源输入端,电感(或共模电感)可以抑制电磁干扰(EMI)。

3.谐振与信号处理

-

电感与电容并联或串联可以构成谐振电路(LC电路),用于无线电调谐、信号选择、频率合成等。

-

在射频电路中,电感用于匹配阻抗、调节频率。

4.典型应用:

-

DCDC开关电源:存储能量并平滑输出电流。

-

滤波电路:与电容配合去除高频噪声。

-

电机驱动:抑制电流突变,保护开关器件。

-

无线充电/射频:与电容构成谐振回路。

LOAD 在电子、电路和工程中一般指 “负载”,意思是由电源、信号源等驱动或供电的对象。

它可以是一个元器件、一组电路、甚至是整个设备。