在verdi中查看波形中的glitch

1.问题

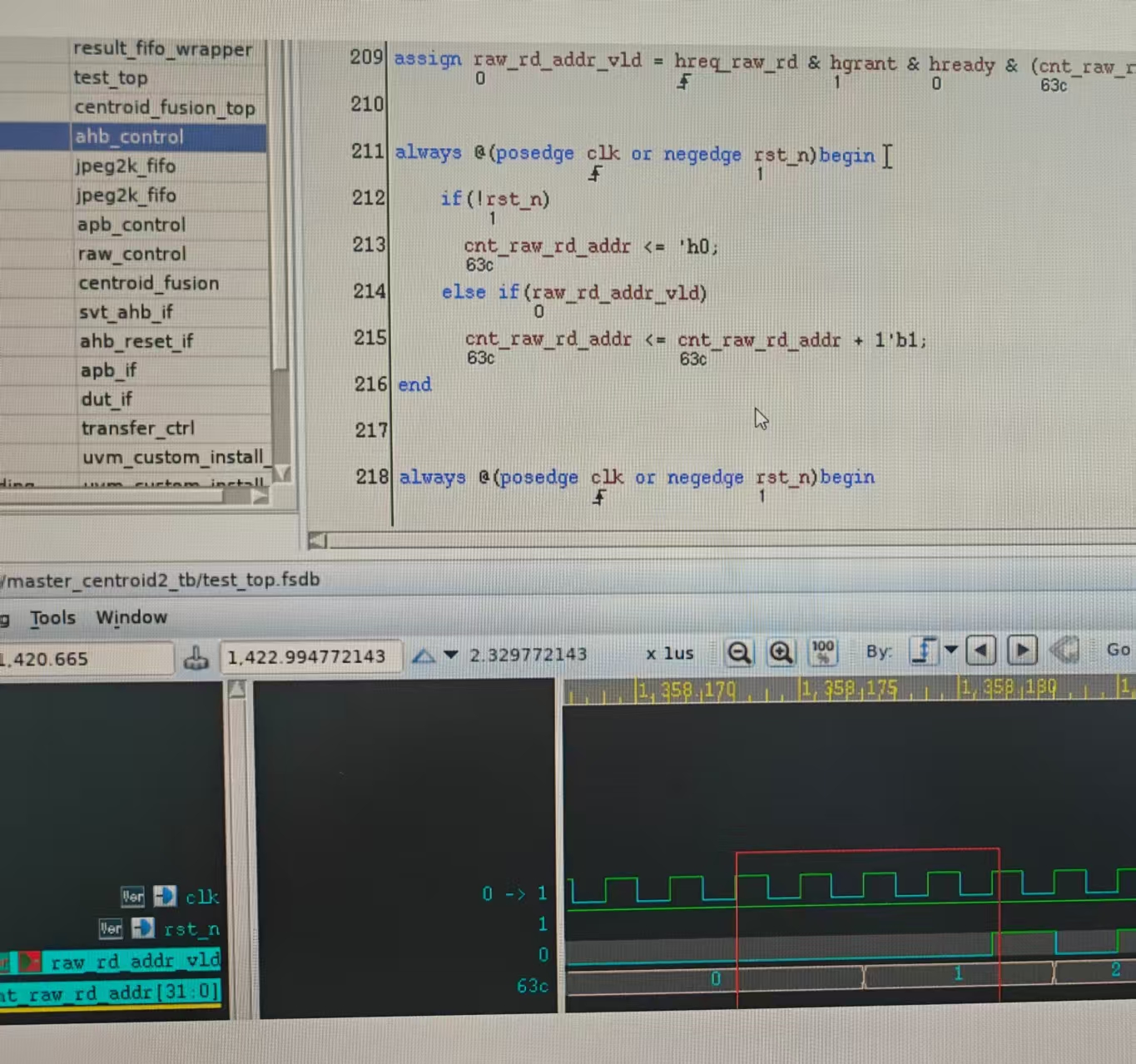

在verdi仿真测试时,遇到一个如下图波形所示的情况,raw_rd_addr_vld信号在波形为低电平时,cnt_raw_rd_addr计数器还是触发了,查看raw_rd_addr_vld波形并没有发现异常情况(实际有毛刺产生)。

2.解决方法

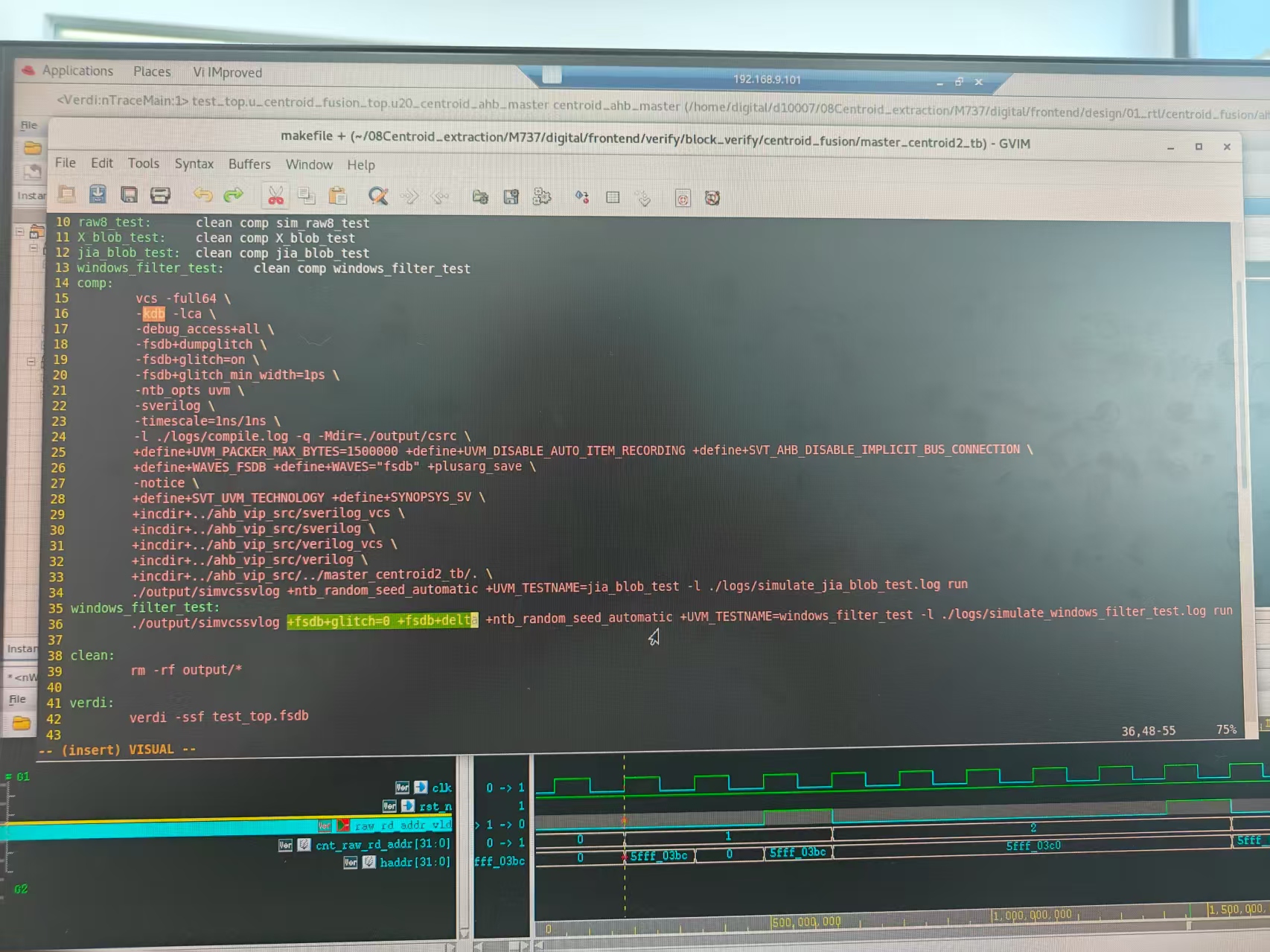

在linux环境makefile中添加如下命令:

+fsdb+glitch=0 +fsdb+delta

重新跑仿真

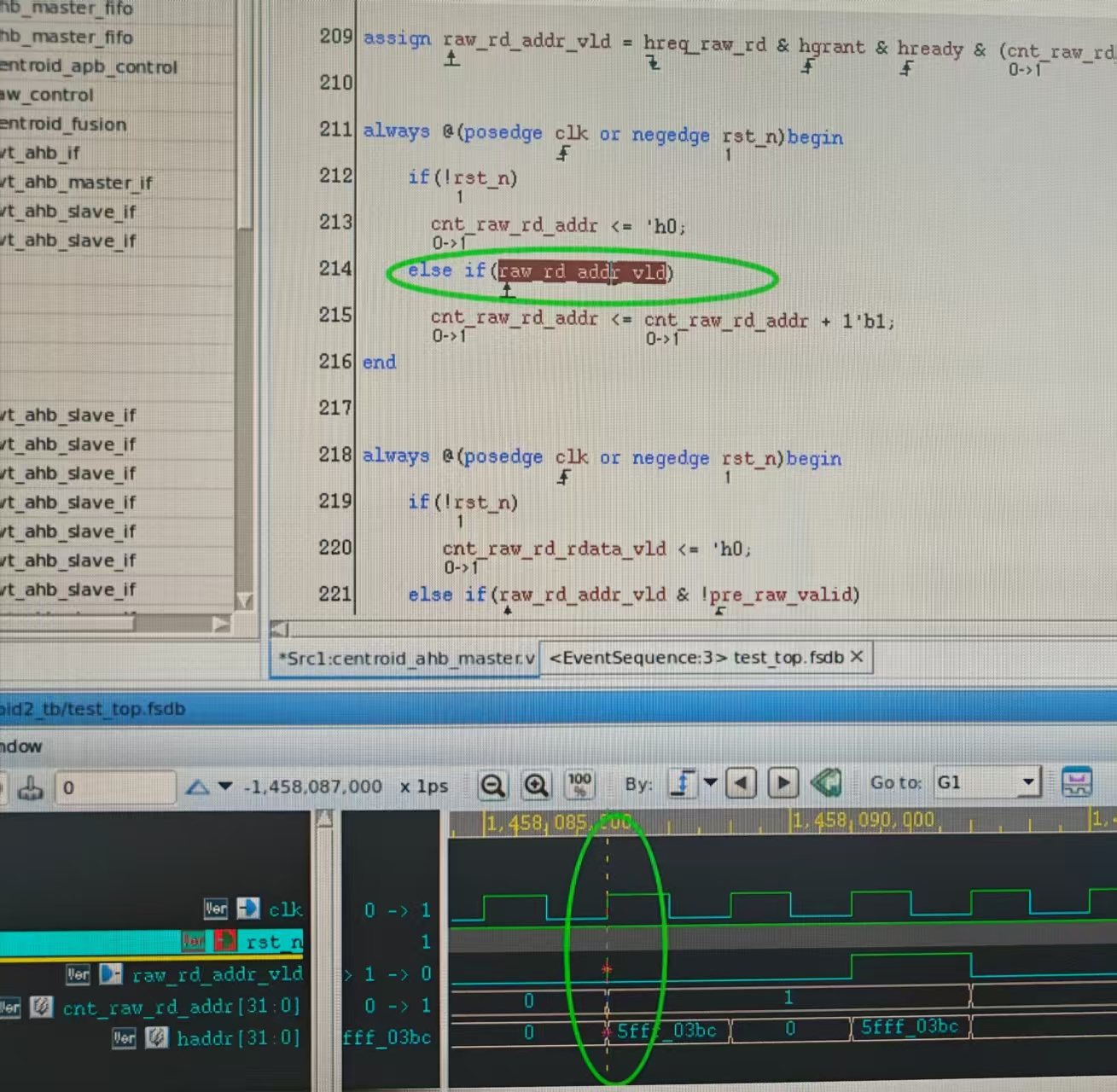

在波形窗口中打开display glitch选项:nwave > view > Display Glitch。Glitch会在波形中展示出来了,会在对应的位置有红色 "*"的标记。

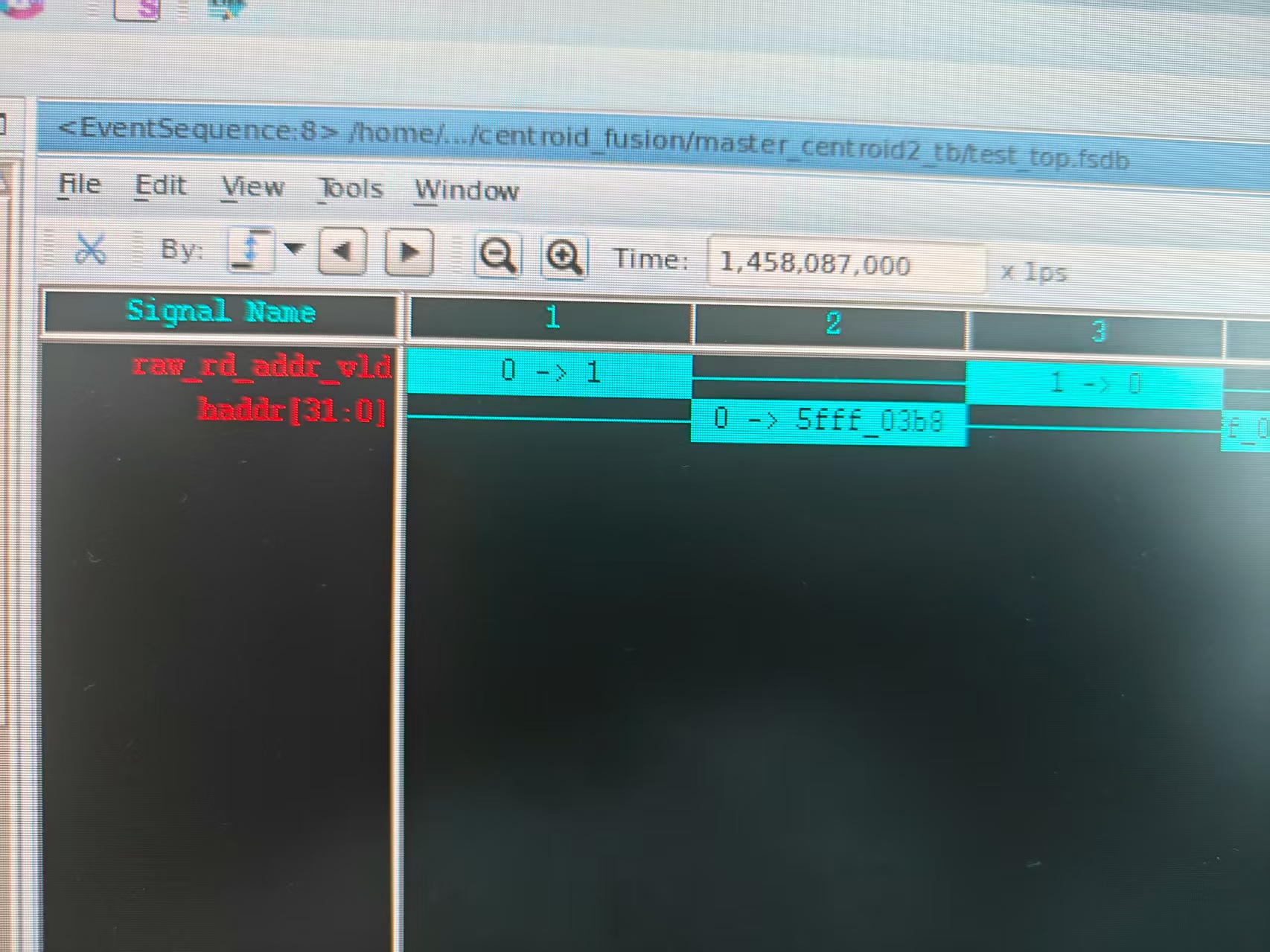

在波形窗口中打开Event Seguence选项:nwave > tools> Event Seguence。然后就可以从Event Seguence查看对应的glitch信息。

3.总结

1.更改了仿真时钟频率,之前时钟跑500M,现在跑250M,问题不复现(但毛刺实际还存在);

2.激励信号是组合逻辑造成的,存在竞争冒险,有毛刺,修改成reg型,问题可解决。