FPGA硬件设计1 最小芯片系统-Altera EP4CE10F17C8、Xilinx xc7a100t

目录

一、Altera EP4CE10F17C8

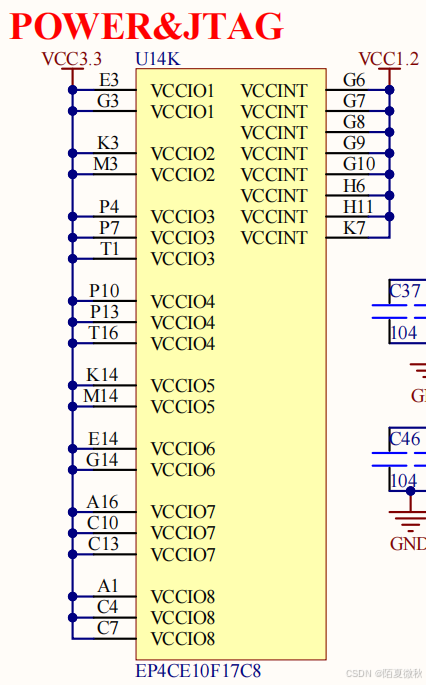

1、供电

(1)、VCCINT

(2)、VCCIO

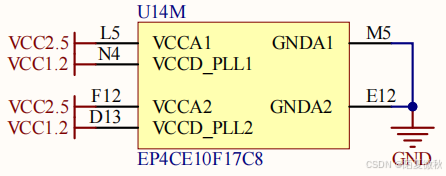

(3)、VCCA

(4)、VCCD_PLL

2、BANK设计

(1)、时钟

(2)、IO

(3)、差分

(4)、专用

二、Xilinx xc7a100t

1、供电电压

(1)、VCCINT

(2)、VCCBRAM

(3)、VCCAUX

(4)、VCCO

2、供电时序

3、BANK设计

(1)、时钟

(2)、IO

(3)、差分

(4)、专用

对比STM32而言,取消了PA、PB、PC、PD、PE此类命名,转为了BANK;

IO命名也不再具有外设的概念,例如IIC、SPI不再具有专用IO,转为了常规IO、差分IO、CLK、差分CLK。

一、Altera EP4CE10F17C8

1、供电

(1)、VCCINT

VCCINT为内核供电,即用于FPGA运行工作。

(2)、VCCIO

而VCCIO用于IO的工作电平,其做了分区处理,即可以实现不同分区的IO用于不同的工作点平。

(3)、VCCA

PLL模拟电压,2.5V,需要注意的是即使FPGA设计中未使用PLL仍要提供VCCA。

(4)、VCCD_PLL

PLL数字电压,1.0V/1.2V,一般接1.2V。

此类低端FPGA一般不考虑严格的上电时序,即有输入5V,输出3.3、2.5、1.2即可。

2、BANK设计

最方便看一个FPGA有几个BANK,就看供电区域即可,IO一般命名为VCCIOx,其中x为数字。

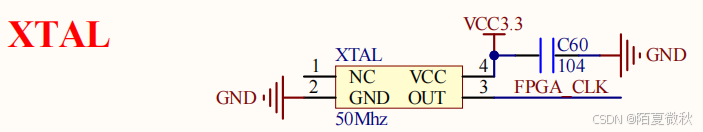

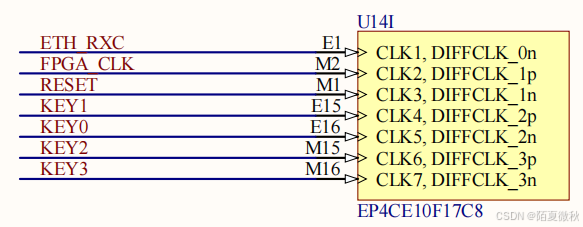

(1)、时钟

这个是FPGA运行起来的核心,例如EP4CE10F17C8,其具有7个CLK输入。

其采用了单端时钟输入模式,因此外置的晶振输出时钟必须接到该IO上。高端的片子具备差分时钟输入接口。

(2)、IO

几乎所有的接口都可以当作常规单端IO口使用。

(3)、差分

一旦使用差分,必须成对存在。

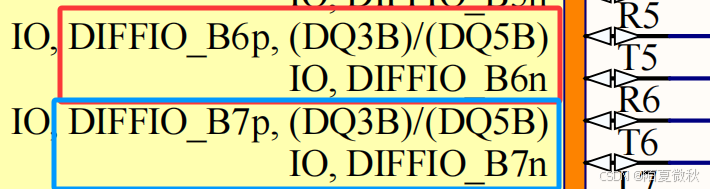

红色6p和6n为一组,蓝色7p和7n为一组,由于差分对在芯片端是固定的,因此IO约束的时候,通常只约束p即可,所以一旦使用必须成对存在。

(4)、专用

以DDR接口为例,此专用IO有的FPGA会允许修改引脚,有的不允许,对于不允许的必须按照IO分配进行DDR连接。进行8位DDR2设计时,就指定了相关的DQ、DQS和DQM引脚,我们设计时应该遵从这些引脚约束。

在该FPGA的上、下、左、右区域分别都指定有这些引脚:

每个方向又都分有4个区,若是选择8位的DDR,则每个区有9个DQ引脚和相应的DQS、DQM:

(1)左:DQ0L、DQ1L、DQ2L、DQ3L,以及DQSL和DML;

(2)下:DQ2B、DQ3B、DQ4B、DQ5B,以及DQSB和DMB;

(3)右:DQ0R、DQ1R、DQ2R、DQ3R,以及DQSR和DMR;

(4)上:DQ2T、DQ3T、DQ4T、DQ5T,以及DQST和DMT;

比如:在DQ5B中,这9个DQ引脚为:Y10,W10,V11,AA8,AA9,AB8,U10,Y8,AB7,以及AB9(DQS)、AA7(DQM)。

因此,在硬件设计时,应该将这些相应的引脚(8位数据DQ和DQS、DQM)正确分配,至于这8位DQ数据的位置则可以根据布线的方便而相互对调,保证它们在同一区即可(如DQ5B区);而对于其它的DDR2引脚(地址线、控制线等),则可以根据布线的方便而随意分配,但必须保证所有DDR2的引脚都在FPGA的同一个或两个Bank区(如Bank3和Bank4,因为有时一个Bank区放不了所有这些引脚)。

这样做的目的就是为了便于对它们进行统一的VCCIO电压的指定,以及考虑后续PCB布线的方便性,注意该Bank区的VCCIO电压必须指定为1.8V。

二、Xilinx xc7a100t

开始有上电时序的概念。

1、供电电压

(1)、VCCINT

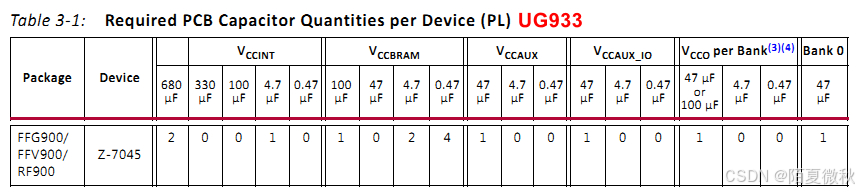

VCCINT为内核供电,即用于FPGA运行工作。要求供电电源为1.0V±3%;该电源网络命名为VCCINT_1V0;由于VCCINT_1V0电源电流很大,在靠近电源芯片侧,需要放置2个680uF或4个330uF的电容(由于低气压要求,不能使用钽电容),用于储能;另外,每个电源管脚视PCB面积保证至少有1个4.7uF或0.47uF去耦电容。该电源的上电爬升时间要求为0.2ms-50ms。

(2)、VCCBRAM

RAM电源电压,要求供电电源为1.0V±3%;该电源网络可以直接连接到VCCINT_1V0,VCCINT and VCCBRAM可用同一电源供电。

(3)、VCCAUX

FPGA辅助电源电压辅助电源,要求供电电源为1.8V1.8V±5%,该电源网络命名为VCC_PL_1V8;保证至少有1个100uF电容,其余每个管脚视PCB面积保证至少有1个100nF去耦电容;该电源的上电爬升时间要求为0.2ms-50ms。

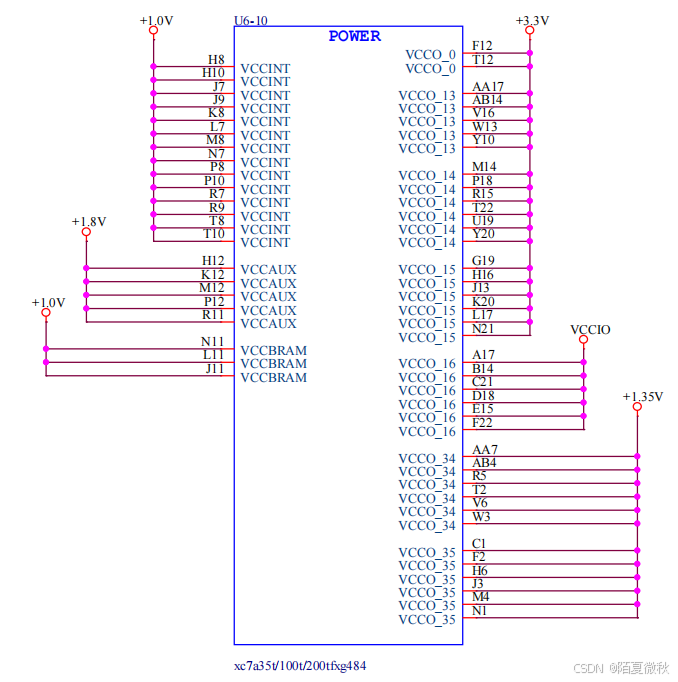

(4)、VCCO

Bank的IO电源电压,K7芯片有HR和HP两种Bank;

- HR Bank的VCCO范围是1.2V-3.3V;HP Bank VCCO一般使用1.8V,要求1.8V±5%,该电源网络命名为VCCO_1V8,该电源网络可以直接连接到VCC_PL_1V8;

- HP Bank的VCCO范围是1.2V-1.8V。HR Bank VCCO一般使用3.3V,要求3.3V±5%,该电源网络命名为VCCO_3V3。

- 信号完整性:高速数据传输要求信号在传输过程中的完整性和稳定性。较高的电压可能会导致信号反射和串扰问题,影响信号的完整性,尤其是在高速接口中。因此,为了保持信号的完整性,DDR接口的Bank电压被限制在1.8V。

- 电源稳定性:随着数据传输速率的提高,对电源稳定性的要求也随之增加。较高的电压可能会增加电源噪声,从而影响数据传输的稳定性。限制Bank电压有助于减少电源噪声,确保数据传输的可靠性。

- 功耗和热管理:高速接口在数据传输过程中会产生较多的热量。限制电压有助于控制功耗,从而减少热量的产生,对于热管理是非常重要的,尤其是在高密度集成的系统中。

- 电气特性:DDR内存的电气特性决定了其工作电压。1.8V是一个平衡点,既能满足高速数据传输的需求,又能保持较低的功耗和热产生。此外,这也是DDR内存规范中定义的标准工作电压之一。

- 兼容性和标准化:在FPGA和ASIC设计中,Bank电压的标准化有助于提高设计的兼容性和可移植性。1.8V作为一个广泛接受的标准电压,有助于确保不同设备和系统之间的兼容性。

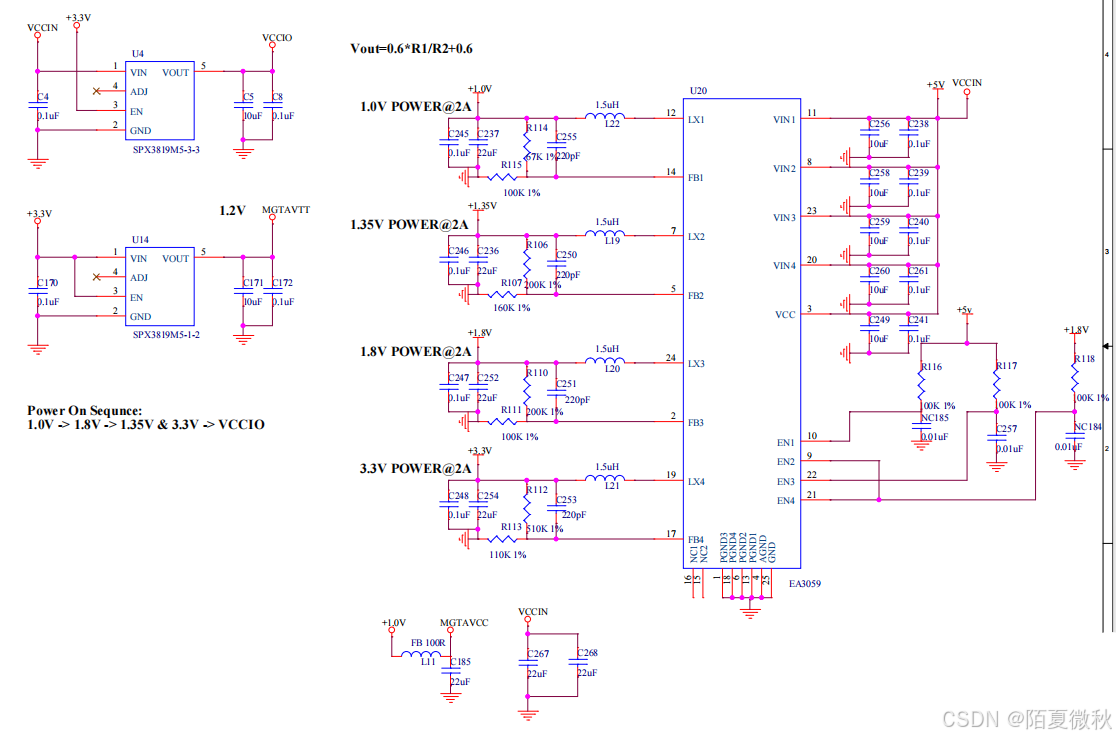

2、供电时序

VCCINT&VCCBRAM→VCCAUX&VCCO_1V8 →VCCO,即VCCINT_1V0→VCC_PL_1V8 →VCCO_3V3;

如果有用到DDR,则保持和VCCO_3V3同步即可。

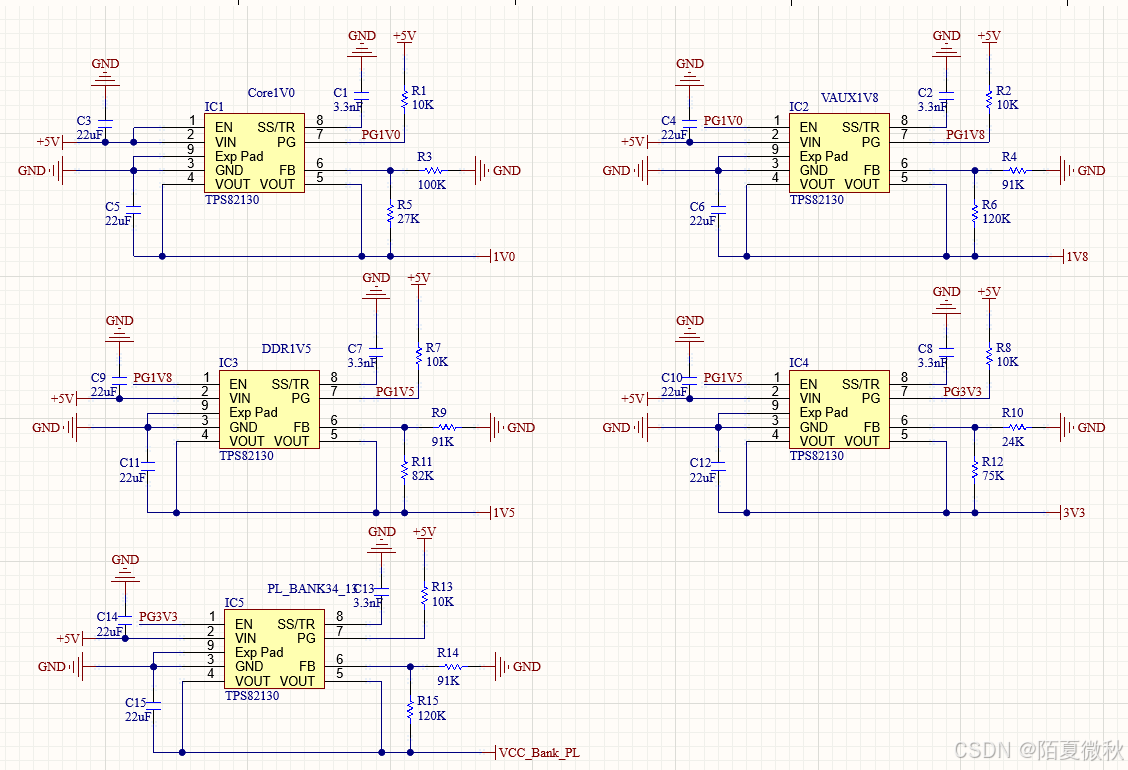

如图为单个芯片输出多路电源及供电时序设计,例如5V进来后先驱动EN1、EN3,即实现1V、1.8V输出。

然后1.8V有了电压后驱动EN2、EN4即1.35和3.3V输出。

同理,较低成本的可以用例如多个电源IC的形式。

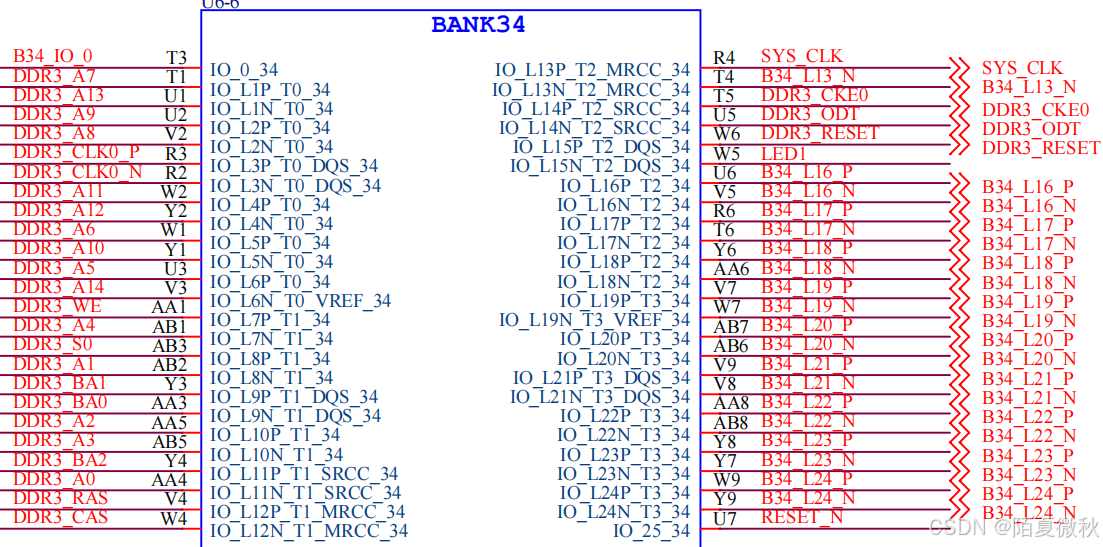

3、BANK设计

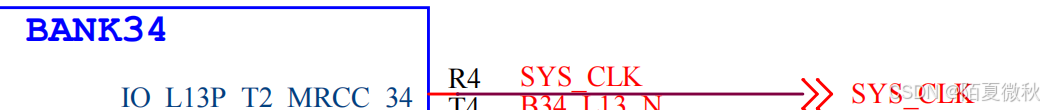

(1)、时钟

Xilinx的时钟IO更加多样化,且几乎每个BANK都有例如:MRCC、SRCC。

MRCC和SRCC都是由外部的时钟驱动,而且MRCC和SRCC的区别就在于MRCC可以驱动BUFMR,SRCC不行。其他基本都一样,它们都可以驱动四个BUFIO、四个BUFR、一个CMT、上下相邻的CMT、16个BUFG和BUFH。

它们都可以驱动BUFG和BUFH,这就意味着,从MRCC和SRCC进来的时钟都可以access全局时钟树,也就都可以当做全局时钟。

(2)、IO

几乎所有的引脚都带了IO的前缀。

(3)、差分

带了P、N的即为差分对,前置Lx即第几对。

(4)、专用

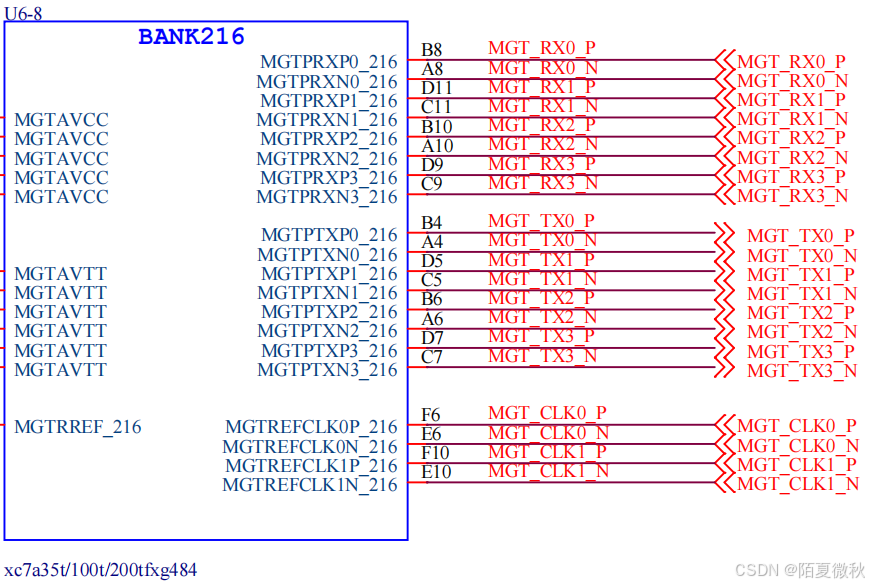

例如MGT,其采用了专用IO的格式,甚至IO都是固定的。

MGTBANK(Multi-GigabitTransceiverBank,多吉比特收发器)是XilinxFPGA中的一个重要功能模块,尤其在支持高速通信和串行传输时至关重要。可以把它理解为一个高速串行并行转换器,其串行速率可达几十G。

它可以将输入的并行数据转换为串行输出,或者将串行数据转换为并行数据。它既可以作为独立的发送装置或接收装置,也可以同时进行发送和接收。此外,用户可以根据需要自定义协议来实现通信,与其他核配合使用,以实现协议通信。不同型号、不同封装的FPGA具有不同数量的MGTBank,传输速度都不一样。

- 高速IO接口类型:GTP、GTX、GTH、GTY、GTZ、GTM

- 速率大小为:GTP<GTX<GTH<GTZ<GTY<GTM