Z20K118库中寄存器及其库函数封装-CLOCK库

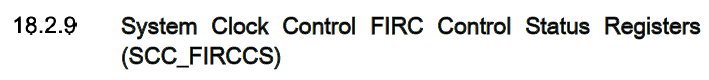

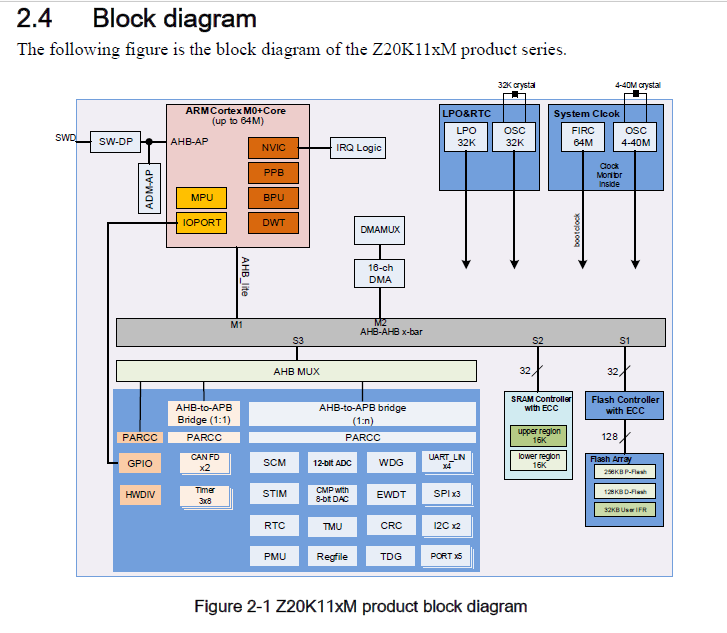

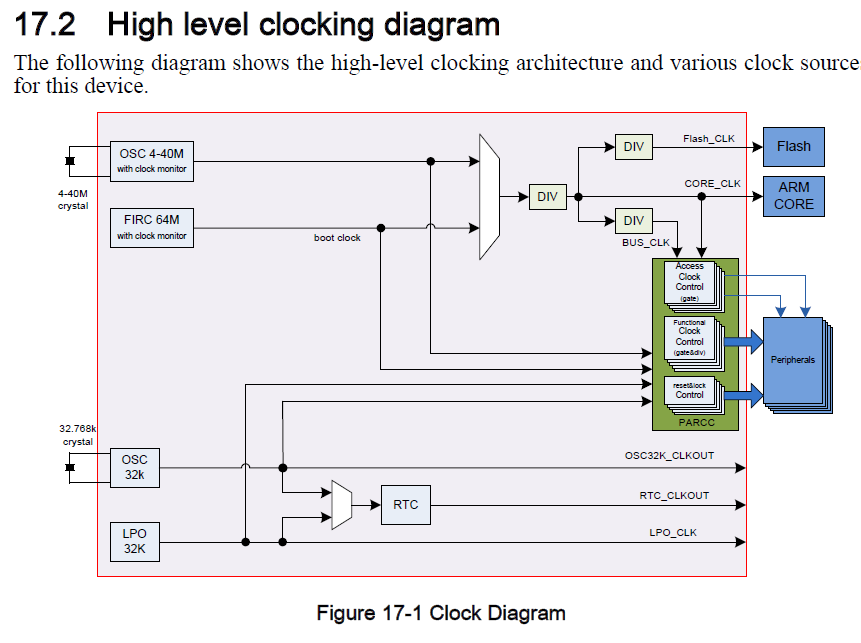

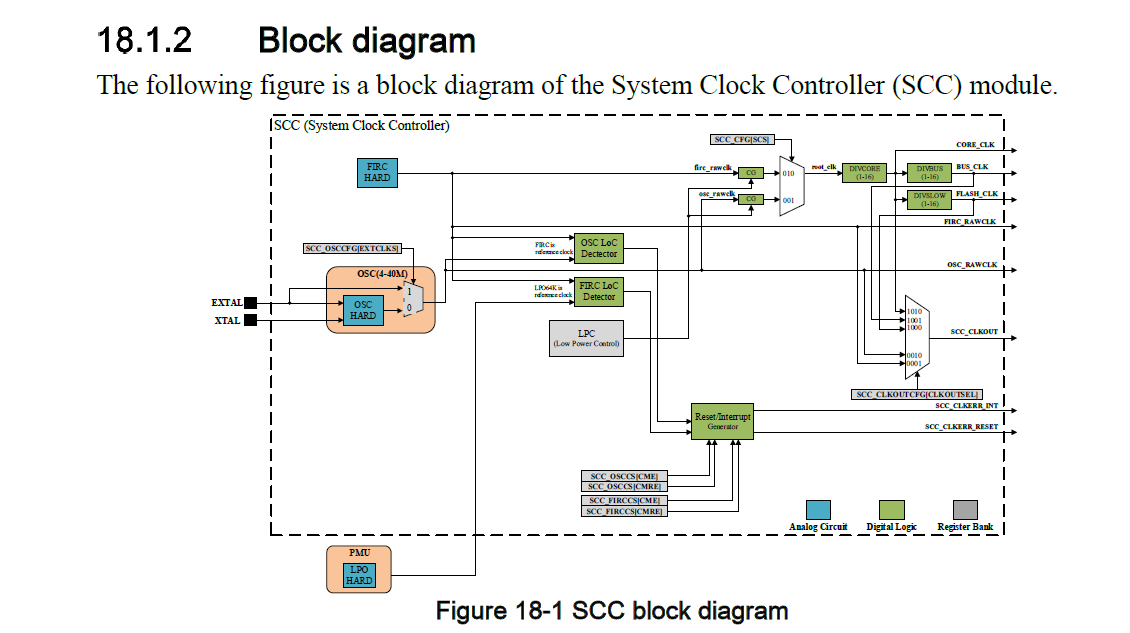

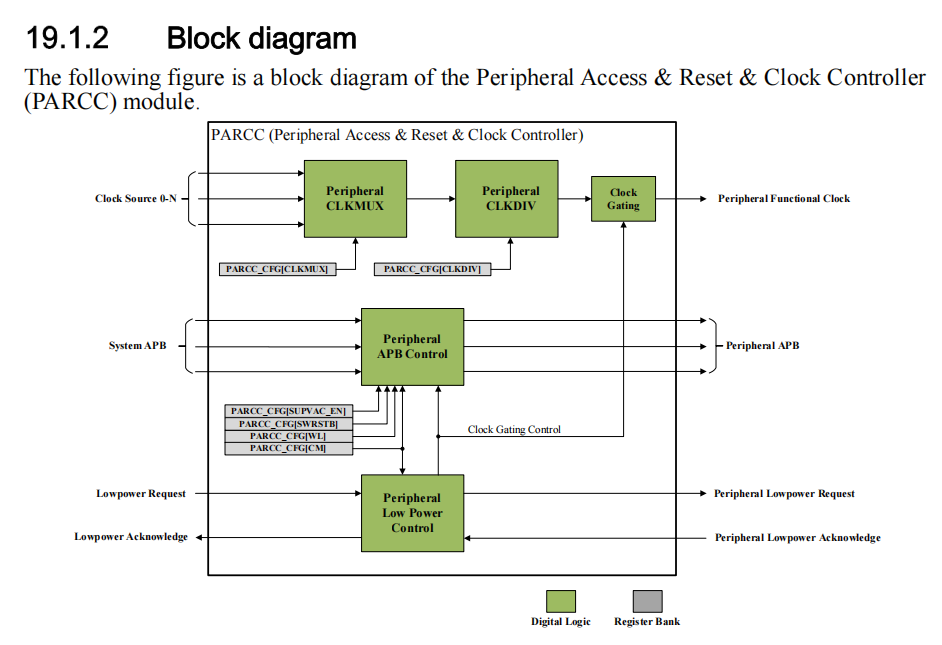

模块框图

1.系统时钟控制_时钟状态寄存器(SCC)

![]()

4个。4个位域表示4个参数的状态:1个系统时钟源,1个总线分频系数,1个内核分频系数,1个闪存(SLOW CLOCK)分频系数。

内核分频系数可理解为系统时钟分频系数,因为其位置紧挨着系统时钟之后,总线、内核等所有模块之前,此时内核模块本身不分频。参考上图。

除了CFG末尾的锁定位,SCC_CFG寄存器和SCC_CST寄存器的所有位名称完全一致,前者用于配置相关参数,后者用于读取相关参数。

1-1

static uint32_t CLK_GetSysClkFreq(uint32_t oscFreq)返回系统时钟频率。读取本寄存器的SCS位判断系统时钟源(FIRC64M/OSC40M两种),若为FIRC64M直接返回64M,若为OSC40M则返回输入的参数,该函数的参数不具备设置时钟频率的功能。1个,核心为返回系统时钟源。

1-2

static void CLK_WaitOSC40MSwitchReady(void)等待OSC切换(方波切晶振)。1个,内核分频系数。该函数由其他库函数调用,用户无需使用只需了解。空循环等待外部两种OSC振荡器切换完成。外部OSC40M可同时接晶体OSC和方波OSC,当方波OSC切换到晶体OSC时需要使用该函数进行切换等待,反过来切换则无需等待。本质上就是单纯的空循环一定次数,默认为3500次(厂商设定),若设定了内核分频系数,则空循环次数/内核分频系数,例如2分频的循环次数为3500/2=1750。因此该函数的等待时间不会根据系统时钟频率发生改变,始终等于OSC振荡器40MHz时钟执行3500次,等待时间固定。

1-3

CLK_System_t CLK_GetSysClkSrc(void)读取系统时钟源(OSC40M/FIRC64M)。实际上读取本寄存器的SCS位判断。1个。

1-4

uint32_t CLK_GetModuleClkFreq(CLK_Module_t module,uint32_t oscFreq)获取模块频率。参考8-2。

2.系统时钟控制_FIRC控制状态寄存器(SCC)

9个。5个为配置FIRC时钟:1.使能 2.停止模式使能 3.FIRC时钟监视器中断或复位使能 4.FIRC时钟监视器中断使能 5.选择监视器检测到丢失信号时中断还是复位。3个位FIRC时钟状态:1.就绪 2.被选为系统时钟 3.监视器检测到丢失信号 。1个锁定位。

FIRC控制状态寄存器与OSC控制状态寄存器内部为一一对应关系。

2-1

void CLK_FIRC64MEnable(ControlState_t stopModeEn)正常模式和停止模式使能。2个。

2-2

void CLK_FIRC64MDisable(void)正常模式失能,1个。

2-3

void CLK_FIRC64MMonitorEnable(CLK_MonitorAct_t act)使能和配置FIRC的监视器为中断或复位。3个,1个使能监视器,1个使能监视器处理(中断或复位),1个选择处理方式(中断或复位)。

2-4

void CLK_FIRC64MMonitorDisable(void)失能FIRC监视器。1个。

3.系统时钟控制_OSC控制状态寄存器&OSC配置寄存器(SCC)

CS: 9个。5个为配置OSC时钟:1.使能 2.停止模式使能 3.OSC时钟监视器中断或复位使能 4.OSC时钟监视器中断使能 5.选择监视器检测到丢失信号时中断还是复位。3个位OSC时钟状态:1.就绪 2.被选为系统时钟 3.监视器检测到丢失信号 。1个锁定位。

CFG:3个。1个选择2种OSC,1个使能循环模式,1个设置高频或低频模式。

FIRC控制状态寄存器与OSC控制状态寄存器内部为一一对应关系。

3-1

ResultStatus_t CLK_OSC40MEnable(uint32_t freq, ControlState_t stopModeEn,CLK_OscMode_t mode)2种OSC时钟的选择、配置和使能。厂商建议使用最下方函数而不是本函数,原因在于参数freq配置的时钟频率可能不精准。CS1个,CFG3个即全部。

先配置停止模式(CS),再根据输入频率设置低频/高频模式(CFG),再选择2种OSC时钟(CFG),再使能循环模式(CFG),最后使能OSC时钟并等待使能完成标志位。

等待标志位使用![]() 函数,4种时钟源(包括非系统时钟源)使能时都要调用该函数。

函数,4种时钟源(包括非系统时钟源)使能时都要调用该函数。

CLK_OSC40MEnable2()3-2

ResultStatus_t CLK_OSC40MEnable2(CLK_OscFreqMode_t freqMode, ControlState_t stopModeEn, CLK_OscMode_t mode)OSC时钟源配置和使能。与3-1基本相同,唯一区别在于3-1的参数1为频率,函数内部通过频率设置高频模式或低频模式,本函数参数1为结构体直接设置高频模式或低频模式,这样可避免3-1输入的频率值为错误值,无需输入32位整型使得本函数更安全。

3-3

void CLK_OSC40MDisable(void)失能OSC40M时钟源。CS1个,CFG1个。即先OSCEN位置0失能OSC,再OLMEN置0关闭循环模式。

3-4

void CLK_OSC40MMonitorEnable(CLK_MonitorAct_t act)使能和配置OSC的监视器为中断或复位。3个CS,1个使能监视器,1个使能监视器处理(中断或复位),1个选择处理方式(中断或复位)。

3-5

void CLK_OSC40MMonitorDisable(void)失能OSC监视器。1个CS。

4:系统时钟控制_时钟配置寄存器(SCC)

5个。4个位域表示4个参数的状态:1个系统时钟源,1个总线分频系数,1个内核分频系数,1个闪存(SLOW CLOCK)分频系数。1个锁定位。

除了CFG末尾的锁定位,SCC_CFG寄存器和SCC_CST寄存器的所有位名称完全一致,前者用于配置相关参数,后者用于读取相关参数。

4-1

ResultStatus_t CLK_SysClkSrc(CLK_System_t clk)系统时钟源选择(OSC40M/FIRC64M)。1个。

4-2

void CLK_SetClkDivider(CLK_Module_t module, CLK_Divider_t divider)总线/外设/内核/闪存/的时钟分频系数配置。若为总线/外设/内核则配置本寄存器,每个各1位域。若为外设则配置对应的PARCC寄存器的相应位域,1个。

5.系统时钟控制_时钟输出配置寄存器(SCC)

1个。选择引脚的时钟输出源,5种选择:FIRC65M,OSC40M,SCC SLOW CLK,SCC BUS CLK,SCC CORE CLK。相关封装库函数参考10.芯片控制寄存器。

6.电源管理单元_LPO32K控制寄存器(PMU)

![]()

2个。1个使能,1个就绪标志位。

6-1

void CLK_LPO32KEnable(void)使能LPO32K时钟。1个。

6-2

void CLK_LPO32KDisable(void)失能LPO32K时钟。1个。

7.RTC时钟_控制和状态寄存器(RTC)

![]()

RTC不仅可以选择OSC32K作为时钟源,还可选择LPO作为时钟源,本次只讨论OSC32K。

12个位域。仅配置其中2个。一个CRYSTAL_EN位使能OSC,一个EXTAL_32K_EN选择2种OSC。

7-1

void CLK_OSC32KEnable(CLK_OscMode_t mode)配置和使能OSC32K时钟。 2个。

7-2

void CLK_OSC32KDisable(void)失能OSC32K时钟。 2个。

8.外设访问/复位/时钟控制寄存器(PARCC)

11个位域。

8-1

ResultStatus_t CLK_ModuleSrc(CLK_Module_t module, CLK_Src_t clockSource)外设时钟源选择。参数1为外设名,参数2为时钟源。1个。

8-2

uint32_t CLK_GetModuleClkFreq(CLK_Module_t module,uint32_t oscFreq)/外设/内核/总线/慢速时钟/的时钟频率获取。参数1为需要读取时钟频率的模块。

外设:读取PARCC(约11位域)的CLKMUX得到时钟源和CLKDIV得到分频系数,相除得到频率。(若外设时钟源为OSC则参数2为其原始频率)。2个PARCC。

内核:读取SCC_CST寄存器的DIVCORE位得到分频系数,调用CLK_GetSysClkFreq(oscFreq)函数得到原始频率,后除前得内核频率。2个CST。

总线:在读取内核分频系数和原始频率的基础上再读取自身分频系数,内核频率除自身分频系数可得总线频率。3个CST。

闪存:在读取内核分频系数和原始频率的基础上再读取自身分频系数,内核频率除自身分频系数可得闪存频率。3个CST。

9.系统控制模块_定时器配置寄存器(SCM)

![]()

本寄存器3个位域,分别对应3个定时器的外部引脚选择。

9-1

void CLK_TimExternalClkSrc(CLK_TIM_t timId, CLK_TIMExtClk_t clockSrc)配置定时器的外部引脚输入时钟源。参数1为定时器号,参数2为外部引脚号(CLK_TIM_PTB1/CLK_TIM_PTE1_PTA5/CLK_TIM_PTE8)。根据参数1选择不同位域配置不同定时器,参数2为该位域填入值。

10.系统控制模块_芯片控制寄存器(SCM)

![]()

3个位域,用于在引脚输出时钟信号。CLKOUTSEL配置时钟输出源(LPO32,OSC32或SCC系统时钟输出 ),CLKOUTDIV配置时钟输出分频系数。CLKOUTEN配置时钟输出使能。本寄存器配置一定要按照如下顺序:选择时钟源(CLKOUTSEL),配置分频系数(CLKOUTDIV),最后使能时钟(CLKOUTEN)。

10-1

void CLK_ClkOutEnable(CLK_OutSrc_t outSrc, CLK_OutDiv_t divider)引脚输出时钟信号的使能和配置。3个。先根据参数1配置引脚的时钟输出源,7种时钟输出源。CLKOUTSEL为10b输出LPO32K,为01b输出OSC32K,为00b则输出系统时钟(由5.时钟输出配置寄存器配置)。再根据参数2配置引脚时钟输出分频系数。最后使能。

10-2

void CLK_ClkOutDisable(void)引脚输出时钟信号失能。1个。

X.多寄存器和通用函数

X-1

FlagStatus_t CLK_GetClkStatus(CLK_Src_t clockSource)获取时钟是否就绪状态。根据4种时钟源分别读取PMU_LPO_32K_CFG/SCC_FIRCCS/ RTC_CSR/SCC_OSCCS的对应RDY位返回时钟准备就绪信息。

X-2

ResultStatus_t CLK_WaitClkReady(CLK_Src_t clockSource)等待时钟就绪。通常由其他库函数调用。进行10w次计数,每次计数根据4种时钟源分别读取PMU_LPO_32K_CFG/SCC_FIRCCS/ RTC_CSR/SCC_OSCCS的对应RDY位,若RDY位置1则跳出循环代表时钟就绪,计满则时钟就绪失败。

X-3

void SCC_InstallCallBackFunc(CLK_Int_t intId,isr_cb_t * cbFun)安装回调函数。

X-4

void SCC_IntClear(CLK_Int_t intId)清除监视器丢失信号的中断标志位。根据配置将SCC_FIRCCS或SCC_OSCCS的OSCLOC或FIRCLOC置1即为清除。

X-5

void SCC_DriverIRQHandler(void)中断处理驱动函数。